## A 1.5 V, 2.4 GHz Monolithic CMOS Sub-Integer-N Frequency Synthesizer for WLAN Application

CHANG, Ka Fai

A Thesis Submitted in Partial Fulfillment

of the Requirements for the Degree of

Doctor of Philosophy

in

Electronic Engineering

The Chinese University of Hong Kong January 2011 UMI Number: 3491995

#### All rights reserved

#### INFORMATION TO ALL USERS

The quality of this reproduction is dependent on the quality of the copy submitted.

In the unlikely event that the author did not send a complete manuscript and there are missing pages, these will be noted. Also, if material had to be removed, a note will indicate the deletion.

#### UMI 3491995

Copyright 2011 by ProQuest LLC.

All rights reserved. This edition of the work is protected against unauthorized copying under Title 17, United States Code.

ProQuest LLC, 789 East Eisenhower Parkway P.O. Box 1346 Ann Arbor, MI 48106 - 1**346**

## **ABSTRACT**

#### A 1.5 V, 2.4 GHz Monolithic CMOS Sub-Integer-N

#### Frequency Synthesizer for WLAN Application

Wireless local area networks (WLANs) are being extensively deployed since their introduction in the late 1990s. Low cost, high performance frequency synthesizers are indispensable in WLAN telecommunication systems. Meanwhile, integer-N phase-locked loop (PLL) architecture is commonly chosen due to its low circuit complexity and clean output spectrum with few spurs. However, designers have to face the tradeoffs between frequency resolution, phase noise performance and switching time. To solve the above dilemma, fractional-N PLL architecture is proposed, but fractional spurs emerge in the output spectrum, degrading the spectrum purity. Sub-integer-N PLL is thus a compromise between the integer-N and fractional-N PLL. Its structure is same as that of the integer-N while fractional division is achieved by a fractional frequency divider that is not relied on time-varying modulus control as in the fractional-N PLL.

This thesis presents the design of a 2.4 GHz sub-integer-N PLL for IEEE 802.11b/g WLAN applications. The proposed PLL not only acquires the advantages of the integer-N PLL, such as simple structure and good spurious performance, but also offers some benefits (for example, faster settling time and better phase noise performance) as in the

fractional-N PLL design. In this design, a novel quadrature-input programmable fractional frequency divider provides fractional division ratio in steps of 0.5 by the phase-switching technique. Its key building block is a dual divide-by-4 injection-locked frequency divider (ILFD), which is realized by coupling two conventional divide-by-4 ILFDs. Two different coupling schemes are introduced, namely the cross-coupling type and coherent-coupling type. In both schemes, symmetric configuration is maintained and hence does not degrade the PLL output phase quadrature accuracy. Furthermore, the generated phase pattern for phase switching is uniquely defined, which simplifies the phase-switching circuitry and suppresses the possibility of incorrect frequency division due to glitches.

To demonstrate the feasibility of the two proposed coupling methodologies, two sub-integer-N PLLs with different fractional frequency dividers have been fabricated in a 0.35 μm standard CMOS process. In design 1, the dual divide-by-4 ILFD in the fractional frequency divider is implemented with the cross-coupling scheme while the coherent-coupling scheme is used in design 2. The measured spurious tones of both designs are under -64 dBc and their measured phase noise at 1 MHz frequency offset is less than -115 dBc/Hz. The two proposed frequency synthesizers settle at approximately 32 μs and their phase mismatches of the quadrature outputs are better than 38 dB (characterized by image rejection ratio). Moreover, both designs individually occupy a chip area as small as 0.70 mm². At a supply of 1.5 V, the total power consumption for each design is below 24.1 mW.

## 摘要

自90年代後期提出概念起至現在,無線區域網絡(WLAN)的發展達到飛躍的進步,低廉且高性能的頻率合成器成爲無線區域網絡通訊系統中不可或缺的元件。在各種頻率合成器電路當中,整數分頻鎖相環因其簡潔構造和高信號純度,而被廣泛應用。不過,它受到頻率分辨度、相位噪聲和穩定速度之間折衷的限制。小數分頻鎖相環可用於解決以上難題,但衍生出來的分數雜散影響了頻譜的純度。於是,人們提出亞整數分頻鎖相環以便在兩者中取得平衡,它的好處在於擁有如整數分頻鎖相環的樸實電路結構,並以非整數除法器取代在小數分頻鎖相環中使用的時變模組控制方法來達到非整數分頻。

本論文呈獻一個依據 IEEE 802.11b/g WLAN 通訊系統考量而設計,並運行於 2.4 GHz 頻譜的亞整數分頻鎖相環。此鎖相環兼備前述兩種鎖相環的優點,如擁有 像整數分頻鎖相環般的易於設計架構和高雜散性能,而穩定速度和相位噪聲也能達 到一般小數分頻鎖相環所有的優勢。另一方面,在本設計中,還提出了一種嶄新的 正交相位輸入、可編程非整數除法器,以相位切換技術,能獲得半步的非整數分頻 步長。在此電路中,主要包含了兩個交互耦合的除四注入鎖定分頻器,而兩種不同 的耦合方法將在本論文內論述,分別爲交叉耦合和同調耦合。這兩種耦合方法都保 有對稱的結構,使得鎖相環輸出端的正交相位精度不受影響。此外,用於相位切換

而產生的相位順序是唯一的,所以,相位切換電路能大大簡化,也降低了因脈衝雜 訊所引起的不正確分頻風險。

兩個擁有不同非整數除法器的亞整數分頻鎖相環電路經由一種標準 0.35 微米互補金屬氧化物半導體 (CMOS) 製程被製作出來,用以檢驗兩種建議的耦合方法之可行性。在一號設計內,交叉耦合方法採用在非整數除法器的雙除四注入鎖定分頻器中,而同調耦合方法則應用在二號設計內。根據實驗結果顯示,兩個鎖相環的雜散譜綫低於 -64 dBc,而離主頻 1 MHz 處的相位噪聲不多過 -115 dBc/Hz,另外,他們能在大約 32 μs 內穩定下來,輸出端的相位差也優於 38 dB (以鏡像消除比率來界定),並且,兩個設計所佔用的芯片面積分別少於 0.7 mm² 及總功率消耗限制在24.1 mW 之下 (由一個 1.5 V 的電源供給)。

## **ACKNOWLEDGMENT**

I would like to express my sincere gratitude to my supervisor, Prof. Cheng Kwok-Keung, for his patience, graceful guidance and high degree of freedom on my research work.

I want to thank Mr. Yeung Wing-Yee, the technician of VLSI/ASIC Design Laboratory, for his assistance in submission for IC fabrication and technical support of the IC design software. Special thanks also go to Fung Yun-Ming, the technician of Microwave and Wireless Communications Laboratory, for his help in conducing experiments.

I extend my thanks to my colleagues Au Yeung Chung-Fai, Tang Siu-Kei and Wong Fai-Leung for their generous technical discussions. I also wish to thank Pedro Cheong, Candy Fok, Dr. Ken Tam and Dr. Welsy Choi for their support in overcoming my financial difficulty after the normative study period.

Finally, I would like to thank my parents for their love and encouragement throughout my study.

## **CONTENTS**

| ABSTRACT        |                                 | ii    |

|-----------------|---------------------------------|-------|

| ACKNOWLEDGM     | TENT                            | vi    |

| ΓABLE OF CONT   | ENTS                            | vii   |

| LIST OF FIGURES | S                               | xi    |

| LIST OF TABLES  |                                 | xviii |

| LIST OF ABBREV  | VIATIONS                        | xix   |

| LIST OF SYMBOI  | LS                              | xxii  |

| CHAPTER 1 IN    | TRODUCTION                      | 1     |

| 1.1 Motivati    | on                              | 1     |

| 1.2 Thesis O    | Organization                    | 4     |

| CHAPTER 2 FR    | REQUENCY SYNTHESIZER BACKGROUND | 6     |

| 2.1 General     | Considerations                  | 6     |

| 2.1.1           | Frequency Accuracy              | 6     |

| 2.1.2           | Frequency Resolution            | 7     |

| 2.1.3           | Phase Noise                     | 7     |

| 2.1.4           | Spurious Signals                | 9     |

| 2.1.5           | Switching Time                  | 10    |

|                 |                                 |       |

|       | 2.1.6     | Power Dissipation                                                       | 11 |

|-------|-----------|-------------------------------------------------------------------------|----|

|       | 2.1.7     | Integration Level                                                       | 12 |

|       | 2.1.8     | Sensitivity to Interference                                             | 12 |

| 2.2   | Integer-1 | N Phase-Locked Loop                                                     | 13 |

| 2.3   | Architec  | tures for Fractional Frequency Synthesis                                | 15 |

|       | 2.3.1     | Direct Digital Frequency Synthesizer                                    | 15 |

|       | 2.3.2     | Fractional-N Phase-Locked Loop                                          | 19 |

|       | 2.3.3     | Dual-Loop Frequency Synthesizer                                         | 23 |

|       | 2.3.4     | Frequency Synthesizer with Truly Modular Fractional Frequency Divider   | 27 |

|       | 2.3.5     | Frequency Synthesizer with Regenerative Frequency Divider               | 30 |

|       | 2.3.6     | Frequency Synthesizer with Phase-Switching Fractional Frequency Divider | 32 |

|       | 2.3.7     | Heterodyne Phase-Locked Loop                                            | 35 |

|       | 2.3.8     | Summary                                                                 | 37 |

| Снарт | ER 3 F    | REQUENCY SYNTHESIZER SYSTEM DESIGN                                      | 39 |

| 3.1   | Frequen   | cy Synthesizer Architecture Description                                 | 39 |

| 3.2   | Frequen   | cy Synthesizer Behavior Simulations                                     | 43 |

|       | 3.2.1     | Linear Model Description                                                | 43 |

|       | 3.2.2     | Stability Analysis                                                      | 45 |

|       | 3.2.3     | Phase Noise Contribution                                                | 52 |

|       | 3.2.4     | Settling Time                                                           | 59 |

|       | 3.2.5     | Summary of Design Parameters and System Performances                    | 61 |

| 3.3   | Frequen   | cy Synthesizer Spurious Tone Analysis                                   | 62 |

|       | 3.3.1     | Spur Generation Mechanism                                               | 62 |

|       | 3.3.2     | Spurs due to Reference Feedthrough                                      | 64 |

|       | 3.3.3     | Spurs due to Phase Mismatch in Phase Switching                          | 68 |

| Снарт |           | ROPOSED PROGRAMMABLE FRACTIONAL FREQUENCY                               |    |

|       | D         | IVIDER                                                                  | 75 |

| 4.1   | Architec  | cture Description                                                       | 75 |

| 4.2    | Dual Div | vide-by-4 Injection-Locked Frequency Divider  | 78  |

|--------|----------|-----------------------------------------------|-----|

|        | 4.2.1    | Cross-Coupling Design                         | 79  |

|        | 4.2.2    | Coherent-Coupling Design                      | 91  |

| 4.3    | Multiple | xer                                           | 101 |

| 4.4    | Phase-S  | witching Control Circuitry                    | 104 |

| 4.5    | TSPC D   | ivide-by-64 Ripple Counter                    | 107 |

| Снарті | ER 5 CI  | RCUIT IMPLEMENTATION OF OTHER BUILDING BLOCKS | 110 |

| 5.1    | Quadrat  | ure LC Voltage-Controlled Oscillator          | 110 |

| 5.2    | Phase Fr | requency Detector                             | 115 |

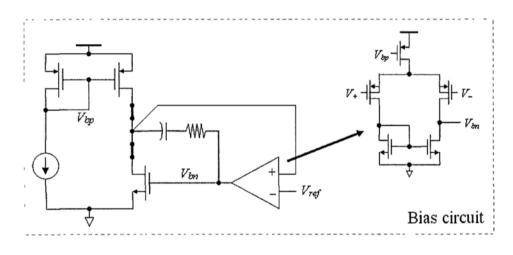

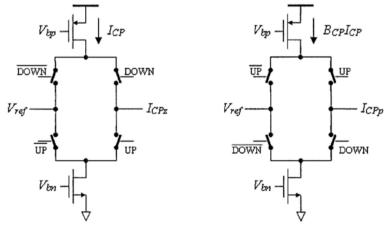

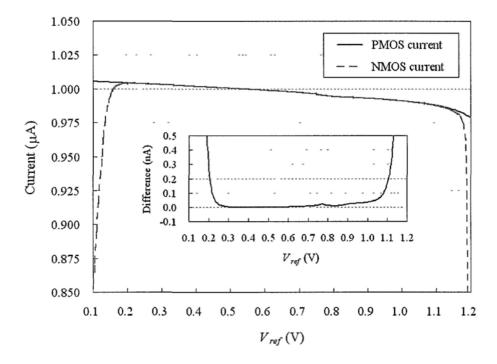

| 5.3    | Charge l | Pump                                          | 118 |

| 5.4    | Loop Fil | lter                                          | 121 |

| Снарт  | er 6 Ex  | KPERIMENTAL RESULTS                           | 125 |

| 6.1    | IC Fabri | cation and Measurement Setup                  | 125 |

| 6.2    | Quadrat  | ure LC Voltage-Controlled Oscillator          | 128 |

|        | 6.2.1    | Frequency Tuning Range                        | 129 |

|        | 6.2.2    | Phase Noise                                   | 131 |

| 6.3    | Dual Di  | vide-by-4 Injection-Locked Frequency Dividers | 132 |

|        | 6.3.1    | Locking Range                                 | 133 |

|        | 6.3.2    | Phase Noise                                   | 134 |

| 6.4    | Program  | mable Fractional Frequency Dividers           | 136 |

|        | 6.4.1    | Locking Range                                 | 136 |

|        | 6.4.2    | Phase Noise                                   | 139 |

| 6.5    | Propose  | d Frequency Synthesizer – Design 1            | 142 |

|        | 6.5.1    | Spurious Tone Performance                     | 142 |

|        | 6.5.2    | Phase Noise                                   | 144 |

|        | 6.5.3    | Settling Time                                 | 144 |

|        | 6.5.4    | Quadrature Accuracy                           | 147 |

| 6.6    | Propose  | d Frequency Synthesizer – Design 2            | 148 |

|        | 6.6.1    | Spurious Tone Performance                     | 149 |

|        | 6.6.2    | Phase Noise                                   | 150 |

|        | 6.6.3 Settling Time                                   | 152 |

|--------|-------------------------------------------------------|-----|

|        | 6.6.4 Quadrature Accuracy                             | 152 |

| 6.7    | Measurement Result Summary and Performance Comparison | 155 |

| Спурт  | PER 7 CONCLUSION                                      | 157 |

|        |                                                       |     |

| 7.1    | Concluding Remark                                     | 157 |

| 7.2    | Recommendation for Future Work                        | 159 |

| Appeni | DIX A PROCESS PARAMETERS OF THE CHOSEN 0.35 μM CMOS   |     |

|        | PROCESS                                               | 161 |

| A.1    | Key Features                                          | 161 |

| A.2    | Wafer Cross-Section                                   | 162 |

| A.3    | Basic Design Rules                                    | 163 |

| A.4    | Device Parameters                                     | 164 |

|        | A.4.1 Active Devices                                  | 164 |

|        | A.4.2 Passive Devices                                 | 165 |

| Appeni | DIX B GENERALIZED DUAL DIVIDE-BY-4 INJECTION-LOCKED   |     |

|        | FREQUENCY DIVIDER BEHAVIOR MODEL                      | 167 |

| AUTHO  | DR'S PUBLICATION LIST                                 | 175 |

| Referi | ENCES                                                 | 176 |

## LIST OF FIGURES

| Figure 2.1  | Influence of phase noise in a transmitter                                                     | 8  |

|-------------|-----------------------------------------------------------------------------------------------|----|

| Figure 2.2  | Influence of phase noise in a receiver                                                        | 9  |

| Figure 2.3  | Influence of spurious signals in a receiver                                                   | 10 |

| Figure 2.4  | Block diagram of an integer-N phase-locked loop                                               | 13 |

| Figure 2.5  | Block diagram of a sine-output direct digital frequency synthesizer                           | 16 |

| Figure 2.6  | Block diagram of a fractional-N phase-locked loop                                             | 20 |

| Figure 2.7  | Architectures of third-order $\Delta\Sigma$ modulators a) MASH and b) single loop             | 22 |

| Figure 2.8  | Architecture of a parallel configuration dual-loop frequency synthesizer                      | 24 |

| Figure 2.9  | Architecture of a parallel configuration dual-loop frequency synthesizer using vernier effect | 25 |

| Figure 2.10 | Architecture of a series configuration dual-loop frequency synthesizer at 900 MHz             | 26 |

| Figure 2.11 | Architecture of a series configuration dual-loop frequency synthesizer at 1.8 GHz             | 26 |

| Figure 2.12 | Example of a divide-by-5.5 static frequency divider                                           | 28 |

| Figure 2.13 | Example of a divide-by-1/1.5 dual-modulus static frequency divider                            | 29 |

| Figure 2.14 | Miller frequency divider with fractional division ratio                                       | 31 |

| Figure 2.15 | Modified Miller frequency divider                                                             | 32 |

| Figure 2.16 | Architecture of a phase-switching frequency divider                                                                         | 33 |

|-------------|-----------------------------------------------------------------------------------------------------------------------------|----|

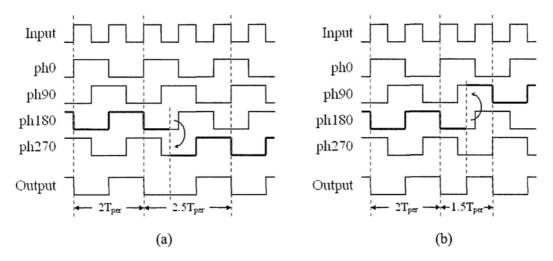

| Figure 2.17 | Illustration of the phase switching operation with a) forward phase selection scheme and b) backward phase selection scheme | 34 |

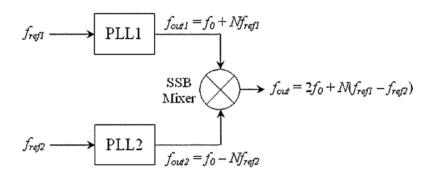

| Figure 2.18 | Architecture of a heterodyne phase-locked loop                                                                              | 36 |

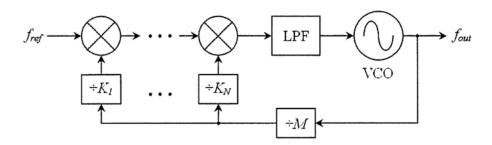

| Figure 3.1  | Architecture of the proposed phase-locked loop                                                                              | 40 |

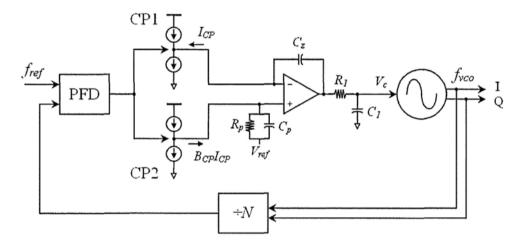

| Figure 3.2  | Dual-path loop filter principle                                                                                             | 41 |

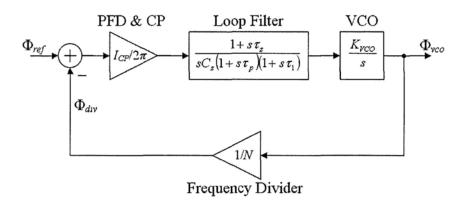

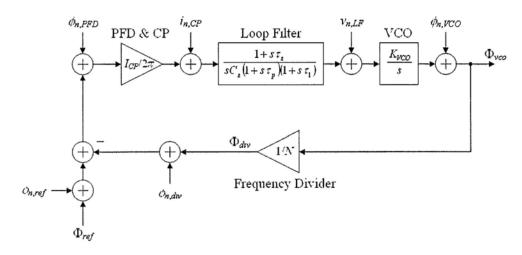

| Figure 3.3  | Linear model of the proposed PLL                                                                                            | 44 |

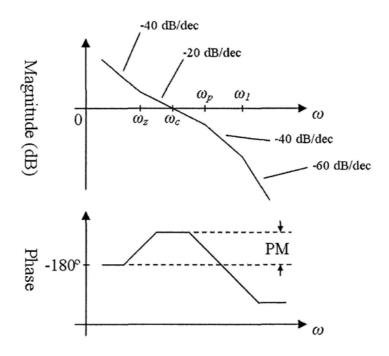

| Figure 3.4  | Bode plot of the PLL system with asymptotic approximation                                                                   | 46 |

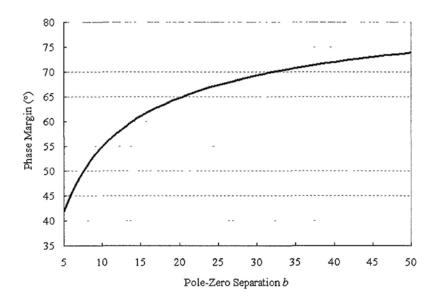

| Figure 3.5  | Relationship between the phase margin and pole-zero separation                                                              | 49 |

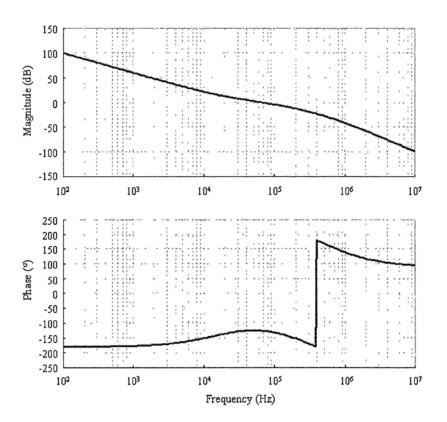

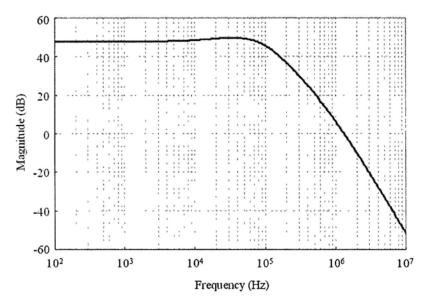

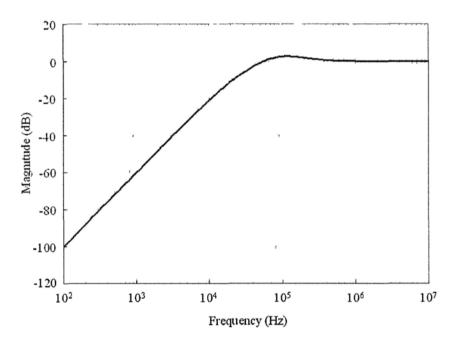

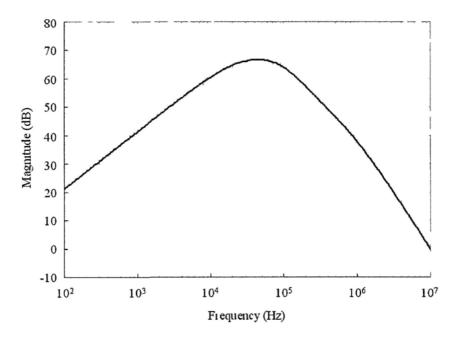

| Figure 3.6  | Open loop transfer characteristic of the PLL system                                                                         | 51 |

| Figure 3.7  | Closed loop transfer characteristic of the PLL system                                                                       | 51 |

| Figure 3.8  | Noise model of the PLL system                                                                                               | 52 |

| Figure 3.9  | Noise transfer function for the VCO noise source                                                                            | 53 |

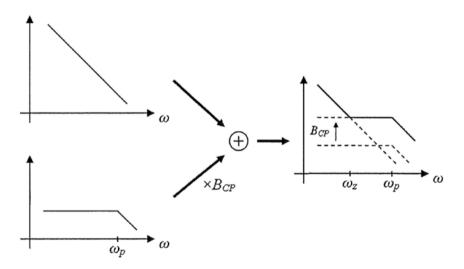

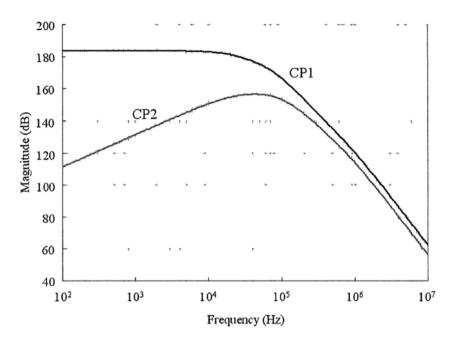

| Figure 3.10 | Noise transfer functions for the charge pump noise sources                                                                  | 55 |

| Figure 3.11 | Noise transfer function for the equivalent noise source of the amplifier in the loop filter                                 | 57 |

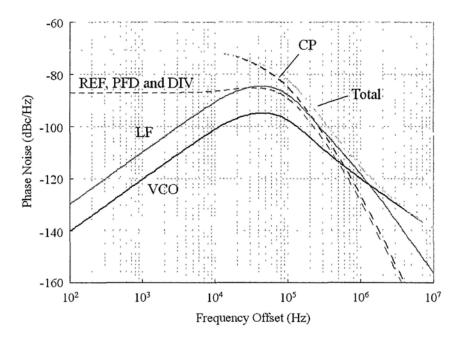

| Figure 3.12 | Estimated overall PLL phase noise and contribution of each component at the PLL output                                      | 59 |

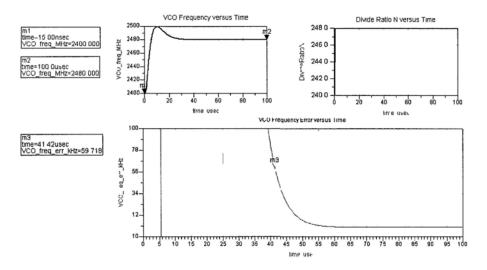

| Figure 3.13 | Settling time simulation result                                                                                             | 61 |

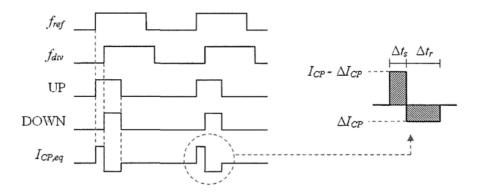

| Figure 3.14 | Effect of charge pump current mismatch in PLL steady state condition                                                        | 65 |

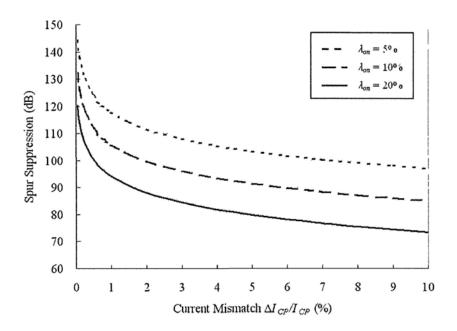

| Figure 3.15 | Spurious tone performance under the influences of charge pump current mismatch and turn-on duty cycle                       | 68 |

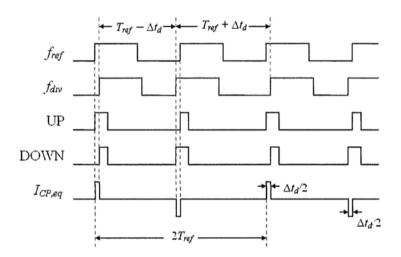

| Figure 3.16 | Effect of phase mismatch in phase switching of the frequency divider                                                        | 70 |

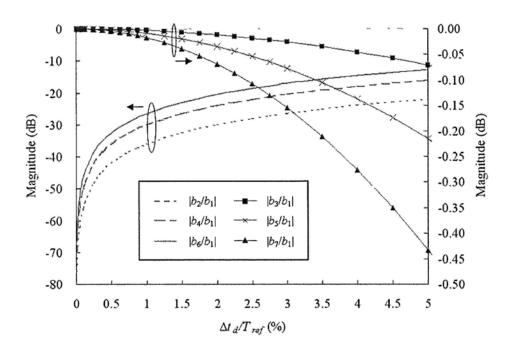

| Figure 3.17 | Influence of phase offset in spurious component magnitudes                                                                  | 72 |

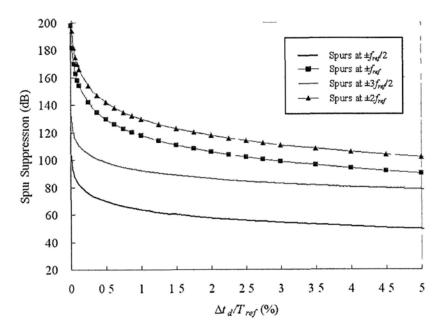

| Figure 3.18 | Spurious tone performance under the influence of phase mismatch                                                                             |    |

|-------------|---------------------------------------------------------------------------------------------------------------------------------------------|----|

|             | in phase switching                                                                                                                          | 74 |

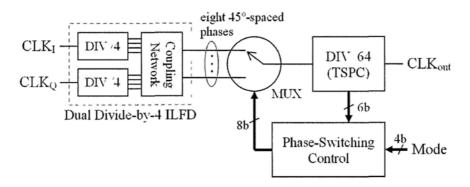

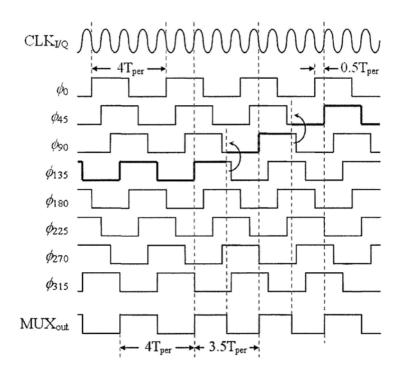

| Figure 4.1  | Architecture of the programmable fractional frequency divider                                                                               | 76 |

| Figure 4.2  | Illustration of fractional division by the phase-switching operation                                                                        | 77 |

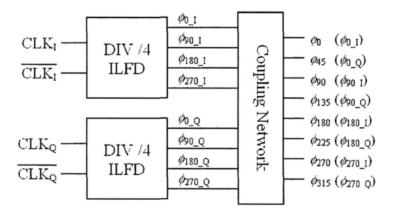

| Figure 4.3  | Block diagram of the dual divide-by-4 ILFD                                                                                                  | 78 |

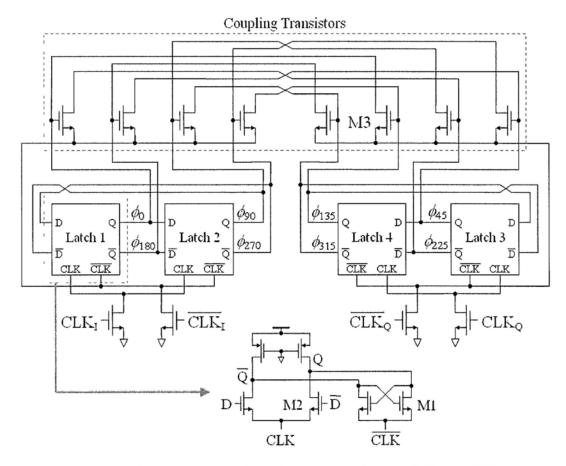

| Figure 4.4  | Schematic of the quadrature-input cross-coupling dual divide-by-4 ILFD                                                                      | 80 |

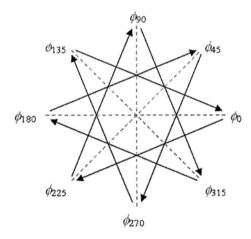

| Figure 4.5  | Coupling sequence of the quadrature-input cross-coupling dual divide-by-4 ILFD                                                              | 81 |

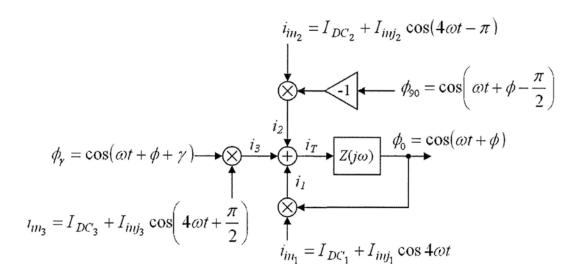

| Figure 4.6  | Behavior model of the quadrature-input cross-coupling dual divide-by-4 ILFD                                                                 | 82 |

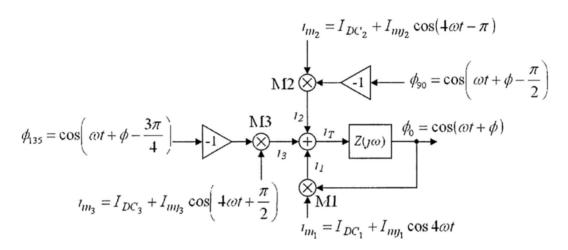

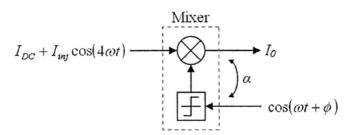

| Figure 4.7  | Mixer operation with a DC and a quadruple frequency sinusoidal input current                                                                | 83 |

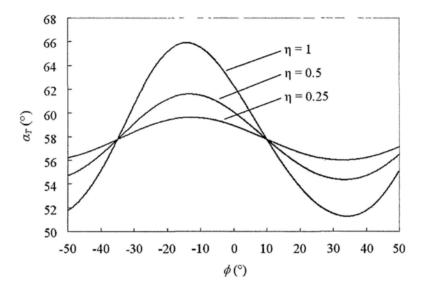

| Figure 4.8  | Resultant mixer output phase response versus divider output phase for various injection ratios                                              | 88 |

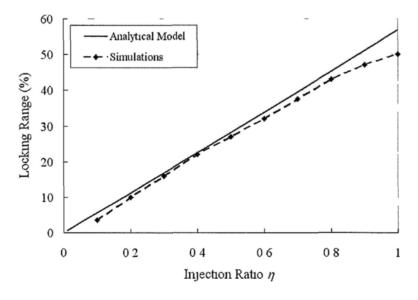

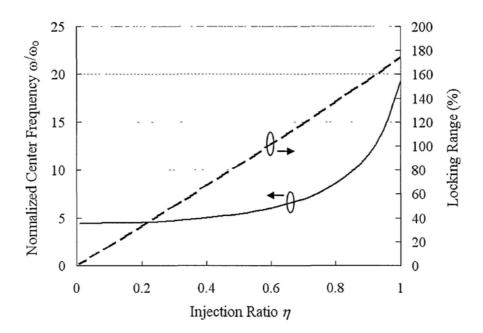

| Figure 4.9  | Calculated and simulated locking range of the cross-coupling dual divide-by-4 ILFD                                                          | 88 |

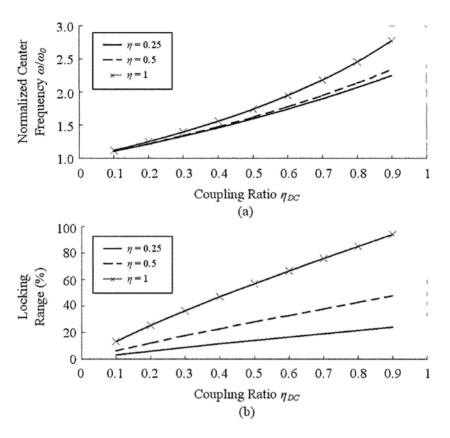

| Figure 4.10 | Influence of coupling strength on (a) divider output center frequency (normalized) and (b) locking range, for different injection ratios    | 90 |

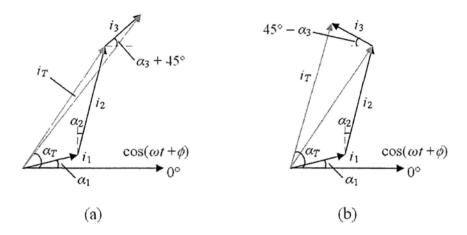

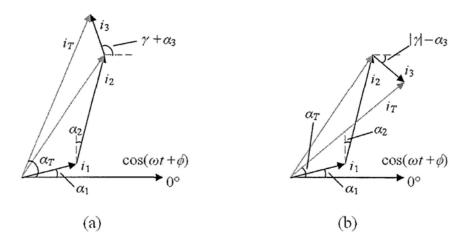

| Figure 4.11 | Phasor diagram of the resultant mixer output current and output voltage for (a) the desired phase pattern and (b) the reverse phase pattern | 91 |

| Figure 4.12 | Schematic of the quadrature-input coherent-coupling dual divide-<br>by-4 ILFD                                                               | 92 |

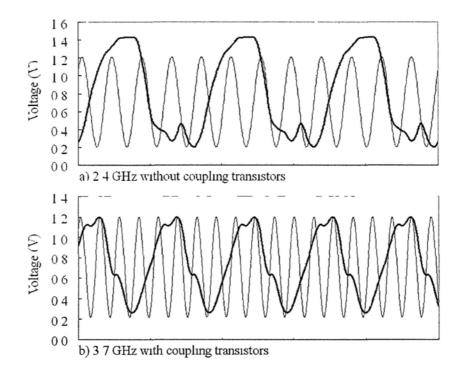

| Figure 4.13 | Simulation result comparison of the divide-by-4 ILFD output with and without coupling transistors                                           | 94 |

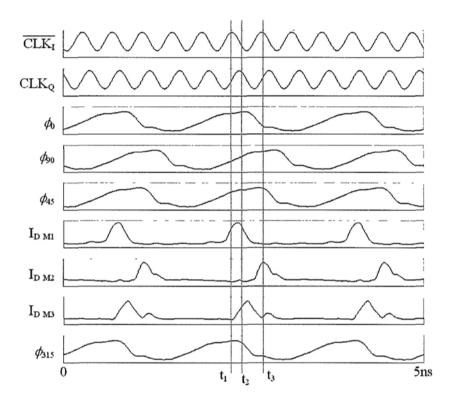

| Figure 4.14 | Simulation result of the operation principle of the quadrature-input coherent-coupling dual divide-by-4 ILFD                                                            | 95  |

|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

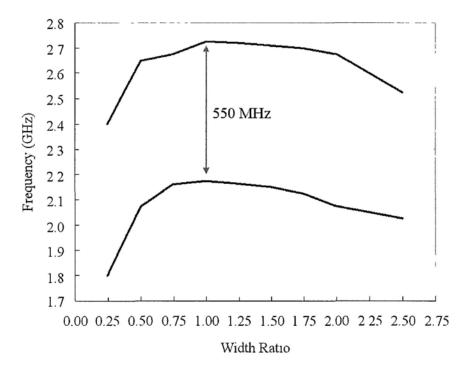

| Figure 4.15 | Simulation result of the operation frequency range of the quadrature-input coherent-coupling dual divide-by-4 ILFD versus coupling transistor size                      | 96  |

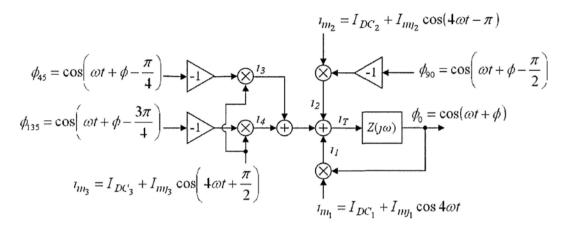

| Figure 4.16 | Behavior model of the quadrature-input coherent-coupling dual divide-by-4 ILFD                                                                                          | 97  |

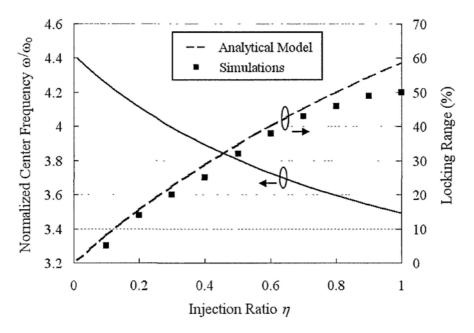

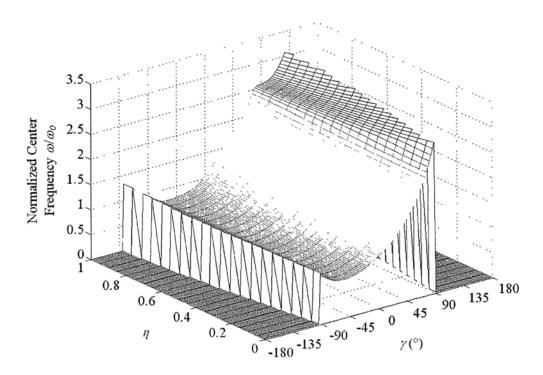

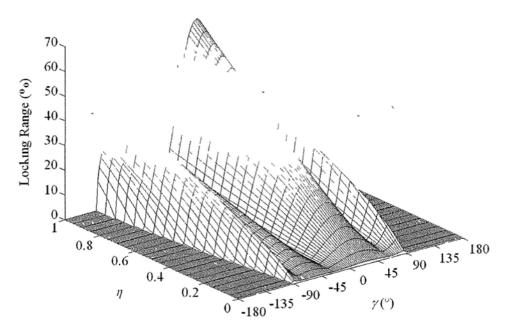

| Figure 4.17 | Normalized center frequency and locking range for various injection ratios                                                                                              | 100 |

| Figure 4.18 | Normalized center frequency and locking range versus injection ratio with simulation result comparison for the quadrature-input coherent-coupling dual divide-by-4 ILFD | 101 |

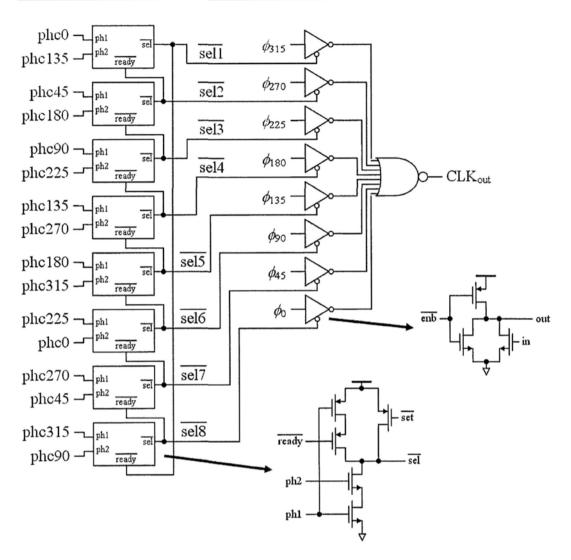

| Figure 4.19 | Schematic of the multiplexer                                                                                                                                            | 102 |

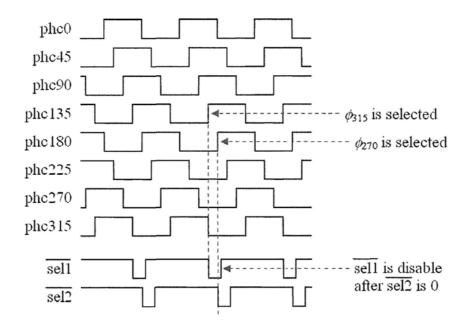

| Figure 4.20 | Timing diagram of phase selection                                                                                                                                       | 104 |

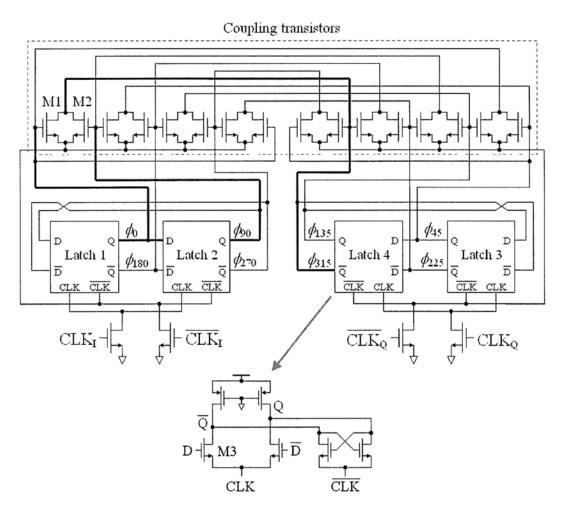

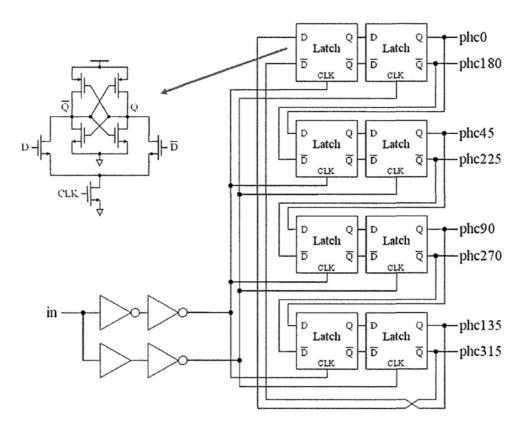

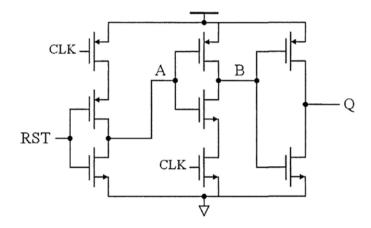

| Figure 4.21 | Schematic of the shift register in the phase-switching control circuitry                                                                                                | 105 |

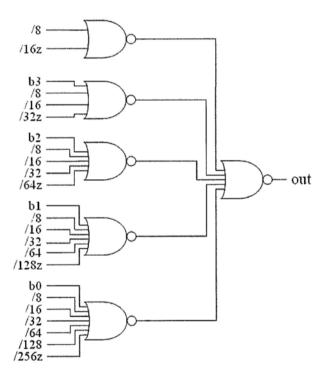

| Figure 4.22 | Schematic of the combinational logic in the phase-switching control circuitry                                                                                           | 106 |

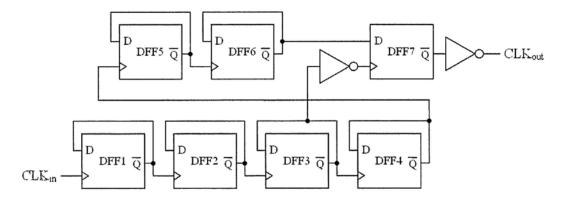

| Figure 4.23 | Schematic of the TSPC divide-by-64 ripple counter                                                                                                                       | 107 |

| Figure 4.24 | Schematic of the TSPC D-flip-flop used in the divide-by-64 ripple                                                                                                       |     |

|             | counter                                                                                                                                                                 | 109 |

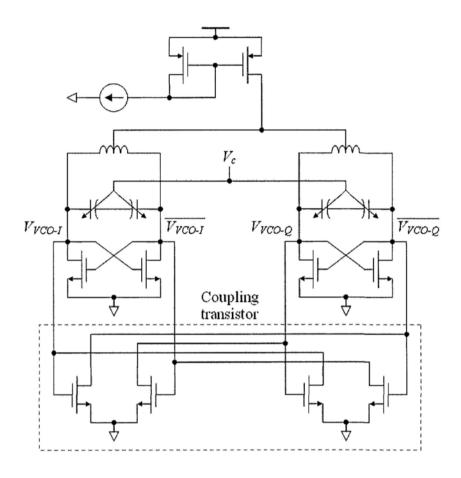

| Figure 5.1  | Schematic of the quadrature VCO                                                                                                                                         | 111 |

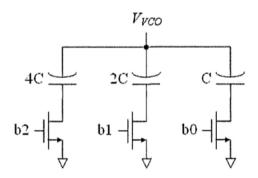

| Figure 5.2  | Schematic of the switched capacitor array                                                                                                                               | 113 |

| Figure 5.3  | Layout of donut transistor                                                                                                                                              | 114 |

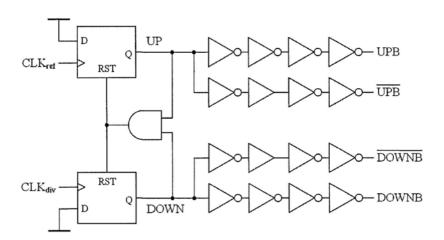

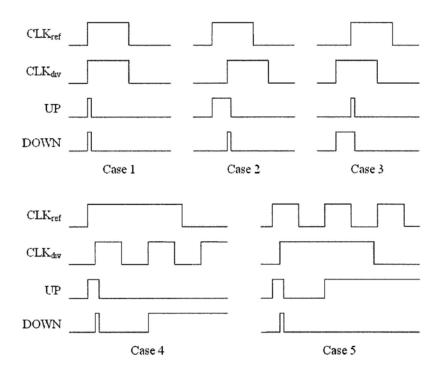

| Figure 5.4  | Schematic of the phase frequency detector                                                                                                                               | 115 |

| Figure 5.5  | Timing diagram of the PFD operation                                                                                                                                     | 116 |

| Figure 5.6  | Schematic of the D-latch in the PFD                                                                                                                                     | 118 |

|             |                                                                                                                                                                         |     |

| Figure 5.7  | Schematic of the charge pumps                                                                                                            | 119 |

|-------------|------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Figure 5.8  | Simulated current matching characteristic of the charge pump                                                                             | 121 |

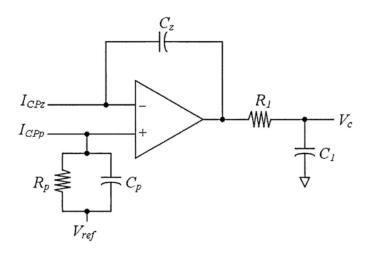

| Figure 5.9  | Schematic of the loop filter                                                                                                             | 122 |

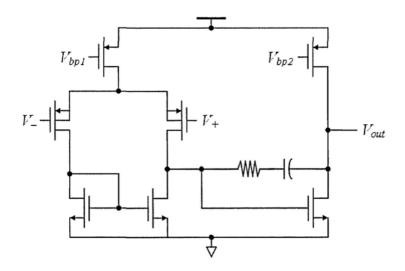

| Figure 5.10 | Schematic of the opamp in the loop filter                                                                                                | 124 |

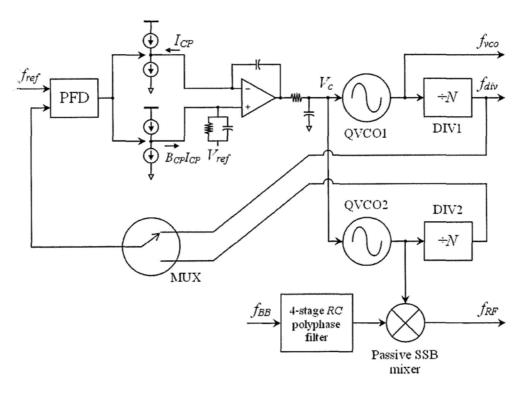

| Figure 6.1  | Overall architecture of the frequency synthesizer for IC fabrication                                                                     | 126 |

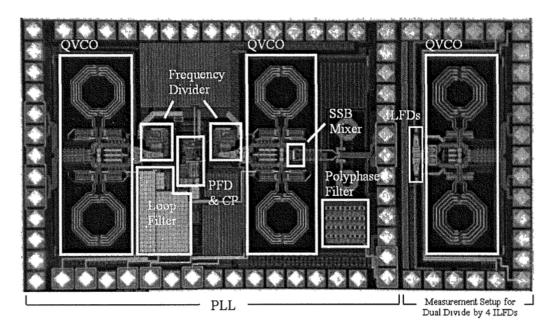

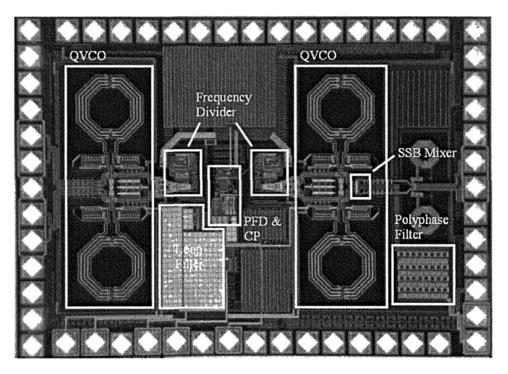

| Figure 6.2  | Die photo of the proposed frequency synthesizer (Design 1) and the measurement setup for the dual divide-by-4 ILFDs                      | 127 |

| Figure 6.3  | Die photo of the proposed frequency synthesizer (Design 2)                                                                               | 128 |

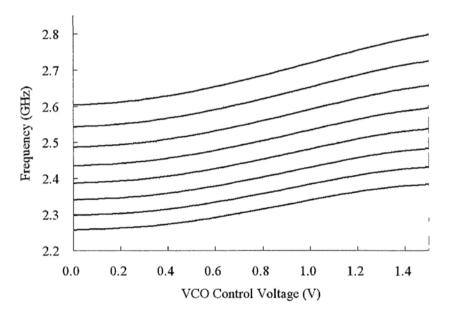

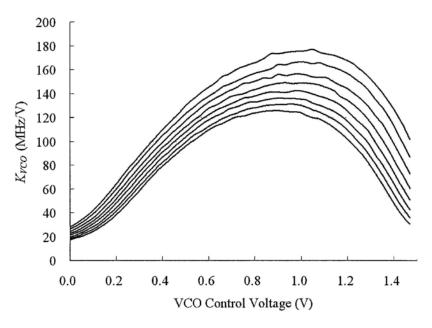

| Figure 6.4  | Measured frequency tuning range of the quadrature VCO                                                                                    | 129 |

| Figure 6.5  | Measured VCO gain of the quadrature VCO                                                                                                  | 130 |

| Figure 6.6  | Measured output spectrum of the quadrature VCO                                                                                           | 130 |

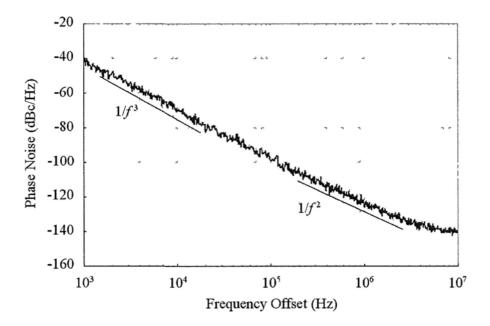

| Figure 6.7  | Phase noise measurement of the quadrature VCO                                                                                            | 131 |

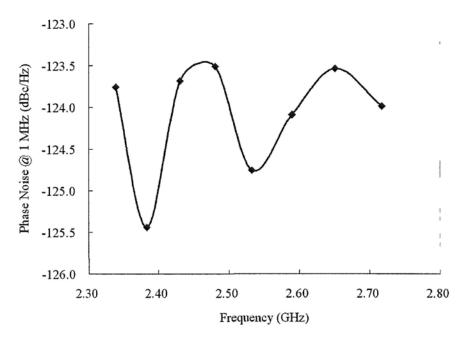

| Figure 6.8  | Measured phase noise at 1 MHz frequency offset of the quadrature VCO                                                                     | 132 |

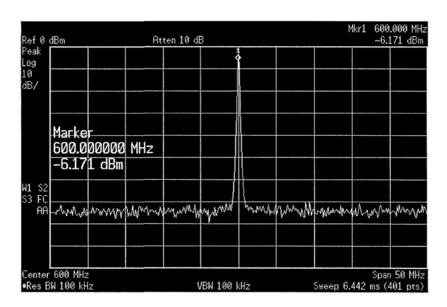

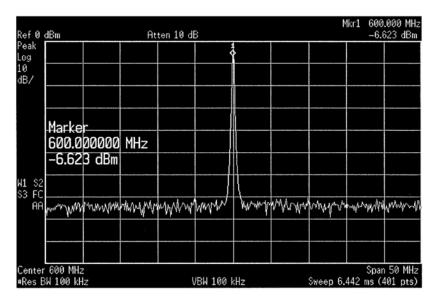

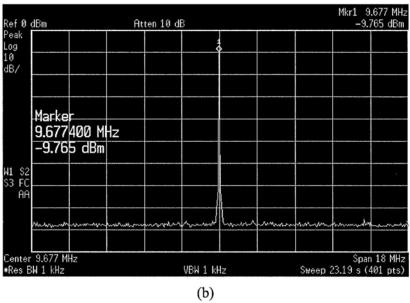

| Figure 6.9  | Measured output spectrum of the cross-coupling dual divider-by-4 ILFD                                                                    | 133 |

| Figure 6.10 | Measured output spectrum of the coherent-coupling dual divider-<br>by-4 ILFD                                                             | 134 |

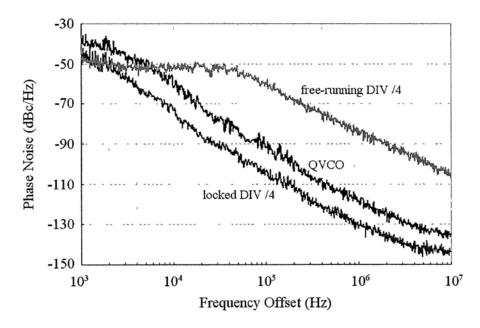

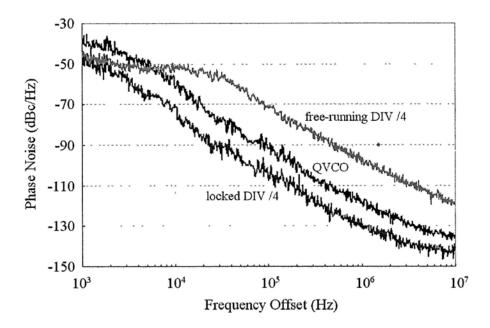

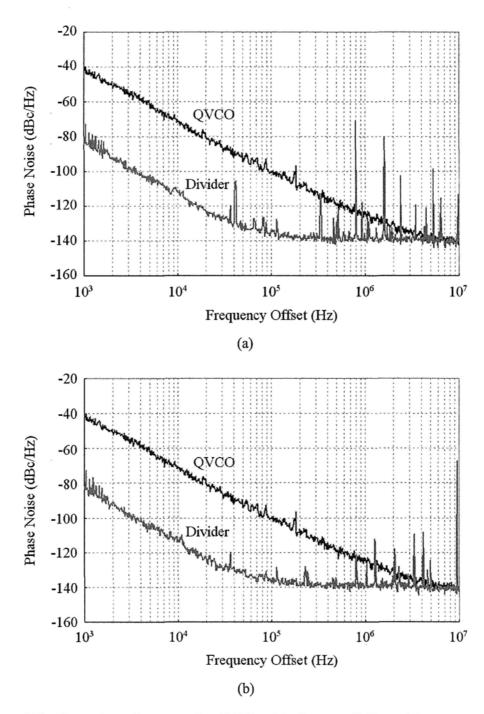

| Figure 6.11 | Phase noise performances of the QVCO and the cross-coupling dual divider-by-4 ILFD                                                       | 135 |

| Figure 6.12 | Phase noise performances of the QVCO and the coherent-coupling dual divider-by-4 ILFD                                                    | 135 |

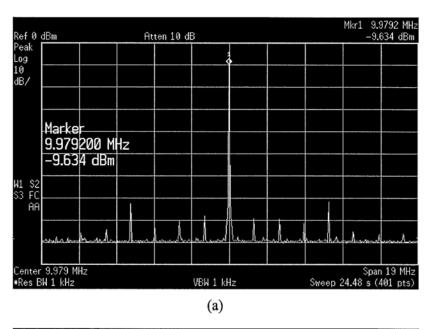

| Figure 6.13 | Measured output spectrum of the frequency divider with the cross-<br>coupling dual divide-by-4 ILFD for division ratios of (a) 240.5 and |     |

|             | (b) 248                                                                                                                                  | 137 |

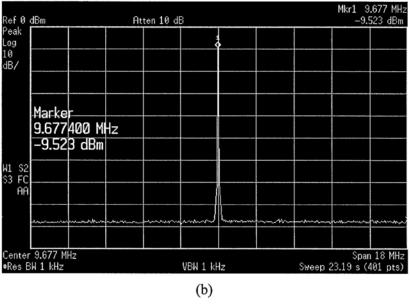

| Figure 6.14 | Measured output spectrum of the frequency divider with the coherent-coupling dual divide-by-4 ILFD for division ratios of (a) 240.5 and (b) 248              | 138 |

|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

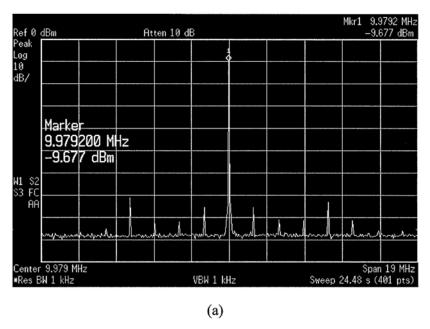

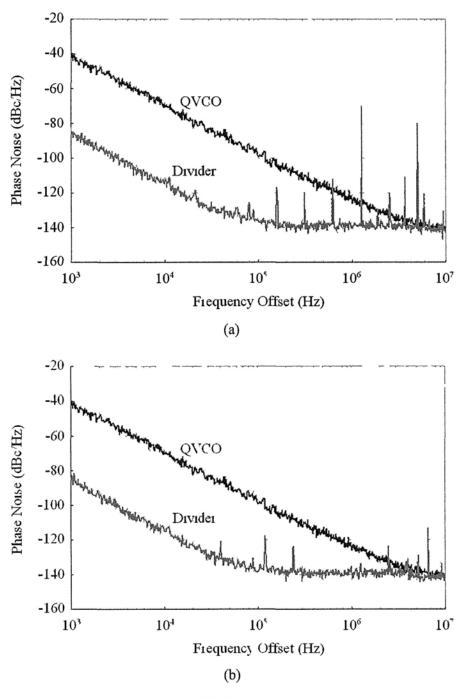

| Figure 6.15 | Phase noise performances of the QVCO and the frequency divider with the cross-coupling dual divide-by-4 ILFD for division ratios of (a) 240.5 and (b) 248    | 140 |

| Figure 6.16 | Phase noise performances of the QVCO and the frequency divider with the coherent-coupling dual divide-by-4 ILFD for division ratios of (a) 240.5 and (b) 248 | 141 |

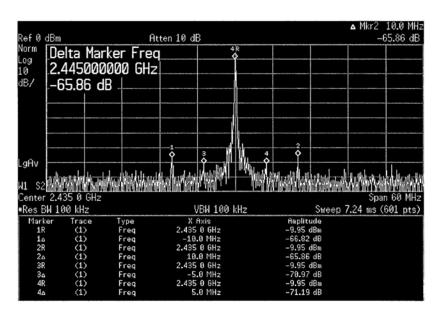

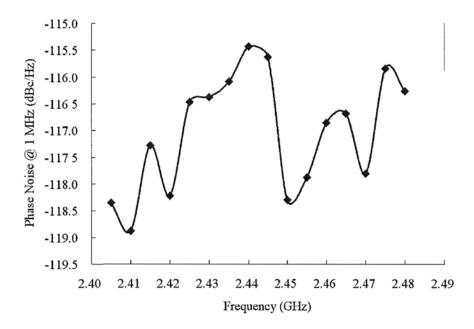

| Figure 6.17 | Measured output spectrum of the proposed frequency synthesizer – design 1                                                                                    | 143 |

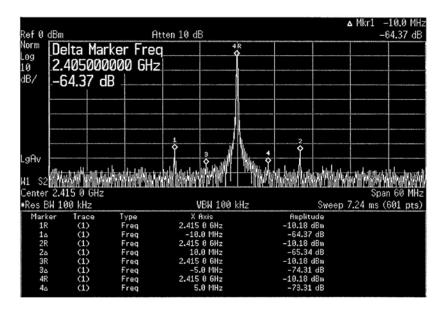

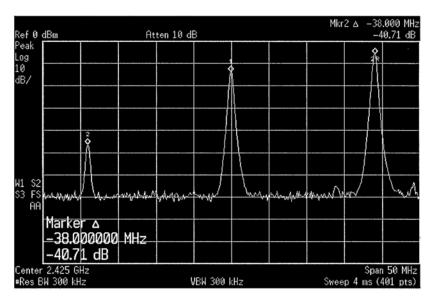

| Figure 6.18 | Measured reference spur performance of the proposed frequency synthesizer – design 1                                                                         | 143 |

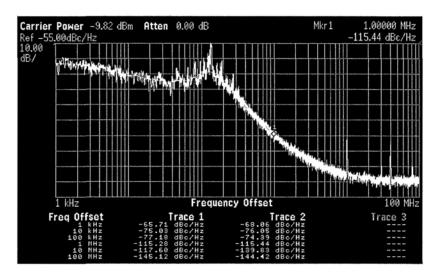

| Figure 6.19 | Phase noise measurement of the proposed frequency synthesizer – design 1                                                                                     | 145 |

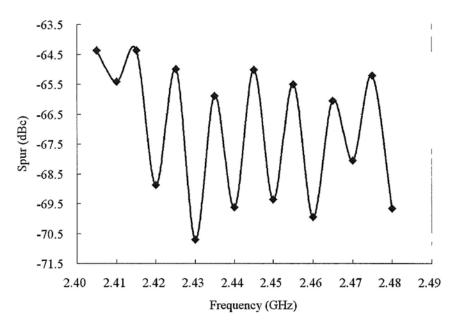

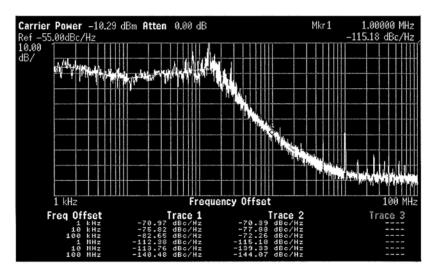

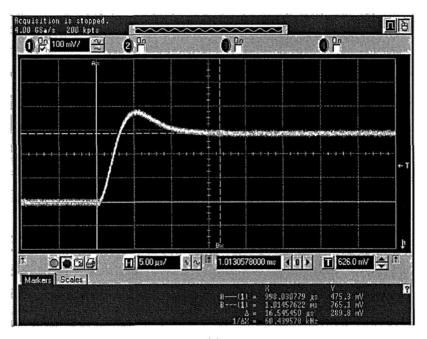

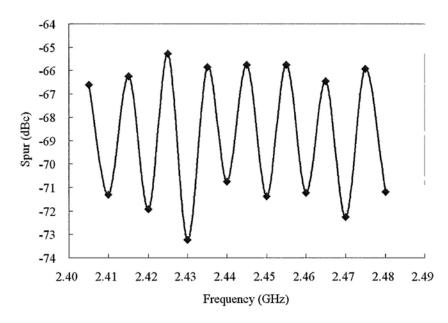

| Figure 6.20 | Measured phase noise at 1 MHz frequency offset of the proposed frequency synthesizer – design 1                                                              | 145 |

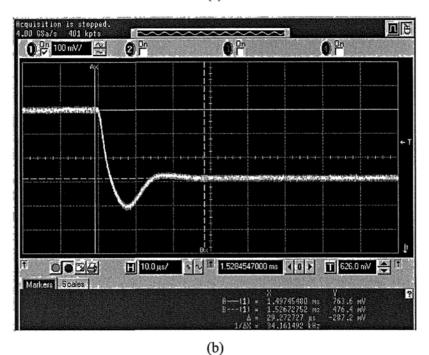

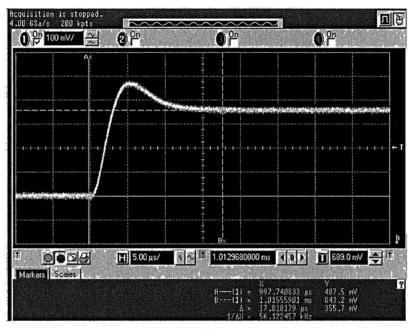

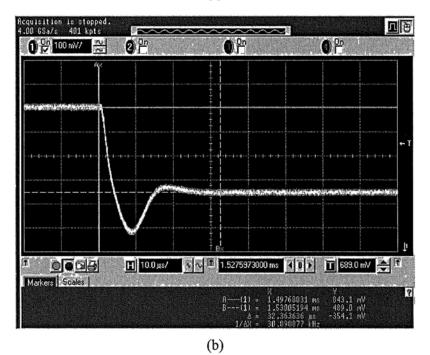

| Figure 6.21 | Settling time measurement of the proposed frequency synthesizer – design 1 (a) from 2.405 GHz to 2.48 GHz and (b) from 2.48 GHz to 2.405 GHz                 | 146 |

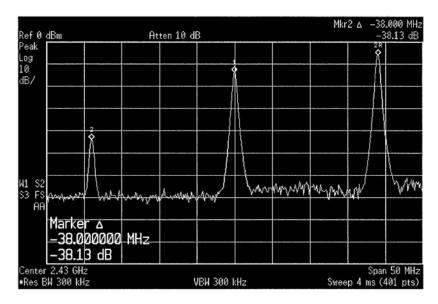

| Figure 6.22 | Measured sideband rejection of the proposed frequency synthesizer – design 1                                                                                 | 147 |

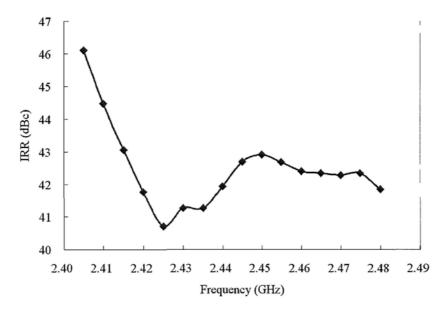

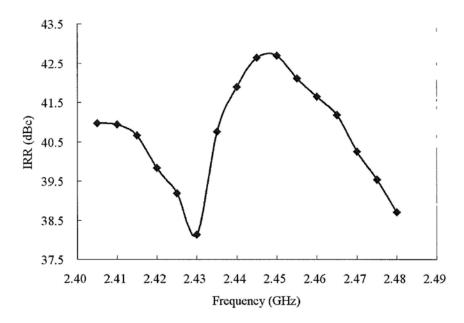

| Figure 6.23 | Image rejection measurement of the proposed frequency synthesizer – design 1                                                                                 | 148 |

| Figure 6.24 | Measured output spectrum of the proposed frequency synthesizer – design 2                                                                                    | 149 |

| Figure 6.25 | Measured reference spur performance of the proposed frequency synthesizer – design 2                                                                         | 150 |

| Figure 6.26 | Phase noise measurement of the proposed frequency synthesizer – design 2                                                                     | 151 |

|-------------|----------------------------------------------------------------------------------------------------------------------------------------------|-----|

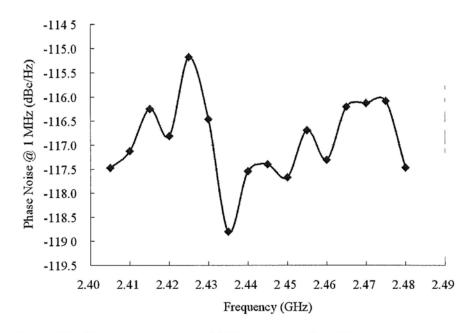

| Figure 6.27 | Measured phase noise at 1 MHz frequency offset of the proposed frequency synthesizer – design 2                                              | 151 |

| Figure 6.28 | Settling time measurement of the proposed frequency synthesizer – design 2 (a) from 2.405 GHz to 2.48 GHz and (b) from 2.48 GHz to 2.405 GHz | 153 |

| Figure 6.29 | Measured sideband rejection of the proposed frequency synthesizer – design 2                                                                 | 154 |

| Figure 6.30 | Image rejection measurement of the proposed frequency synthesizer – design 2                                                                 | 154 |

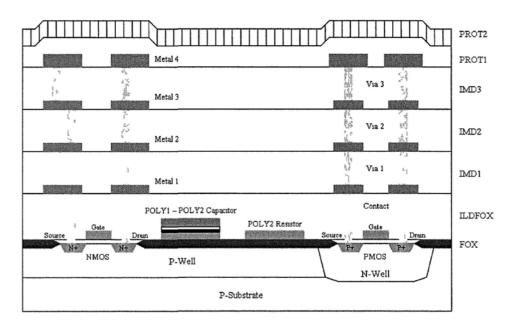

| Figure A.1  | Wafer cross-section of the chosen 0.35 $\mu m$ CMOS process                                                                                  | 162 |

| Figure B.1  | Generalized dual divide-by-4 injection-locked frequency divider behavior model                                                               | 168 |

| Figure B.2  | Normalized center frequency with respect to $\eta$ and $\gamma$                                                                              | 171 |

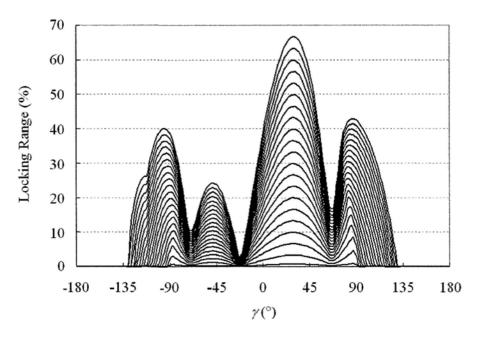

| Figure B.3  | Locking range with respect to $\eta$ and $\gamma$                                                                                            | 172 |

| Figure B.4  | Phasor diagram of the resultant mixer output current and output                                                                              |     |

|             | voltage for (a) positive $\gamma$ and (b) negative $\gamma$                                                                                  | 173 |

| Figure B.5  | Locking range versus $\gamma$ under the influence of $\eta$                                                                                  | 173 |

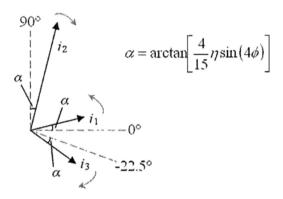

| Figure B.6  | Phasor diagram of the current components for $\gamma$ = -22.5°                                                                               | 174 |

## LIST OF TABLES

| Table 1.1 | IEEE 802.11a/b/g WLAN standards                             | 2   |

|-----------|-------------------------------------------------------------|-----|

| Table 2.1 | Summary of fractional frequency synthesis architectures     | 38  |

| Table 3.1 | Component values of the loop filter elements                | 50  |

| Table 3.2 | Component parameters of the proposed PLL                    | 61  |

| Table 3.3 | Performance summary of the proposed PLL                     | 62  |

| Table 5.1 | Component parameters of the loop filter                     | 122 |

| Table 6.1 | Performance comparison of the fractional frequency dividers | 155 |

| Table 6.2 | Measurement result summary of the proposed frequency        |     |

|           | synthesizers and comparison with other published works      | 156 |

| Table A.1 | Basic design rules of the chosen 0.35 $\mu m$ CMOS process  | 163 |

| Table A.2 | Device parameters of MOS transistors                        | 164 |

| Table A.3 | Device parameters of bipolar transistors                    | 164 |

| Table A.4 | Device parameters of poly capacitor                         | 165 |

| Table A.5 | Device parameters of resistors                              | 165 |

| Table A.6 | Device parameters of MOS varactor                           | 166 |

| Table A.7 | Device parameters of spiral inductors                       | 166 |

## LIST OF ABBREVIATIONS

$\Delta\Sigma$  Delta-Sigma

BER Bit Error Rate

BPF Bandpass Filter

CCK Complementary Code Keying

CMOS Complementary Metal-Oxide Semiconductor

CORDIC Coordinate Rotational Digital Computation

CP Charge Pump

DAC Digital-to-Analog Converter

DCS Digital Cellular System

DDFS Direct Digital Frequency Synthesizer

FCW Frequency Control Word

FM Frequency Modulation

FOM Figure of Merit

GSM Global System for Mobile Communication

IC Integrated Circuit

ICI Inter-Carrier Interference

IF Intermediate Frequency

ILFD Injection-Locked Frequency Divider

IQ In-phase and Quadrature-phase

IRR Image Rejection Ratio

ISM Industrial, Scientific and Medical

LO Local Oscillator

LPF Lowpass Filter

LSB Least Significant Bit

MASH Multi-Stage Noise Shaping

MB-OFDM Multi-Band Orthogonal Frequency Division Multiplexing

MIM Metal-Insulator-Metal

MOS Metal-Oxide Semiconductor

MSB Most Significant Bit

NTF Noise Transfer Function

OFDM Orthogonal Frequency Division Multiplexing

PA Power Amplifier

PCB Printed Circuit Board

PFD Phase Frequency Detector

PLL Phase-Locked Loop

PM Phase Margin

ppm Parts Per Million

QAM Quadrature Amplitude Modulation

QVCO Quadrature Voltage-Controlled Oscillator

ROM Read Only Memory

SCA Switched Capacitor Array

SCL Source-Coupled Logic

SFDR Spurious Free Dynamic Range

SNR Signal-to-Noise Ratio

SoC System-on-a-Chip

SSB Single-Sideband

TSPC True Single-Phase Clocking

UNII Unlicensed National Information Infrastructure

UWB Ultra-Wideband

VCO Voltage-Controlled Oscillator

WLAN Wireless Local Area Network

## LIST OF SYMBOLS

$\Delta I_{CP}$ Charge pump current mismatch PLL phase error in phase domain  $\Phi_{\varepsilon}$ Divider output phase in phase domain  $\Phi_{div}$ Reference phase in phase domain  $\Phi_{ref}$ PLL output phase in phase domain  $\Phi_{vco}$ Phase shift introduced by mixing operation  $\alpha$ β Frequency modulation index Divider output phase in the dual divide-by-4 ILFD behavior model Injection ratio in the dual divide-by-4 ILFD behavior model η Coupling ratio in the dual divide-by-4 ILFD behavior model  $\eta_{DC}$ Phase shift introduced by the RC load in the dual divide-by-4 ILFD behavior model Charge pump turn-on duty cycle  $\lambda_{on}$ Time constant of the second pole in the PLL open loop transfer  $\tau_I$ function Time constant of the first pole in the PLL open loop transfer function  $\tau_p$ Time constant of the compensation zero in the PLL open loop transfer  $\tau_z$ function Second pole in the PLL open loop transfer function  $\omega_I$

$\omega_c$  PLL crossover frequency

$\omega_p$  First pole in the PLL open loop transfer function

$\omega_z$  Compensation zero in the PLL open loop transfer function

$B_{CP}$  Charge pump current factor

$f_{ref}$  Reference clock frequency

$f_{vco}$  VCO output frequency

$G_{loop}(s)$  PLL open loop transfer function

$H_{LF}(s)$  Loop filter transfer function

$H_{PLL}(s)$  PLL closed loop transfer function

$I_{CP}$  Charge pump current

$I_{DC}$  DC current component in the dual divide-by-4 ILFD behavior model

$I_{inj}$  Injection signal in the dual divide-by-4 ILFD behavior model

$K_{VCO}$  VCO gain

$L(\Delta f)$  Phase noise at a frequency offset  $\Delta f$  from the carrier

N Division ratio

$N_{free}$  Division ratio of fractional-N PLL

$T_{ref}$  Reference clock period

V<sub>c</sub> VCO control voltage

## CHAPTER 1

## Introduction

## 1.1 Motivation

Wireless local area networks (WLANs) are rapidly developed and penetrated in everyday life in the past two decades. Several generations of standards with increasing data rates and improved system performance were developed [1]. The three popular WLAN standards in use today are based on the IEEE 802.11a, 802.11b and 802.11g specifications [2]-[4]. Although the IEEE 802.11a and 802.11b standards were ratified at the same time in 1999, products based on the IEEE 802.11b standards were available in the market a couple of years earlier, making it the incumbent standard. On the other hand, to improve data throughput and to maintain backward compatibility with existing IEEE 802.11b products, the IEEE 802.11g standard was ratified in June 2003.

Table 1.1 summarizes the information of these three WLAN standards. Both IEEE 802.11b and 802.11g standards operate in the 2.4 GHz industrial, scientific and medical (ISM) band while the IEEE 802.11a standard specifies communication in the 5 GHz unlicensed national information infrastructure (UNII) band. The IEEE 802.11a standard

occupies 300 MHz bandwidth with 12 non-overlapping channels. The other two standards have an aggregate bandwidth of 83.5 MHz, where 11 channels are available in total and only three of them are non-overlapping. Besides, the IEEE 802.11a and 802.11b standards employ different modulation schemes. More sophisticated orthogonal frequency division multiplexing (OFDM) modulation with 52 sub-carriers is used in the IEEE 802.11a standard for higher data throughput while complementary code keying (CCK) modulation is employed in the IEEE 802.11b standard with maximum data rate of 11 Mbps. The IEEE 802.11g standard provides either the high data rate option as the IEEE 802.11a standard or backward compatibility with the IEEE 802.11b standards. When there is no legacy 802.11b devices in the network, 802.11g devices can operate with data rate of 6 – 54 Mbps in OFDM mode. However, in order to communicate with 802.11b devices, they can only work in CCK mode and the data rate drops to 1 – 11 Mbps.

|                                        | IEEE 802,11a                 | IEEE 802.11b | IEEE 802.11g |

|----------------------------------------|------------------------------|--------------|--------------|

| Available Spectrum (MHz)               | 300                          | 83.5         | 83.5         |

| Frequency (GHz)                        | 5.15 - 5.35<br>5.725 - 5.825 | 2.4 – 2.4835 | 2.4 – 2.4835 |

| Number of Non-<br>overlapping Channels | 12                           | 3            | 3            |

| Modulation Scheme                      | OFDM                         | CCK          | CCK/OFDM     |

| Data Rate (Mbps)                       | 6 – 54                       | 1 – 11       | 1-11,6-54    |

Table 1.1 IEEE 802.11a/b/g WLAN standards [1]

In WLAN telecommunication systems, low cost, high performance frequency synthesizers are essential. Among them, integer-N phase-locked loop (PLL) architecture

is usually selected due to its ease in implementation and excellent spurious performance. However, the intrinsic tradeoffs between frequency resolution, phase noise performance and switching time [5] are its major drawbacks. The frequency resolution specified by the application limits the choice of reference clock frequency and loop bandwidth. The reference clock frequency cannot be larger than the required frequency resolution while the loop bandwidth is set to be less than one tenth of the reference clock frequency for PLL loop stability [6]. As such, it leads to high division ratio and narrow loop bandwidth if fine frequency resolution is recommended. The in-band phase noise contribution is also amplified by large division ratio and the phase noise specification for the reference clock becomes tough. Moreover, with narrow loop bandwidth, the PLL settling time is long and the phase noise contributed by the VCO is not suppressed sufficiently due to low cutoff frequency.

Fractional-N PLL architecture is hence used to solve the above dilemma. Since the dependence of loop bandwidth on frequency resolution is void, the frequency resolution can be set arbitrarily fine with wide loop bandwidth. Due to the loop bandwidth expansion, the VCO phase noise contribution is attenuated more and the PLL settling time becomes shorter. The in-band phase noise amplification can also be optimized with appropriate selection on frequency resolution and division ratio. Nevertheless, the spectral purity is deteriorated by fractional spurs due to the time varying division modulus control. Dithering or sigma-delta-based averaging [7] is the common practice to randomize the division modulus pattern for spur and quantization noise suppression, but residual spurs cannot be completely eliminated due to mismatches in the circuit components (for example, the charge pump current mismatch [8]).

As a compromise, sub-integer-N PLL [9] is proposed. It shares the same architecture as integer-N PLL, but provides fractional frequency resolution. This relieves the intrinsic tradeoffs in integer-N PLL. On the other hand, unlike in fractional-N PLL, fractional frequency division is accomplished by a fractional frequency divider with time-invariant modulus control. Consequently, the circuit structure is simple, the spurious performance is superior, no unexpected fractional spurs are created, the reference clock frequency and loop bandwidth can be higher, division ratio can be decreased, and phase noise can be well suppressed.

In this research, the implementation of a 2.4 GHz sub-integer-N PLL for IEEE 802.11b/g WLAN applications in a standard 0.35 µm CMOS process is demonstrated. Details of the system level design and block level circuit implementations are presented.

## 1.2 Thesis Organization

Besides this introductory ones, there are six additional chapters. In Chapter 2, general considerations in frequency synthesizer design are discussed. Overviews of integer-N PLL operation principle and different architectures for sub-integer frequency synthesis are also presented. The system level design of the proposed frequency synthesizer architecture is then addressed in Chapter 3.

In Chapter 4, the structure of the proposed programmable fractional frequency divider and its circuit implementation are demonstrated. The characteristics of the novel dual

divide-by-4 injection-locked frequency dividers (ILFDs) are also analyzed. Afterwards, in Chapter 5, the circuit implementation of other building blocks, including the quadrature voltage-controlled oscillator (QVCO), phase frequency detector (PFD), charge pump and loop filter, is depicted.

Experimental verifications of the proposed frequency synthesizers and the circuit components (including the QVCO, dual divide-by-4 ILFDs and programmable fractional frequency dividers) are described in Chapter 6. Finally, conclusion is drawn in Chapter 7.

## CHAPTER 2

# FREQUENCY SYNTHESIZER BACKGROUND

## 2.1 General Considerations

#### 2.1.1 Frequency Accuracy

The frequency accuracy of frequency synthesizers is essential. For instance, frequency tolerance of less than 25 ppm is specified in the IEEE 802.11 WLAN standard. Typically, the reference frequency of frequency synthesizers is derived from a high accuracy crystal oscillator. Due to temperature variation and crystal aging effect, frequency error is inevitable and cause rotation in the signal constellation for quadrature-modulated signal. On the other hand, the orthogonal frequency division multiplexing (OFDM) modulation scheme employed in the IEEE 802.11a/g standards requires accurate frequency synchronization between the receiver and the transmitter; otherwise frequency offsets will induce inter-carrier interference (ICI), that is, crosstalk between the sub-carriers.

Frequency compensation of crystal oscillator [10] can be performed to adjust its oscillating frequency. The frequency shift is first measured in the rotated constellation diagram during the training phase at the beginning of communication. Frequency correction is then applied on the crystal oscillator. Besides, in some WLAN applications, frequency correction is performed directly on the received constellation by multiplying it with a complex exponential signal for constellation rotation [11].

#### 2.1.2 Frequency Resolution

The frequency resolution of frequency synthesizers is the minimum frequency step that can be provided by the systems. Usually, it is determined by the required channel spacing for the intended application. Depending on the chosen frequency synthesizer architecture, the specified frequency resolution may limit the choice of system parameters and thus affect the system performance too. For example, the reference frequency of integer-N phase-locked loop (PLL) is generally equal to its frequency resolution. Its loop bandwidth is then set as one tenth of the reference frequency for stability [6]. Once the loop bandwidth is specified, the phase noise performance, spurious suppression and switching time of the PLL are determined.

#### 2.1.3 Phase Noise

Phase noise is defined as the ratio between the total carrier power and the noise power in 1 Hz bandwidth at frequency offset  $\Delta f$  from the carrier  $f_0$ , which is:

$$L(\Delta f) = 10 \log \left( \frac{\text{power in 1 Hz bandwidth at } f_0 + \Delta f \text{ frequency offset from the carrier}}{\text{total carrier power}} \right)$$

(2.1)

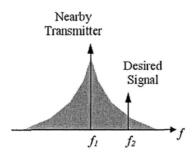

Frequency synthesizer phase noise will corrupt both upconverted and downconverted signals [12], degrading the signal-to-noise ratio (SNR) of the wanted signals. As shown in Figure 2.1, the phase noise sideband of a nearby strong interferer at  $f_I$  condemns the frequency band of the weak desired signal at  $f_2$ . Even with a noiseless receiver, the desired signal cannot be discriminated from the phase noise of the nearby interferer as they are in the same frequency band. As such, in wireless communication standards, the transmitter output spectrum should obey the transmit spectrum mask, which specifies the maximum noise levels at certain frequency offsets from the carrier frequency.

Figure 2.1 Influence of phase noise in a transmitter

Direct and reciprocal mixing effects [13] occur in downconversion, as depicted in Figure 2.2. If the LO contains phase noise and a strong interferer locates near the desired signal, two overlapping noise spectra are created at the intermediate frequency (IF) after downconversion. The LO phase noise is superposed into the wanted signal by direct mixing while the phase noise sideband of the interferer corrupts the desired signal by reciprocal mixing. The SNR of the demodulated signals hence degrades.

Figure 2.2 Influence of phase noise in a receiver

It can be seen that the influence of reciprocal mixing is determined by the LO phase noise at large frequency offset from the carrier, fallen into the desired signal frequency band. The phase noise at such region is usually dominated by that of voltage-controlled oscillators (VCOs). Therefore, VCO design with low phase noise has a direct impact on the reciprocal mixing effect. Moreover, the main consideration in the direct mixing effect is the in-band phase noise contribution of frequency synthesizers, which needs system optimization (for instance, decrease of loop bandwidth with sacrifice of speed).

#### 2.1.4 Spurious Signals

In addition to phase noise, unwanted spurious signals appear in the output spectrum of frequency synthesizers. They are usually generated due to parasitic coupling of signals in the systems. For example, the reference spurs in integer-N PLL are induced by charge injection of the charge pump at a rate equal to the reference frequency. Ripples with frequency components at multiples of the reference frequency occur at the VCO control

input and modulate the VCO oscillating frequency. Spurious tones are then generated at frequency offsets equal to multiples of the reference frequency from the carrier.

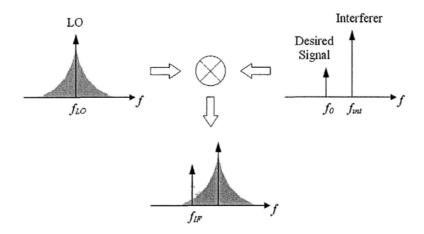

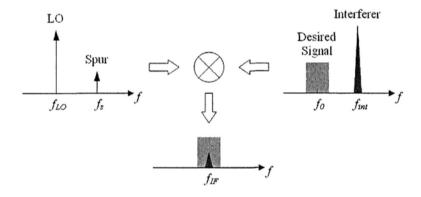

In some occasions, spurious signals may mix with interference and the resulting signals fall into the desired signal frequency band, deteriorating the desired signal SNR. An example is illustrated in Figure 2.3. The frequency synthesizer output contains a main tone at  $f_{LO}$  and a spur at  $f_s$ . The desired signal at  $f_0$  is convolved with the LO and shifted to  $f_{IF}$ , where  $f_{IF} = f_0 - f_{LO}$ . The interference signal is also downconverted to  $f_{IF}$  if  $f_{int} - f_s = f_{IF}$ . Consequently, the wanted signal is condemned.

Spurious signals can be suppressed by reducing the PLL loop bandwidth or increasing the loop filter order at the expenses of longer settling time and PLL stability.

Figure 2.3 Influence of spurious signals in a receiver

### 2.1.5 Switching Time

In frequency hopping telecommunication systems like Bluetooth<sup>TM</sup>, frequency synthesizers have to switch from one frequency to another within certain frequency

accuracy at a specified time slot. The switching time for Type-II, third-order PLL-based frequency synthesizers can be estimated as [14]:

$$t_{lock} = \frac{\ln \left( \frac{f_{step}}{f_{error}} \right)}{f_c \cdot \xi_e(\phi_m)}$$

(2.2)

where

$f_c$  the open loop bandwidth

$f_{step}$  the amplitude of frequency jump

$f_{error}$  the maximum frequency error at  $t_{lock}$

$\phi_m$  the phase margin

$\xi_e(\phi_m)$  the effective damping coefficient at a specified phase margin

As suggested in Equation 2.2, wide loop bandwidth is beneficial for fast switching time. However, the phase noise and spurious performance become worse as a tradeoff. PLL stability should also be considered because the loop bandwidth is limited to at least one tenth of the reference frequency, as a rule of thumb.

### 2.1.6 Power Dissipation

Low power consumption is a crucial aspect for portable electronic devices and products. First, it determines the battery life-time and standby-time of the portable products. Additionally, since less heat is generated, the failure due to thermal problem is alleviated and thus the product lifetime and reliability improve. To achieve low power dissipation for frequency synthesizers, current reuse [15] is one of the possible solutions.

#### 2.1.7 Integration Level

Full integration of frequency synthesizers in the monolithic CMOS process faces two bottlenecks, namely the absence of high quality factor inductor and considerable area occupied by the loop filter capacitors. Conductor loss and substrate loss are the main causes for the high loss of on-chip inductors. Bond wires [16] can be used to replace on-chip inductors, but they lack accurate modeling and their reliability and repeatability are poor. Nowadays, the modern CMOS technology with mixed-signal RF option provides thick top metal layer and less conductive substrate to improve the quality factor of on-chip inductors.

The loop dynamic behavior and phase noise performance of frequency synthesizers determine the capacitor size of the loop filter. High capacity MIM capacitor is available in the modern CMOS process to minimize capacitor area. Moreover, the capacitance multiplier [17] and dual path loop filter topology [18] can be used to reduce the capacitor size with tradeoffs of extra power consumption and noise contribution.

### 2.1.8 Sensitivity to Interference

In modern telecommunication systems, the system-on-a-chip (SoC) solution acquires low cost and small form factor by implementing all functions in a single design. Nevertheless, this induces serious unwanted coupling to sensitive parts of the system and crosstalks in the substrate. Spike-like noise produced by digital baseband circuits on the supply and on the substrate may deteriorate the spectrum purity of frequency synthesizers with spurious

tones. Careful designs in layout [19] help to isolate the noise sources. Furthermore, the frequency pulling by the power amplifier (PA) in the direct conversion transmitter [20] may corrupt the synthesized signal, degrading system performance. Clever frequency planning [21], [22] has to be adopted to ensure that the PA output spectrum and LO output are sufficiently far apart.

#### 2.2 Integer-N Phase-Locked Loop

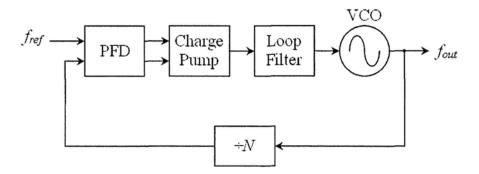

Figure 2.4 depicts the integer-N PLL structure, which consists of a phase frequency detector (PFD), a charge pump (CP), a loop filter, a VCO and a frequency divider. It can be used to generate a high frequency carrier with low frequency drift and superior spurious performance, from a low frequency accurate reference source (for example, crystal oscillator). The PLL output frequency  $f_{out}$  is N times greater than the reference frequency  $f_{ref}$ , where N is an integer. Additionally, it is synchronized in phase with the reference source.

Figure 2.4 Block diagram of an integer-N phase-locked loop

Integer-N PLL is a feedback system. The PLL output frequency is scaled down N times by the frequency divider in the feedback path. It is then used for comparison with the reference source to determine if the system is in lock. Comparison is performed by the PFD, which is an error detector to detect both phase and frequency differences between the reference source and the frequency divider output. The PFD controls the charge pump to inject correction current pulses with appropriate polarity, duration and amplitude. The charge pump correction current is filtered by the loop filter to extract the desired average VCO control voltage level. Any high frequency components in the VCO control voltage are removed to assure the VCO output spectral purity. Afterwards, the VCO alters its oscillating frequency with respect to the change in its control voltage level. The frequency regulation process repeats until no phase and frequency error is detected by the PFD.

Integer-N PLL is the most commonly used frequency synthesizer architecture due to its simple structure and good spurious performance. Its building blocks are well developed and can be integrated together without great difficulty, which speeds up the implementation process. Moreover, it does not generate any unexpected spurious tones in its output spectrum and the reference spurs can be easily suppressed by the loop filter.

The main deficiency of integer-N PLL is the tradeoffs between frequency resolution, phase noise performance and switching time. The frequency divider in integer-N PLL only acquires integral division ratio. As such, the PLL output frequency should be the integer multiple of the reference frequency and the frequency resolution is limited by the reference frequency. Since the PLL loop bandwidth is generally set less than one tenth of

the reference frequency for stability, fast settling behavior is restricted with narrow loop bandwidth. On the other hand, the large division ratio due to fine frequency resolution also causes deterioration of the in-band phase noise characteristic due to high amplification factor. The considerable VCO phase noise contribution is another issue as it is not attenuated with narrow loop bandwidth.

## 2.3 Architectures for Fractional Frequency Synthesis

#### 2.3.1 Direct Digital Frequency Synthesizer

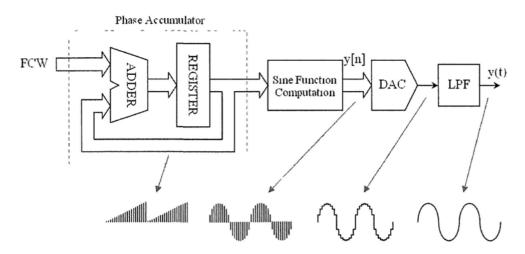

The Direct digital frequency synthesizer (DDFS) was first proposed by Tierney *et al.* in 1971 [23]. Figure 2.5 shows its architecture for sine wave generation, which composes of four basic building blocks: a phase accumulator, a phase to amplitude sine function generator, a digital-to-analog converter (DAC) and a lowpass filter (LPF).

The phase accumulator consists of a L-bit full adder and a L-bit phase register, functioning as an overflowing accumulator to generate instantaneous phase argument for the sine function generator. The frequency control word (FCW) controls the rate of phase accumulator overflow, which corresponds to one sine wave output period. With the input clock frequency  $f_{clk}$ , the output frequency  $f_{out}$  and frequency resolution  $\Delta f$  can be expressed as:

$$f_{out} = \frac{FCW}{2^{L}} f_{clk} \qquad 0 \le FCW \le 2^{L-1}$$

(2.3)

$$\Delta f = \frac{f_{clk}}{2^L} \tag{2.4}$$

Figure 2.5 Block diagram of a sine-output direct digital frequency synthesizer

The instantaneous phase values generated by the phase accumulator are then passed to the sine function generator, which is a sine function ROM lookup table in the simplest implementation. Discrete sine output waveform is produced and converted to analog output by the DAC. To remove the harmonics and high frequency spurious signals, a lowpass filter is used.

Since the DDFS does not have a feedback loop, agile frequency switching can be acquired. Its frequency synthesis process is completely performed in digital domain, enabling transient free frequency changes with phase continuity, direct phase and frequency modulation in digital domain, and excellent temperature and aging stability.

Fine frequency resolution can also be obtained easily by increasing the number of bits in the phase accumulator. Besides, the DDFS is a synchronized system with low phase jitter as its phase noise performance is typically determined by that of the input clock source.

In spite of its many advantages, the DDFS is only suitable for manipulating IF signals of few hundreds MHz since power consumptions of both digital circuitry and DAC are huge when operating at high speed. Furthermore, the DDFS output frequency is fundamentally limited by the Nyquist criterion to bandwidth of  $f_{clk}/2$ . In practice, however, it is constrained to be less than  $f_{clk}/3$  due to the circuit limitation and spurious problem [24].

The sine function generator is considered as the most critical block in DDFS. High frequency resolution and good spectral purity require large ROM size and it is power hungry to scan the ROM at high speed. Generally, the sine function quarter-wave symmetry property is exploited to reduce the ROM size [25]. The ROM size is also truncated to less than *L*-bit, but the quantization effect leads to degradation in spurious free dynamic range (SFDR) of the systems. Various optimization approaches for the sine function generator were introduced in literature and are classified into three categories: 1) CORDIC-like angle-rotation algorithms [24], [26]–[28]; 2) polynomial interpolation techniques [29]–[32]; and 3) angular decomposition ROM compression techniques [33]–[35].

In CORDIC-like angle-rotation approaches, coordinate rotation of a vector with known sine and cosine values in complex plane is performed until the error to desired angle is sufficiently small. Very small lookup memories are needed, but a complex arithmetic

circuitry is required, limiting operation speed and increasing power dissipation and tuning latency.

In polynomial interpolation techniques, trigonometric functions are approximated by using interpolation in each equal-length sub-interval. Only a small ROM is used to store the polynomial coefficients and some additional arithmetic circuitries (adders, multipliers, etc.) are built to implement the polynomial approximation.

The last method, angular decomposition ROM compression technique, divides the lookup table into smaller parts. One table stores the coarse value while others contain the fine values. The final sine/cosine values are obtained by adding up the coarse and fine values. Small lookup table and simple arithmetic circuitry are the advantages of this method.

Instead of optimizing the sine function generator, another approach was proposed in literature to eliminate the ROM completely by using a nonlinear DAC [36], [37]. The sine function generator and DAC are combined into a single nonlinear DAC to perform phase-to-amplitude transformation and digital-to-analog conversion simultaneously. Circuit complexity is reduced and considerable area and power are saved.

Due to its fast switching speed, fine frequency resolution and high precision frequency control, the DDFS plays an important role in wireless telecommunication systems (including frequency hopping and spread-spectrum systems), radar applications, electronic warfare and high precision measurement systems.

#### 2.3.2 Fractional-N Phase-Locked Loop

For frequency synthesizer applications which demand fast switching time with narrow channel spacing, fractional-N PLL is a suitable candidate. It can synthesize fractional multiples of the reference frequency with fine resolution. High reference frequency can be used, which results in wide loop bandwidth and agile switching time.

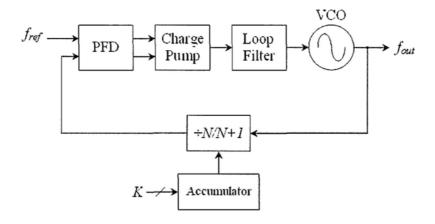

Figure 2.6 depicts the block diagram of a fractional-N PLL [38]. The frequency divider is implemented as a dual-modulus prescaler with division ratios of N and N+1, which is controlled by a k-bit digital accumulator. The digital word input K determines the accumulator overflow rate. Once the accumulator overflows, a carry bit is generated to change the dual-modulus prescaler division ratio. In each cycle, the dual-modulus prescaler divide K cycles by N+1 and  $2^k-K$  cycles by N and hence the average division ratio  $N_{frac}$  is evaluated as:

$$N_{frac} = \frac{(2^k - K)N + K(N+1)}{2^k} = N + \frac{K}{2^k}$$

(2.5)

where N is an integer and the last term belongs to the fractional part.

According to Equation 2.5, long accumulator length k results in fine frequency resolution, but this complicates the accumulator design and consumes more power. On the other hand, the choice of the reference frequency  $f_{ref}$  and the frequency resolution requirement specifies the minimum number of bits needed in the accumulator.

Figure 2.6 Block diagram of a fractional-N phase-locked loop

High reference frequency not only leads to wide loop bandwidth and fast settling time, but also improves system phase noise performance. With wide loop bandwidth, VCO phase noise is attenuated more by the highpass characteristic with increased cutoff frequency. Division ratio *N* becomes smaller and therefore the in-band phase noise is less amplified.

In spite of its various advantages, fractional-N PLL faces fractional spur problem. The accumulator overflows and changes the division modulus periodically in the fractional-N frequency synthesis. For example, to realize fractional division ratio of N + 0.25, the accumulator output bit pattern is N, N, N, N + 1, which repeats at frequency of  $f_{ref}/4$ . Although the overall phase error for each cycle is zero, the phase difference between the reference clock and frequency divider output is nonzero and varies repetitively. Frequency components at multiples of  $\pm f_{ref}/4$  are generated at the VCO control input. Due to frequency modulation performed by the VCO, spurious tones appear next to the carrier at frequency offsets of  $\pm n \cdot f_{ref}/4$ , where n is an integer. Fractional spurs at large frequency

offsets can be filtered out by the loop filter, but the problem becomes severe for those fall within the loop bandwidth.

To eliminate fractional spurs, the phase error should be compensated. In the classical approach [39], the accumulator provides phase error information to control a DAC, generating opposite polarity current pulses at the charge pump output to cancel out periodicities in the phase error signal. The compensation scheme depends heavily on the precise match between the DAC output and the phase error signal, which is sensitive to temperature and process variations.

A more effective solution is to replace the accumulator by a delta-sigma ( $\Delta\Sigma$ ) modulator [7], [40]–[45]. The  $\Delta\Sigma$  modulator randomizes the division modulus to eliminate its periodicity. The resulting bit stream consists of an average value equal to the desired fractional division ratio and of shaped quantization noise. The quantization noise introduced is whitened and transposed to high frequencies, which is attenuated by the loop filter. Besides, since high order modulators are generally required to obtain sufficient noise suppression within the loop bandwidth, quantization noise at large frequency offset becomes serious and hence a higher order loop filter is implemented to counteract increased noise slope.

Another advantage of using the  $\Delta\Sigma$  modulator in fractional-N PLL is the ability of indirect digital frequency modulation at RF [42], [43]. This greatly simplifies the transmitter structure. Furthermore, all-digital implementation of the  $\Delta\Sigma$  modulator is favorable in CMOS technology, providing convenient approach for full chip integration.

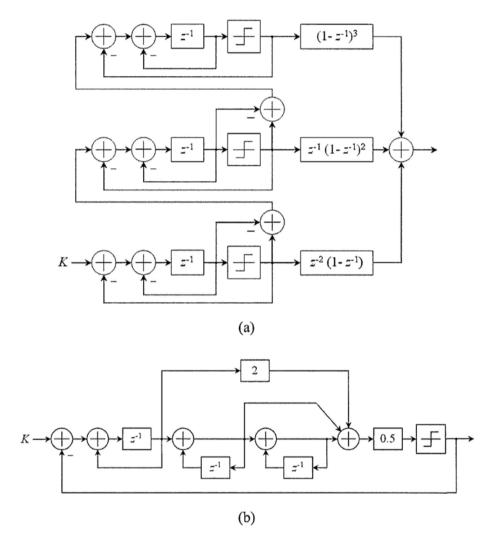

There are two main topologies of  $\Delta\Sigma$  modulators used in fractional-N PLLs, namely the multi-stage noise shaping (MASH) structures [42], [43] and the single loop architectures [44], [45]. Third-order examples of these two topologies are displayed in Figure 2.7.

Figure 2.7 Architectures of third-order  $\Delta\Sigma$  modulators a) MASH [43] and b) single loop [45]

The MASH  $\Delta\Sigma$  modulator consists of first-order modulators in cascade, where the quantization error of previous stage is the input to next stage. Quantization errors of all stages except the last one are cancelled out by summing the stage outputs in a noise-

shaping block. Since there is no feedback path between different stages and each stage is first-order, the MASH  $\Delta\Sigma$  modulator is unconditionally stable [46]. Besides, it is simple in structure, only adders and registers are needed. Pipelining [42] can be applied to further reduce logic gate count and power dissipation. However, the MASH  $\Delta\Sigma$  modulator tends to generate widespread fast-changing bit patterns, which transits substantial amount of quantization noise to high frequency. High order loop filter is thus needed to attenuate the high frequency quantization noise.

In contrast to the MASH counterpart, the single loop  $\Delta\Sigma$  modulator composes of accumulators with feedforward and feedback coefficients. There is higher flexibility in constructing the noise transfer function (NTF), but stability is a concern for high order topologies. By proper pole positioning, the high frequency quantization noise can be smoothed out, which relaxes the loop filter design. The prescaler division modulus switching is less intense and its dynamic range is enhanced when compared with the MASH  $\Delta\Sigma$  modulator. Nonetheless, there is a tradeoff between structure complexity and noise transfer function realization. The feedforward and feedback coefficients are usually approximated to values in power of two for the sake of complete removal of multipliers. As such, the stability and causality of the approximated NTF should be verified.

#### 2.3.3 Dual-Loop Frequency Synthesizer

As the name suggested, the dual-loop frequency synthesizer composes of two PLLs. One PLL generates a fixed high frequency carrier while another produces a low frequency signal with fine frequency steps. The low frequency signal is then superposed on the high

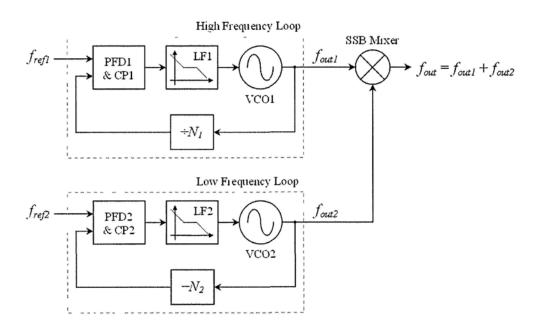

frequency carrier to obtain the desired carrier frequency and frequency resolution. An example [47] is given in Figure 2.8. Large loop bandwidth can be chosen in the high frequency loop to attenuate the VCO1 phase noise. In the low frequency loop, the VCO2 phase noise contribution is comparatively low [48] due to low center frequency. The overall phase noise performance is therefore good. But, the single-sideband (SSB) mixer specifications are critical. Poor spurious performance results due to the phase mismatches of both PLLs quadrature outputs, and nonlinearity and mismatches of the SSB mixer.

Figure 2.8 Architecture of a parallel configuration dual-loop frequency synthesizer

Another dual-loop frequency synthesizer in parallel configuration [47] is presented in Figure 2.9. The two PLLs operate at approximately half of the output frequency. Since its frequency resolution is determined only by the difference of the two reference frequencies, large values of reference frequencies can be selected to acquire wide loop bandwidth in both PLLs. Spurious performance of this frequency synthesizer type is

limited by the SSB mixer performance. On the other hand, the cross products of the two PLL outputs' harmonics may fall into the desired frequency band. This restricts the choice of the center frequency  $f_0$  and reference frequencies  $f_{refl}$  and  $f_{ref2}$ . Frequency pulling also occurs as both PLLs operate at almost the same center frequency.

Figure 2.9 Architecture of a parallel configuration dual-loop frequency synthesizer using vernier effect

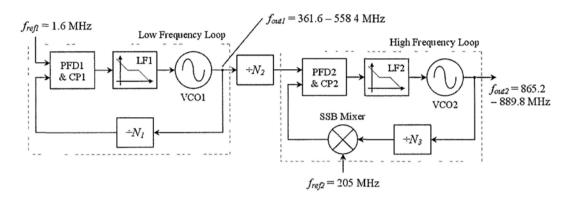

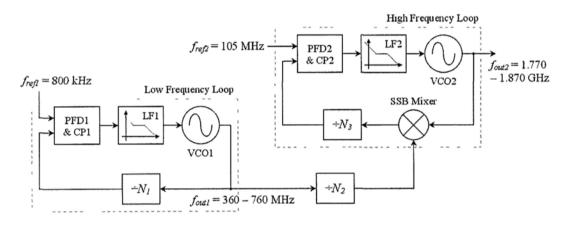

To alleviate its specifications, the SSB mixer can be placed inside the PLL feedback loop. In this way, the sidebands due to component mismatches and harmonics are attenuated by the loop filter. Two examples for GSM-900 [49] and DCS-1800 [50] applications are illustrated in Figure 2.10 and 2.11 respectively. Compared with traditional integer-N PLLs, division ratio can be greatly reduced in dual-loop frequency synthesizers. For example, the division ratio of an integer-N PLL for GSM-900 application should be 4236 – 4449 to realize channel spacing of 200 kHz while, in [49], it is just 226 – 349 (more than 10 times reduction).

Figure 2.10 Architecture of a series configuration dual-loop frequency synthesizer at 900 MHz

Figure 2.11 Architecture of a series configuration dual-loop frequency synthesizer at 1.8 GHz

In this dual-loop frequency synthesizer type, two PLLs are connected in series. The low frequency loop output becomes the high frequency loop input. In Figure 2.10, the divided low frequency loop output acts as the PFD2 input in the high frequency loop while it is inputted to the SSB mixer in Figure 2.11. Their noise transfer functions are different. In the first design, the low frequency loop phase noise is amplified by division ratio  $N_3$  in the high frequency loop, but not in the second design.

Channel selection is performed in the low frequency loop with a multi-modulus frequency divider  $N_I$  and wide loop bandwidth is preferable for fast switching time. Besides performing frequency upconversion, the high frequency loop is also intended for the suppression of phase noise and spurious tones induced by the low frequency loop.

Compared with integer-N PLLs, dual-loop frequency synthesizers acquire higher reference frequencies and lower division ratio, which are advantageous for wide loop bandwidth, fast switching time and low in-band phase noise. But their drawbacks include the need of two reference sources and more circuit components.

## 2.3.4 Frequency Synthesizer with Truly Modular Fractional Frequency Divider

Conventional flip-flop-based static frequency dividers act as frequency counters. The counters go through the state sequence repeatedly and advance one state in each clock cycle to provide integral division ratio. By using double-edge-triggered flip-flops instead of single-edge-triggered ones, the original divide-by-N circuits can work as divide-by-N/2 frequency dividers because the routine state propagation occurs at both rising and falling edges of the input clock. Examples with fixed fractional division ratio [51]–[53] and dual-modulus design [54], [55] can be found in literature.

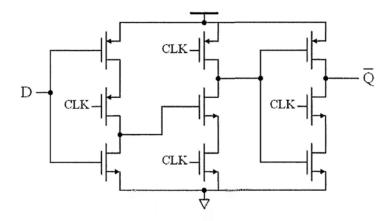

A double-edge-triggered flip-flop [56] composes of two latches and a multiplexer. The two latches operate at different time slots, utilizing both positive and negative level of the input clock, while the multiplexer selects the output from the latch that is holding the

valid data. All of them are synchronized with the input clock and hence input clock loading increases. In order to guarantee sufficient time margin for related logic operation during both clock Hi and Lo cycles, the input clock duty cycle should be 50%. As such, a duty cycle corrector [51], [52] is needed, which consumes power and chip area.

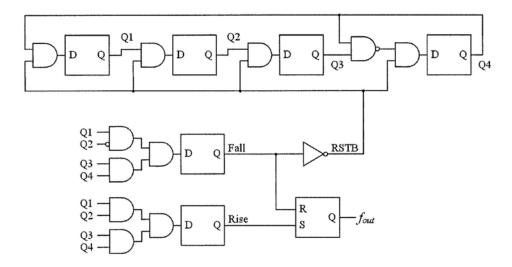

Extra logic gates and flip-flops are required in divide-by-N/2 designs when compared with their divide-by-N counterparts. For example, a divide-by-11 frequency divider can be implemented by using four flip-flops and some combinational logic gates. If implemented using double-edge-triggered flip-flops instead, divide-by-5.5 operation results and a circuit example is shown in Figure 2.12. In addition to the four flip-flops and combinational logic gates for the state machine in the original circuit, two more D-flip-flops, one RS latch and some logic gates for output manipulation and state machine initialization are required. The extra components not only increase the input clock loading, but also prolong the critical path propagation delay, limiting the circuit operation speed.

Figure 2.12 Example of a divide-by-5.5 static frequency divider [52]

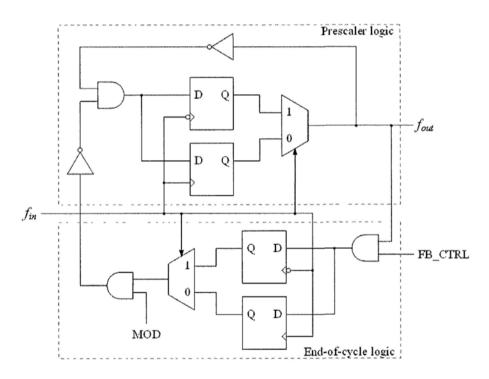

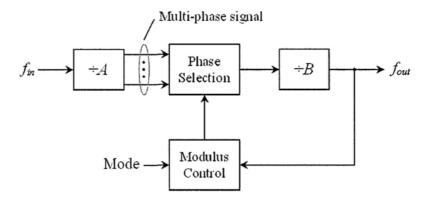

A dual-modulus prescaler design with fractional division ratio [54] is presented in Figure 2.13. Its structure is similar to the divide-by-2/3 divider cell in [57] and consists of two parts: the prescaler logic to perform frequency division operation and the end-of-cycle logic to select the desired division ratio. The latches are configured as double-edge-triggered flip-flops. In the divide-by-1.5 mode (both MOD and FB\_CTRL are Hi), half extra period of the input clock is swallowed by the prescaler logic to perform divide-by-1.5 operation. When either MOD or FB\_CTRL is Lo, the output simply tracks the input and the circuit is in the divide-by-1 mode.

Figure 2.13 Example of a divide-by-1/1.5 dual-modulus static frequency divider [54]

## 2.3.5 Frequency Synthesizer with Regenerative Frequency Divider

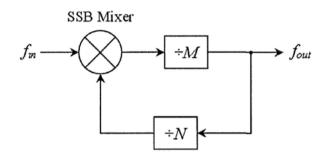

Regenerative frequency dividers are originated from the dynamic Miller frequency divider [58]. Figure 2.14 depicts the general architecture of the regenerative frequency divider with fractional division ratio, which composes of a SSB mixer and frequency dividers. A feedback loop is formed where the divided version of the output is mixed with the input. Under proper phase and gain conditions, the desired frequency component will remain and circulate around the loop [59]. For instance, the output frequency  $f_{out}$  can be expressed as:

$$f_{in} \pm \frac{f_{out}}{N} = M f_{out} \tag{2.6}$$

$$f_{out} = \frac{N}{MN \pm 1} f_{in} \tag{2.7}$$

where plus sign is selected if the lower sideband is chosen while minus sign corresponds to selection of the upper sideband.

The operation frequency of the regenerative frequency divider is considered higher than that of the flip-flop-based static type because the device capacitances can be tuned out by means of resonance with on-chip spiral inductors. Quadrature outputs with symmetric waveforms can also be easily acquired from the regenerative frequency divider outputs, but the SSB mixer mismatches and nonlinearity may generate spurious tones at the output.

Figure 2.14 Miller frequency divider with fractional division ratio

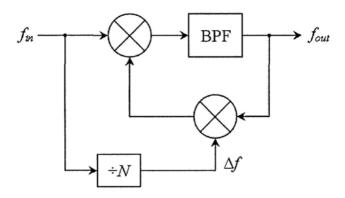

In [60], a modified Miller frequency divider for fractional division was proposed and its structure is displayed in Figure 2.15. The major difference apart from the conventional ones is the introduction of a mixer in the feedback path, in which the output is first translated by frequency derivation  $\Delta f$  before mixing with the input signal. In this design, there are two possible output frequencies:

$$f_{out} = \frac{f_m}{2} \pm \frac{\Delta f}{2}$$

$$= \frac{N \pm 1}{2N} f_m$$

(2.8)