# Institutionen för datavetenskap

Department of Computer and Information Science

#### Final thesis

# **Evaluation of the Configurable Architecture REPLICA with Emulated Shared Memory**

by

# Erik Alnervik

LIU-IDA/LITH-EX-A--14/010--SE

2014-02-06

# Linköpings universitet

#### **Final Thesis**

# **Evaluation of the Configurable Architecture REPLICA with Emulated Shared Memory**

by

# Erik Alnervik

LIU-IDA/LITH-EX-A--14/010--SE

2014-02-06

Supervisor: Erik Hansson Examiner: Christoph Kessler

## **Avdelning, Institution** Division, Department

Division of Software and Systems Department of Computer and Information Science SE-581 83 Linköping

| Datu |

|------|

| Date |

2014-02-06

|                               | english | Rapporttyp Report category  □ Licentiatavhandling  ⊠ Examensarbete □ C-uppsats □ D-uppsats □ Övrig rapport □ □ □ □ □ □ □ □ □ □ □ □ □ □ □ □ □ □ □ | ISBN  — ISRN  LIU-IDA/LITH-EX-A14/  Serietitel och serienummer  Title of series, numbering | /010SE  ISSN — |

|-------------------------------|---------|--------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------|----------------|

| Titel Title Författare Author | Ü       | of the Configurable Architec                                                                                                                     | ekturen REPLICA med emulerat d<br>ture REPLICA with Emulated Shar                          |                |

#### Sammanfattning

Abstract

REPLICA is a family of novel scalable chip multiprocessors with configurable emulated shared memory architecture, whose computation model is based on the PRAM (Parallel Random Access Machine) model.

The purpose of this thesis is to, by benchmarking different types of computation problems on REPLICA, similar parallel architectures (*SB-PRAM* and *XMT*) and more diverse ones (*Xeon X5660* and *Tesla M2050*), evaluate how REPLICA is positioned among other existing architectures, both in performance and programming effort. But it should also examine if REPLICA is more suited for any special kinds of computational problems.

By using some of the well known *Berkeley dwarfs*, and input from unbiased sources, such as *The University of Florida Sparse Matrix Collection* and *Rodinia benchmark suite*, we have made sure that the benchmarks measure relevant computation problems.

We show that today's parallel architectures have some performance issues for applications with irregular memory access patterns, which the REPLICA architecture can solve. For example, REPLICA only need to be clocked with a few MHz to match both Xeon~X5660 and Tesla~M2050 for the irregular memory access benchmark breadth~first~search. By comparing the efficiency of REPLICA to a CPU (Xeon~X5660), we show that it is easier to program REPLICA efficiently than today's multiprocessors.

| Nycl | kelord |

|------|--------|

|------|--------|

Keywords

REPLICA, PRAM, Benchmark

#### Sammanfattning

REPLICA är en grupp av konfigurerbara multiprocessorer som med hjälp utav ett emulerat delat minne realiserar PRAM modellen.

Syftet med denna avhandling är att genom benchmarking av olika beräkningsproblem på REPLICA, liknande (SB-PRAM och XMT) och mindre lika (Xeon X5660 och Tesla M2050) parallella arkitekturer, utvärdera hur REPLICA står sig mot andra befintliga arkitekturer. Både prestandamässigt och hur enkel arkitekturen är att programmera effektiv, men även försöka ta reda på om REPLICA är speciellt lämpad för några särskilda typer av beräkningsproblem.

Genom att använda välkända Berkeley dwarfs applikationer och opartisk indata från bland annat The University of Florida Sparse Matrix Collection och Rodinia benchmark suite, säkerställer vi att det är relevanta beräkningsproblem som utförs och mäts.

Vi visar att dagens parallella arkitekturer har problem med prestandan för applikationer med oregelbundna minnesaccessmönster, vilken REPLICA arkitekturen kan vara en lösning på. Till exempel, så behöver REPLICA endast vara klockad med några få MHz för att matcha både *Xeon X5660* och *Tesla M2050* för algoritmen *breadth first search*, vilken lider av just oregelbunden minnesåtkomst. Genom att jämföra effektiviteten för REPLICA gentemot en CPU (*Xeon X5660*), visar vi att det är lättare att programmera REPLICA effektivt än dagens multiprocessorer.

#### **Abstract**

REPLICA is a family of novel scalable chip multiprocessors with configurable emulated shared memory architecture, whose computation model is based on the PRAM (Parallel Random Access Machine) model.

The purpose of this thesis is to, by benchmarking different types of computation problems on REPLICA, similar parallel architectures (*SB-PRAM* and *XMT*) and more diverse ones (*Xeon X5660* and *Tesla M2050*), evaluate how REPLICA is positioned among other existing architectures, both in performance and programming effort. But it should also examine if REPLICA is more suited for any special kinds of computational problems.

By using some of the well known *Berkeley dwarfs*, and input from unbiased sources, such as *The University of Florida Sparse Matrix Collection* and *Rodinia benchmark suite*, we have made sure that the benchmarks measure relevant computation problems.

We show that today's parallel architectures have some performance issues for applications with irregular memory access patterns, which the REPLICA architecture can solve. For example, REPLICA only need to be clocked with a few MHz to match both *Xeon X5660* and *Tesla M2050* for the irregular memory access benchmark *breadth first search*. By comparing the efficiency of REPLICA to a CPU (*Xeon X5660*), we show that it is easier to program REPLICA efficiently than today's multiprocessors.

# **Acknowledgments**

I would like to thank Erik Hansson for his work as supervisor and his comments on this thesis, Martti Forsell for his technical support of the REPLICA architecture, and Christoph Kessler for his work as examiner and his comments on this thesis.

Linköping, February 2014 Erik Alnervik

# **Contents**

| No | otatio | n                                            | xiii |

|----|--------|----------------------------------------------|------|

| 1  | Intr   | oduction                                     | 1    |

|    | 1.1    | Purpose                                      | 2    |

|    | 1.2    | Thesis Outline                               | 2    |

|    | 1.3    | The PRAM Model                               | 2    |

|    | 1.4    | Performance Metrics                          | 4    |

|    |        | 1.4.1 Amdahl's Law                           | 5    |

|    | 1.5    | The Dwarfs from Berkeley                     | 6    |

|    | 1.6    | Related Work                                 | 6    |

|    | 1.7    | Some Available Parallel Benchmarks           | 7    |

|    | 1.8    | Publications                                 | 8    |

| 2  | TL.    | A 1. i. 4 4                                  | 9    |

| 2  | 2.1    | Architectures REPLICA                        | 9    |

|    | 2.1    |                                              | 10   |

|    |        |                                              | 10   |

|    |        | 2.1.2 Memory Modules                         | 11   |

|    |        | 2.1.4 The Baseline Language                  | 14   |

|    |        |                                              | 16   |

|    |        | <ul><li>2.1.5 The REPLICA Language</li></ul> | 16   |

|    |        | 2.1.7 Limitations                            | 17   |

|    |        | 2.1.8 Previous REPLICA Works                 | 17   |

|    | 2.2    | Xeon X5660                                   | 18   |

|    | 2.2    | 2.2.1 Xeon Machine Setup                     | 19   |

|    |        | 2.2.2 OpenMP                                 | 19   |

|    | 2.3    | XMT                                          | 23   |

|    | 2.5    | 2.3.1 XMTC                                   | 25   |

|    |        | 2.3.2 XMTSim                                 | 27   |

|    | 2.4    | Tesla M2050                                  | 27   |

|    | 2.1    | 2.4.1 CUDA C                                 | 28   |

|    |        | 2.4.2 Tesla's Host Setup                     | 30   |

|    | 2.5    | SB-PRAM                                      | 30   |

|    |        |                                              |      |

x CONTENTS

|   |      | 2.5.1   | Fork                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 31    |

|---|------|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|

|   |      | 2.5.2   | pramsim                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 34    |

|   |      |         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |       |

| 3 | The  | Bench   | mark Suite                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 35    |

|   | 3.1  | Measu   | ıring                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 35    |

|   | 3.2  | Prefix  | Sum (PS)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 37    |

|   |      | 3.2.1   | PS for REPLICA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 38    |

|   |      | 3.2.2   | PS for Xeon                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 39    |

|   |      | 3.2.3   | PS for XMT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 40    |

|   |      | 3.2.4   | PS for Tesla                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 40    |

|   |      | 3.2.5   | PS for SB-PRAM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 41    |

|   | 3.3  | Dense   | Matrix-Matrix Multiplication (DeMM)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 41    |

|   |      | 3.3.1   | DeMM for REPLICA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 42    |

|   |      | 3.3.2   | DeMM for Xeon                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 44    |

|   |      | 3.3.3   | DeMM for XMT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 47    |

|   |      | 3.3.4   | DeMM for Tesla                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 48    |

|   |      | 3.3.5   | DeMM for SB-PRAM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 50    |

|   | 3.4  |         | e Matrix-Vector Multiplication (SpMV)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 51    |

|   |      | 3.4.1   | SpMV for REPLICA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 53    |

|   |      | 3.4.2   | SpMV for Xeon                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 54    |

|   |      | 3.4.3   | SpMV for XMT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 55    |

|   |      | 3.4.4   | SpMV for Tesla                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 55    |

|   |      | 3.4.5   | SpMV for SB-PRAM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 56    |

|   | 3.5  |         | th First Search (BFS)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 57    |

|   | 0.0  | 3.5.1   | BFS for REPLICA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 59    |

|   |      | 3.5.2   | BFS for Xeon                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 60    |

|   |      | 3.5.3   | BFS for XMT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 62    |

|   |      | 3.5.4   | BFS for Tesla                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 62    |

|   |      | 3.5.5   | BFS for SB-PRAM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 63    |

|   | 3.6  |         | sort (QS)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 63    |

|   | 5.0  | 3.6.1   | QS for REPLICA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 65    |

|   |      | 3.6.2   | QS for Xeon                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 66    |

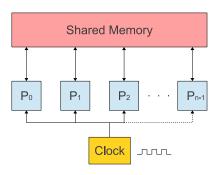

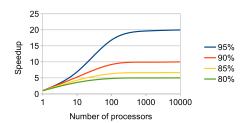

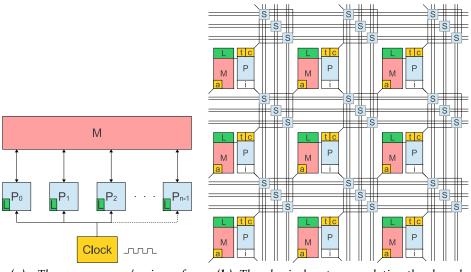

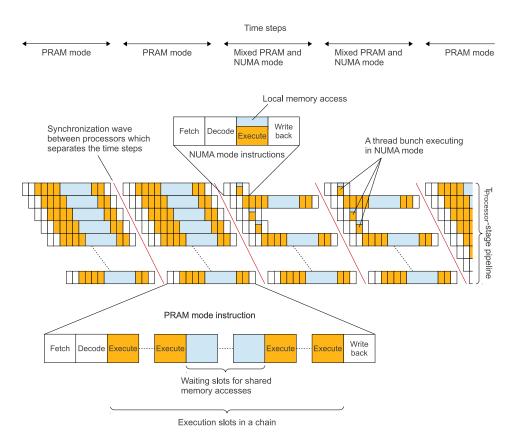

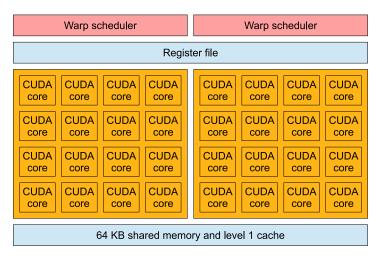

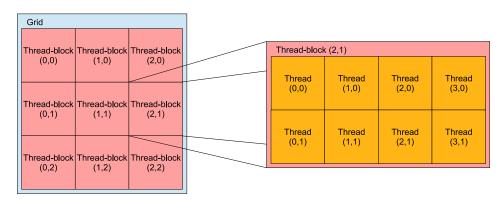

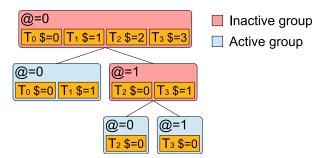

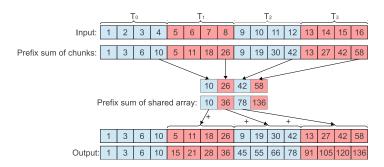

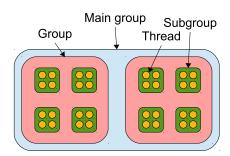

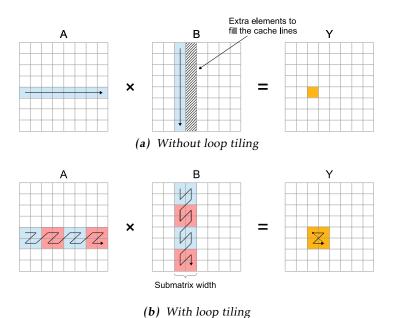

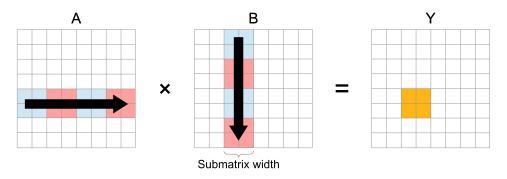

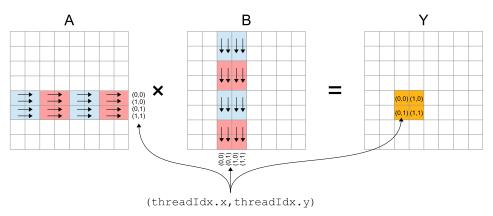

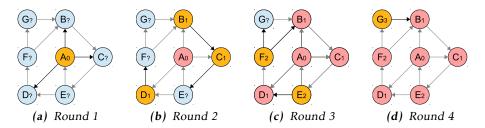

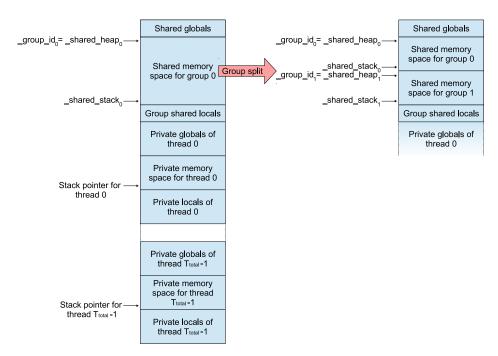

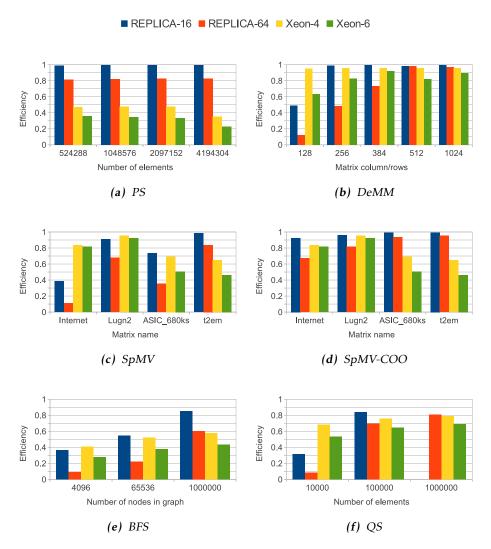

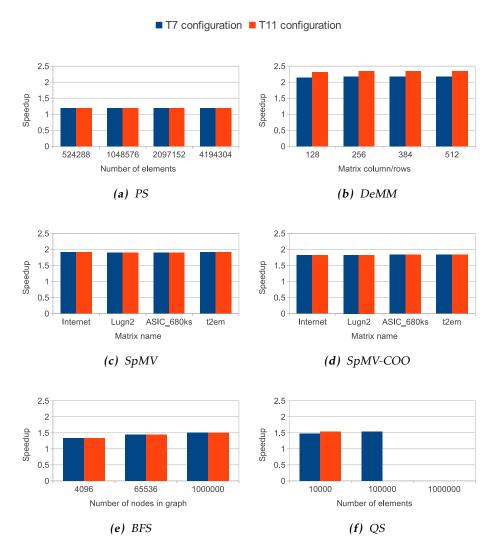

|   |      | 3.6.3   | QS for XMT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 67    |