## Dynamic Binary Translation on the .NET Platform

by

Patrick Andrew Wright

BSc, Victoria University of Wellington, New Zealand, 1994

A Thesis Submitted in Partial Fulfillment of the Requirements for the Degree of

MASTER OF SCIENCE

in the Department of Computer Science

© Patrick Andrew Wright, 2014 University of Victoria

All rights reserved. This thesis may not be reproduced in whole or in part, by photocopy or other means, without the permission of the author.

## **Supervisory Committee**

Dynamic Binary Translation on the .NET Platform

by

Patrick Andrew Wright

BSc, Victoria University of Wellington, New Zealand, 1994

## **Supervisory Committee**

Dr. Nigel Horspool, (Department of Computer Science)

## Co-Supervisor

Dr. Micaela Serra, (Department of Computer Science)

## Co-Supervisor

## **Abstract**

## **Supervisory Committee**

Dr. Nigel Horspool, Department of Computer Science

Co-Supervisor

Dr. Micaela Serra, Department of Computer Science

Co-Supervisor

Emulation is the practice of simulating one computer system on another. There are many methods of implementing an emulator. They exist on a performance continuum from simple interpretation to dynamic binary translation extended with various optimizations. Optimizations are diverse, including just in time compilation, large translation units, shadow stack, register mapping and many more. The goal of this thesis is to develop a high performance, portable emulator for the ARM v4 architecture without requiring substantial code analysis. This thesis describes the implementation of a dynamic binary translator translating to an intermediate language targeting a virtual machine. Targeting a virtual machine ensures that the emulator is portable. Optimizations implemented include forming large translation units and branch straightening in hot regions. The particular combination of translating to intermediate form for a virtual machine, and creating large translation units from hot regions does not seem to appear in the literature. The performance of the described dynamic binary translator exceeds the performance of an interpreter on the same platform by an order of magnitude. Code analysis was only used to straighten branches in hot regions. While many popular dynamic binary translation optimizations are not readily applicable when using a virtual machine target, the performance achieved shows that using virtual machine as translation target is viable method of implementing dynamic binary translator.

## **Table of Contents**

| Su | perviso   | ry Comm  | ittee                                                            | ii   |

|----|-----------|----------|------------------------------------------------------------------|------|

| Al | ostract   |          |                                                                  | iii  |

| Та | ible of C | Contents |                                                                  | iv   |

| Li | st of Tal | bles     |                                                                  | viii |

| Li | st of Fig | gures    |                                                                  | ix   |

| A  | cknowle   | dgments. |                                                                  | xi   |

| De | edication | 1        |                                                                  | xii  |

| 1  | Introdu   | uction   |                                                                  | 1    |

| 2  | Backg     | round    |                                                                  | 2    |

|    | 2.1       | Emulati  | on                                                               | 2    |

|    |           | 2.1.1    | Interpretation                                                   | 2    |

|    |           | 2.1.2    | Binary Translation                                               | 4    |

|    |           | 2.1.3    | Dynamic Binary Translation                                       | 5    |

| 3  | Previo    | us Work  |                                                                  | 8    |

|    | 3.1       | Reducir  | ng Translation Overhead                                          | 8    |

|    | 3.2       | Reducir  | ng Execution Overhead                                            | 8    |

|    |           | 3.2.1    | Translation Unit Size                                            | 9    |

|    |           | 3.2.2    | Shadow Stack                                                     | 11   |

|    |           | 3.2.3    | Indirect Branch Target Caching/Software Indirect Jump Prediction | 11   |

|    |           | 3.2.4    | Map Source Registers to Target Registers                         | 12   |

|    |           | 3.2.5    | Optimize Condition Code Handling                                 | 12   |

|    |           | 3.2.6    | Take Advantage of the Target ISA                                 | 12   |

|    |           | 3.2.7    | Cache Decoded Instructions                                       | 12   |

|    | 3.3       | Alternat | tives to Dynamic Binary Translation                              | 12   |

|   |       | 3.3.1     | Hybrid Static/Dynamic Translation                        | 13 |

|---|-------|-----------|----------------------------------------------------------|----|

|   |       | 3.3.2     | Hybrid Instruction Set Compiled Simulation               | 13 |

|   | 3.4   | The AR    | M v4 Instruction Set Architecture and Binary Translation | 13 |

|   |       | 3.4.1     | PC Relative Addressing                                   | 13 |

|   |       | 3.4.2     | Shifter Operand and Shifter Carry Out                    | 13 |

|   |       | 3.4.3     | Condition Flags.                                         | 14 |

|   |       | 3.4.4     | Conditional Execution                                    | 14 |

| 4 | An Ap | proach to | Dynamic Binary Translation                               | 15 |

|   | 4.1   | The AR    | M v4 Architecture                                        | 16 |

|   |       | 4.1.1     | Programmer's Model                                       | 17 |

|   |       | 4.1.2     | Instructions                                             | 19 |

|   |       | 4.1.3     | CodeDOM                                                  | 24 |

|   |       | 4.1.4     | Reflection.Emit                                          | 24 |

|   |       | 4.1.5     | Dynamic Language Runtime                                 | 26 |

|   |       | 4.1.6     | How the Dynamic Code is Executed                         | 29 |

|   | 4.2   | CLR Op    | otimization                                              | 29 |

|   | 4.3   | Challen   | ges                                                      | 30 |

|   |       | 4.3.1     | Hardware Simulation Challenges                           | 30 |

|   |       | 4.3.2     | When and What to Translate                               | 31 |

|   |       | 4.3.3     | Translating Program Flow                                 | 31 |

| 5 | Imple | nenting a | Dynamic Binary Translator                                | 33 |

|   | 5.1   | Hardwa    | re Simulation                                            | 33 |

|   |       | 5.1.1     | Registers                                                | 33 |

|   |       | 5.1.2     | Memory                                                   | 34 |

|   |       | 5.1.3     | Translating Instructions                                 | 35 |

|   |        | 5.1.4      | Flag Setting and Condition Codes | 36 |

|---|--------|------------|----------------------------------|----|

|   |        | 5.1.5      | Register to Stack Machine        | 39 |

|   | 5.2    | What to    | Translate                        | 40 |

|   |        | 5.2.1      | Discovering Dynamic Basic Blocks | 40 |

|   |        | 5.2.2      | Translation                      | 41 |

|   |        | 5.2.3      | When to Translate                | 42 |

|   | 5.3    | Translat   | ting Program Flow                | 42 |

|   |        | 5.3.1      | Creating Large Translation Units | 42 |

|   | 5.4    | Measuri    | ing Performance                  | 49 |

|   | 5.5    | Testing    |                                  | 49 |

| 6 | Bench  | marking 1  | the Translator                   | 50 |

|   | 6.1    | Perform    | nance of Interpreter             | 50 |

|   | 6.2    | Perform    | nance of Simple DBT              | 51 |

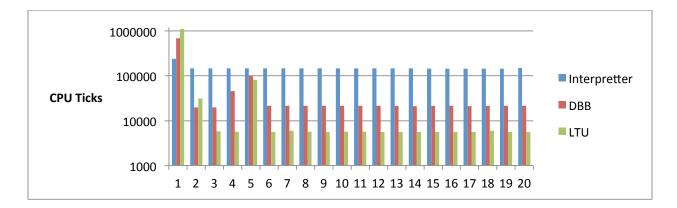

|   | 6.3    | Perform    | nance of DBT using LTU           | 51 |

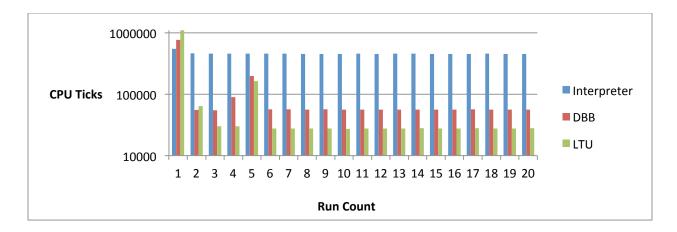

|   | 6.4    | Compar     | ring Different Approaches        | 52 |

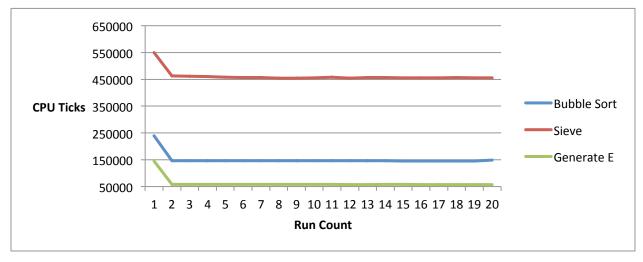

|   | 6.5    | Start Up   | o                                | 54 |

|   |        | 6.5.1      | Loading                          | 54 |

|   |        | 6.5.2      | Translation and Hot Traces       | 55 |

|   | 6.6    | When to    | o Translate                      | 56 |

|   | 6.7    | What to    | Translate – Hot versus All       | 57 |

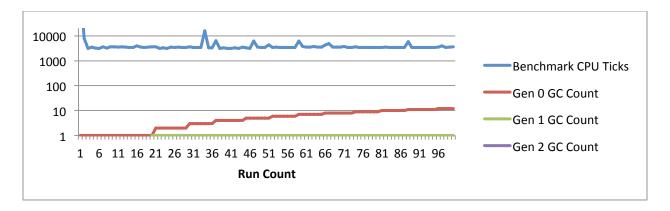

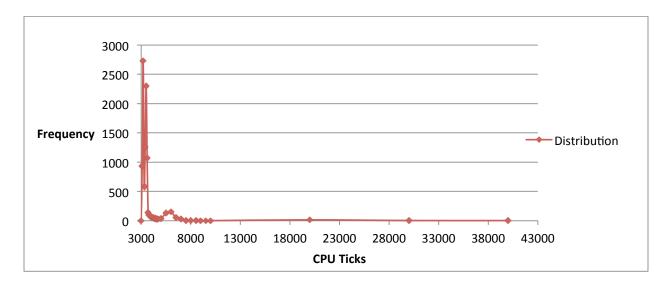

|   | 6.8    | Garbage    | e Collection                     | 59 |

| 7 | Conclu | usions and | d Future Work                    | 62 |

|   | 7.1    | Future V   | Work                             | 63 |

|   |        | 7.1.1      | Performance                      | 63 |

|   |        | 7.1.2      | Integration with ARMSim#         | 64 |

|   |        | 7.1.3  | Measuring Performance                   | 65 |

|---|--------|--------|-----------------------------------------|----|

|   |        | 7.1.4  | Thumb Instruction Support               | 65 |

| 8 | Biblio | graphy |                                         | 66 |

| 9 | Appen  | ndices |                                         | 71 |

|   | 9.1    | Append | lix A: Benchmark ARM Assembler Programs | 71 |

|   |        | 9.1.1  | Bubble Sort                             | 71 |

|   |        | 9.1.2  | Sieve of Eratosthenes                   | 72 |

|   |        | 9.1.3  | Generate E to n Decimal Places          | 73 |

|   | 9.2    | Append | lix B: Comparing Translation Targets    | 75 |

|   | 9.3    | Append | lix C Code Expansion                    | 77 |

## **List of Tables**

| Table 1 | EHS Performance improvement                       | 10 |

|---------|---------------------------------------------------|----|

| Table 2 | Average CPU ticks discarding start-up costs       | 53 |

| Table 3 | Cold versus warm execution time.                  | 54 |

| Table 4 | CPU Ticks for first run of each benchmark program | 55 |

| Table 5 | Comparison of block counts in benchmark programs  | 55 |

# List of Figures

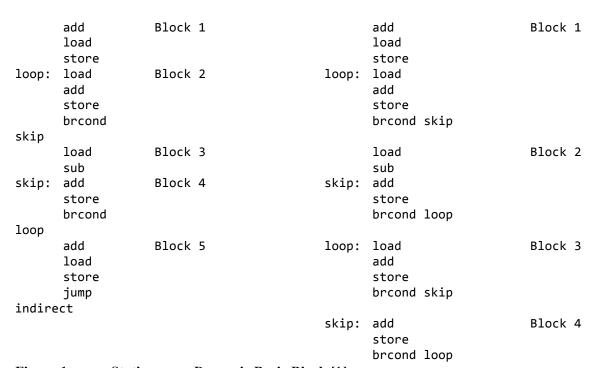

| Figure 1  | Static versus Dynamic Basic Block [1]                               | 6  |

|-----------|---------------------------------------------------------------------|----|

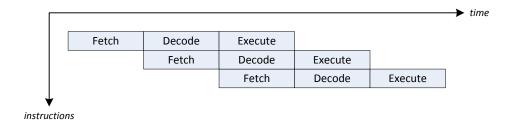

| Figure 2  | Three stage instruction pipeline (ARM 7 TDMI)                       | 18 |

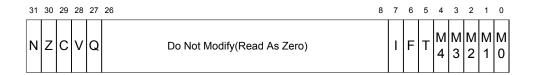

| Figure 3  | Format of the CPSR                                                  | 18 |

| Figure 4  | Conditional execution                                               | 20 |

| Figure 5  | Stack manipulation overhead                                         | 25 |

| Figure 6  | Translation from C# to Expression tree                              | 27 |

| Figure 7  | Translation C# to CIL                                               | 27 |

| Figure 8  | Block expression                                                    | 29 |

| Figure 9  | Accessing simulated registers.                                      | 33 |

| Figure 10 | Expression syntax mapping a source address to a target address      | 34 |

| Figure 11 | A simple instruction translation.                                   | 35 |

| Figure 12 | Indirect branch translation                                         | 36 |

| Figure 13 | Translation of instruction with conditional execution.              | 37 |

| Figure 14 | Translation of flag setting instruction.                            | 39 |

| Figure 15 | Dynamic basic block discovery algorithm                             | 41 |

| Figure 16 | Algorithm to decide when to translate a block                       | 41 |

| Figure 17 | Compiling a translation                                             | 41 |

| Figure 18 | Profiling algorithm                                                 | 43 |

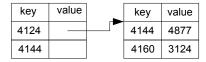

| Figure 19 | Adjacency list                                                      | 43 |

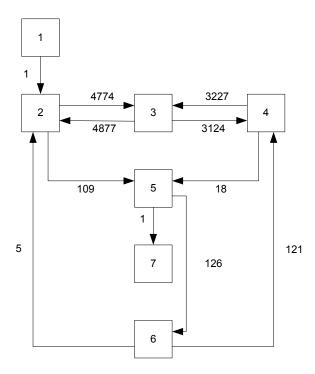

| Figure 20 | Directed weighted graph for bubble sort program                     | 44 |

| Figure 21 | Extended profiling algorithm to detect and create a hot region      | 44 |

| Figure 22 | An Expression.Block implementing a loop                             | 45 |

| Figure 23 | SCCs from bubble sort directed weighted graph                       | 46 |

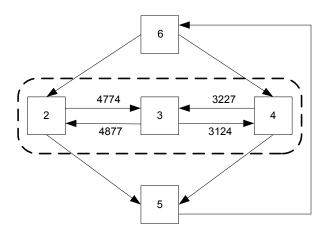

| Figure 24 | Control flow comparison between DBB translation and LTU translation | 47 |

| Figure 25 | .NET Stopwatch class in use                                         | 49 |

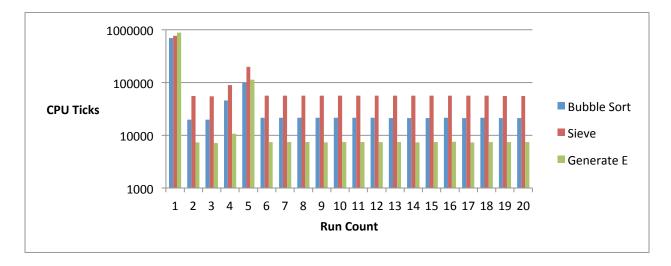

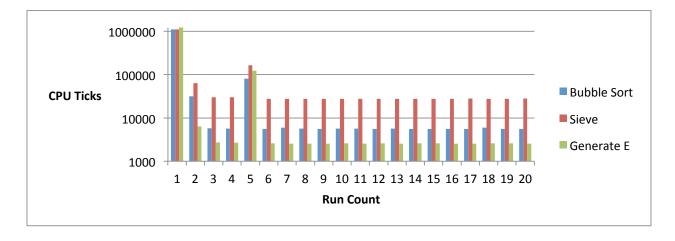

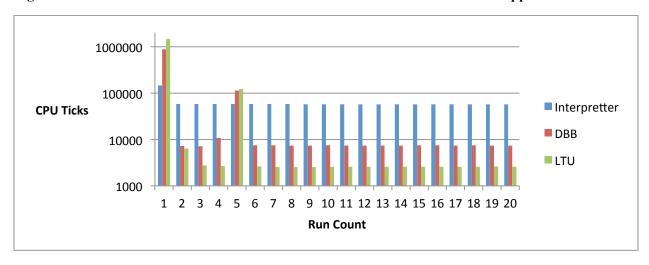

| Figure 26 | Interpreter performance                                             | 50 |

| Figure 27 | Block DBT Performance                                               | 51 |

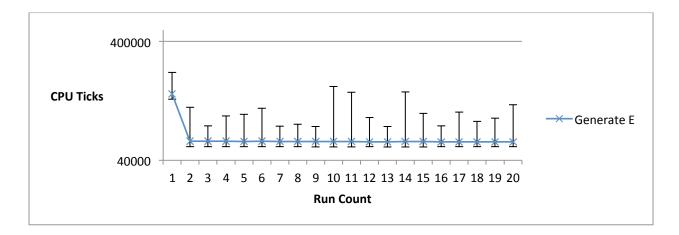

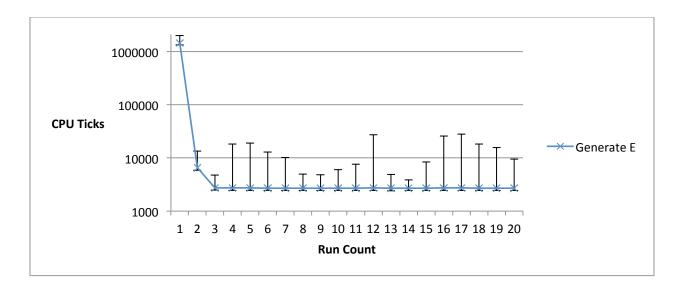

| Figure 28 | LTU DBT Performance                                                 | 52 |

| Figure 29 | Bubble Sort benchmark execution times for different approaches      | 52 |

| Figure 30  | Sieve of Eratosthenes benchmark execution times for different approaches          |        |  |

|------------|-----------------------------------------------------------------------------------|--------|--|

| Figure 31  | Generate E benchmark execution times for different approaches                     |        |  |

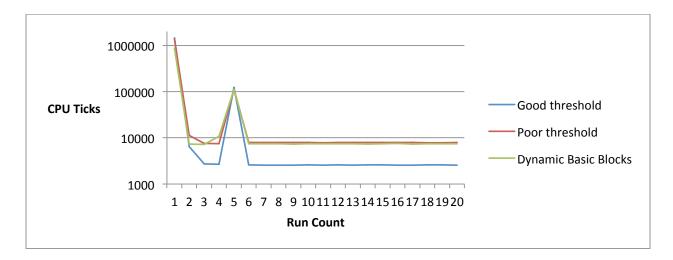

| Figure 32  | Performance effects of different translation threshold values for translating Gen | erate  |  |

| E program  | 56                                                                                |        |  |

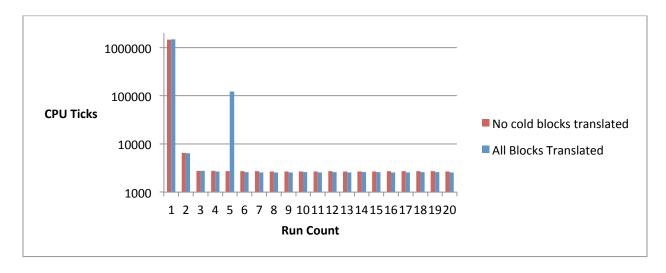

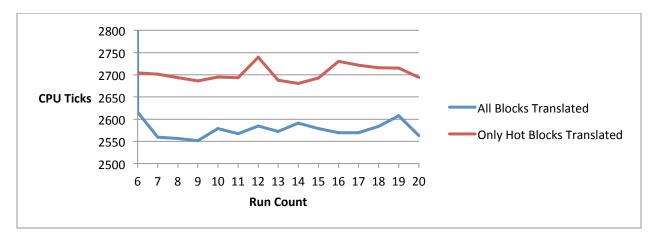

| Figure 33  | Translating all blocks versus only hot blocks                                     | 58     |  |

| Figure 34  | Hot blocks only versus all blocks translated, after final translation             | 58     |  |

| Figure 35  | Minimum, maximum and average execution times for the interpreter running th       | e      |  |

| Generate E | benchmark                                                                         | 59     |  |

| Figure 36  | Minimum, maximum and average execution times for the LTU translator running       | ng the |  |

| Generate E | benchmark                                                                         | 60     |  |

| Figure 37  | CPU Ticks and Garbage Collection                                                  | 60     |  |

| Figure 38  | Execution CPU ticks distribution                                                  | 61     |  |

## **Acknowledgments**

I wish to acknowledge all the people who have helped and guided me during my studies. I would like to express my sincere gratitude to my supervisors, Dr. Nigel Horspool and Dr. Micaela Serra. Lastly I want to thank my family members for their understanding and endless support.

## Dedication

For Jenny.

## 1 Introduction

This thesis investigates dynamic binary translation, which is a particular form of emulation. Emulation may be described simply as the practice of simulating one computer system on another. Emulation is useful for:

- Preservation (the ability to execute programs from an obsolete system).

- New system development develop a system emulator as a precursor to developing the hardware.

- Software development when no hardware is available. E.g. an emulator is built in to Apple Computer's Xcode development environment.

- Education, e.g. the UVic ARMSim#, an emulator for the ARM7TDMI processor.

- Migration, providing the ability to run programs from a previous platform. E.g. Apple

computer provided an emulator for Motorola when they migrated to PowerPC, and again

when they migrated to Intel processors.

- Performance tuning, e.g. an emulator may give access to count clock cycles for memory access and other operations, which can be difficult even when hardware is available.

The goal of this thesis is to develop and describe a high performance, portable emulator for the ARM v4 architecture. An existing interpreter will be extended to create a dynamic binary translator (DBT) that implements some of the techniques discussed in the recent literature. The implemented DBT runs on three platforms<sup>1</sup> and is more than ten times faster than the interpreter when compared using three benchmark programs. These results are achieved without requiring static code analysis.

This thesis will first introduce the area of emulation, followed by a review of the technologies used to implement the dynamic binary translator and the current literature in the area. The implementation of the DBT and the incorporation of concepts from the literature will be described and the results achieved discussed.

\_

<sup>&</sup>lt;sup>1</sup> Microsoft Windows, Linux and Apple Macintosh OSX

## 2 Background

#### 2.1 Emulation

A broad definition of emulation is "the process of implementing the interface and functionality of one system or subsystem or subsystem having a different interface or functionality" [1]. The same authors give another definition, which is more useful for the purpose of this thesis "In terms of instruction sets, emulation allows a machine implementing one instruction set, the target instruction set, to reproduce the behaviour of software compiled to another instruction set, the source instruction set".

Emulation is an important enough area that large corporations have invested time and money to create emulators. This is often done to allow software migration to new hardware, for example Apple Computer provided the Rosetta emulator with OS X v10.4.4 to allow Intel based machines to run software compiled for the earlier PowerPC machines.

There are several common techniques that are used to create emulators. These techniques exist on a continuum of complexity, performance and resource requirements. Interpretation is the simplest, slowest, least resource intensive technique while binary translation lies toward the other end of the continuum requiring more resources but delivering superior performance. Several other techniques including threaded interpretation and pre-coding lie between the two extremes.

#### 2.1.1 Interpretation

Interpretation is a widely used technique for implementing high-level programming languages, for example Perl, Ruby and Python are currently popular interpreted languages. However in the context of emulation the goal is to interpret machine code rather than a high level language. The operation of a simple interpreter may be defined as "stepping through the source program instruction by instruction, reading and modifying the source state according to the instruction" [1].

A simple interpreter may be described as having 3 parts:

- 1. Simulated memory area containing code, data and the stack.

- 2. A context block that stores the simulated state of the source machine.

#### 3. The interpreter codes.

The interpreter operates by loading an instruction from the simulated memory area, decoding the instruction and updating the state and/or memory based on the decoded instruction. This approach is known as a *decode-and-dispatch* interpreter because there is a central loop that *decodes* the instruction and *dispatches* it to a routine that updates the memory and state of the simulated machine [1].

A simple interpreter may be enhanced in several ways. Common approaches include:

- Indirect Threaded interpretation removes the central dispatch loop and replaces it with code to move directly to the next instruction at the end of each instruction interpretation routine. The goal of this is to reduce the number of branch instructions executed. The key component of this technique is the dispatch table, which maps instructions to routines that interpret them. When interpretation of the current instruction is complete the next instruction is decoded and the address of the routine to interpret it is obtained from the dispatch table. This is referred to as indirect threading because of the indirection of the dispatch table.

- When a source instruction is interpreted multiple times, some of the work that is done to extract the meaning of the instruction is repeated. The precoding technique captures this repeated work and stores the instruction in an intermediate form that allows the instruction to be interpreted more easily. The operands and other information from the instruction are extracted into the fields of the precoding. The precoding is based on the instruction type so one precoding may be shared across multiple instructions. The interpreter routine to execute the decoded instruction retains the mechanism from Indirect Threaded interpretation that loads the next instruction, but now the dispatch table stores the pointer to the routine that executes the pre-coded instruction. It has been suggested that this technique is better suited to CISC architectures where the instruction decode is a more complex process due to variable instruction lengths and layouts [1].

- Direct Threaded Interpretation is based on precoding but discards the dispatch table.

Instead of storing the address of the routine to execute the pre-coded instruction in the dispatch table the address of the routine is held in the structure that contains the pre-coded instruction.

## 2.1.2 Binary Translation

Binary translation is the process of converting the instructions of the source program into instructions for the target and update the simulated state of the source machine. Each instruction in the source program is mapped to a specific translation on the target that simulates the operation of the source instruction. Two things separate binary translation from precoding:

- 1. The translated form is directly executable on the target and requires no interpreter routine.

- 2. Each translation fragment maps to a specific source instruction, block or region.

Binary translation is a hard problem in the absence of a high level representation of the source program because all knowledge of the program must be derived from the in memory representation of the source program. In a static context this presents several significant challenges [1]:

- Code discovery

- Code location

- Self referencing code

- Self modifying code

#### 2.1.2.1 Code Discovery

Code discovery is the problem that it is hard to know in any given block of memory exactly which bytes represent code and which represent data. This is a more significant problem with CISC instruction sets, because of the inconsistent instruction lengths and layouts, but is relevant to RISC also. For example the bytes following a jump instruction may or may not be code, or be reachable if they are code.

Some common object/executable file formats separate code and data e.g. the Portable Executable (PE) format on Windows. In the case of the PE format the operating system maps text areas as execute/read-only and data areas as no execute/read write. However there may be read-only data in the text area so code discovery remains an issue.

#### 2.1.2.2 Code Location

Code location is the issue of knowing where in the target memory code is located. The problem can be illustrated with an indirect jump such as the following ARM v4 instruction:

MOV PC, R2

At runtime this causes the processor to branch to the location held in register 2, at translation time the address is usually not known and sometimes cannot be known. We can assume that the contents of R2 is an address in the memory block that contains the code and data. The issue is that the address in R2 is a source address, which means that a mechanism to determine the translated address at runtime must be implemented.

### 2.1.2.3 Self Referencing Code

Self-referencing code is where the program reads data from its code area. This is a variation of the code location problem in that the address that is being read from must be translated to a target address

## 2.1.2.4 Self-Modifying Code

Self-modifying code is code which writes into its code area at runtime, so potentially instructions may change after they have been translated. Again as with the code location problem, it's also necessary to be able to find the correct location to write to.

Data execution prevention (DEP) in modern operating systems normally prevents execution of any writeable memory areas, except for privileged applications such as just-in-time (JIT) compilers. The purpose of DEP is to improve the security of the operating system against attacks such as buffer overflow exploitation.

### 2.1.3 Dynamic Binary Translation

One way to overcome some of these issues is to perform translation on the source program when it is executing with actual data. This is dynamic translation, as code is discovered it is translated.

A simple DBT has several parts [1]:

- An emulation manager that controls the process at a high level.

- An interpreter.

- A binary translator that converts one or more source instructions to one or more target instructions.

- A source code block an address range in memory that contains the code and data of the source program.

- A target code cache.

- A mechanism to map the source program counter to target program counter.

The general procedure is to build some minimal translation unit, which is called by the emulation manager in place of interpreting individual instructions. This minimal translation unit may be described as a dynamic basic block [1], which is defined as a block of instructions that starts with the first instruction executed after a branch or a jump and ends with the next branch or jump instruction. This differs from a static basic block in that it may contain multiple entry points. It also means that a series of instructions may be present in multiple DBBs.

#### **Static Basic Blocks**

## **Dynamic Basic Blocks**

Figure 1 Static versus Dynamic Basic Block [1]

The execution of the translator may be described as follows:

1. From the program entry point instructions are interpreted until execution reaches the first branch or jump instruction.

- 2. The branch or jump instruction ends the dynamic basic block (DBB).

- 3. The DBB may be translated and stored in the translated block cache (TBC). The source program counter to target program counter map is updated to point to the translated block. Now the block can be executed without falling back to the emulation manager between translated instructions.

- 4. Before an instruction following a branch or jump is interpreted the emulation manager checks the TBC for a translation for the address of the next block:

- a. If the address is a miss in the TBC the next block is interpreted until execution reaches a branch or jump instruction which ends the DBB.

- b. If the address is a hit in the TBC the translated block is executed. At the end of the translated block control passes back to the emulation manager.

A primary goal of Dynamic Binary Translation is to significantly improve performance when compared to an interpreter as well as being easier to implement than a Static Translator. While a DBT may require additional memory to store the translated code cache and extra execution time to create the translated instructions it has performance potential well beyond the interpreter. DBT has been widely used to implement emulators [2] including:

- Apple Computer, M68K to PowerPC

- Transitive Corporation, QuickTransit Motorola Power PC to Intel x86 (also SPARC to x86, x86 to Power Architecture)

- DEC, FX!32 x86 to DEC Alpha

- HP ARIES, HP 9000 HP-UX to HP Integrity HP UX 11i

- Sun Microsystems Wabi x86 to SPARC

## 3 Previous Work

Current work in dynamic binary translation is focused in several areas:

- The reduction of the overhead associated with binary translation [3], [4].

- The ability to target many different kinds of applications without being limited to static program code [5].

- The ability to observe the simulated system state at any point during a simulation [6].

- The ability to easily change the target architecture from one instruction set architecture (ISA) to another [7].

However the main focus of research is on improving the performance of binary translation through reducing the associated overhead. This overhead has been characterized in several ways:

- The overheard is made up of translation overhead and execution overhead. Most processor time is spent executing translated code so optimizing the translated code to reduce the execution overhead is important [4].

- A less generalized view of the overhead is that it is comprised of overhead from initialization, cold code translation, profiling, and hot trace building, all of which should be targeted to reduce their impact [3].

- Another view is that there is overhead in translating code and in executing translated code and a balance must be struck between the two. Up to some limit improving the quality of the translated code pays off with a reduction in overall execution time [8].

## 3.1 Reducing Translation Overhead

While this is described as needing to be balanced with the execution overhead, there appears to be very little work being done to reduce it. One way to reduce the translation effort is to simply translate only the 'hot' blocks [9], [6].

## 3.2 Reducing Execution Overhead

The approaches to improving the quality of translated code are many and varied, some address improving the efficiency of running the translated code, others address the issue of code expansion and attempt to reduce the number of target instructions that are generated for each source instruction. Proposed approaches for reducing execution overhead include:

- Increase translation unit size

- Shadow stacks

- Indirect branch target caching/software indirect jump prediction

- Duplicate and rearrange code

- Map source registers to target registers

- Optimize condition code handling

- Take advantage of powerful instructions in the target ISA that may replace several source instructions

- Cache decoded instructions for reuse by the interpreter

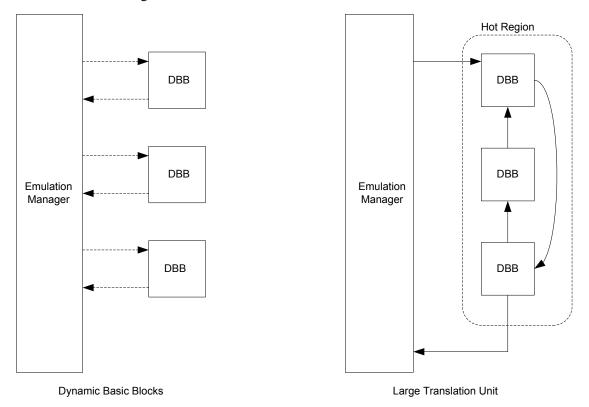

The first three of the above can be grouped together as mechanisms to reduce calls to the emulation manager. The emulation manager in a binary translator performs a similar role to the dispatcher in an interpretive simulator. When a translation unit's execution is completed the emulation manager determines whether execution can continue from the translation cache or whether further source code must be translated.

#### 3.2.1 Translation Unit Size

A common approach to reducing calls to the emulation manager is to execute larger units of code. Larger units of code may improve performance in two ways:

- 1. Give fewer points at which to return to the emulation manager (minimize context switching).

- 2. Provide the compiler of the translated code greater scope for optimization (improve code quality).

While some DBT systems have used single instructions [5] as the translation unit, it is more common that the unit of translation is the basic block, [6], [9] or dynamic/extended basic block [10], [11].

Generating larger translation units is an active area of research. The general approach is to profile the execution of the program and monitor the number of times that each basic block is executed. Blocks that are executed more times than a configurable threshold value are marked as hot blocks. Various-schemes have been proposed for making use of the hot block profile.

The Edinburgh High-speed Simulator (EHS) implements four execution modes to investigate the effects of translation unit size [12]. The system maintains a counter to track the total number of interpreted blocks and only performs translation after some number of blocks have been interpreted. They refer to the interval between two successive translations as an epoch. During an epoch the simulator builds an execution profile for each physical page. The baseline mode counts the number of times each block on the page is interpreted and translates the 'hot' blocks. This is referred to as basic block (BB) mode. There are three additional large translation unit (LTU) modes with translation units of increasing size. In LTU mode a control flow graph (CFG) is created for each physical page, the page may contain several separate CFGs, one or more combined CGs or a combination of separate and combined CFGs. The first increment of translation unit size use strongly connected components (SCC) as translation units. An SCC is a collection of basic blocks that have hot control flow graph (CFG) arcs between them, and any attached linear regions. Tarjan's algorithm is used to extract the strongly connected components from the page. The next increment in translation unit size is the CFG where each CFG within the page forms a translation unit. The final translation unit is the page that contains one or more CGFs. The page LTU has the best simulation performance, but the performance difference between the large translation unit approaches is minimal.

| Translation Unit | Performance Improvement over BB |

|------------------|---------------------------------|

| SCC              | 1.63                            |

| CFG              | 1.64                            |

| Page             | 1.67                            |

Table 1

EHS Performance improvement

A similar approach is to create hot regions, which are arbitrary CFG sub-graphs constructed from hot basic blocks and the blocks neighboring them that are also hot [13] [8].

Another mechanism is to patch the end of a translated block with a jump to the start of the next BB [14], [15]. This may be the simplest approach since no profiling is involved. A similar approach is lazy block linking, where blocks are only linked together when a context switch occurs [16].

A significant difference between these approaches is whether the large execution units are formed by joining together smaller translation units [13] or compiled directly to larger translation units [12].

Creating dynamic basic blocks often results in code duplication as more than one entry point may exist to the same piece of code. This code duplication has been measured and found to only increase the generated code size minimally [4], [13].

#### 3.2.2 Shadow Stack

When a function is called the return address is usually stored in a register or pushed onto the stack to enable the epilogue of the called function to jump to the saved location. In a DBT returning from a function call may entail returning to the emulation manager to determine the address of the next instruction to execute. The shadow stack is a mechanism to avoid the cost of mapping the source return address to the target return address when returning from a function call. The address of the translated block to return to is saved on the shadow stack, while the address of the source address to return to is stored in the source stack. On return from the function call, if the address from the shadow stack matches the translation of the address from the source stack, the target address from the shadow stack can be used to access the next translated block directly. If the addresses don't match or there is no translated block for the address, then the call goes to the emulation manager [1], [16]. The shadow stack technique is only applicable to DBTs that maintain both a source program counter and a target program counter (TPC). Many of the DBTs that are JIT compiled do not maintain a TPC [6], [11]. This idea can be extended to preemptively translate the code at the return site if it has not already been translated [17].

## 3.2.3 Indirect Branch Target Caching/Software Indirect Jump Prediction

Software indirect jump prediction exploits the observation that indirect branch targets seldom or never change. By profiling the execution of the code the common destinations for an indirect branch may be recorded and used to directly access the translated block. The simulation can fall back to the emulation manager if the target is an address that has no translation. This can be achieved by adding a series of if statements that check the return address to the end of the function body [1]. A similar but more expensive operation at run time is to use the indirect

branch target address to look up Target PC values which allows the translated branch target to be executed directly without returning to the emulation manager [17], [16].

## 3.2.4 Map Source Registers to Target Registers

A simple way to manage the translation of source registers is to map them to memory. However this causes significant overhead as each read or write from a register requires a memory operation. One way to avoid this overhead is map source registers directly to target registers for each register use in a basic block [14], or within a region [8].

### 3.2.5 Optimize Condition Code Handling

Simulating the condition code flags in memory incurs significant overhead in a similar manner to simulating registers in memory. It is possible to avoid this overhead if the effect of the instruction on the condition code flags in the source ISA matches the behavior in the target ISA [8].

## 3.2.6 Take Advantage of the Target ISA

In some case the target ISA contains powerful instructions that may map to several source ISA instructions. For example in the ARM v4 ISA the MLA maybe used to simulate the sequence of MUL and ADD instructions in the Intel x86 ISA. Patterns of instructions in the source ISA suitable to be mapped to a single target instruction may be found by constructing directed flow graphs for each basic block and the searching for sub-graphs that match the pattern that can be replaced by a single instruction [18].

### 3.2.7 Cache Decoded Instructions

In general there is little mention in the literature of the interpretation stage of DBT. However, one scheme for improving the efficiency of the interpretation stage is to cache the decoded instructions for future use, saving the cost of repeated decodes [6].

## 3.3 Alternatives to Dynamic Binary Translation

As discussed previously performing binary translation in a static context has a significant number of challenges. Combining static and dynamic binary translation can overcome the difficulties of creating a static translation and create a translation with performance that exceeds a typical dynamic binary translator.

## 3.3.1 Hybrid Static/Dynamic Translation

One approach to combining dynamic and static translation is to statically decode the program, adding instructions into a single translation unit until a branch to a location that cannot be statically determined is encountered. When the entire program has been translated and is executing, dynamic branches are profiled and if the destination of the branch is not in the current translated block a 'miss' is generated. If a sequence of instructions generates too many misses it is recompiled using the collected branch destination information [11].

## 3.3.2 Hybrid Instruction Set Compiled Simulation

Another approach to combining static and dynamic translation is to perform a static analysis to create a decoder for each type of instruction that is discovered in the program [19]. The compiler optimizes the decoder for each instruction type when the translator is compiled. The compilation time for the translator for the program is minimized because only the instructions discovered in the program have translators compiled, not the whole of the ISA. At run time instructions are executed one at a time giving the flexibility of interpretive simulation.

## 3.4 The ARM v4 Instruction Set Architecture and Binary Translation

The ARM ISA has several features that provide additional challenges for binary translation [20].

#### 3.4.1 PC Relative Addressing

PC relative addressing is an instance of the code discovery problem. Large constants may be loaded from the text section by using the PC as the base address for the LDR (Load Register) instruction. The PC that is used must be the source PC. PC relative addressing may also be used to implement switch statements [20], [17].

### 3.4.2 Shifter Operand and Shifter Carry Out

The ARM v4 ISA provides several addressing modes for instruction operands, as described in section 4.1.2.8. While some of these modes generate an operand from a straightforward immediate or register value, others may apply one of several shift operations to generate the operand value. Instructions using an addressing mode that is performing a shift to calculate the operand value require additional code in the translation to perform the shift. Using this type of addressing in an instruction also sets the C flag if there is a Carry Out from the shifter operand. So translated code also has to provide a mechanism to set the C flag [20].

## 3.4.3 Condition Flags

Many instructions in the ARM ISA may set the condition codes, the comparison instructions, CMN, CMP, TEQ and TST, as well as arithmetic, logical or move instructions. Exactly how the flags are set depends on the instruction. Flag setting introduces considerable translation overhead to any instruction that sets the flags. The translator requires additional functionality to handle the specific flag setting for the various instruction groups [20].

#### 3.4.4 Conditional Execution

Nearly all instructions in the ARM v4 ISA contain a conditional execution prefix as described in section 4.1.2.1. This prefix determines if the instruction will be executed based on the settings of the flags in the Current Program Status Register (CPSR), described in section 4.1.1.3. The action of checking the CPSR flags can introduce a considerable overhead to the translation of any particular instruction. The number of flags checked depends upon the particular condition code. Any instruction that has a condition code prefix other than "always" requires that the translator generate code that implements the condition code check. On some other architectures similar condition code mechanisms exist and there may be ways to use the target architectures condition code flags to emulate those of the source architecture, in place of generating a translation that checks the simulated CPSR [8].

## 4 "An Approach to Dynamic Binary Translation"

In this thesis we investigate the specific case of implementing a portable dynamic binary translator for the ARM v4 ISA. The translator is portable because it runs on both the Microsoft .NET Common Language Runtime (CLR) and the Mono open source implementation of the ECMA C# and CLR standards. Mono is supported on the Linux, OS X and Windows operating systems<sup>2</sup>. The translator implements the usual features of a DBT as well as some of the optimization techniques described in Chapter 3 Previous Work that are suited to CIL as a translation target, including:

- Large translation units

- Code layout changes

- Code duplication

- Conditional execution optimization

- Branch condition inversion

The ARMSim#³ emulator previously developed in the Department of Computer Science at the University of Victoria was implemented in C# on Microsoft's .Net platform. The interpreter extracted from ARMSim# provided a readily available starting point to develop a DBT from. Choosing to use the ARMSim# interpreter made using the same development environment the default choice. In turn, choosing to develop the DBT using CIL as the target constrained the implementation in other ways. Many of the techniques outlined in Chapter 3 Previous Work are not suited to an intermediate language as a translation target or cannot be readily implemented on a stack machine.

Register mapping is not a useful technique in this context as there are no registers to map

to.

<sup>&</sup>lt;sup>2</sup> http://www.mono-project.com/Main\_Page

<sup>&</sup>lt;sup>3</sup> ARMSim# is an ARM7TDMI emulator that provides simulation of state including the 16 general purpose registers and the CPSR, the L1 Cache, both code and data, main Memory, and the Stack. ARMSim# also includes an assembler and a linker, so that when a file is loaded it is automatically assembled and linked [40].

• CIL does not contain powerful instructions that multiple ARM assembler instructions may be mapped to.

The approach taken in this thesis combines several techniques from Chapter 3. Instructions are translated in isolation and combined to form DBBs. DBBs are coalesced to form large translation units that span hot regions in the control flow graph.

The particular combination of translating to an intermediate language for a virtual machine and forming large translation units from hot traces does not seem to appear in the literature.

#### 4.1 The ARM v4 Architecture

Implementing a translator for the ARM processor requires some understanding of the features of the device that a programmer may use. There are many versions of the ARM architecture. This thesis describes a translator for the ARM7TDMI processor, which implements the ARM v4 architecture. The ARM is a RISC processor [21] and as such implements these typical features:

- The instruction fields have fixed lengths and are uniform across different instructions. Instruction decoding is simplified because the same mechanism can be used to decode different instructions, wherever instructions share the same layout. For example all data processing instructions share the same addressing mode options in the shifter operand.

- Addressing modes are simple with the address for the load or store instructions being determined from a combination of values in registers and immediate values in the instruction.

- A large uniform register file, which means there are a large number of registers and they are all a uniform 32 bits.

- A load/store architecture, which means that instructions do not manipulate memory directly, rather instructions manipulate registers. Memory is loaded into registers, manipulated by instructions and stored from registers back to memory.

## 4.1.1 Programmer's Model

#### 4.1.1.1 Modes

There are seven processor modes in the ARM architecture, for the purpose of this thesis we are only interested in User mode, which is normal program execution mode. The other six modes are generally only used by the operating system.

#### 4.1.1.2 Registers

Although the ARM processor has 31 general-purpose registers, only 16 are visible to the programmer in user mode. The remaining non-visible registers are used for speeding up exception processing [21]. Exceptions are outside the scope of this thesis so I will not mention them further. The use of the registers is defined by the ARM calling convention [22] as follows:

- Registers 0 to 11 or 12 are available for the use of the programmer

- Register 12 is the intra procedure call scratch register (IP)

- Register 13 is by convention used as the stack pointer (SP)

- Register 14 is the Link Register (LR) used to hold the return address of the Branch and Link instruction, which is used when making a function call

- Register 15 is the program counter (PC)

The programmer may change the PC directly; this is sometimes described as the program counter being exposed [17]. Changing the PC directly is the equivalent of a branch instruction. However the PC should only be read or written according to the specified rules. [21][A2-7] ARM v4 and earlier have a three-stage instruction pipeline so the PC contains the address of the next instruction to fetch, two instructions after the instruction being executed. <sup>4</sup>This is important for calculating branch destinations when translating instructions [21][A1-5].

Each column in Figure 2 represents a single clock cycle, so in each cycle the processor:

- Fetches an instruction.

- Decodes the instruction fetched in the last clock cycle.

- Executes the instruction fetched two cycles ago.

<sup>&</sup>lt;sup>4</sup> More recent versions of the architecture have deeper pipelines, but the 2 instruction offset is maintained for reasons of compatibility

Figure 2 Three stage instruction pipeline (ARM 7 TDMI)

## 4.1.1.3 Current Program Status Register

The current program status register (CPSR) shown in Figure 3 is a special purpose register outside of the general-purpose registers 0 through 15. The bits of interest in the CPSR are the highest 5 and the lowest 8 (bits 8 through 26 are defined as Do Not Modify).

Figure 3 Format of the CPSR

Bits 31 to 28 are the condition code flags, N, Z, C and V. These flags are modified by comparison instructions, as well as arithmetic, logical and move instructions. Many of the arithmetic, logical and move instructions may be flag setting or flag-preserving depending on whether the instructions S bit is set. If the S bit is set:

- The N flag is set to 1 if the result of the instruction is negative when viewed as 2's complement signed integer. Otherwise the N flag is 0.

- The Z flag is set to 1 if the result is zero; otherwise it is set to 0.

- The C flag is set in one of four ways depending on the instruction. The C flag is the carry flag, so if the operation would have produced a carry then the flag is set.

- The V flag is the overflow flag and is generally set if an operation causes a signed overflow, but it may be set for other reasons.

Bit 27 is the Q flag and is used in some variants of the ARM architecture that support Enhanced DSP Extensions.

The bottom 8 bits of the CPSR are known as control bits. The I bit and the F bit enable and disable interrupts, the T bit is set when in thumb mode which is an alternative operation mode supported by the ARM processor that uses 16 bit instructions. The M bits indicate the processor mode. The control bits are not modifiable in User mode code so they will not be discussed further

### 4.1.1.4 Memory

In the ARM architecture v4 memory is a single address space of  $2^32$  8 bit bytes, with unsigned integer addresses from 0 to  $2^32 - 1$ . This address space may also be viewed as  $2^20$  32 bit words aligned on 4 byte boundaries.

#### 4.1.1.5 Data Types

The ARM processor itself supports 3 data sizes:

- 1. Word, which is normally aligned to 4 byte boundaries. The 4 bytes making up the word with the address A, are at A, A+1, A+2, A+3.

- 2. Half-Word, which is normally aligned to 2 byte boundaries.

- 3. Byte.

The data types are extended to include double word values when the floating point coprocessor is present and quad word values when the DSP unit is present.

#### 4.1.1.6 Memory Alignment

The ARM processor operates most efficiently when data access is aligned, the address for a word is word-aligned and the address for a halfword is halfword-aligned. The assembler provides a directive for the programmer to align data. Alignment is not compulsory but there is a performance penalty for unaligned access.

#### 4.1.2 Instructions

Version 4 of the ARM architecture supports two different instructions sets. By default instructions are 32 bits. However there is a second instruction set, called the Thumb instruction set which is a re-encoded 16 bit subset of the 32 bit instruction set. The Thumb instruction set is not in the scope of this thesis.

The Architecture Reference Manual [21] [A1-5] states "The ARM instruction set can be divided into six broad classes of instruction":

- Branch instructions

- Data-processing instructions

- Status register transfer instructions

- Load and Store instructions

- Coprocessor instructions

- Exception-generating instructions"

#### 4.1.2.1 Conditional Execution

Before considering the classes of instructions it is important to note that most instructions may be executed conditionally. The top 4 bits of nearly all instructions is the condition code. This code determines which flag or combination of flags from the CPSR must be checked in order for the instruction to be executed.

```

Loop:

CMP r1, #0

SUBGT r1, r1, #1

BNE loop

Figure 4 Conditional execution

```

The small loop shown in Figure 4 demonstrates conditional execution. The compare (CMP) instruction sets the flags in the CPSR based on the results of the comparison as follows:

- N flag is set to the MSB of the result of r1 0

- Z flag is set if r1 0 = 0

- C flag is set if  $r1 0 \ge 0$

- V flag is set if r1 0 generates a 32 bit signed overflow<sup>5</sup>

The SUBGT instruction is conditionally executed on checking the flags in the CPSR. For GT the flags are checked as follows:

• Z flag is clear

<sup>&</sup>lt;sup>5</sup> Subtraction causes an overflow if the operands have different signs, and the first operand and the result have different signs. (Seal, 2000)

## • N flag equals V flag

Before the BNE instruction is executed the flags in the CPSR are checked as follows:

• Z flag is clear

The default condition code prefix is *always* (mnemonic AL) which instructs the processor to execute the instruction regardless of the setting of the flags. The remaining 14 conditions cover:

- Tests for equality and non-equality.

- Tests for <, <=, > and >+ inequalities in both signed and unsigned arithmetic.

- Each flag to be tested individually.

### [**21**][A1-5]

One purpose of conditional execution is to reduce the number of branch instructions. Reducing branches is beneficial because they cause the instruction pipeline to be flushed. A conditional instruction that is not executed is equivalent to a no operation (NOP) instruction [21].

### 4.1.2.2 Branch Instructions

The ARM processor has several different branch instructions as well as allowing direct setting of the program counter which has the same effect as a branch (There are very specific rules as to how the program counter may be changed).

- 1. B is the plain branch instruction.

- 2. BL is the branch and link instruction, effectively a subroutine call. Setting the L bit causes the instruction to save the return address in the link register (register 14). At the end of the subroutine the link register can be copied into the program counter to return from the subroutine.

- 3. BX is the branch and exchange instruction, this instruction branches to a destination that is held in a register. This instruction allows the option of changing into Thumb mode.

The other significant difference between 1-3 and 4 above is that 1-3 branch to an immediate value that is encoded in the instruction, whereas 4 is indirect and branches to a destination held in a register.

## 4.1.2.3 Data Processing Instructions

There are 16 data processing instructions, which perform operations including addition, subtraction, logical and, logical or etc. All the data processing instructions, except for move and move negative, take two source operands. The first source operand is always a register. The second source operand is called the shifter operand and is calculated using one of eleven modes. All the data processing instructions may update the condition code flags in the CPSR depending on whether the S bit is set. Exactly how the flags are set is specific to the instruction.

#### 4.1.2.4 Status Register Access Instructions

These two instructions allow the value of the CPSR to be loaded into a register or updated from a value in a register.

#### 4.1.2.5 Load and Store Instructions

Load instructions retrieve a value from memory into a register, store instructions save a value from a register to memory. The instructions come in two forms:

- 1. Operates on 32-bit word or 8-bit unsigned byte values

- 2. Loads or stores 16-bit unsigned halfwords and loads 8-bit byte or 16-bit halfwords with sign extension.

Similarly to the data processing instructions the load and store instructions have several addressing modes available to determine the memory address to read from or write to.

#### 4.1.2.6 Coprocessor Instructions

The ARM processor has a set of instructions specifically for communication with coprocessors. These instructions fall outside the scope of this thesis.

#### 4.1.2.7 Exception-Generating Instructions

The binary translation application described in this thesis makes minimal use of the software interrupt instruction (SWI) to terminate a program. The SWI instruction is normally used to allow user mode to transfer control to privileged Operating System code. Breakpoint (BKPT) is the other exception generating instruction; this instruction is not available in the translator described in this thesis.

### 4.1.2.8 Addressing Modes

In the ARM v4 architecture there are five addressing modes associated with five different classes of instructions.

- Mode 1 Data processing operands

- Mode 2 Load and store word or unsigned byte

- Mode 3 Miscellaneous Loads and stores

- Mode 4 Load and store multiple

- Mode 5 Load and store coprocessor

#### 4.1.2.9 Setting of CPSR Flags Depends on Specific Instruction:

The MOV instruction sets the flags in the following manner:

- N Flag = MSB of destination register

- Z Flag = if destination register == 0 then 1 else 0

- C Flag = shifter carry out

- V Flag unaffected

Whereas the SUB instruction does the following

- N Flag = MSB of destination register

- Z Flag = if destination register == 0 then 1 else 0

- C Flag = NOT *Borrow From*<sup>6</sup>(operand a operand b)

- V Flag = Overflow From<sup>7</sup> (operand a operand b)

However, how instructions set the flags fall into several groups so that it is possible to maintain a small collection of methods to generate the flag checking translations.

<sup>&</sup>lt;sup>6</sup> "Returns 1 if the subtraction specified as its parameter caused a borrow (the true result is less than 0, where the operands are treated as unsigned integers), and returns 0 in all other cases. This delivers further information about a subtraction which occurred earlier in the pseudo-code. The subtraction is not repeated." (Seal, 2000)

<sup>&</sup>lt;sup>7</sup> "Returns 1 if the addition or subtraction specified as its parameter caused a 32-bit signed overflow. Addition generates an overflow if both operands have the same sign (bit[31]), and the sign of the result is different to the sign of both operands. Subtraction causes an overflow if the operands have different signs, and the first operand and the result have different signs." (Seal, 2000)

This is a very brief outline of the ARM processor. For further information, refer to the ARM Architecture Reference Manual [21].

As discussed at the start of this chapter the previously implemented ARMSim# interpreter runs on Microsoft's .NET platform. This made the most obvious choice of target instruction set one of the dynamic code generation technologies supported on the .NET platform. The ability to easily generate and execute code dynamically also makes the .NET framework attractive as a translation target. The .NET framework provides several mechanisms for generating dynamic code:

- 1. CodeDOM

- 2. Reflection.Emit

- 3. ExpressionTrees

#### 4.1.3 CodeDOM

The CodeDOM is a library of types that provide representations for many types of source code items. A multi-step process allows using this library to create assemblies that can be stored in memory (or on disk) and executed dynamically.

While CodeDOM has been used as a translation target for binary translation it's a poor choice if simulation performance is an important goal. CodeDOM requires the use of a high level language such as C# as the translation target and each source instruction may generate as many as 1500 native target instructions [11].

#### 4.1.4 Reflection.Emit

Another possibility for generating code dynamically is the System.Reflection.Emit library. A major benefit of using IL as the translation target is that it allows access to all of the features of the CLR. Using IL it is possible to generate methods, classes and assemblies. Assemblies may be saved to disk, as well as executed dynamically.

However using CIL directly makes the job of the programmer considerably more difficult for two reasons. The first is that it is hard to ensure the correctness of the CIL, "... unfortunately Reflection.Emit makes it very easy to generate invalid IL ..." and "But the correctness and validity of IL is a far more subtle matter" [23].

Because the emitted CIL is not available until runtime, the only way to investigate the validity of the generated code is to capture the emitted output using WinDBG or a similar console debugger.

The second challenge with emitting CIL directly is that while the ARM processor is a register machine, the CLR is a stack machine. This means that the process of translating ARM instructions to CIL is a two part process where the instruction must be translated to the equivalent CIL instruction or instructions, but also the register manipulation performed by the instruction must be translated to the equivalent stack machine sequence. This introduces a large amount of code overhead to each translated instruction that the programmer is responsible for<sup>8</sup>.

```

CIL

ARM Asm

sub r1, r2, r3

Ldarg 0

// push reference to class instance

Ldfld, _registerInfo

// push ref to the registers array

Ldc_I4, (int)rd

// push index of rd

Ldarg 0

// push reference to class instance

// push ref to the registers array

Ldfld, _registerInfo

Ldc I4, (int)rn

// push index of rn

Ldelem U4

// push the value from rn

Ldarg 0

// push reference to class instance

Ldfld, _registerInfo

// array info

// push index of rm

Ldc_I4, (int) rm

Ldelem U4

// push the value from rm

// perform subtraction

Sub

Stelem, typeof(uint)

// store element in rd

Figure 5

Stack manipulation overhead

```

Figure 5 shows the translation of a simple subtraction instruction to CIL. Translating to the stack machine requires inserting instructions to configure the stack from the simulation context block, performing the desired operation and storing the result from the stack back to the context block. The stack machine nature of this code can be seen in that the initial items pushed onto the stack are the register array and the index of the register in which to store the result, and the last instruction stores the result

An obvious limitation of translating one instruction at a time is that the stack is reconfigured for each instruction, generating overhead when the results from one instruction and that state of the stack may be useful to the next instruction – hence the idea of translating blocks of instructions

<sup>&</sup>lt;sup>8</sup> See Appendix C for an example of code expansion due to simulating register access and CPSR flag setting and checking.

rather than isolated instructions. In practice this may require two passes to generate the IL, removing redundant store and load instructions on a second pass.

The emitted CIL is used to can be used in various ways. Used in the most minimal way it can generate a dynamic method, which is stored in memory and discarded when it is no longer required. Alternatively it can be used to generate an assembly containing modules, types and methods that may be saved to disk and used outside the scope of the currently executing program.

In contrast with the high level code generated by the CodeDOM the IL generated by Reflection. Emit is at a similar level of abstraction to the source ARM assembly code. The number of instructions required to emulate a specific ARM instruction may be significant, especially if the condition codes are involved but it still generates many, many fewer instructions than the CodeDOM [11].

## 4.1.5 Dynamic Language Runtime

The Dynamic Language Runtime (DLR) [24] is a library that sits on top of the CLR and provides a set of runtime services for supporting dynamic languages<sup>9</sup>. These services include:

- Expression trees which are used to represent the semantics of a programming language.

- Call site caching, which is a mechanism where operands and operations are cached so that if the same operation and operand types are seen subsequently the cached version can be used. This saves repeatedly looking up the same method.

- Dynamic object interoperability, a set of classes and interfaces is provided that enable representation of dynamic objects and operations by language implementers.

### 4.1.5.1 Expression Trees

Expressions and Expression Trees form the basis of the translation mechanism in the binary translator described in this thesis. Expressions are implementations of the abstract Expression class. The System.Linq.Expressions namespace contains a large number of Expression classes that implement various programming language constructs. It also includes an Expression class that provides static factory methods to create the various node types. E.g. The Expression.Add

<sup>&</sup>lt;sup>9</sup> Examples include Ruby, Python, Lisp, Smalltalk, Lua and many more.

factory method creates an instance of the BinaryExpression class that represents an addition operation without overflow checking. A key feature of expressions is that any operands of an expression are themselves expressions. This enables representing any source code as a tree of expression objects. An additional advantage to using the Expression class is that the class manages the IL stack transparently.

An expression tree is a tree of objects where each node in the tree is an instance of an Expression object. An Expression tree is "also a representation of a program that can be manipulated at runtime" [25].

For example Figure 6 shows a simple C# assignment translated to an Expression tree.

Figure 6 Translation from C# to Expression tree

To obtain an expression that represents the field in the class, the Expression. Field method requires a reference to the class that contains the field, which is supplied by Expression. Constant(this). The field itself is accessed via a FieldInfo object, which has been created previously. Expression. Constant(1) supplies the value to assign to the field and the Expression. Assign on the outside performs the assignment of the constant to the field.

The expression syntax compares favorably to the CIL syntax for the same operation shown in Figure 7.

Despite the fact that the expression tree code is making 4 calls to CLR API functions there is little or no difference in the performance between the two implementations. This was determined empirically by writing a small test program to repeatedly assign a value to a field. The variability

between runs exceeds the difference between the two implementations. See Appendix B for a small test program demonstrating this.

To execute an Expression tree, it is compiled into a delegate, which can then be called. A delegate is a type safe callback mechanism, or put more simply 'a handle to piece of code that can be called' [25]. The delegate provides C# with a mechanism that is similar to a function pointer in C/C++. A delegate can also be defined as a class that holds a reference to a method. The signature of the delegate must match the signature of the method.

## The delegate may be:

- Created at runtime.

- A custom delegate provided by the programmer.

- One of the generic delegate types provided by the runtime. Two categories of generic

delegate types are available, Func<T> delegates which return a value and Action<T>

delegates which do not.

The CLR executes the delegate by calling its invoke method. A delegate can have several methods chained to it, both static and instance methods.

```

var assignDelegate = Expression.Lambda<Action>(assignExpression).Compile();

assignDelegate();

```

The Compile method generates CIL that is available to be JIT compiled when the delegate is called.

One of the primary purposes of expression trees is to implement dynamic programming languages. This also makes them ideal for creating a DBT. Both IronRuby<sup>10</sup> and IronPython<sup>11</sup> are implemented on the DLR, and work in a similar manner. Both use a tokenizer and a parser to generate an abstract syntax tree that is either an expression tree in the case of IronPython, or converted into an expression tree in the case of IronRuby. In these dynamic languages the expression trees are first interpreted, to reduce the start up time, before being compiled.

<sup>10</sup> http://ironruby.codeplex.com

<sup>11</sup> http://ironpython.net

In the case of DBT on the CLR the Expression tree simplifies implementing the instructions from the target language because there is no need to translate from the register architecture of ARM assembler to the stack architecture of the CLR's IL. The JIT compiler manages the stack.

# 4.1.5.2 Nested and Block Expressions

The Expression tree syntax becomes difficult to read once expressions exceed a certain size, however the combination of the fact that most Expression methods take at least one Expression parameter and that the Block Expression allows expressions to be grouped means that simple expressions may be combined to form more complex ones.

Figure 8 Block expression

## 4.1.6 How the Dynamic Code is Executed

Both Reflection.Emit and Expression trees can be used to add methods to the existing assembly. These methods are compiled to native code by the CLR's just-in-time compiler when the method is called. The CodeDOM is a much less dynamic approach requiring the creation of an assembly containing a class.

### 4.2 CLR Optimization

A significant benefit of targeting a runtime such as the CLR is the optimizations that the runtime itself provides. The optimizations provided by the runtime also improve as new versions are released. There have been significant improvements to the CLR between .NET 2.0 and .NET 4.5.

This is not an exhaustive list, but rather some of the documented optimizations included in the CLR JIT compiler [26], [27]:

• Multi-core JIT [27] Added in .NET 4.5, when an application is started a background thread running on a different processor is also started to perform JIT compilation. The goal of running the compilation on a separate thread is to avoid the compilation overhead

in making method calls. When a method is required in the application, it has already been compiled on the background thread. To know which methods are required by the application and in what order the application generates an execution profile that is stored. The execution profile is used by the background thread to determine which methods to compile and the order in which to compile them.

- Method inlining. The method call is replaced by the body of the method. The CLR has many rules governing which methods may be in-lined, which vary with the specific version of the CLR. The trend has been to allow more inlining of methods between the initial release of the CLR and the latest .NET 4.5 release.

- Assertion propagation (what is known to be true), this is a generalization of constant propagation.

- Constant folding, e.g. y = 3 \* 2 is changed to y = 6 by the compiler.

- Branch straightening via prediction which is reordering of code so that the likely path taken in a branch is moved to the fall through position [26].

- Tail call, if the last code element in method1 is a call to method2 call then the stack frame of method1 may be reused by method2 rather than adding another frame to the stack. This optimization may be shared between the language to IL compiler and the JIT IL to native compiler by the language compiler creating IL code that the JIT compiler is more likely to apply the tail call optimization to [28].

- Value type handling has been improved by implementing "value type scalar replacement" which is essentially converting value types that are suitable into a collection of scalars. Other improvements have been made that allow methods with value type parameters, local variables or return value to be inlined [29].

# 4.3 Challenges

There are three major challenges to resolve in order to implement a DBT for ARM v4 ISA with CIL as a target.

## 4.3.1 Hardware Simulation Challenges

At first glance the translation from one instruction set to another might seem quite straightforward, however in the case of ARM v4 assembler to the System.Linq.Expression syntax there are a number of challenges. Many of these challenges are simply challenges of

dealing with code expansion; a single ARM instruction may expand into tens of Expressions. This code expansion is generally driven by the need to simulate features of the ARM v4 ISA in software:

- Since CIL is executed on a stack machine the registers of the ARM processor must be simulated.

- Many ARM instructions make use of addressing modes that are encoded in the instruction and the calculations performed by the addressing mode must be simulated.

- Simulating the CPSR flags and the setting of the flags.

- Accessing the simulated memory block.

- Simulating conditional execution.

See Appendix C for an example showing code expansion in a translated block.

#### 4.3.2 When and What to Translate

Translation is expensive in terms of the computation time required to translate the code, so there is little point in translating code that is unlikely to be executed enough to recoup the cost of the translation. After a DBB is discovered it isn't translated until some decision is reached regarding the expected pay back from translating the block. Various mechanisms have been used to decide when to translate from a simple execution count [7], to a heuristic based on the block size and the execution count [6]

## 4.3.3 Translating Program Flow

A very similar problem is deciding which regions of an executing program are hot and worth creating large translation units for. In the case of forming large translation units (LTU) there is the additional challenge of discovering which code should be included in the LTUs. Forming LTUs also opens up other optimization possibilities such as code reordering. Forming LTUs may also be regarded as translating the program flow. When the unit of translation is the DBB the emulation manger controls the flow of the executing translation. At the end of each DBB control is transferred back to the emulation manager to determine which block to execute next. The formation of LTUs requires that this flow of control be translated. An additional challenge to maximizing the performance of LTUs is to ensure that the translation doesn't become so large that it adversely affects the JIT compilation time.

The final challenge of translation is purely a challenge for the programmer, ensuring that the generated translation is an accurate representation of the source program.

# 5 Implementing a Dynamic Binary Translator

Faculty and students in the CS department at the University of Victoria developed the ARMSim# ARM simulator, which runs on the .NET framework. This simulator is based on a simple fetch and decode interpreter, and as mentioned previously the decoder from the interpreter makes an ideal starting point for implementing a dynamic binary translator. Many additional components were required to create a functioning DBT.

## 5.1 Hardware Simulation

While the ARMSim# emulator contains a simulation of the processor state the implementation is tightly coupled to the graphical user interface. For this reason the registers and memory of the processor had to be implemented in a manner suitable for use in a translator.

## 5.1.1 Registers

Since the CLR is implemented as a stack machine there are no registers available to map the registers of the ARM architecture to. The registers of the ARM architecture must be simulated in a Context Block, described previously. A simple approach to implementing the context block is to make it globally accessible. Translated data instructions may access the global context block for many reasons:

- Loading data from source registers.

- Storing data in destination registers.

- Accessing the program counter to calculate offsets for immediate addressing.

The System.Linq.Expression namespace provides a mechanism to access an array by index. This provides a way to implement translation of the actions of data transfer instructions on the simulation of the ARM processor's registers. For example:

```

Expression.ArrayAccess

(

Expression.Field(

Expression.Constant(this),

_registerInfo),

Expression.Constant(rd)

)

```

Figure 9 Accessing simulated registers

The Field expression on Line 3 provides the ArrayAccess expression on line 1 with the array to access. The Constant expression on line 4 is a reference to the object that the Field is a member of. The variable \_registerInfo on line 5 is an instance of the System.Reflection.FieldInfo class that holds meta-data about the \_registers array. This meta-data is used to access the array via Expression syntax. Fields may also be accessed by name. The second Constant expression on line 6 is the index of the element to retrieve, where the value of the index is supplied by a local variable, rd.

This Expression.ArrayAccess is used to obtain the value of a register for use as an input in another expression or as an assignment target when creating an assignment Expression.

## 5.1.2 Memory