# New Generation 4-Channel GNSS Receiver

Design, Production, and Testing

Guillem Antoja Lleonart

Space Engineering, master's level (120 credits) 2017

Luleå University of Technology Department of Computer Science, Electrical and Space Engineering

| Version Log   | Issued by       | Date         |

|---------------|-----------------|--------------|

| First version | Antoja, Guillem | Nov. 8, 2017 |

# **Abstract**

Due to the current research needs and the lack of commercial multi-channel, multi-constellation GNSS receivers, a two-board solution has been developed so it can be mated with and take advantage of the processing power of the FPGA board branded as MicroZed.

In order to achieve the proposed goals, an initial phase for assessing and updating the older design, building, and testing of SiGe modules (including both the electronics and casings) has been carried out. The results included demonstrate performances at logging GPS-L1 data with similar  $C/N_0$  and AGC values as the previous versions of the modules and offering navigation solutions with accuracies of a few meters. Secondly, a first iteration and design proposal for the new generation receiver has been proposed for GPS and GLONASS L1 and L2, which has been manufactured and tested. Partial tests have been performed due to the flaws of the current revision of the MicroZed Board in regards to its communication peripherals, and the results have validated the receiver's design provided certain modifications are considered for future iterations. Furthermore, voltage and frequency tests have provided results with an error of less than 7%, and signal tests have provided  $C/N_0$  values similar to those of the SiGe modules of around 47[dB-Hz] which will be a useful baseline for future iterations. Finally, a design proposal for an Interface Board used between the older NT1065\_PMOD Board and other FPGA boards carrying the standardized FMC connectors has been added to the report and negotiations with manufacturers have been engaged.

# Acknowledgments

First and foremost, I would like to thank Prof. Alos for the opportunity of working with him and his team at CU Boulder, for his guidance during the project, and for all the support he offered out of the project that made moving to and living in Boulder a much more pleasant and comfortable experience.

Secondly, I'm also thankful to the rest of Prof. Akos' team and in particular Dr. Shivaramaiah, with whom I've worked the most during the project, for all the help and kindness.

Next, I would like to appreciate the help from my examiner in Luleå, Per Lindgren.

And last, but not least, I would also like to thank my family, who made it all possible and have always supported me.

# **Table of Contents**

| 1. | Introduc | tion                                | 1  |

|----|----------|-------------------------------------|----|

| 2. | Backgrou | und                                 | 3  |

|    | 2.1 Hist | tory                                | 3  |

|    | 2.1.1    | GPS                                 | 5  |

|    | 2.1.2    | GLONASS                             | 6  |

|    | 2.2 Syst | tem Structure                       | 6  |

|    | 2.2.1    | GPS                                 | 7  |

|    | 2.2.2    | GLONASS                             | 11 |

|    | 2.3 App  | olications                          | 16 |

|    | 2.3.1    | Direct Applications                 | 17 |

|    | 2.3.2    | Indirect Applications               | 17 |

|    | 2.3.3    | Other Applications                  | 18 |

| 3. | Phase 1: | The SiGe Module                     | 19 |

|    | 3.1 Intr | oduction                            | 19 |

|    | 3.2 Har  | dware Design                        | 19 |

|    | 3.2.1    | Electronics                         | 19 |

|    | 3.2.2    | Casing                              | 23 |

|    | 3.3 Soft | tware Design                        | 25 |

|    | 3.3.1    | Firmware                            | 25 |

|    | 3.3.2    | Drivers                             | 25 |

|    | 3.3.3    | Data Logging                        | 26 |

|    | 3.4 Mai  | nufacturing and Testing             | 30 |

|    | 3.4.1    | Manufacturing                       | 30 |

|    | 3.4.2    | Testing                             | 32 |

| 4. | Phase 2: | The New Generation Receiver         | 39 |

|    | 4.1 Intr | oduction                            | 39 |

|    | 4.1.1    | The GN3S_PMOD Board                 | 39 |

|    | 4.1.2    | The ZedBoard and the MicroZed Board | 40 |

|    | 4.1.3    | The Receiver                        | 41 |

|    | 4.2 Firs | t Iteration - Hardware Design       | 41 |

|    | 4.2.1    | Schematics                          | 42 |

|    | 4.2.2 | 2       | Layout                                                     | 47 |

|----|-------|---------|------------------------------------------------------------|----|

|    | 4.3   | First   | Iteration – Manufacturing and Testing                      | 49 |

|    | 4.3.1 | 1       | Manufacturing                                              | 49 |

|    | 4.3.2 | 2       | Testing                                                    | 50 |

| 5. | Phas  | se 3: / | Additional Work                                            | 59 |

|    | 5.1   | Intro   | oduction                                                   | 59 |

|    | 5.1.1 | 1       | FPGA – System on Chip Boards                               | 59 |

|    | 5.1.2 | 2       | The Interface Board                                        | 59 |

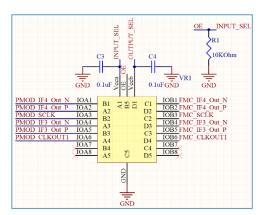

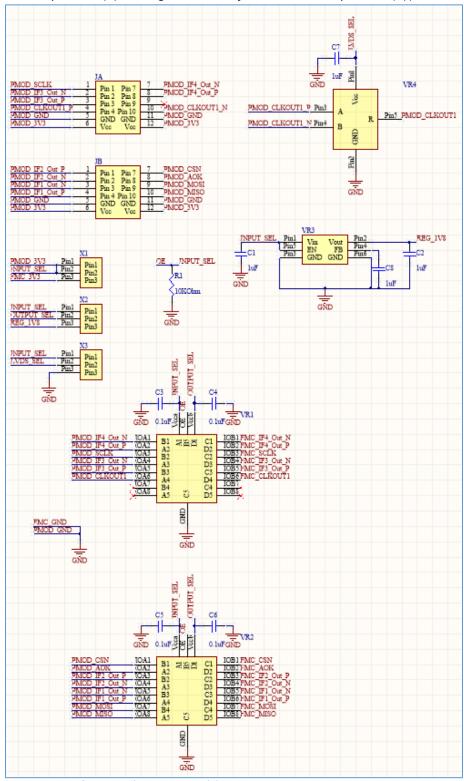

|    | 5.2   | The     | Interface Board - Hardware Design                          | 60 |

|    | 5.2.1 | 1       | Schematics                                                 | 60 |

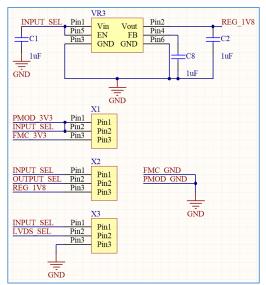

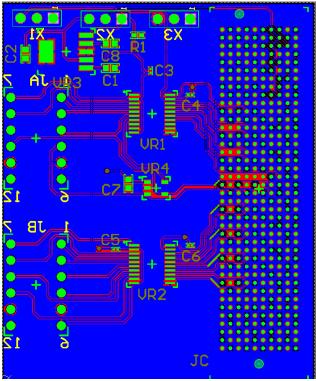

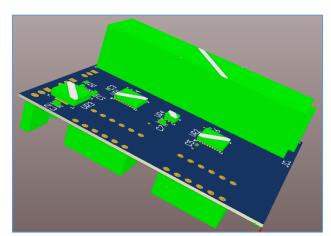

|    | 5.2.2 | 2       | Layout                                                     | 62 |

| 6. | Cond  | clusic  | ons and Future Steps                                       | 65 |

|    | 6.1   | Cond    | clusions                                                   | 65 |

|    | 6.1.1 | 1       | Phase 1                                                    | 65 |

|    | 6.1.2 | 2       | Phase 2                                                    | 66 |

|    | 6.1.3 | 3       | Additional Work                                            | 67 |

|    | 6.2   | Futu    | re Steps                                                   | 67 |

|    | 6.2.2 | 1       | Phase 1                                                    | 67 |

|    | 6.2.2 | 2       | Phase 2                                                    | 68 |

|    | 6.2.3 | 3       | Additional Work                                            | 69 |

| 7. | Bibli | ogra    | phy                                                        | 71 |

| 8. | Ann   | exure   | 3                                                          | 73 |

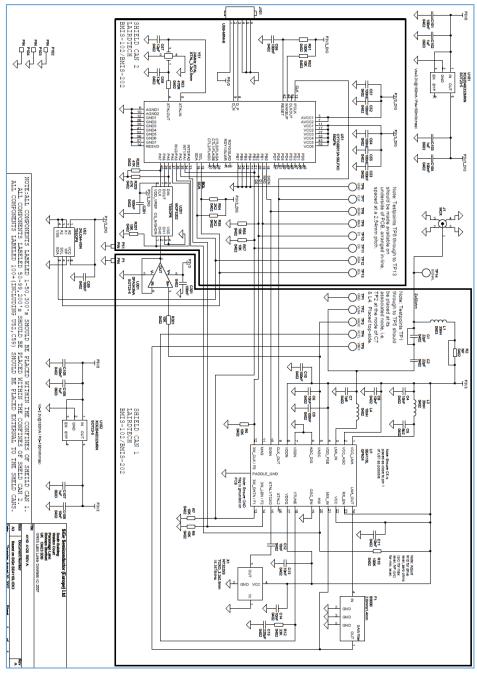

|    | 8.1   | Ann     | exure 1 – SiGe's Schematics                                | 73 |

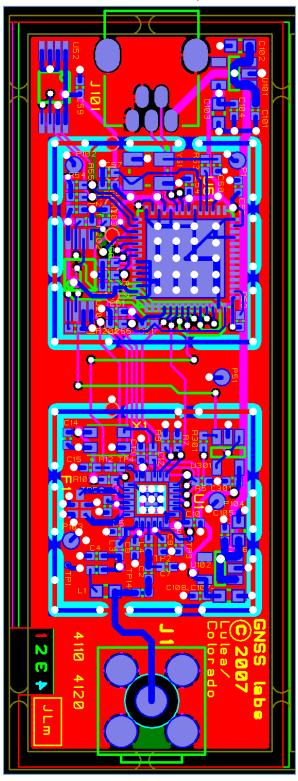

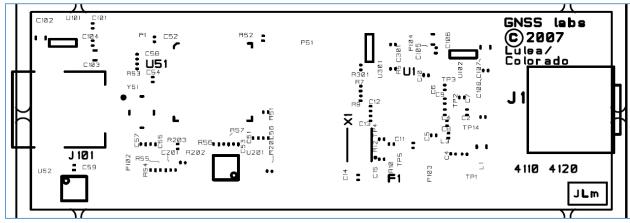

|    | 8.2   | Ann     | exure 2 – SiGe's Layout                                    | 74 |

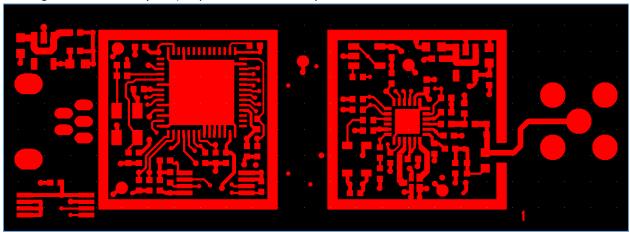

|    | 8.3   | Ann     | exure 3 – NT1065_MicroZed's Schematics                     | 77 |

|    | 8.4   | Ann     | exure 4 – NT1065_MicroZed's Layout                         | 81 |

|    | 8.5   | Ann     | exure 5 – NT1065_MicroZed's Original GNSS Signal Test Plan | 85 |

|    | 8.6   | Ann     | exure 6 – Interface Board's Schematics                     | 87 |

|    | 8.7   | Anne    | exure 7 – Interface Board's Lavout                         | 89 |

# Table of Figures

| Figure 1: GPS constellation                                                                          | 9    |

|------------------------------------------------------------------------------------------------------|------|

| Figure 2: GPS Ground Segment                                                                         | 10   |

| Figure 3: Antipodal assignment of GLONASS satellites                                                 | 11   |

| Figure 4: GLONASS constellation                                                                      | 14   |

| Figure 5: GLONASS Ground Segment                                                                     | 15   |

| Figure 6: Trilateration method                                                                       | 16   |

| Figure 7: GPS-L1 for MEO and GEO                                                                     | 17   |

| Figure 8: SiGe GN3S Sampler                                                                          | 19   |

| Figure 9: SiGe's layout                                                                              | 20   |

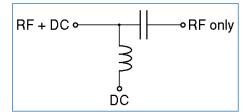

| Figure 10: Bias Tee generic circuit                                                                  | 20   |

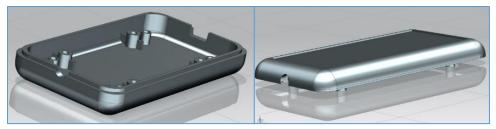

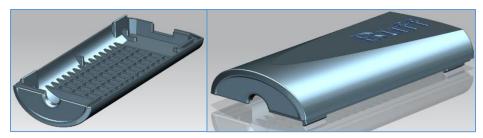

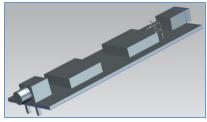

| Figure 11: SiGe's latest housing                                                                     | 24   |

| Figure 12: SiGe's new housing model v.1 lower (left) and upper (right) parts                         | 24   |

| Figure 13: SiGe's new housing model v.2 inner view (left) and outer view (right)                     | 24   |

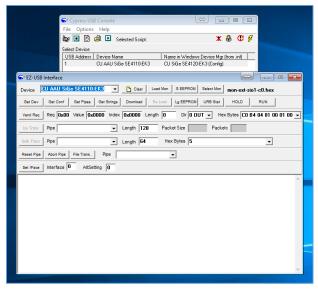

| Figure 14: Cypress' CyConsole                                                                        | 26   |

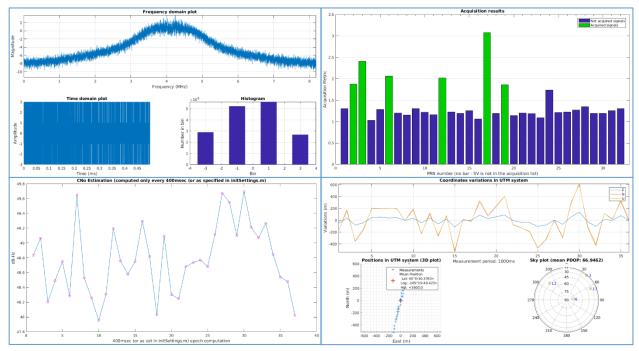

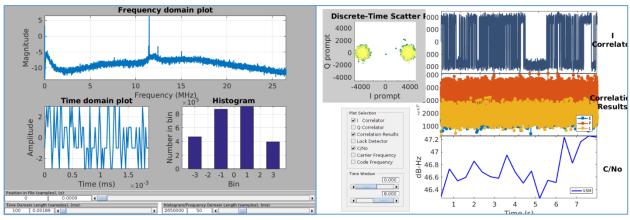

| Figure 15: IF post-processing results                                                                | 28   |

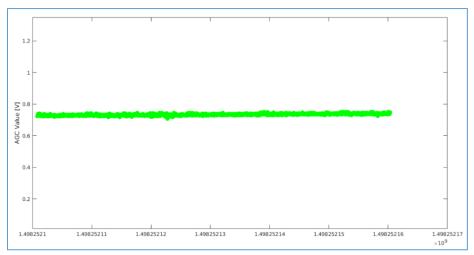

| Figure 16: AGC post-processing results                                                               | 29   |

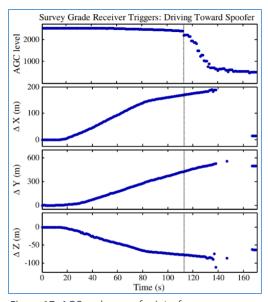

| Figure 17: AGC under spoofer interferences                                                           | 29   |

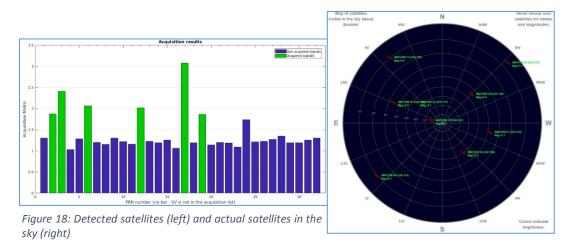

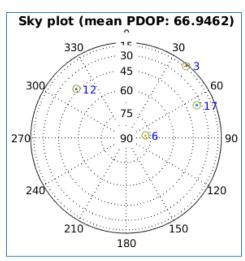

| Figure 18: Detected satellites (left) and actual satellites in the sky (right)                       | 34   |

| Figure 19: Sky plot of the tracked satellites                                                        | 34   |

| Figure 20: SiGe's PCB model                                                                          | 35   |

| Figure 21: SiGe's casing digital test                                                                | 36   |

| Figure 22: SiGe's casing prototype (top left), assembled module (top right), and comparison (bottom) | . 36 |

| Figure 23: SiGe's casing final parts (samples)                                                       | 37   |

| Figure 24: GN3S_PMOD Board                                                                           | 39   |

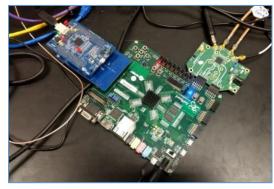

| Figure 25: ZedBoard (center), GN3S_PMOD (right), and Cypress' EZ-USB FX3 (left) stack                | 40   |

| Figure 26: MicroZed Board                                                                            | 40   |

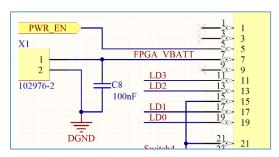

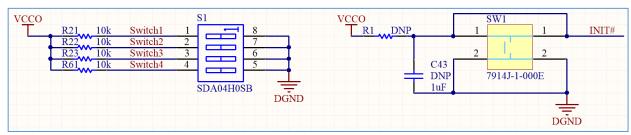

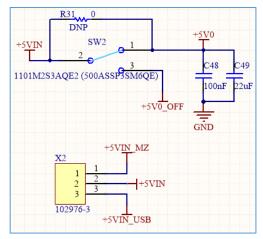

| Figure 27: Battery connector and Power Enable                                                        | 42   |

| Figure 28: In-Line switch and initialization button                                                  | 42   |

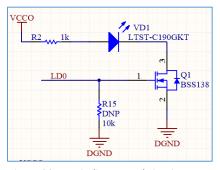

| Figure 29: LED indicator and circuitry                                                               | 42   |

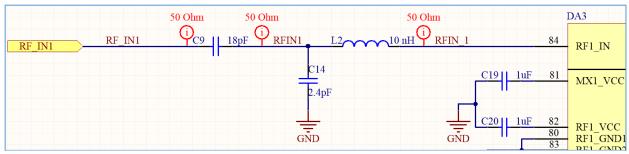

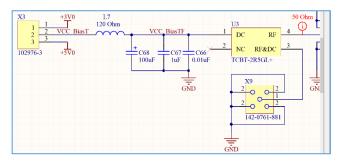

| Figure 30: Incoming RF line to the ASIC                                                              | 43   |

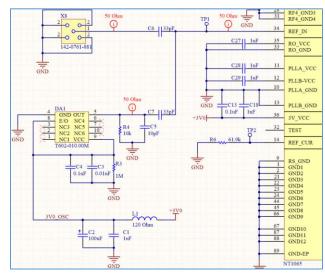

| Figure 31: ASIC's oscillator                                                                         |      |

| Figure 32: Power selection components                                                                | 44   |

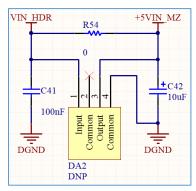

| Figure 33: Power supply protection circuit                                                           | 44   |

| Figure 34: Bias Tee and antenna connection                                                           | 44   |

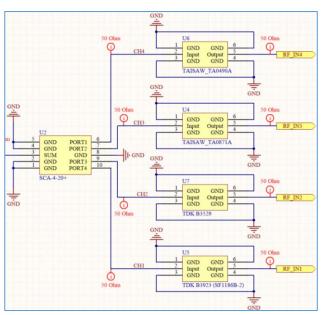

| Figure 35: Power divider and SAW filters                                                             | 45   |

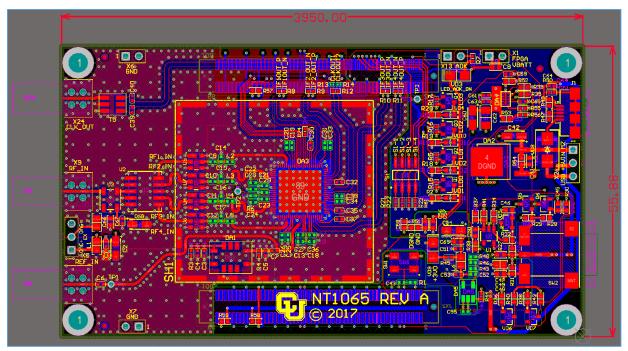

| Figure 36: New generation 2-board receiver layout design                                             | 47   |

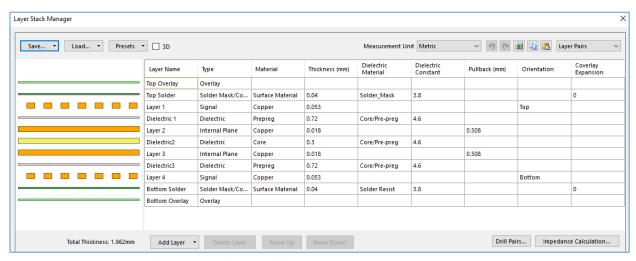

| Figure 37: New generation 2-board receiver layer stack design                                        | 48   |

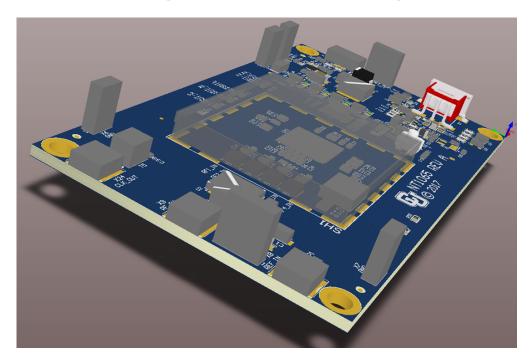

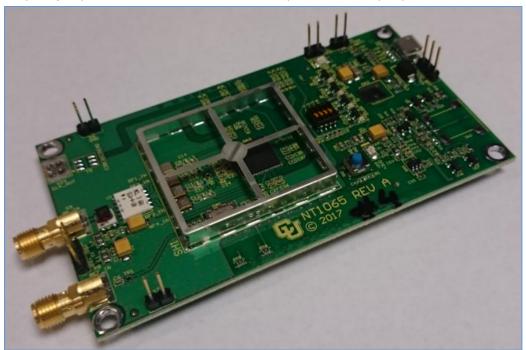

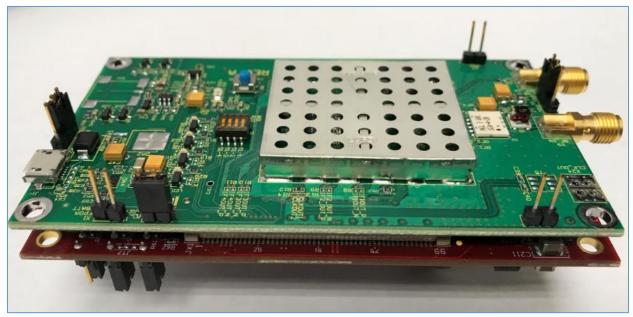

| Figure 38: NT1065_MicroZed Board                                                                     | 50   |

| Figure 39: NT1065_MicroZed and MicroZed Board stacked                                                | 53   |

| Figure 40: GPS-L1 generated spectrum and tracking results                                            | 57   |

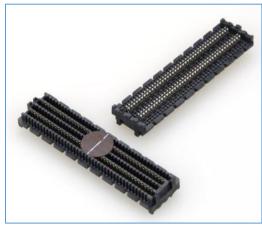

| Figure 41: FMC connector                                                                             |      |

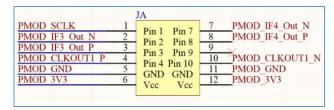

| Figure 42: PMOD connector (JA)                                                                       | 60   |

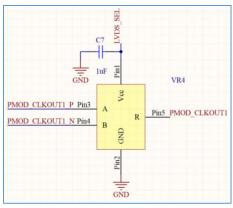

| Figure 43: LVDS receiver                                     | 61 |

|--------------------------------------------------------------|----|

| Figure 44: Voltage translator (VR1)                          | 61 |

| Figure 45: Power supply unit                                 | 61 |

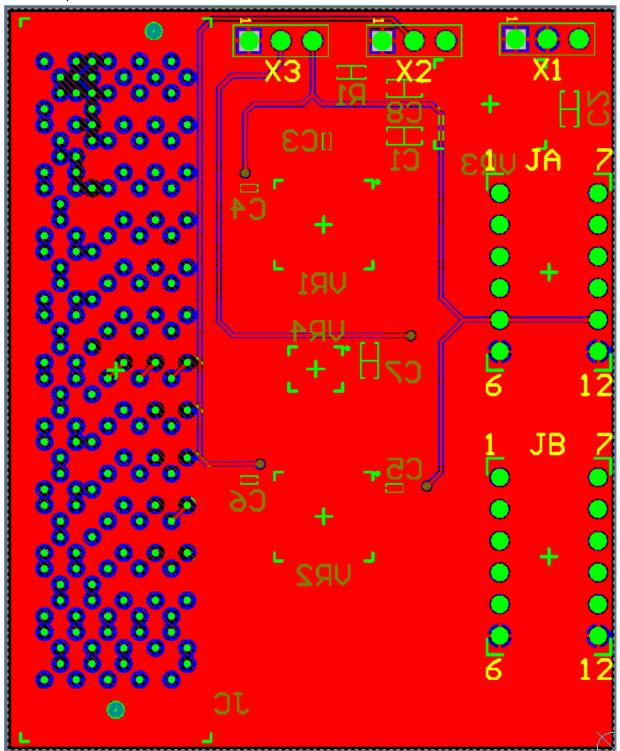

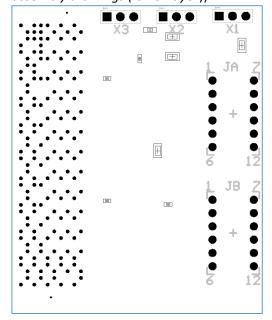

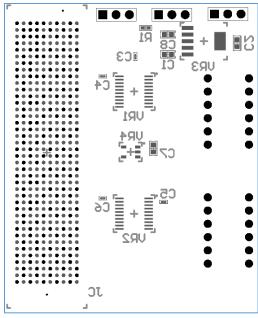

| Figure 46: Interface board's layout (bottom view)            | 63 |

| Figure 47: Interface Board's 3D model (upside down)          | 63 |

| Figure 48: SiGe's schematic                                  | 73 |

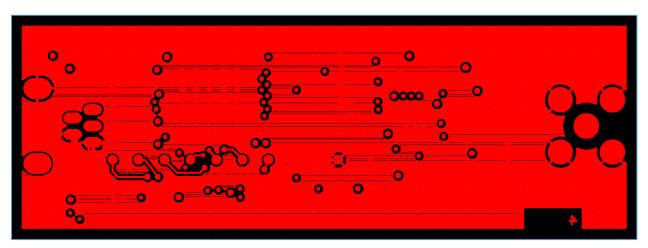

| Figure 49: SiGe module on CADSTAR                            | 74 |

| Figure 50: SiGe's silkscreen                                 | 75 |

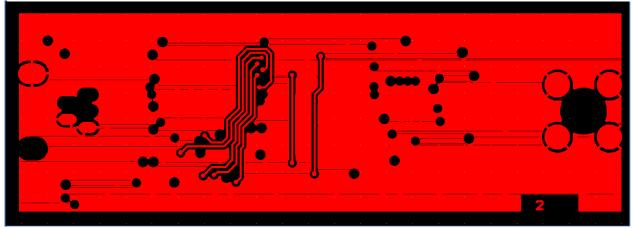

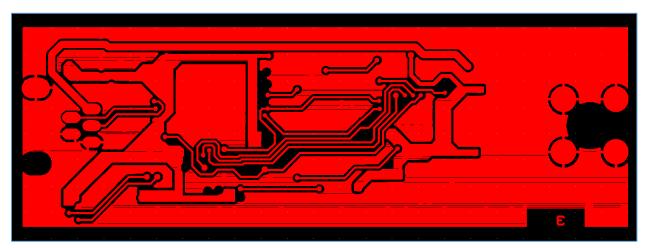

| Figure 51: SiGe's Layer 1                                    | 75 |

| Figure 52: SiGe's Layer 2                                    | 75 |

| Figure 53: SiGe's Layer 3                                    | 76 |

| Figure 54: SiGe's Layer 4                                    | 76 |

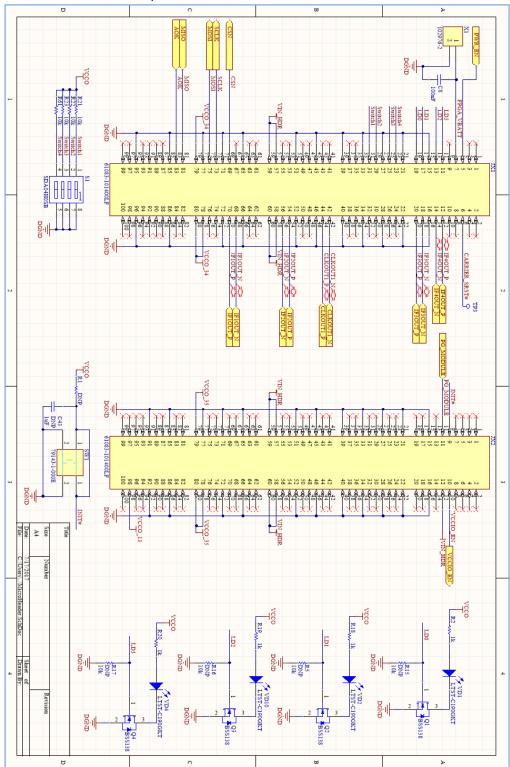

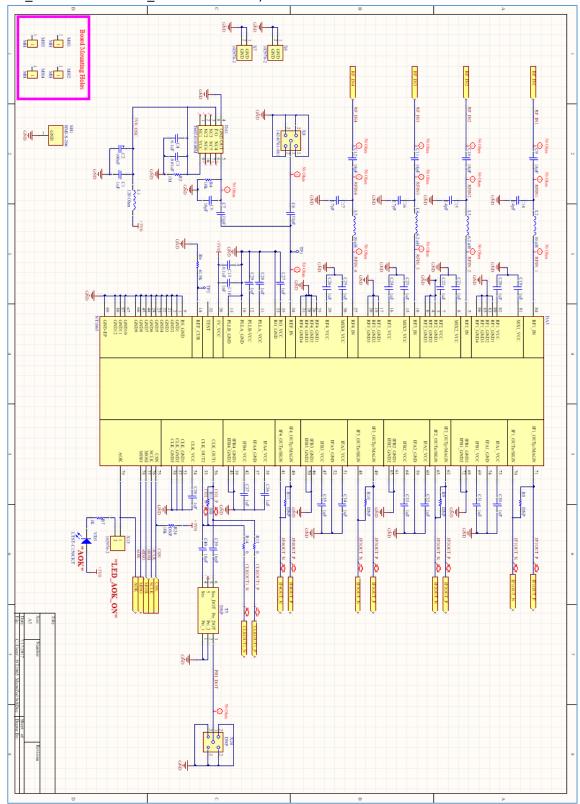

| Figure 55: NT1065_MicroZed's MicroHeaders.SchDoc             | 77 |

| Figure 56: NT1065_MicroZed's NT1065_MicroZed.SchDoc          | 78 |

| Figure 57: NT1065_MicroZed's Power.SchDoc                    | 79 |

| Figure 58: NT1065_MicroZed's RFInput.SchDoc                  | 80 |

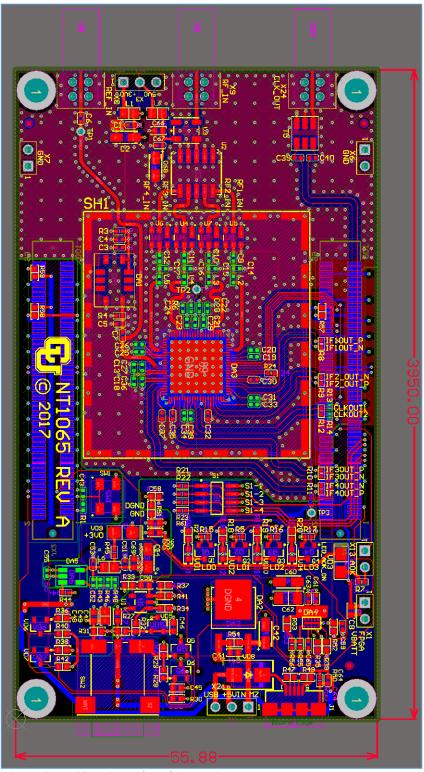

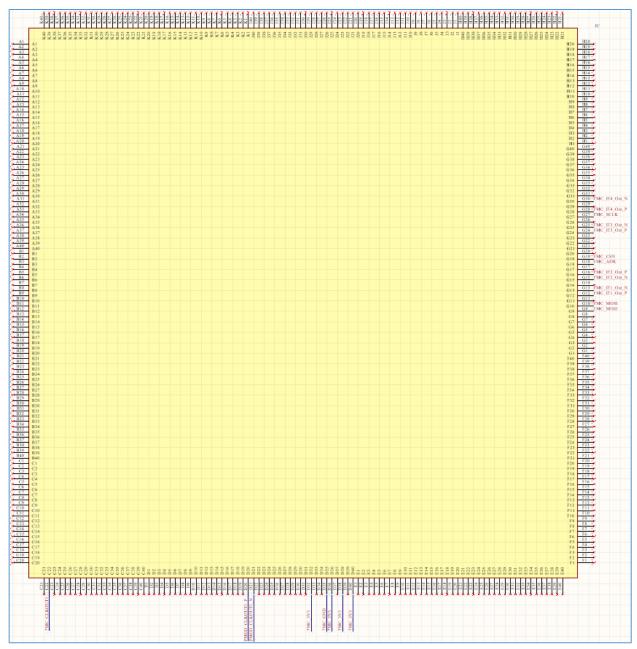

| Figure 59: NT1065_MicroZed on Altium Designer                | 81 |

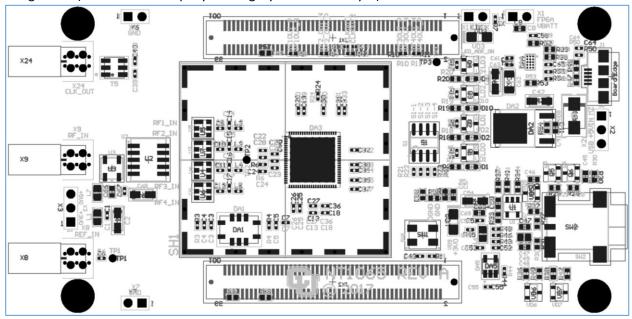

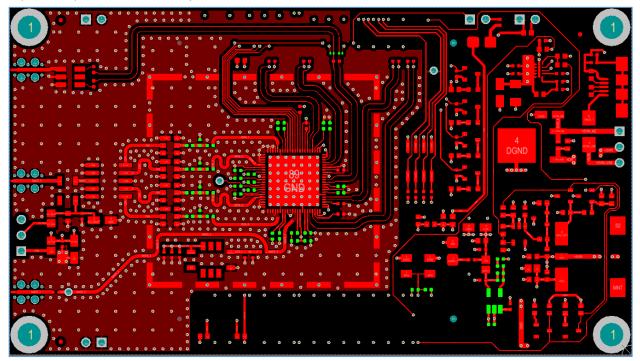

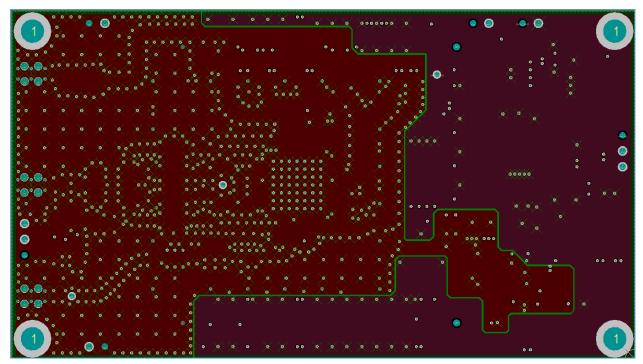

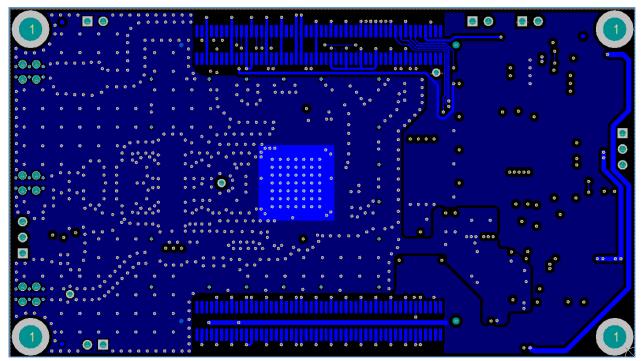

| Figure 60: NT1065_MicroZed's assembly drawing                | 82 |

| Figure 61: NT1065_MicroZed's Layer 1                         | 82 |

| Figure 62: NT1065_MicroZed's Layer 2                         | 83 |

| Figure 63: NT1065_MicroZed's Layer 3                         | 83 |

| Figure 64: NT1065_MicroZed's Layer 4                         | 84 |

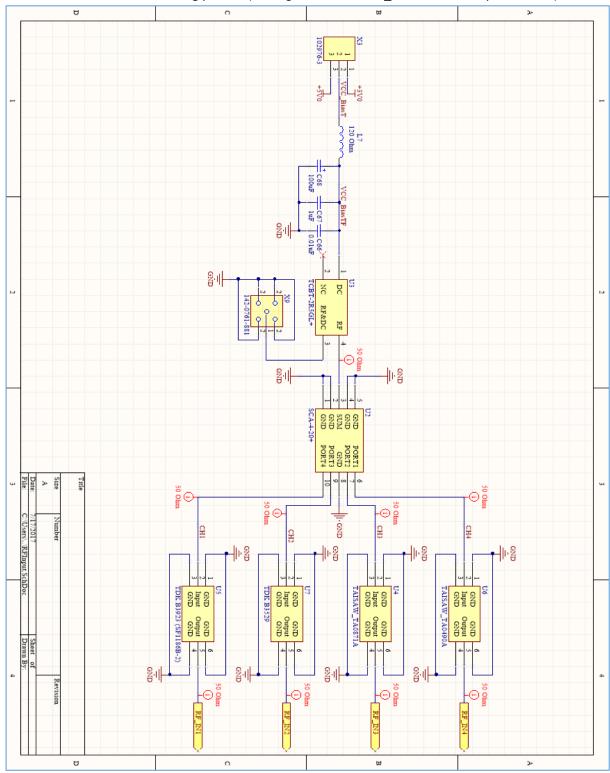

| Figure 65: Interface Board's components (1)                  |    |

| Figure 66: Interface Board's components (2)                  | 88 |

| Figure 67: Interface Board's layout on Altium Designer       | 89 |

| Figure 68: Interface Board's assembly drawings (upper layer) | 90 |

| Figure 69: Interface Board's assembly drawings (lower layer) | 90 |

| Figure 70: Interface Board's layout (upper layer)            | 90 |

| Figure 71: Interface Board's layout (lower layer)            | 90 |

# Table of Tables

| Table 1: SE4110L and SE4120L pin comparison                          | 22 |

|----------------------------------------------------------------------|----|

| Table 2: TCXO alternative comparison                                 | 23 |

| Table 3: SiGe's operational modes                                    | 27 |

| Table 4: GPS satellites' ID and name                                 | 33 |

| Table 5: SiGe's electronic tests results (1)                         | 35 |

| Table 6: SiGe's electronic tests results (2)                         | 35 |

| Table 7: Power divider options (1)                                   | 45 |

| Table 8: Power divider options (2)                                   | 46 |

| Table 9: Raw Single Tests – Power supply voltages                    | 51 |

| Table 10: Raw Single Tests – Signal voltages                         | 51 |

| Table 11: Raw Single Tests – Signal frequencies                      | 52 |

| Table 12: Raw Single Tests – Frequency responses                     | 53 |

| Table 13: Raw Composite Tests – Power supply voltages                | 54 |

| Table 14: Raw Composite Tests – Signal voltages                      | 55 |

| Table 15: Raw Composite Tests – Signal frequencies                   | 56 |

| Table 16: Raw Composite Tests – Frequency responses                  | 56 |

| Table 17: NT1065_MicroZed Board satellite detection results per band | 85 |

| Table 18: NT1065_MicroZed Board C/N <sub>0</sub> and AGC results     | 85 |

# **Abbreviations**

ADC Analog to Digital Converter

AGC Automatic Gain Control

AMS Agile Mixed Signaling

ASIC Application-Specific Integrated-Circuit

BPSK Binary Phase-Shift Keying

BeiDou BeiDoü Navigation Satellite System

BOC Binary Offset Carrier

BOM Bill of Materials

CCAR Colorado Center for Astrodynamics Research

CC-M GLONASS Central Clock

CDMA Code Division Multiple Access

DC Direct Current

DIP Dual In-line Package

EEPROM Electrically Erasable Programmable Read-Only Memory

EoL End of Life

FDMA Frequency Division Multiple Access

FPGA Field-Programmable Gate Array

GEO Geostationary Earth Orbit

GLONASS Globalnaya Navigazionnaya Sputnikovaya Sistema

GNSS Global Navigation Satellite System

GPS Global Positioning System

GS Ground Segment HPC High Pin Count

IF Intermediate Frequency

IO Input/Output

ITLL Integrated Teaching & Learning Laboratory

LED Light-Emitting Diode

LEO Low Earth Orbit

LNA Low Noise Amplifier

LoS Line of Sight Low Pin Count

LVDS Low Voltage Differential Signal

MCS Master Control Station

MEO Medium Earth Orbit

MOSFET Metal–Oxide–Semiconductor Field-Effect Transistor

MS Monitoring and Measuring Station

NAVSTAR Navigation System with Timing and Ranging

NGA National Geo-Intelligence Agency

NUDET Nuclear Detonation

OCX Operational Control System

OS Operating System

PCB Printed Circuit Board

PID Product ID (identification)

PMOD Peripheral Module

PR Pseudo Random

QPSK Quadrature Phase Shift Keying

RAAN Right Ascension of the Ascending Node

RAM Random Access Memory

RF Radio Frequency

SAESD Smead Aerospace Engineering Science Department

SAR Search and Rescue

SAW Surface Acoustic Wave

SCC System Control Center

SD Secure Digital

SLR Laser Ranging Stations

SNR Signal to Noise Ratio

SS Space Segment

TCXO Temperature Compensated Crystal Oscillator

TMBOC Time-Multiplexed BOC

TT&C Telemetry, Tracking, and Command

UART Universal Asynchronous Receiver/Transmitter

ULS Mission Uplink Station

USB Universal Serial Bus

USNDS United States NUDET Detection System

VID Vendor ID (identification)

VITA VMEbus International Trade Association

WWI World War I WWII World War II

# 1. Introduction

Throughout history, navigation has played an important role in many different areas, such as exploration, commerce, and warfare. The very initial techniques included determining one's position by observing the stars and using maps and specific tools. However, in the 20<sup>th</sup> century, new technologies were developed which allowed for a greater degree of automation while also increasing the accuracy of the results; this was the beginning of Radio Frequency (RF) navigation. Many different ground-based systems were used, each an evolution of the previous one, but the latest step in development brought the systems to space. As this newer version of RF navigation was then satellite-based, it was known as Global Navigation Satellite System (GNSS).

Currently there are many companies and organization with working GNSS receivers for the most popular constellations and services. However, solutions are mostly compatible with only one of the systems, usually either Global Positioning System (GPS) or Глобальная навигационная спутниковая система (Russian for Global Navigation Satellite System or GLONASS), and sometimes even a combination of two systems this time also including 北斗卫星导航系统 (simplified Chinese for BeiDoü Navigation Satellite System or only BeiDou) and the new (under development) Galileo and BeiDou-2 to the list. Nonetheless, some companies have brought their new dual-frequency (or 2-channel), multi-band, multi-constellation to the market, such as Swift Navigation and their Piksi Multi GNSS Module¹ which includes an FPGA for data processing and is currently one of the most advanced solutions. Another close alternative to this module would be the NT1065\_USB3² developed by NTLab, which is a 4-channel, multi-band, multi-constellation evaluation board for their NT1065 "Nomada", this time without a processing FPGA but instead a USB3 for forwarding the data. Lastly, there are organizations such as Virginia Polytechnic Institute and State University, and Miami University among many others that are currently developing their own multi-channel, multi-band, multi-constellation GNSS receivers.

Taking into consideration the aforementioned state of the art solutions and organizations developing newer receivers, a collaboration project with the GNSS Lab<sup>3</sup> at the Smead Aerospace Engineering Science Department (SAESD) in Colorado University Boulder (from now on CU Boulder) in order to design and build a new generation receiver in close relationship with the Colorado Center for Astrodynamics Research (CCAR), also hosted by the SAESD. This receiver will be an evolution of a previous front-end used by the research group, and will include four RF channels and compatibility with any combination of GNSS constellations and bands, with components carefully chosen so that they can be easily replaced without having to alter the design. Furthermore, the processing side of the receiver will also experience a quite important optimization, as the front-end will be able to be stacked with the new MicroZed Board, a powerful credit card-sized FPGA board. It should be noted, though, that this project will be the first design iteration so the receiver will be designed to be compatible with GPS-L1, GPS-L2, GLONASS-L1, and GLONASS-L2 mainly due to the fact that these are the most common services of the only two fully operational GNSS constellations with worldwide coverage. Furthermore, this design project will be the

<sup>&</sup>lt;sup>1</sup> Swift Navigation's Piksi Multi website: https://www.swiftnav.com/piksi-multi

<sup>&</sup>lt;sup>2</sup> NTLab's NT1065\_USB3 board description: <a href="http://ntlab.com/IP/NT1065/NT1065">http://ntlab.com/IP/NT1065/NT1065</a> USB3 description v1.04.pdf

<sup>&</sup>lt;sup>3</sup> GNSS Lab at CCAR in CU Boulder website: <a href="https://ccar.colorado.edu/gnss/">https://ccar.colorado.edu/gnss/</a>

first step towards a more advanced solution, this time including both the GNSS front-end and the required components from the FPGA board into a single board so costs and dimensions can be optimized.

Therefore, this report will first include a background study of the different RF navigation technologies where, in regards to GNSS, special emphasis will be put on GPS and GLONASS as these will be the ones included in the initial design proposed by this project. Secondly, "Phase 1: The SiGe Module" will be described as a get-to-know phase, where an older GNSS data sampler will be revised and brought back to a production stage. Next, the core of the project will be introduced and explained in detail under the title of "Phase 2: The New Generation Receiver". In this chapter, a brief description of previous solutions used at CU Boulder will be included followed by an elaborated motivation for this new design and a detailed explanation of both the process and parts involved in the project. Afterwards, "Phase 3: Additional Work" will comprise an additional board which does not fit in any of the previous phases but has also been designed during this project. Finally, supplementary material regarding the design and production files of the different phases will be added in the form of annexures.

Additionally, several pieces of software will be used during the execution of this project. The core element will be Altium Designer<sup>4</sup>, which is the electronic design software used by the members of the GNSS Lab, which allows not only to design the schematics but also the component and board layouts as well as performing simulations and obtaining 3D models and all the files required for production. Furthermore, for designing mechanical pieces such as module housings, the software of choice will be Siemens NX<sup>5</sup>. In this case, the selection has completely been an individual decision motivated by personal expertise. Lastly, the CyConsole<sup>6</sup> by Cypress Semiconductor will be used in order to program the modules built during Phase 1, as this piece of software has been specifically designed and provided for facilitating the programming of these modules' core processor.

As a final note for this introductory chapter and regarding the methodology followed during the practical part of the project, each phase will begin with a specific background study, be it either previous design files or guidelines, component datasheets, and data from alternative solutions in the market. Next, the design (or revision in the case of the first phase) activities will be engaged. In that regard, component availability and specifications will be checked for the SiGe modules, whereas a block-based design will be carried out for the other two phases. Said block-based design will mainly consist on studying the different technologies that can be successfully implemented for different parts of the board along with an analysis and electronic design of all the associated components for each individual block of the board (such as the oscillator, the core ASIC, the power supply, and so on). The layout design that follows will be outsourced and, once all production files are ready, manufacturers will be contacted for quoting and building the boards. During the production stage, the experiments for testing the boards will be designed accordingly to the TLR of the phase, which will then be executed. These tests will range from simple programmability and performance tests for the SiGe modules to complete voltage and frequency tests on critical parts of the circuitry and further performance tests for the New Generation Receiver, always comparing the results to those obtained from previous versions of the board or from the datasheets, as well as comparing the final performance with online tools in order to verify the satellites IDs that have been detected and the navigation solutions.

<sup>&</sup>lt;sup>4</sup> Altium Design website: http://www.altium.com/altium-designer/overview

<sup>&</sup>lt;sup>5</sup> Siemens NX website: <a href="https://www.plm.automation.siemens.com/en/products/nx/">https://www.plm.automation.siemens.com/en/products/nx/</a>

<sup>&</sup>lt;sup>6</sup> CyConsole website: <a href="http://www.cypress.com/documentation/software-and-drivers/suiteusb-34-usb-development-tools-visual-studio">http://www.cypress.com/documentation/software-and-drivers/suiteusb-34-usb-development-tools-visual-studio</a>

# 2. Background

## 2.1 History

RF navigation systems are based on performing measurements over the signals transmitted by strategically positioned stations, said measurement being primarily regarding the direction of an incoming beam (either by bearing, phase, or interferometry), the distance the signal has traveled from the transmitter (mostly by time-of-travel), and the velocity at which the target or user is moving (Doppler shift of the received signal). There have been many different RF navigation systems throughout history, which can be classified as Bearing-Measurement Systems, Beam Systems, Transponder Systems, Hyperbolic Systems, and Satellite-based Systems.

The first type, the Bearing-Measurement Navigation Systems, was developed and used from before World War I (WWI) to the 1960s. Although there are many different variants of this systems, one of the most relevant and early ones is the Radio Direction Finding, which used a rotating directive antenna in order to determine the incoming direction of multiple RF beams, which then where used to triangulate the receiver position. Another example, which happens to be an evolution of the previous one, is the Reverse Radio Direction Finding, in which the rotating antenna was placed on the ground in order to simplify the onboard receivers and which would transmit the station's ID in Morse code. One more variant would be the Automatic Direction Finder, similar to the original Radio Direction Finding but adding phase comparison thanks to receiving with multiple antennas, also with the re-introduction of Non-Directional Beacons at low and medium frequency which removed the Line of Sight (LoS) restriction of the system. As a final version, the Very High Frequency Omnidirectional Range introduced many changes to the Reverse Radio Direction Finding systems, such as omnidirectionally broadcasting the Morse-coded station ID along with a continuous signal, and a directive signal rotating at 30[rmp].

The second kind of navigation systems that has been mentioned above are the Beam Systems, which were used especially before World War II (WWII). They are characterized by being especially simple on the receiver side and their operation consisted in keeping the receiver centered in an RF beam so multiple beams broadcasted by different stations may create the track to be followed by the receiver. The first of this kind was the Lorenz System, developed by the homonym German company after WWI, and it consisted in transmitting audio signals on two directive beams which overlapped by a bit, so the users could position themselves right where the beams overlapped by listening to the audio of both channels. A second version of Beam System could be the Low Frequency Radio Range, used between WWI and WWII during both en route navigation and instrument approach procedures (maneuvers for transitioning between instrumental flight to visual flight). The Low Frequency Radio Range was based on having a set of stations between airports that would have four antennas transmitting to in four cardinal directions. Furthermore, the signals transmitted by each antenna were two Lorenz beams Morse-coded with "shortlong" and "long-short" respectively, so once the receiver was properly positioned in the beam overlap a steady tone would be perceived. The last example of Beam System could be the Instrument Landing System Localizer which is still used nowadays and provides planes with horizontal and vertical positioning, distance to the landing runway, and additional airport data.

Thirdly, the Transponder Systems are another kind of positioning and navigation system developed before WWII, and based on distance determination via radar. The simplest version of Transponder Systems would

be to use a transponder in order to reply to the signal received from a scanning radar in order to measure distances from objects, which would highly increase the accuracy of using previously described systems such as the Lorenz System by measuring the time between transmission and reception (including both a known transducer delay and the time-of-travel). In addition, a Lorenz beam may be added for horizontal positioning while keeping the transducer for ranging in order to improve the long-distance accuracy. Moreover, other versions would use multiple stations, each with its own frequency so ground control could estimate the transponder's (usually mounted on a plane) position by triangulation. One last example of transponder-based navigation system could be the Distance Measuring Equipment System developed in the early 40s and which mostly improved the electronics from the previously described system, which allowed further automation and included some changes in the pulses transmitted. Each of the operators of this system had available a specific pulsed code in order to prevent ambiguity. Finally, Distance Measuring Equipment Systems have traditionally been allocated next to Very High Frequency Omnidirectional Range systems, which provide both angle and distance estimations.

The next type of RF navigation system from the list above are the Hyperbolic Systems, introduced during WWII, and which main benefit was not needing transponders that replied to the messages broadcasted by the ground stations thanks to being able to determine a position solution by using any number of hyperbolic lines in space. Although there are many different examples of Hyperbolic Systems, below a brief description of three of them has been included, namely Gee, Decca, and LORAN-C. Regarding Gee, it was the first ever hyperbolic system, developed by the United Kingdom during WWII. Gee users could determine the distance to multiple transmitting stations over hyperbolic lines by knowing the fixed transmission delays and the time of arrival of the different pulsed signals. The second system, Decca, was another British system similar to Gee, but in this case instead of pulsed signals, the stations would transmit continuous signals with delayed phases, making it easier to display and requiring much simpler electronics. Lastly, LORAN-C (standing for long range navigation version 3) was being developed in 1952 by the US as an evolution of the original LORAN (similar to Gee but at much lower frequencies), with the main characteristic of combining Gee's pulse delays with Decca's phase delays at rather low frequencies. Although LORAN-C was much more complex than the previous alternative systems, electronics miniaturization greatly benefitted this system becoming this way one of the most popular ones until the introduction of GNSS.

Once the first satellite was launched (Sputnik in 1957), development was focused on new navigation systems, this time satellite-based. The first system of this kind was Transit, deployed in the 60s by the US, which allowed users to obtain accurate positioning data thanks to analyzing the Doppler shift of signals broadcasted at a certain frequency by satellites orbiting fixed and known orbits (set of low polar orbits at approximately 1,100[km]). Afterwards, there have been many different satellite-based systems, some offering regional coverage and some others offering worldwide coverage. GPS (US) and GLONASS (RU) are the only global satellite-based navigation systems which are fully functional, even though both are undergoing a modernization and updating process, whereas Galileo (EU) and BeiDou-2 (CN) are being developed and implemented, and they are both expected to be fully operational in 2020. Therefore, bearing in mind that only GPS and GLONASS are currently fully operational at the time of writing this document, their history has been detailed in the following subchapters.

#### 2.1.1 GPS

After the military success of Transit in the 60s and with the reliable and accurate navigation needs for the American submarine-launched ballistic missiles, strategic bombers, and intercontinental ballistic missiles during the Cold War, the US government started working on a new generation of GNSS first known as Defense Navigation Satellite System but soon rebranded to Navigation System with Timing and Ranging (NAVSTAR), most commonly known simply as GPS. Although it is usually mentioned that the program's design began in 1973 during a meeting held by military officers in Labor Day Weekend, there are evidences that the design phase was engaged before that year, such as articles discussed in the aforementioned meeting like "Low-Altitude Navigation Satellite System" (by R.B. Kershner of the Johns Hopkins Applied Physics Laboratory), "Mid-Altitude Navigation Satellites" (by R.L. Easton of the U.S. Naval Research Laboratory), and "Satellite Systems for Navigation using 24-Hour Orbits" (by J.B. Woodward, W.C. Melton & R.L. Dutcher, of the Aerospace Corporation)<sup>7</sup>.

The first 10 GPS satellites (model Block I) were launched between 1978 and 1985<sup>8</sup>, and provided service for military applications but, after the Korean Air Lines Flight 007 was shot down in 1983 due to flying over USSR's prohibited airspace by mistake<sup>9</sup>, US president Ronald Reagan stated the plans for GPS including civilian services and further signed an executive order in 1983<sup>10</sup>. The next generation of GPS satellites began with the launch of the first Block II in 1989, and it took five years to fully deploy the 24 vehicles. This newer constellation provided for the first time civilian service, which was originally degraded in terms of accuracy due to fear of US enemies using it for their advantage.

A few years after becoming fully operational, additional needs were foreseen and so a modernization process was announced. This modernization affected both the military and the civilian services, and its implementation started with Block IIR(M), a modernized version of the legacy Block IIR, followed with the current Block IIF and the future Block III, always keeping compatibility with the legacy services and the ones introduced by previous modernized versions. The first step of this modernization process was to remove the selective availability (for which civilian precision was forcedly lower than the military) as techniques for both increasing civilian signal accuracy (such as differential GPS) and denning GPS service over specific areas had been developed. Secondly, a service rework was done, with which both signal characteristics like forward error correction and new services such as additional civilian and a modernized military signals on GPS-L2 or a Safety-of-Life (SoL) service on GPS-L5 (find more information about the GPS signals in chapter 2.2.1 GPS). During the modernization process, also the ground segment has been being upgraded with a newer operational control system by Raytheon. The process for the control center is currently undergoing phase two out of three, where Block III satellites launch and verification and capabilities of the civil GPS-L2 have already been included, the migration from the old control system to

<sup>&</sup>lt;sup>7</sup> Easton, Roger L., McCaskill, Thomas B., "Defense Navigation Satellite Systems Proposed Prior to GPS", Proceedings of the 55th Annual Meeting of The Institute of Navigation (1999), Cambridge, MA, June 1999, pp. 57-61.

<sup>&</sup>lt;sup>8</sup> Hegarty, Christopher J., Chatre, Eric, "Evolution of the Global Navigation SatelliteSystem (GNSS)", Proceedings of the IEEE, Vol. 96, No. 12, December 2008, pp. 1902-1917.

<sup>&</sup>lt;sup>9</sup> International Civil Aviation Organization, "ICAO Completes Fact-Finding Investigation - PIO 8/93 Revised", Montreal: ICAO, June 16<sup>th</sup> 1993.

<sup>&</sup>lt;sup>10</sup> "Statement by Deputy Press Secretary Speakes on the Soviet Attack on a Korean Civilian Airliner", extracted from reaganlibrary.archives.gov, September 16, 1983.

the new is expected to be Ready to Transition to Operations in 2019, and additional navigation signals, such as the civil GPS-L1 and GPS-L5, will be supported, monitored, and controlled in the near future<sup>11</sup>.

#### 2.1.2 GLONASS

The Russian navigation system GLONASS was born in 1957 from the research of potential applications of radio-astronomy techniques, in particular for aero-navigation. Its first soviet ancestor was the Low Earth Orbit (LEO) *Tsiklon*, developed in the early 60s, and having a total of 31 satellites launched between 1967 and 1978 with the main goal of providing ballistic missile submarines with accurate enough position fixes. Shortly after the first launch, though, development efforts were already placed in improving the design of a part of the system, known as *Parus*, and the whole modified version of *Tsiklon* became *Tsiklon-B. Parus* consisted of a six-plane constellation and usually had one active satellite (with additional spare ones) per plane, which had a nominal lifetime between 1.5 and 2 years, resulting in around 100 satellite launches between 1974 and 2010. Furthermore, and in order to complement the new *Parus* military system with civilian services, another system was developed after the first *Parus* flight test in 1974, the civilian *Tsikada*. With most of the development being done for *Parus*, it took no more than two years until the first satellite was placed in orbit for flight tests, and in 1978 the deployment of operational four-plane constellation (again each orbital plane with at least one operational satellite and one spare) of satellites with similar lifetime as *Parus*.

Nonetheless, these newly developed systems took too much time in order to establish a position fix (the order of minutes), and so they could only be used with stationary or slowly moving targets. Therefore, a set of system requirements was prepared and basic research performed in the early 70s, establishing this way the foundation of GLONASS. Later in 1978, the system design was complete, leading to flight tests three years later and a preliminary 10- 12-satellite constellation in 1984. GLONASS was completely operational with a 24-satellite constellation with three orbital planes. As a final note, it is worth mentioning that although GLONASS was conceived as an alternative and competition for the more popular American GPS, it has been often used in conjunction with GPS by many receivers in order to either complement or serve as backup.

## 2.2 System Structure

GNSS are, as the name suggests, satellite-based navigation systems and, therefore, they share the same structure as any other space system. These systems are composed of a Space (SS) and a Ground Segment (GS). In this subchapter, a description of these two segments can be found as well as their most relevant agents or parts, focusing on GPS' modernized form and GLONASS.

<sup>&</sup>lt;sup>11</sup> "PE 0603423F / Global Positioning System III - Operational Control Segment", Project 67A021 / OCX, US Air Force, February 2015.

#### 2.2.1 GPS

#### 2.2.1.1 Space Segment

The SS consists of all the elements of the system allocated outside the Earth's atmosphere, which are mostly the Space Vehicles (SV) or satellites. Nonetheless, GPS signals have been included in this section because they have their origin in space.

#### 2.2.1.1.1 Signals

GPS satellites have five different RF bands assigned, each of them for different particular applications and, as mentioned in chapter 2.2.1 GPS, they system being based on Code Division Multiple Access (CDMA), meaning that all satellites transmit a specific service at the same frequency and time, but using a satellite-specific code. A brief description of each band and its services has been detailed in the subchapters below.

#### 2.2.1.1.1.1 GPS-L1

GPS-L1 is the most commonly used for navigation purposes, it offers four different services, and it is characterized for broadcasting code-multiplexed signals In-Phase or Quadrature at a central frequency of 1,575.42[MHz] depending on the service.

The first service is L1 – Coarse Acquisition (C/A) and is one of the Quadrature civil signals in L1. Modulated by a BPSK(1), it uses 1,023-chip long Gold Codes at a 1.023[MHz] frequency which identify the SV that broadcasted the signal, and has a total data rate of 50[bps] / 50[sps] (bits per second and symbols per second respectively).

Another Quadrature civil signal is L1 - L1C, which is modulated by a TMBOC(6,1,1/11) characterized by two sub-carriers, one at 1.023[MHz] and another at 6.138[MHz]. In this case, the codes used are Weil Codes, with a total length of 10,230 chips per main sequence and 1,800 chips per secondary sequence, and a code frequency of 1.023[MHz]. Last but not least, this service has a data rate of 50[bps] / 100[sps].

Regarding the military services, the first one is the L1 – P(Y) Code, also known as Encrypted Precision Code, and is transmitted In-Phase. It is modulated on a BPSK(10) with a data rate of 50[bps] / 50[sps], and is based on an encryption of a 37-week long code composed of  $2x10^{14}$  chips, thus having a code frequency of 10.23[MHz]. Each of the SV has a specific week of the total code assigned, which relates to the SV's ID and is repeated every 7 days.

Finally, the second military service offered in L1 is the L1 – M-Code, which had been designed for military purposes only and is expected to replace the P(Y) code. The improved jamming resistance relies on basically allowing a higher power transmission without interfering with the C/A or P(Y) codes, thanks to allocating most of the energy at the sides of the band  $^{12}$ . Although little has been disclosed about this service, it is known that it uses a BOC<sub>sin</sub>(10,5) modulation with a sub-carrier frequency of 10.23[MHz] and a code frequency of 5.115[MHz].

<sup>&</sup>lt;sup>12</sup> Barker, Brian C., Betz, John W., Clark, John E., Correia, Jeffrey T., Gillis, James T., Lazar, Steven, Rehborn, Kaysi A., Straton, John R., "Overview of the GPS M Code Signal", Proceedings of the 2000 National Technical Meeting of The Institute of Navigation, Anaheim, CA, January 2000, pp. 542-549.

#### 2.2.1.1.1.2 GPS-L2

Similarly to the GPS L1 band, the L2 band is used for providing four services, the main difference being that the center frequency is in this case 1,227.60[MHz], but the same In-Phase and Quadrature signal structure using CDMA is used.

The first two services are the civil L2 – L2CM and L2 – L2CL, both in Quadrature, and they are multiplexed onto a BPSK(1) at 1.023[MHz]. The codes they are based on are Moderate (10,230 chips) and Long (767,250 chips) Ranging Codes, both types with a code frequency of 511.5[kHz]. Thanks to this multiplexed signals which add redundancy, it is possible for L2 – L2C to improve the accuracy of navigation with an easy to track signal especially in case of localized interferences.

The two remaining services are L2 - P(Y) and L2 - M-Code, which are basically the same as those in L1 but in this case at a different frequency band. For more information about these services refer to the point above 2.2.1.1.1.1 GPS-L1.

#### 2.2.1.1.1.3 GPS-L3

The GPS L3 band has a center frequency of 1,381.05[MHz] and is nowadays no longer being used. Nonetheless, its original usage was providing a communication link for the US Nuclear Detonation (NUDET) Detection System (USNDS), which could provide near real-time worldwide, highly survivable capability to detect, locate, and report any nuclear detonations or other high-energy infrared events in the Earth's atmosphere or in near space<sup>13</sup>.

#### 2.2.1.1.1.4 GPS-L4

Contrarily to GPS L3, L4 (center frequency of 1,379.913[MHz]) wasn't originally used, and technically it still isn't in the modernized version of GPS, but it is being studied for additional ionospheric correction, which could improve GPS accuracy.

#### 2.2.1.1.1.5 GPS-L5

The lowest frequency band GPS uses is L5, centered at 1,176.45[MHz] and, similarly to L1 and L2, it uses an In-Phase and Quadrature signal modulation. The main service provided over this band is the SoL service (data transferred In-Phase and pilots in Quadrature), which is a safety service for aviation that features higher power, greater bandwidth, and more advanced signal design. Regarding the technical specifications of the signals, both signals are modulated over a BPSK(10) and use codes obtained by combination and short-cycling of M-sequences. Said codes have a frequency of 10.23[MHz] and a length of 10,230 chips. As one last detail about this service and in order to benefit the most from it, it may be used in combination with L1 - C/A and L2 - L2C, resulting in a technique called trilaning that enables submeter accuracies without augmentations, and very long range operations with augmentations.

<sup>&</sup>lt;sup>13</sup> "PE 0305913F: NUDET Detection System (Space)", Project 672808 / Nuc Detonation Det Sys (sensors), US Air Force, February 2012.

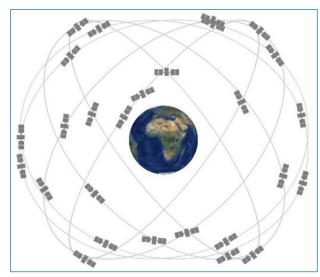

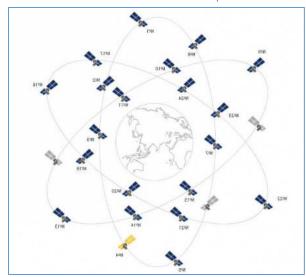

#### 2.2.1.1.2 Constellation and Space Vehicles

The GPS constellation consist of 32 satellites orbiting a set of six orbital planes (see *Figure 1: GPS constellation*), which ensures that at any point in time and anywhere on Earth a receiver would be able to get the signals of at least 4 GPS satellites, which allows it to obtain its coordinates. Regarding the orbits in particular, those are characterized for being approximately circular, being Medium Earth Orbit (MEO) with an altitude above sea level of 20,200[km], having an inclination of 55° and a 60° separation between Right Ascension of the Ascending Node (RAAN). Moreover, this orbits allow the SVs to pass over the same point on Earth's surface twice a day, which is also beneficial for some military applications among others.

Figure 1: GPS constellation

In regards to the SVs, as mentioned before, the constellation is formed by 32 satellites, 30 of which are active, but these vehicles are not all the same. Instead, there are three different types of SV being used and one being developed, asides from one of the legacy types which is obsolete. There are, from oldest to newest, 11 operational Block IIR, 7 Block IIR(M), and 12 Block IIF.

Regarding the Block IIR, they were launched between 1997 and 2004 and they were renewed versions of the older Block IIA so the latter could be replaced after their End of Life (EoL). Since they were essentially the same as the previous version, they also broadcasted L1 - Coarse Acquisition, L1 - P(Y), and L2 - P(Y), and they had a similar lifespan of about 7 years and a half. Considering their launch date, they are already approaching their expandable EoL, being the latest decommission for satellite E6 on May 5, 2017.

The next generation were Block IIR(M) satellites, launched between 2005 and 2009 and, as an evolution (M standing for modernized) of Block IIR, they offered some additional signals such as a second civil one in L2 (L2 – L2C) and a new military one with increased jamming resistance, the L1 – M-Code. Furthermore, they also provided flexible power levels for military signals, although the lifespan had not been improved.

The 4<sup>th</sup> GPS satellite generation is known as Block IIF. These satellites broadcasted the same signals as the previous generations, with the addition of a third civil signal, the L5 – Safety-of-Life. These have been launched since 2010, and they also provide other performance improvements such as more advanced atomic clocks, improved accuracy, signal strength, and quality while increasing the life span for the first time since Block IIA.

Finally, the new GPS III is considered to be ready for launch in 2017 and will add a civil signal to L1, enhance the signal reliability, accuracy, and integrity, and even increasing the life span by approximately 3 years.

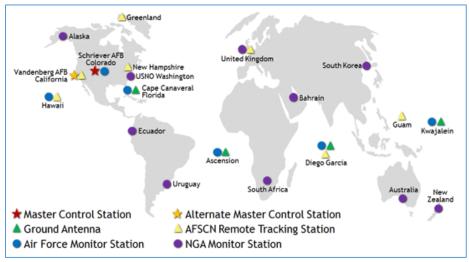

#### 2.2.1.2 Ground Segment

The GS comprises all the elements which are, as the name suggests, on the ground. In the case of GPS, these elements are a Master Control Station (MCS), the Monitoring and Measuring Stations (MS), and the Ground Antennas (see *Figure 2: GPS Ground Segment*).

Figure 2: GPS Ground Segment

The MCS is at the Schriever Air Force Base, Colorado, where the 2<sup>nd</sup> Space Operations Squadron commands and controls the GPS constellation. The main tasks performed there are generation and upload of navigation messages as well as ensuring the proper operation and accuracy of the GPS constellation. Furthermore, the MCS also receives navigation information form the MS, which is used to track the different satellite positions in orbit so their orbital distribution can be modified in case of failure in order to maintain an optimum service. It should also be noted that there is an Alternate MCS, this one in Vandenberg Air Force Base, which used to be the main one originally now serves as redundancy.

Secondly, regarding the MS, there is a total of 15 located throughout the world. The first 6 are from the Air Force and the other 9 are from the National Geospatial-Intelligence Agency (NGA). The main goal of such stations is to track the SV as they orbit above them and report the collected data (including not only the downlink messages themselves but also atmospheric data and other signal measurements) to the MCS.

The third element that has been mentioned as part of the ground segment are the Ground Antennas. These are the elements that allow communication with the satellites and they support S-Band frequencies. There are two kinds of antennas, GPS dedicated and shared. The GPS dedicated antennas are only 4, and they are located at Kwajalein (Marshall Islands), Ascension Island (Saint Helena, Ascension and Tristan da Cunha), Diego Garcia (British Indian Ocean Territory), and Cape Canaveral (US). The remaining 7 antennas are shared with the Air Force Satellite Control Network (AFSCN), which are remote tracking stations located throughout the globe and help increasing communication windows with satellites as well as improving tracking capabilities.

Lastly, it is worth mentioning that the GS is undergoing a modernization process by implementing the next generation Operational Control System (OCX) which will, among others, provide improved cybersecurity and resilience in managing both civil and military navigation signals and the different GPS satellite families.

#### 2.2.2 GLONASS

#### 2.2.2.1 Space Segment

Similarly to GPS, GLONASS' SS comprises those elements outside the Earth's atmosphere, namely the SV, but signals have also been included.

#### 2.2.2.1.1 Signals

GLONASS is a double-band system, meaning that its services are found in two different bands: L1, and L2; and mentioned in chapter 2.1.2 GLONASS, it traditionally used Frequency-Division Multiple Access (FDMA) for its services. Nonetheless, the usage of CDMA was disclosed in 2008<sup>14</sup> for the already existing bands and 2 additional ones: L3 (already being implemented by some SVs) and L5. The following subchapters contain more information regarding each of the bands and their signals.

#### 2.2.2.1.1.1 GLONASS-L1

The highest frequency band used by GLONASS is L1, with its center frequency at 1,602[MHz]. It is important to notice that although the constellation has 24 nominally operating satellites, in order to both optimize the amount of frequency channels and at the same time comply with the CCIR Recommendation 769, GLONASS has been using a maximum of 15 channels since 2005, where each channel's center frequency is calculated by:

$$f_{k_{L1}} = f_{0_{L1}} + k\Delta f_{L1}$$

#### Where:

- k: frequency channel number.

-  $f_{0_{L1}}$ : 1,602[MHz].

-  $\Delta f_{I,1}$ : 562.5[kHz].

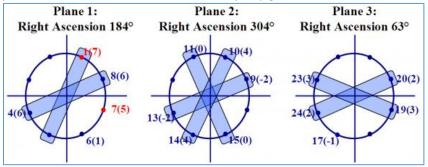

This is possible because, as can be seen in the figure below (see *Figure 3: Antipodal assignment of GLONASS satellites*, where the displayed parameters have the form i(k), "i" standing for satellite almanac slot, and "k" being the frequency channel number), satellites occupying antipodal slots may use the same frequency as they will never be seen at the same time by any ground user.

Figure 3: Antipodal assignment of GLONASS satellites

Regarding the different services provided in L1, satellites broadcast both an open signal known as Standard Precision (SP) or L1OF ("O" meaning открытый от ореп, and "F" meaning FDMA), and an

<sup>&</sup>lt;sup>14</sup> Gibbons, G., "Russia Approves CDMA Signals for GLONASS, Discussing Common Signal Design", Inside GNSS, April 28, 2008.

obfuscated signal also known as High Precision (HP) or L1SF ("S" meaning зашифрованный or encrypted, and again "F" meaning FDMA).

L1OF is characterized by using a BPSK(0.511), an M-sequence Pseudo Random (PR) code for all satellites with a frequency of 511[kHz], a Meander sequence of 1,000[Hz] which Modulo-2 addition with the PR code is used to modulate the signal, and a data rate of 50[bps]. The L1SF, on the other hand, uses a BPSK(5.11), meaning the undisclosed PR code has a frequency of 5.11[MHz], and it is transmitted In-Quadrature (phased by 90°) of the L1OF.

As a side note and as a consequence of GLONASS' modernization, newer satellites (from GLONASS-K2 launched since 2015) have started including CDMA-compatible payloads. These newer SV additionally offer the same L1 services originally broadcasted in FDMA, but in CDMA, thus becoming L1OC and L1SC (the "C" logically meaning CDMA). The new services have a center frequency of 1,600.995[MHz], and they use Time-Division Multiplexing in order to send the pilot and data signals, with a BOC(1,1) and BPSK(1) respectively for L1OC, and a BOC(5,2.5) both for L1SC. Finally, another service is being developed for L1 which is expected to be provided by GLONASS-KM vehicles in 2025, L1OCM. It is an interoperable CDMA signal based on the same frequencies and format as GPS-L1 – L1C (see chapter 2.2.1.1.1.1 GPS-L1 for information on GPS-L1) that uses a BOC(1,1) modulation.

#### 2.2.2.1.1.2 GLONASS-L2

Similarly to GLONASS-L1, L2 has a 15-channel frequency setup (see chapter 2.2.2.1.1.1 GLONASS-L1 for more details), but in this case the center frequency is 1,246[MHz] and each channel's center frequency is obtained by the following expression:

$$f_{k_{L2}} = f_{0_{L2}} + k\Delta f_{L2}$$

Where:

- k: frequency channel number.

-  $f_{0L2}$ : 1,246[MHz].

-  $\Delta f_{L2}$ : 437.5[kHz].

GLONASS-L2 services are the same as those for L1, receiving the names L2OF and L2SF, meaning L2 open FDMA (for Standard Precision) and encrypted FDMA (for High Precision) respectively. Furthermore, these two services are transmitted with a 90° difference in phase, being L2OF In-Phase and L2SF In-Quadrature.

As mentioned above, L2 services are identical to L1's ones but with a different carrier frequency. Therefore, L2OF is again characterized by a data rate of 50[bps], a BPSK(0.511) signal modulation, an M-sequence code with a frequency of 0.511[MHz], and a Meander sequence of 100[Hz], the last two being combined by the Modulo-2 addition and further used to modulate the signal. In regards to the High Precision signal, the L2SF, its known specifications (it should be kept in mind that not all specs are available to the public) are also the same as the ones from L1SF, having a BPSK(5.11) modulation and a PR code frequency of 5.11[MHz], which is kept private.

In addition to the traditional FDMA signals and alike GLONASS-L1, CDMA services over GLONASS-L2 are being developed and implemented, starting with GLONASS-K2 launches in 2015, which included a CDMA-compatible payload. These CDMA services on GLONASS-L2 are the L2OC (open or Standard Precision

CDMA) and the L2SC (encrypted or High Precision CDMA), both using a carrier frequency of 1,248.06[MHz]. The public service known as L2OC uses Time-Division Multiplexing so both data and pilot signals can be transmitted over the same medium, which are modulated with a BPSK(1) and a BOC(1,1) respectively. On the other hand, the encrypted service known as L2SC has its data and pilots modulated by a BOC(5,2.5), and it is broadcasted In-Quadrature in respect to the public services.

#### 2.2.2.1.1.3 GLONASS-L3

GLONASS-L3 is a CDMA-only band that provides the service L3OC (open or Standard Precision CDMA) with a carrier frequency of 1,202.025[MHz] and a bandwidth of 20.46[MHz] which was first tested in February 2011<sup>15</sup>. In more detail, the signal is modulated by a QPSK, where the data is In-Quadrature and the pilots are In-Phase, and has a total chip rate of 10.23[Mcps]. About the codes used, GLONASS-L3 uses ranging codes based upon Kasami sequences with a length of 214-1 symbols which are truncated at 10,230 symbols, where each symbols lasts for 10 chips and each chips has a duration of 10[ms]. Additionally, secondary codes with 1[ms] per symbol are used for both data and pilots, these being a 5-bit Barker code (00010) and a 10-bit Neuman-Hoffman code (0000110101) respectively.

In a similar way as in other GNSS systems, new services for GLONASS-L3 are being developed, namely the L3SC and the L3OCM, which are expected to be available by 2025. Regarding the L3SC (encrypted or High Precision CDMA), it will be an encrypted version of the L3OC, meaning that the codes will be private so only authorized users may take advantage of this service. Secondly, the L3OCM will be a modernized and interoperable CDMA signal, which will use a BPSK(10) modulation centered at 1,207.14[MHz] and will be similar to the Galileo/COMPASS E5b signal in order to improve multiple GNSS interoperability.

#### 2.2.2.1.1.4 GLONASS-L5

Efforts are being put onto developing another GLONASS service which is compatible with other GNSS so easier and cheaper implementation of multi-standard GNSS receivers is possible. One of such services in L5 is L5OCM (meaning Open CDMA Modernized), which is expected to be provided by GLONASS-KM satellites from 2025, will be very similar in specifications to the GPS-L5 and Galileo/COMPASS E5a, will use a BPSK(10) modulation, and will have a carrier frequency at 1,176.45[MHz]. Similarly to GPS-L5, the main goal of this new frequency band and its signals is to provide a SoL service, which will mostly be used by the aviation sector.

-

<sup>&</sup>lt;sup>15</sup> Thoelert, S., S. Erker, J. Furthner, M. Meurer, G. X. Gao, L. Heng, Walter, and P. Enge, "First Signal in Space Analysis of GLONASS K-1", Proceedings of ION ITM 2011, Portland, OR, September 2011, pp. 3076-3082, 2011.

#### 2.2.2.1.2 Constellation and Space Vehicles

Figure 4: GLONASS constellation

GLONASS's satellite constellation (see *Figure 4: GLONASS constellation*) consists, as of summer 2017, of 27 vehicles, of which 24 are operational. The 3 unused SV are either under check by the Prime Contractor, spare satellites in case of another one failing, or in in-flight tests phase. These satellites are orbiting a set of 3 orbital planes, all with an inclination of 64° 8′, an altitude of 19,140[km] and a separation between their respective RAANs of 120°.

Regarding the SV themselves, only 2 out of the 4 different generations are operative nowadays, being Generation Zero prototypes and having all First Generation (Block IIa, IIb, and IIv) satellites been decommissioned before 1989. Out of the 27 in-orbit SV, the active ones are 23 belonging to the Second

Generation and 1 to the Third Generation. Regarding the 3 non-operative satellites, the spare one and the one under maintenance are from the Second Generation, whereas the one being tested belongs to the Third Generation.

Second Generation satellites, also known as GLONASS-M, Urugan-M or simply M, were developed from the 90s and put in orbit after 2003. These satellites provided substantial improvements regarding the propulsion subsystem and clock stability, which allowed at its turn an increase of lifetime. Another important upgrading over the previous generation is that these newer satellites broadcast a second civil signal on G2 frequency band which allows ionospheric refraction cancelation. It is also worth mentioning that one of the GLONASS-M vehicles are capable of transmitting CDMA signals in GLONASS – L3, which originally was only intended for the Third Generation.

GLONASS-K is the name Third Generation SVs receive. The main changes these propose over the previous versions are an additional CDMA-capable payload, an increased lifetime, a clock stability improvement of an order of magnitude, and a weight reduction of almost a half compared to GLONASS-M, allowing twin launches.

Finally, a newer version of the GLONASS-K is being developed and expected to fly by 2025, the GLONASS-KM. It will feature CDMA-compatible payloads capable of offering modernized and interoperable signals on L1, L3, and L5 as well as all legacy signals.

#### 2.2.2.2 Ground Segment

GLONASS' GS consists of the different elements required for the system to nominally operate which are on Earth's surface, namely the System Control Center (SCC), the Telemetry, Tracking, and Command Centers (TT&C) and Upload Stations (ULS), the Central Clock (CC-M), the Laser Ranging Stations (SLR), and the MS (see *Figure 5: GLONASS Ground Segment*, where red is for the SCC, yellow other operative centers, and green facilities available in the future).

Figure 5: GLONASS Ground Segment

The core of the GS is the SCC, located at Krasnoznamensk, which main goal is to control the constellation as well as each individual satellite as it coordinates all different functions and it processes the gathered information in order to determine satellite clocks, orbits, and updates their navigation messages.

The second element mentioned above are the TT&C Centers. GLONASS has 5 of them located in Russia, in particular at Shchyolkovo, Komsomolsk, St. Petersburg, Ussuriysk, and Yeniseysk. Their main purpose is to track GLONASS satellites in view and log ranging data and telemetry from their signals, which is then forwarded to the SCC where it is processed. Two of this centers, in particular the ones at Shchyolkovo and Komsomolsk, have Mission Uplink Stations (ULS), which receive data from the SCC that has to be uploaded to the satellites, such as basic commands, navigation message updates, etc.

Regarding the system clock, a reference time is kept at Shchyolkovo at the CC-M, which is used by the SCC to compare with the onboard clocks and can be obtained thanks to the correction terms transmitted by the system.

The next element of GLONASS' GS are the eight SLR which are part of the Russian Laser Tracking Network and are located at Svetloye, Shchyolkovo, Zelenchuck, Arkhyz, Zmeinogorsk (Altai Krai), Badary, Irkutsk, and Komsomolsk-na-Amure, and a mobile one used at Baikonur as of 2014<sup>16</sup>. They are provided with three different optical channels: ranging, angular measurement, and photometric. The ranging channel is mostly used as a single source of calibration data for SV ephemeris determination, which is useful for also provide support for the estimation of accuracy and calibration of RF means for orbit measurements, for monitoring the on-board clocks, and applying the data for operational control of GLONASS time and ephemeris data thanks to their geodetic-class RF navigation receivers connected to hydrogen maser

<sup>&</sup>lt;sup>16</sup> Shargorodsky, V., "Russian laser station network and the plan for network expansion", GGOS Bureau on Networks and Communication (BNC) Meeting, Viena, AT, April 30, 2014.

frequency standards, providing the geodetic base for GLONASS reference frame, and finally for providing declared values of the ephemeris precision as well as computation and forwarding of accuracy factor in the navigation frame. Regarding the angular measurement channel, it provides data for implementing a single-point flight control for geostationary satellites by performing periodical orbit inclination measurements. Lastly, the photometric channel is used for registering flight phases during highly elliptical and geostationary orbits (such as engines turn-on), and for attitude stability and determining the motion of a SV relatively to its center of mass.

The last GS element are the MS, of which 4 conform a network located throughout Russian territory (namely at Krasnoznamensk, Shchyolkovo, Yeniseysk, and Komsomolsk) and 6 others were planned to start operating both in Russia and nearby states (in particular in Murmansk, Zelenchuck, Vorkuta, Nurek, Ulan-Ude, and Yakutsk) after 2010<sup>17</sup>. These monitoring and measuring stations are very similar to TT&C Centers in functionality and are sometimes even located in the same place. The have as main objectives to perform measurements on the RF signals received from the SVs, and they also include some parameter analysis.

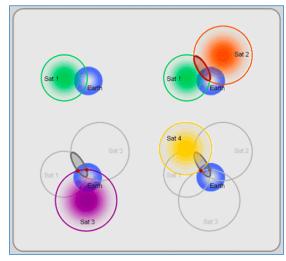

## 2.3 Applications

The main application for GNSS is that for which they are designed: to provide a ground user (or any inside the atmosphere) with precise location coordinates. This may be achieved by applying the trilateration method (see Figure 6: Trilateration method) for which at least signals from at least four different satellites (although it may be implemented at a lower scale with transmitting stations instead) shall be received, and both the data contained in the messages (transmission time, ephemeris, satellite ID in the form of freq. or code, etc.) and their physical parameters (frequency, phase, Doppler, etc.) shall be analyzed. The way trilateration works is that with the first satellite signal, a sphere of possible locations is set around that particular SV. Next, the second signal is used for setting another sphere of positions around the

Figure 6: Trilateration method

second SV, which intersects with the first one and thus narrows down the amount of potential locations. Similarly to the previous cases, the third signal is also use to generate a sphere of locations around the third satellite, which intersects with the last selection and thus results in an ambiguity of only two points. The fourth signal (again by generating a sphere around the SV) assists with calculating a time and local correction that will determine which of the two remaining points is the actual position.

There are many different applications for such a system, so they have been grouped into "Direct Applications", "Indirect Applications", and "Other Applications", all of them detailed in the following subchapters.

<sup>&</sup>lt;sup>17</sup> United Nations Office for Outer Space Affairs, "Current and Planned Global and Regional Navigation Satellite Systems and Satellite-based Augmentations Systems", United Nations publication, AT, 2010.

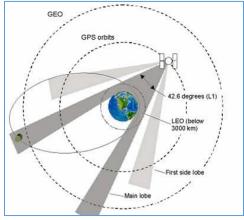

# 2.3.1 Direct Applications

The first set of applications are those that directly relate to the original purpose of the system, more specifically all the navigation applications, which may be further divided into space and ground applications.

Figure 7: GPS-L1 for MEO and GEO

Regarding the space navigation application GNSS networks may be used for orbit determination thanks to the trilateration method explained above. GNSS satellites commonly have directive antennas in order to focus the transmitted power on the Earth's circle where the original users are. For this reason, using these navigation signals is mostly useful for LEO vehicles positioned right between the GNSS satellites and the Earth. Nonetheless, considering the small amount of RF power radiated at the sides of the Earth, some SV at higher orbits may receive GNSS messages of rather low power for short periods of time when flying through the spillover coverage windows as can be seen in Figure 7: GPS-L1 for MEO and GEO.

In regards to ground applications, it should be borne in mind that ground applications will also include using the navigation signals on flying receivers as long as these are inside the atmosphere. That being said, the most common ground application of GNSS is to use a receiver which provides location coordinates or more elaborated data, such as maps and navigation instructions, to users, regardless of these using vehicles (such as ground, water, or air transport) or not. In order to implement GNSS' most direct application, an independent receiver may be used, even though these can also be integrated into other devices more commonly used by people, as is the case of smartphones, tablets, and the currently growing smartwatches and smartbands.

#### 2.3.2 Indirect Applications

GNSS' Indirect Applications have been defined as those in which position data is used by another system which goal is not directly navigation, although it might be included as part of the goal.

The first of these applications, which could be argued whether or not it should instead be considered a direct one, would be the usage of the position data by another system in order to track where all members of the system are. Some particular examples would be to track pets, people with special need, registered criminals such as sex offenders, or people who work in dangerous environments like those under heavy (or relatively heavy) radioactive environments (airline cabin crew and pilots, astronauts).

Another application which could as well be considered direct would be using the navigation data in order to command an autopilot system. This could be used in a variety of sectors, including transport vehicles (mostly unmanned aerial vehicles, planes and ships, but cars might be included in the near future), military applications such as guided ammunition, and the industrial sector (including smart agriculture, construction, and mining among many others, where machinery is automatically guided using GNSS data).

Using positioning data obtained from a GNSS system may also be used for Safe and Rescue (SAR) means, making it easier to locate and rescue those in distress such as hikers, rock climbers, and others. Also

related to sports and recreational activities, GNSS positioning data may be used by sport practitioners such as cyclists in order to log distances, trajectories, and timings. It may also be used in other recreational activities, such as in sky diving in order know the right drop zone, in wreck diving so specific shipwrecks may be found, or even in social networking for knowing when users of certain applications or products are nearby.

Regarding Cartographic and Geology/Geophysics applications, GNSS data may be used for different purposes. The first could be to automatically geo-tag images taken from planes which will be further used for map production and analysis, although this same application may be used by the public for geo-tagging pictures. Another application may be to use the relative displacement of GNSS receivers, which had been previously strategically positioned, in order to preform high precision measurements of Earth movements like those caused by volcanos or faults (as in planar fractures). Somewhat related to geophysics, but in this case closer to safety and construction, survey-grade receivers may be used to monitor position survey markers, buildings, and road construction (among others) thanks to the accurate positioning (down to 1[cm] or sometimes even less) achieved by using both L1 and L2, the latter for ionospheric compensation.

Finally, some other commercial uses of GNSS data may include the use of geo-fences and smart road pricing. Regarding geo-fences, those would allow devices to be switched on or off depending on their location, whereas smart road pricing would allow tracking vehicles and automatically charge them depending on distance and road type as well as gathering other data such as speed and exact trajectories which might be useful for insurance companies.

### 2.3.3 Other Applications

The third kind of applications are all those that don't really fit into the previous groups. These may be understood as "smart uses" of GNSS, meaning that they do not use the signals in the traditional way as navigation messages, but instead they take advantage of certain signal properties in order to obtain different information.

The first example of these applications could be a Global High-Precision Timing System. Thanks to having GNSS satellites orbiting and giving coverage to the whole planet, and broadcasting a specific time, this could be used by devices which include a receiver in order to accurately display or use the GNSS time.

Another way to take advantage of such systems could be to analyze the RF properties of the received signals. Knowing in advance how signals are generated and how atmosphere may change it (attenuation, phase, and polarization changes at different frequencies), knowledge about these and other parameters can be used to determine atmospheric properties, such as layer composition, winds, and many others, which at their turn may be useful for assisting in weather predictions.

To conclude, GNSS signals may also be used both on ground and space, in addition to positioning, for attitude of the receiver. This may be achieved by including multiple antennas and including a phase comparison between the signals received by each.

# 3. Phase 1: The SiGe Module

#### 3.1 Introduction

The SiGe GN3S Sampler (see Figure 8: SiGe GN3S Sampler), also known as SiGe module, is a Universal Serial Bus (USB) GPS-L1 data sampler developed by the GNSS Lab at the SAESD in CU Boulder and SiGe Semidonductor<sup>18</sup>. The main purpose of this device is to be programmed with the Firmware (see chapter 3.3.1 Firmware) and use the Data Logging Software (see chapter 3.3.3 Data Logging), both developed by the GNSS Lab, in order to store and post-process the raw GPS-L1 data.

This module's production had been discontinued after having had three updated designs due to core Application-Specific Integrated-Circuit (ASIC) SE4120L becoming an obsolete part. Nonetheless, thanks to the GNSS Lab having some spare parts as well as there being a couple of potential replacements, it had been decided that the module would be brought back not

Figure 8: SiGe GN3S Sampler

only because of its rather high demand by other research organizations, but also as a starting point and getting-used-to for this thesis project.

## 3.2 Hardware Design

SiGe's hardware can be divided into an electronics part and a casing part, both of which have been revised in this project, with more details in the following subchapters.

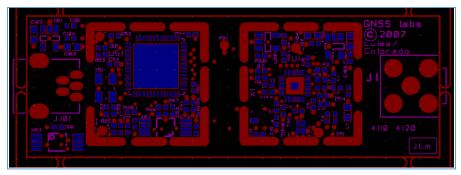

#### 3.2.1 Electronics

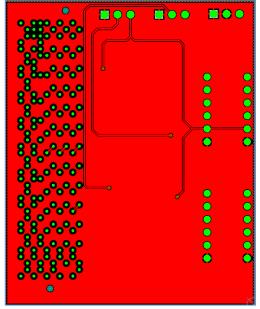

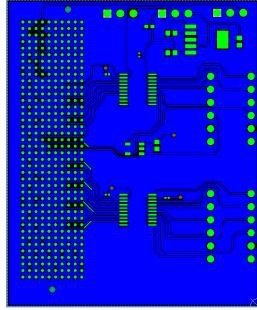

The very first step carried out in this phase has been to determine which design files included the very last changes in order not to have to modify any and save time. From a general point of view in regards to the electronics of the module (see the complete schematics in 8.1 Annexure 1 – SiGe's Schematics and the detailed design files in 8.2 Annexure 2 – SiGe's Layout), they can all be found on the top layer (see Figure 9: SiGe's layout) of a 4-layer Printed Circuit Board (PCB). SiGe's electronic parts can be grouped as RF- or Computer-related, each group having a specific connector (USB or coaxial), having the most RF-sensitive parts protected by an RF shield. Moreover, it is worth mentioning that in order to further isolate the more robust digital (Computer) side from the more sensitive analog (RF) side, each has its own power supply which regulates the power provided by the USB to that required by the individual components.

<sup>&</sup>lt;sup>18</sup> SiGe GN3S Sampler's main website: <a href="https://ccar.colorado.edu/gnss/">https://ccar.colorado.edu/gnss/</a>

Figure 9: SiGe's layout

inaccuracies.