#### Design Techniques for Low Voltage Wideband Delta-Sigma Modulator

#### HE, XIAOYONG

A Thesis Submitted in Partial Fulfillment of the Requirements for the

Degree of doctor of Philosophy

in

Electronic Engineering

The Chinese University Of Hong Kong January 2010 UMI Number: 3436640

#### All rights reserved

#### INFORMATION TO ALL USERS

The quality of this reproduction is dependent upon the quality of the copy submitted.

In the unlikely event that the author did not send a complete manuscript and there are missing pages, these will be noted. Also, if material had to be removed, a note will indicate the deletion.

UMI 3436640

Copyright 2010 by ProQuest LLC.

All rights reserved. This edition of the work is protected against unauthorized copying under Title 17, United States Code.

ProQuest LLC 789 East Eisenhower Parkway P.O. Box 1346 Ann Arbor, MI 48106-1346

#### Abstract

#### Abstract of thesis entitled:

## Design Techniques for Low Voltage Wideband Delta-Sigma Modulator

Submitted by HE Xiao Yong

for the degree of Doctor of Philosophy

in Electronic Engineering

at The Chinese University of Hong Kong

in October 2009

The development of low-voltage design techniques for analog circuits has recently received a lot of attention due to the continuous shrinking of the supply voltage in modern CMOS technologies, which is projected to reduce to 0.5V for low power applications within ten years in the International Technology Roadmap for Semiconductor. This thesis focuses on developing circuit techniques for low-voltage delta-sigma modulator, a functional block that is widely used in mixed-signal integrated circuits. Several delta-sigma modulators operating at supply voltages below 0.9V have been reported in the open literature. However, none of them supports a signal bandwidth wider than 100kHz with a reasonable performance.

In this thesis, we present research works on developing a low-voltage delta-sigma modulator with a wide signal bandwidth. Specifically, a 0.5V complex low-pass continuous-time (CT) third-order delta-sigma modulator that has a single-sided signal bandwidth of 1MHz, targeting for application in Bluetooth receivers, is presented

without using any internal voltage boosting techniques which are potentially harmful to the reliability of the device. The wide bandwidth of the modulator at this low supply voltage is enabled by a special common-mode (CM) level arrangement in the system level and by new low-voltage amplifies. Realized in a 0.13µm CMOS process the proposed modulator achieves a 61.9-dB peak signal-to-noise-and-distortion ratio at the nominal supply of 0.5V with 3.4mW consumption, and occupies an active area of 0.9mm<sup>2</sup>. The modulator achieves the best figure-of-merit among its class.

Furthermore, a new dynamic CM level shifting technique for low-voltage CT delta-sigma modulators that employ a return-to-open feedback DAC is reported in the thesis. The technique maintains a stable CM level at the amplifier's inputs for this type of modulators. Simulation results show that it improves the modulator's SNDR by 11%.

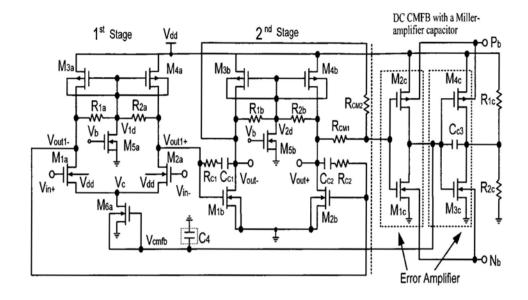

Finally, another new 0.5V fully differential wideband amplifier, which can be used in the wideband modulator, has been proposed. The gate-input two-stage amplifier employs a DC common-mode feedback circuit that uses a Miller-amplified capacitor for its frequency compensation. With the proposed technique, the power consumption of the low-voltage amplifier is drastically reduced.

#### 摘要

参照国际半导体技术的演进蓝图,在未来十年内低电压应用的供电电压将降低到 0.5 伏。由于现代 CMOS 技术工艺尺寸的不断降低激起模拟电路的低电压设计技术的研究。本论文集中讨论低电压过采样调制解调器这一广泛应用于混合信号集成电路功能模块的电路设计技术。公开的文献里已经报道了多个供电电压低于 0.9 伏的过采样调制解调器,但是它们在合理的性能下的带宽都不超过 100k 赫兹。

本论文呈现设计低压宽带过采样调制解调器所进行的工作。具体的说,本论文呈现一个单边信号带宽为 1M 赫兹的三阶连续时间复数低通过采用调制解调器,应用目标为蓝牙接收器,工作电压为 0.5 伏。在本设计中,并没有采用有害于器件的可靠性内部电压推进技术。 本调制解调器在低压下的高宽带特性的取得要归功于系统级的特殊共模电压布局以及一个新的运算放大器。本论文提出的调制解调器实现于 0.13 微米 CMOS 工艺,取得了 61.9dB 的峰值信噪比,供电电压为 0.5V,功耗为 3.4 毫瓦,占用米面积为 0.9 平方毫米,在同类调制解调器中,取得了最佳的性能指数。

此外,本论文提出一个新的动态共模电压提升技术,可用于采用 RTO DAC 的低压连续时间调制解调器中。此技术,在放大器的输入端维持了一个稳定的共模电压。仿真结果表明,采用此技术调的制解调器的信噪比提升了11%。

最后,论文提出了另一个新的 0.5 伏全差分的宽带运算放大器,可用于宽带调制解调器中。这个栅输入的两级运算放大器,采用了米勒放大电压电容的频率补偿直流共模负反馈电路。这一米勒放大电容频率补偿负反馈技术,极大的降低了低压运放的功耗。

I

#### Acknowledgement

This thesis could not be finished without the help and support of many people who are gratefully acknowledged here.

At the very first, I'm honored to express my deepest gratitude to my dedicated research supervisor, Prof. Kong-Pang Pun. Without his guidance and help, I couldn't finish my thesis. His patience, kindness, valuable ideas, suggestions and generous financial support are greatly appreciated.

Second, I would like to thank the professors in ASIC laboratory, who are Prof. Chiu-Sing Choy, Prof. Cheong-Fat Chan, Prof. Ka-Nang Leung. They provide course giving me the foundation of my research. Thanks you all very much.

Then, it is my pleasure to express my thanks for Mr. WY Yueng, our technician, who gives me valuable technical support for the design software and help build the chip test equipments.

I owe special thanks to Chan Chi Hong, Hang Wei, Leung Pak Keung, K.Y. Wong for their grateful help on the birth of my twins. I wish to extend my thanks to all research students of ASIC lab, Xin Ling, Zhen YanQi, Jia JingBin, Xu Ke, Fan Wen, Chen Yan, Tang Xian, Zhao YinSheng, Hong Yang, Guo JianPing, Li Bing, Zhan Ming, Ko Chi-Tung, Tang Siu-kei. I am very happy to work and play with them during the years in ASIC laboratory.

At last but not least, I would like to thank my parents, sisters and brothers for their always support in my life.

I'm very grateful to my wife for her endless love and encouragement, and my loveable twins. They are my heart.

I take the chance to express my thanks to all the people who give me help or encouragement during my Ph.D study in CUHK.

## **Table of Content**

|             | Acknowledgement |                                                              |     |  |  |  |

|-------------|-----------------|--------------------------------------------------------------|-----|--|--|--|

| Table of Co | ontent          |                                                              | . П |  |  |  |

|             |                 |                                                              |     |  |  |  |

| Table of Ta |                 |                                                              |     |  |  |  |

| Chapter 1   |                 | ction                                                        |     |  |  |  |

| 1.1.        |                 | ch motivation                                                |     |  |  |  |

| 1.2.        | -               | al contribution of this thesis                               |     |  |  |  |

| 1.3.        |                 | organization                                                 |     |  |  |  |

| Chapter 2   |                 | ew of delta-sigma modulator and quadrature signal processing |     |  |  |  |

| 2.1.        |                 | of delta-sigma modulator                                     |     |  |  |  |

| 2.2.        |                 | oise shaping of delta-sigma modulator                        |     |  |  |  |

| 2.3.        |                 | rder and second-order low-pass modulators                    |     |  |  |  |

| 2.4.        | -               | gies of delta-sigma modulators                               |     |  |  |  |

| 2.5.        | -               | ture signal processing                                       |     |  |  |  |

| Chapter 3   | •               | design of complex CT delta-sigma modulator                   |     |  |  |  |

| 3.1.        |                 | ng of CT modulators from DT prototypes                       |     |  |  |  |

| 3.2.        | Synthe          | sis for complex CT modulators                                |     |  |  |  |

| 3           | 3.2.1.          | The DT complex loop filter prototype H(z)                    |     |  |  |  |

| 3           | 3.2.2.          | Transformation from H(z) to H(s)                             |     |  |  |  |

| 3           | 3.2.3.          | The synthesized complex CT modulator                         |     |  |  |  |

| 3           | 3.2.4.          | Simulations of the synthesized modulator                     |     |  |  |  |

| Chapter 4   |                 | nentation of complex CT delta-sigma modulator                |     |  |  |  |

| 4.1.        | Nonide          | ealities in oversampling delta-sigma modulator               |     |  |  |  |

| 4           | 1.1.1.          | Op-amp non-idealities                                        |     |  |  |  |

| 4           | 1.1.2.          | Time constant variation                                      |     |  |  |  |

| 4           | 4.1.3.          | Comparator nonidealites                                      |     |  |  |  |

| 4           | 4.1.4.          | Feedback DAC nonidealites                                    |     |  |  |  |

| 4           | 4.1.5.          | Clock jitter                                                 |     |  |  |  |

| 4.2.        |                 | simulation using ideal models                                |     |  |  |  |

| 4.3.        | Circuit         | implementation                                               |     |  |  |  |

| 4           | 4.3.1.          | Noise consideration                                          |     |  |  |  |

| 4           | 1.3.2.          | Amplifier design                                             |     |  |  |  |

| 4           | 1.3.3.          | Operation of the integrator                                  |     |  |  |  |

| 4           | 1.3.4.          | Bias circuit                                                 |     |  |  |  |

| 4           | 4.3.5.          | Comparator and DAC                                           |     |  |  |  |

| 4.4.        |                 | stor-level simulation results of the modulator               |     |  |  |  |

| 4.5.        | •               | of the modulator                                             |     |  |  |  |

| Chapter 5   | Measu           | rement results                                               | 75  |  |  |  |

| 5.1.      | Measurement results with 171.875KHz sine-wave input          | 75  |

|-----------|--------------------------------------------------------------|-----|

| 5.2.      | Measurement result with 1MHz sinewave input                  | 81  |

| Chapter 6 | A 0.5V Amplifier for a 1MHz CT Complex Delta-Sigma Modulator | 83  |

| 6.1.      | 0.5V wide band amplifier                                     | 83  |

| 6.2.      | The Modulator Design                                         | 89  |

| 6.3.      | Simulation Results                                           | 92  |

| Chapter 7 | Dynamic CM shift technique for CT Delta-sigma modulator      | 95  |

| 7.1.      | Dynamic CM shift techinque                                   | 95  |

| 7.1.      | Simulation results                                           | 98  |

| Chapter 8 | Conclusions and recommendation for future work               | 102 |

| 8.1.      | Future works                                                 | 103 |

|           | es                                                           |     |

| Appendix. |                                                              | 112 |

|           | cation list                                                  |     |

|           |                                                              |     |

### **Table of Figures**

| Fig 1.1 Process feature sizes (left), supply and threshold voltage scaling (right)             | 2   |

|------------------------------------------------------------------------------------------------|-----|

| Fig 1.2 A low-IF receiver architecture                                                         | 4   |

| Fig 2.1 Block Diagram of Oversampling Delta-Sigma Modulator                                    | 7   |

| Fig 2.2 General architecture of a delta-sigma modulator                                        | 8   |

| Fig 2.3 z-domain linear model of delta-sigma modulator                                         | 9   |

| Fig 2.4 Power spectral density of uniformly distributed quantization noise                     | .10 |

| Fig 2.5 First-order delta-sigma modulator                                                      |     |

| Fig 2.6 Second-order delta-sigma modulator                                                     | .12 |

| Fig 2.7 Output spectrum of first-order delta-sigma modulator with -8dBFs sine-wave input       | 13  |

| Fig 2.8 Output spectrum of second-order delta-sigma modulator with -8dBFs sine-wave in         | put |

|                                                                                                |     |

| Fig 2.9 Two-stage cascade topology modulator                                                   |     |

| Fig 2.10 Single stage modulator with distributed input and distributed feedback topology       | .17 |

| Fig 2.11 Single stage modulator with distributed input and distributed feedforward topological |     |

|                                                                                                |     |

| Fig 2.12 Trigonometric format of a real signal                                                 |     |

| Fig 2.13 Quadrature mixing                                                                     |     |

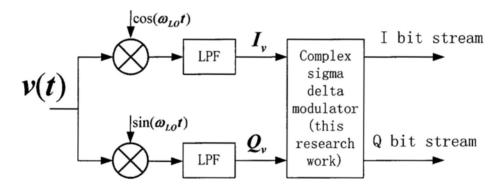

| Fig 2.14 Diagram of a complex delta-sigma converter including the quadrature mixer             |     |

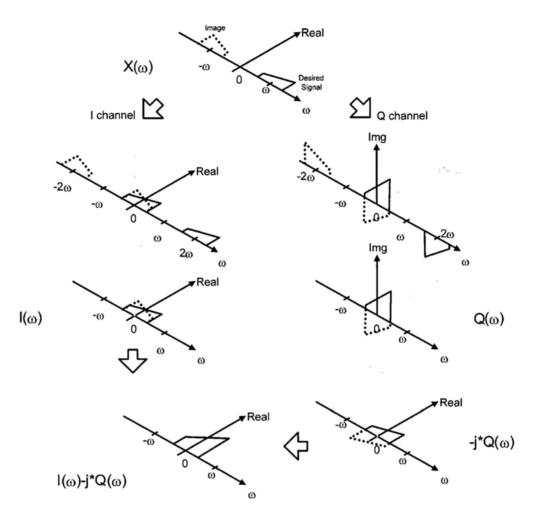

| Fig 2.15 Spectrum of signals along the I and Q channels                                        |     |

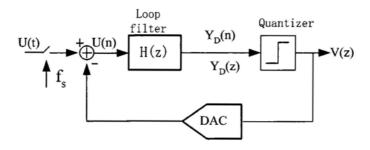

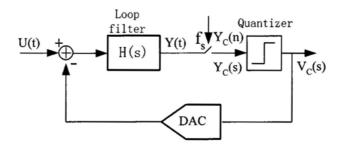

| Fig 3.1 Block diagram of DT delta-sigma modulator                                              |     |

| Fig 3.2 Block diagram of CT delta-sigma modulator                                              |     |

| Fig 3.3 Block diagram of open loop of CT modulator                                             |     |

| Fig 3.4 Block diagram of open loop of DT modulator                                             |     |

| Fig 3.5 NRZ DAC impulse response and corresponding laplace transform                           |     |

| Fig 3.6 RZ DAC impulse response and corresponding laplace transform                            |     |

| Fig 3.7 Noise Transfer function H(z) (a) pole-zero map; (b) Frequency response                 |     |

| Fig 3.8 Quadrature resonator realizing                                                         |     |

| Fig 3.9 Topology of the CT complex modulator with distributed feedback                         |     |

| Fig 3.10 The architecture of the complex CT modulator                                          |     |

| Fig 3.11 Return-to-Zero DAC and its control clock                                              |     |

| Fig 3.12 Simulated output spectrum of the complex CT modulator                                 |     |

| Fig 3.13 Simulated SNR performance versus input level.                                         |     |

| Fig 4.1 Typical RC integrator with single pole amplifier used in CT modulators                 |     |

| Fig 4.2 Excess loop delay of NRZ DAC (a) ideal case (b) practical case with delay              |     |

| Fig 4.3 Excess loop delay of RZ DAC (a) ideal case (b) practical case with delay               | .45 |

| Fig 4.4 Clock jitter error source in typical CT modulator                                      |     |

| Fig 4.5 DAC output (a) without jitter (b) with jitter (c) and the uncertainty                  |     |

| Fig 4.6 Simplified circuit of the CT complex delta-sigma modulator                             |     |

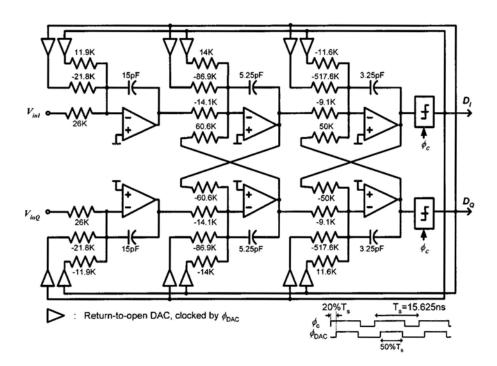

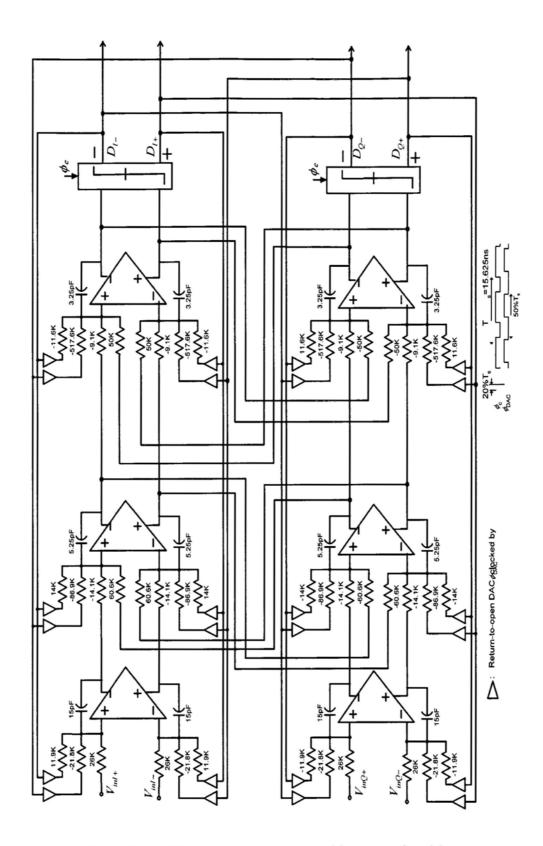

| Fig 4.7 Fully differential schematic circuit of the proposed modulator                         |     |

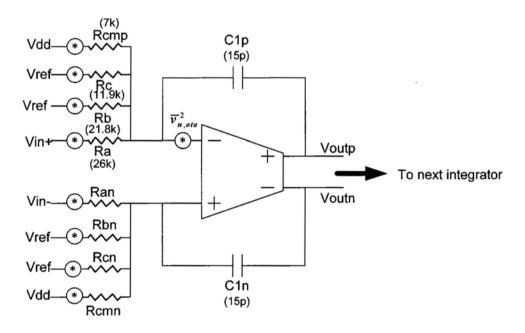

| Fig 4.8 First integrator with additional noise source caused by amplifier and resistors        | .56 |

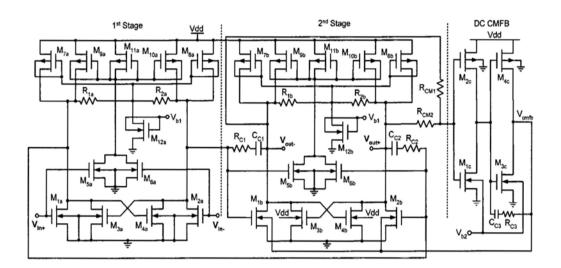

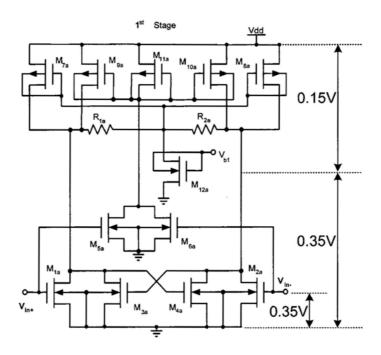

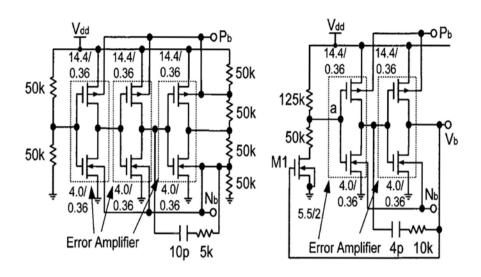

| Fig 4.9 Schematic for the low-voltage gate-input two-stage OTA                         | 57  |

|----------------------------------------------------------------------------------------|-----|

| Fig 4.10 The DC bias of the first stage                                                | 59  |

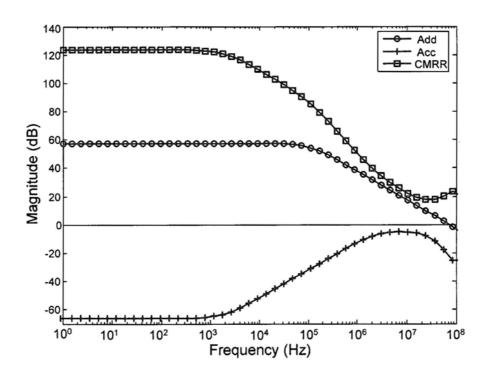

| Fig 4.11 Simulated performance of Add, Acc, and Add/Acc the amplifier                  | 61  |

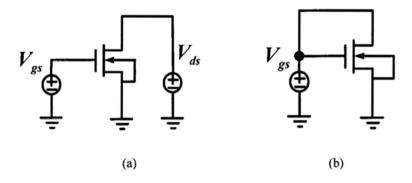

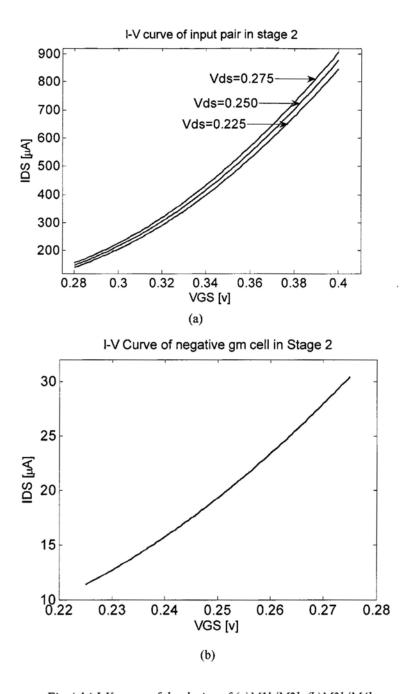

| Fig 4.12 I-V curve simulation schematic for (a) Input pair and (b) negative gm pair    | 62  |

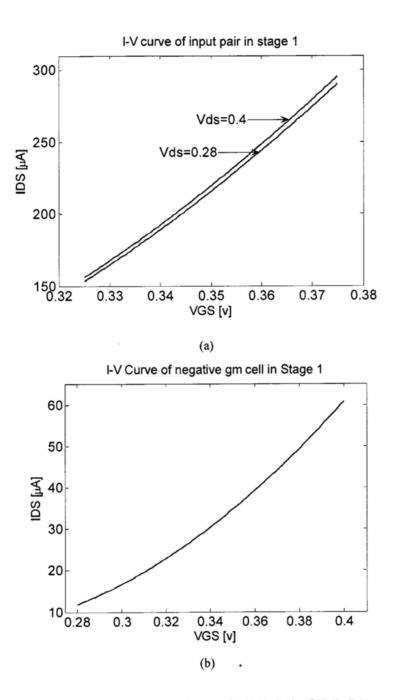

| Fig 4.13 I-V curve of the device of (a)M1a/M2a (b)M3a/M4a                              | 63  |

| Fig 4.14 I-V curve of the device of (a)M1b/M2b (b)M3b/M4b                              | 64  |

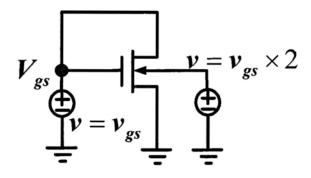

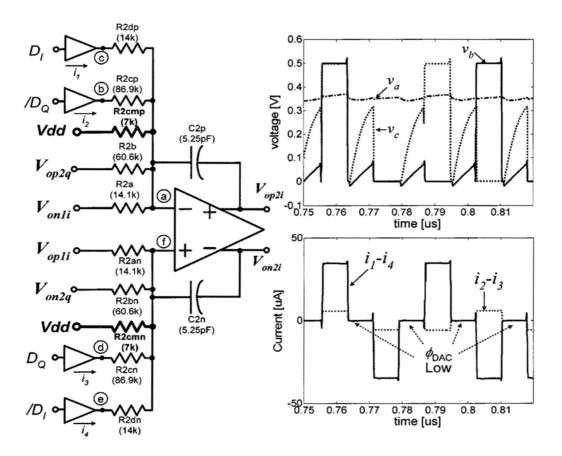

| Fig 4.15 Schematic of bulk current simulation                                          | 65  |

| Fig 4.16 Bulk current of M3b/M4b                                                       | 65  |

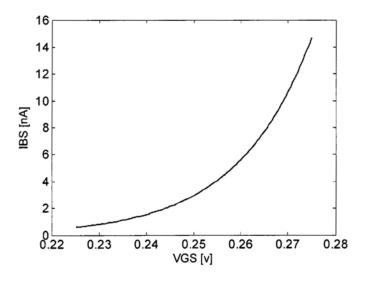

| Fig 4.17 Detailed circuit for the second integrator in the I-path                      | 67  |

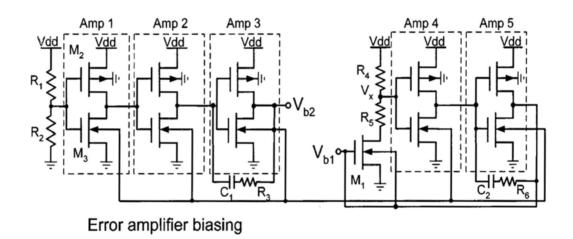

| Fig 4.18 Bias generation circuit for V <sub>b1</sub> and V <sub>b2</sub> in Fig 4.9    | 68  |

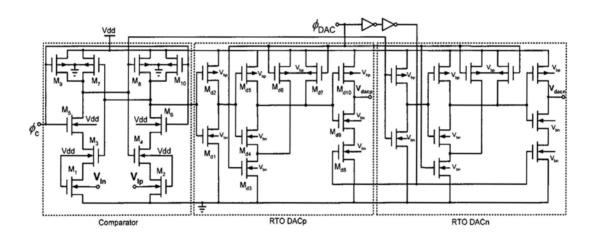

| Fig 4.19 Comparator and RTO DAC circuit                                                | 70  |

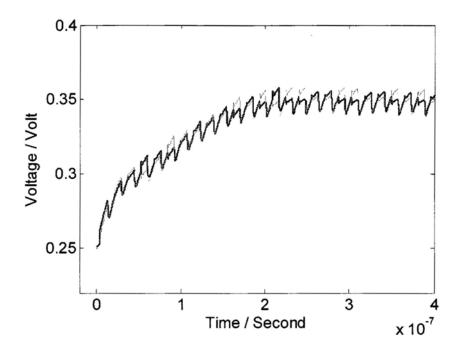

| Fig 4.20 Waveform of input node of the amplifier in I channel                          | 71  |

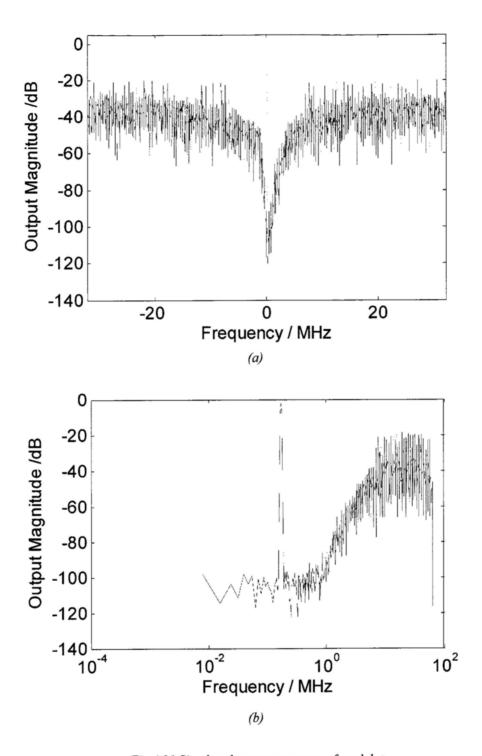

| Fig 4.21 Simulated output spectrum of modulator                                        | 72  |

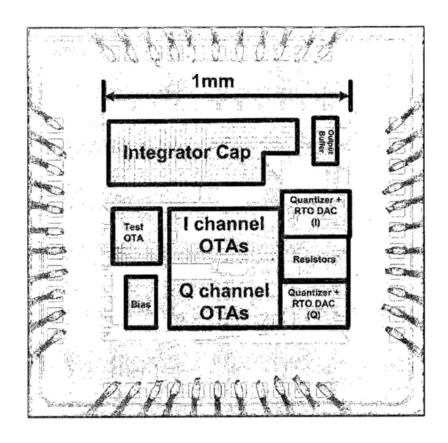

| Fig 4.22 Die photo of the 0.5V complex $\Delta\Sigma$ modulator in a 0.13 $\mu$ m CMOS |     |

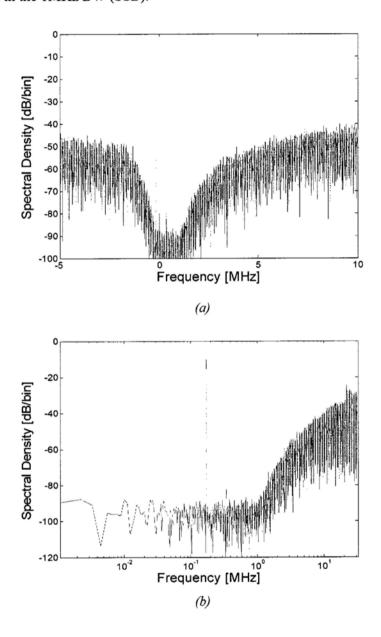

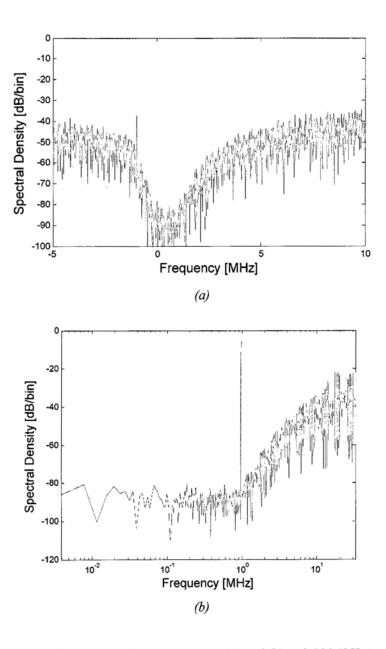

| Fig 5.1 Measured output spectrum (a) and (b)                                           |     |

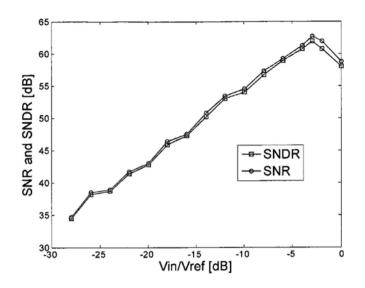

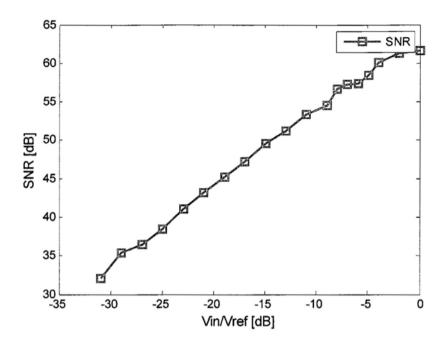

| Fig 5.2 Measured SNR and SNDR versus Vin at 0.5V supply (Vref = $ 1+j $ Vpp-diff)      | 77  |

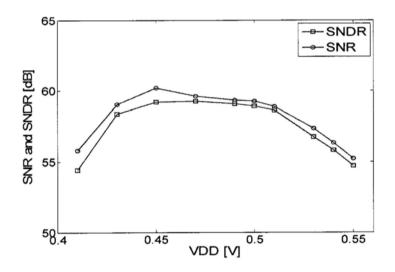

| Fig 5.3 SDR and SNDR versus supply voltage                                             | 77  |

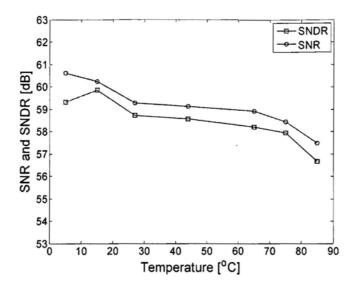

| Fig 5.4 SNR and SNDR versus temperature.                                               | 78  |

| Fig 5.5 Measured output spectrum (a) and (b) with 980.5kHz input                       | 81  |

| Fig 5.6 Measured SNR versus Vin at 0.5V supply with fin=980.5kHz.                      | 82  |

| Fig 6.1 The fully differential amplifier with overall miller-compensated CMFB Loop     | 84  |

| Fig 6.2 Bias generation circuit for the amplifier                                      | 85  |

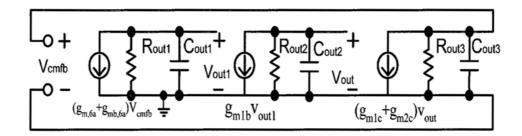

| Fig 6.3 Small signal model of the CMFB loop                                            |     |

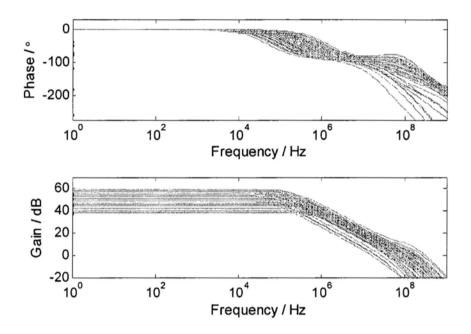

| Fig 6.4 AC response of the amplifier over PVT corners                                  | 89  |

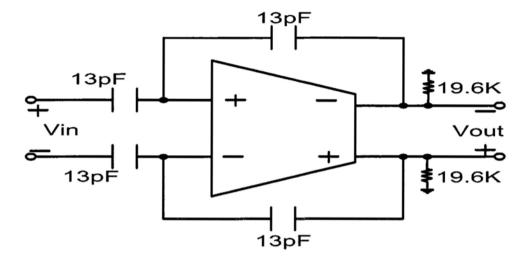

| Fig 6.5 Simplified schematic of the $\Delta\Sigma$ modulator                           |     |

| Fig 6.6 Schematic for simulation of amplifier's output settling                        | 91  |

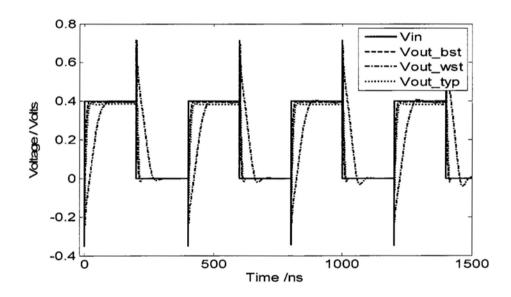

| Fig 6.7 Differential output waveform of the amplifier                                  | 91  |

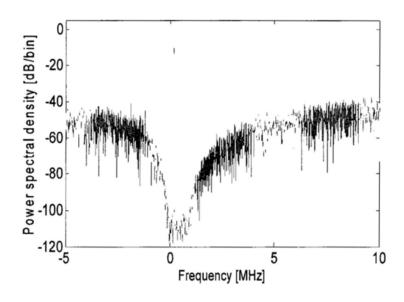

| Fig 6.8 Simulated output spectral density double-sided plot                            | 93  |

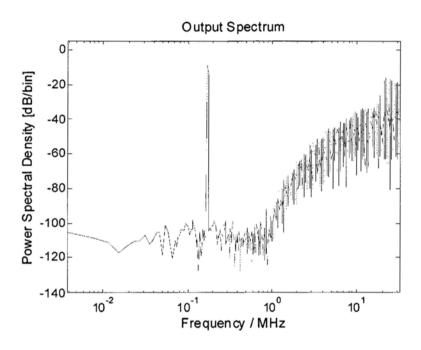

| Fig 6.9 Simulated output spectral density of the modulator single-sided                | 94  |

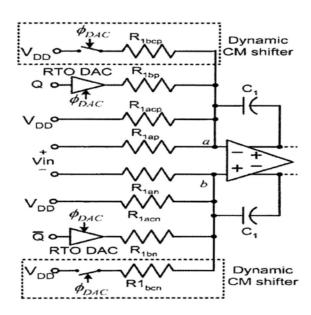

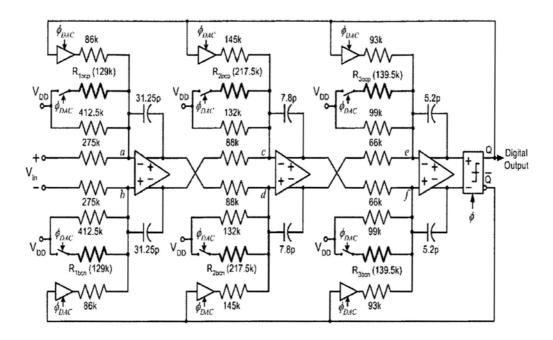

| Fig 7.1 An active RC integrator stage and dynamic CM level shifting                    | 96  |

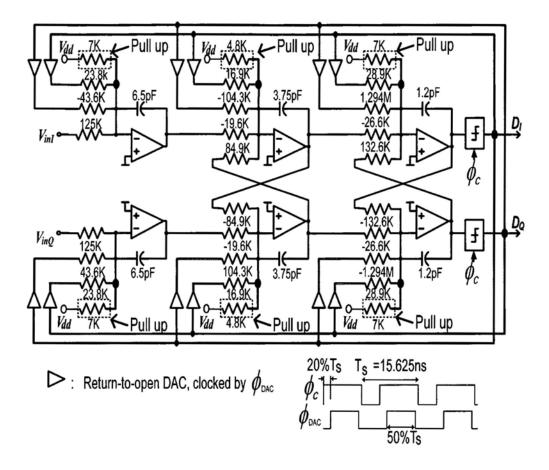

| Fig 7.2 A 3rd 1-bit CT low-pass modulator with dynamic CM level shifting               | 98  |

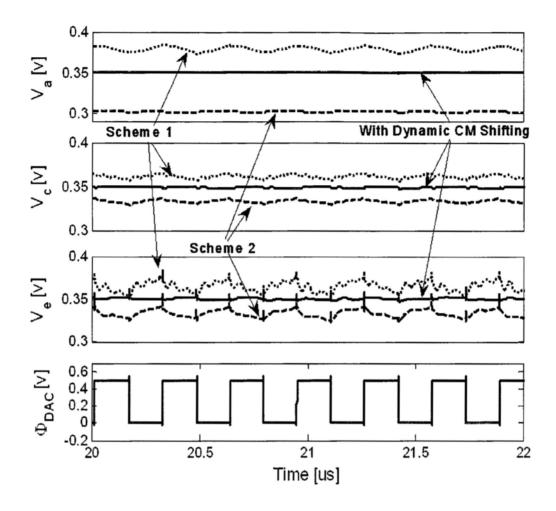

| Fig 7.3 Simulated waveforms at nodes a, c and e for different CM shifting techniques   | 99  |

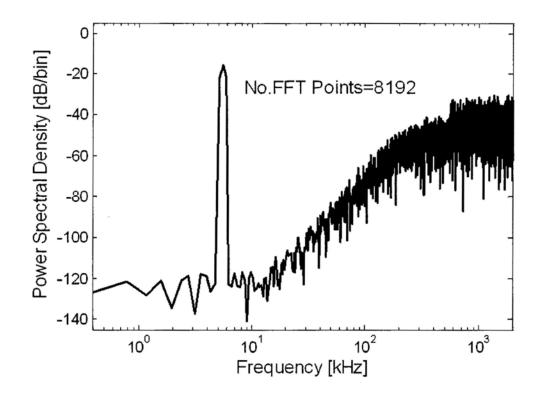

| Fig 7.4 Simulated output spectrum for a 1V <sub>pp,diff</sub> 5.47kHz input            | 100 |

|                                                                                        |     |

|                                                                                        |     |

|                                                                                        |     |

|                                                                                        |     |

|                                                                                        |     |

### **Table of Tables**

| Table 3-1 CT equivalents for DT loop filter poles                   | 28 |

|---------------------------------------------------------------------|----|

| Table 4-1 Transistor Sizes and Component Values                     | 61 |

| Table 4-2 Transistor Sizes and Component Values for the Bias        | 69 |

| Table 4-3 Transistor Sizes for the 0.5V comparator and DAC          | 70 |

| Table 5-1 Performance summary                                       | 80 |

| Table 5-2 Performance comparison with sub-1V Delta-Sigma modulators | 80 |

| Table 6-1 Transistor Sizes and Component Values for amplifier       | 84 |

| Table 6-2 Simulated performance of the proposed amplifier           | 88 |

#### **Chapter 1 Introduction**

#### 1.1. Research motivation

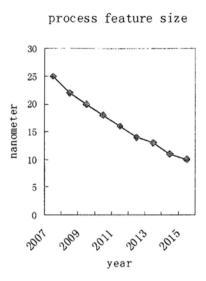

For past several decades, the CMOS technology has continuously advanced according to "Moore's law," and it is expected that this scaling will maintain for at least another decade. The International Technology Roadmap for Semiconductor (ITRS) gives us a unique opportunity to look into the projected future of semiconductor technology. The feature-size of CMOS technology is projected to keep scaling deeper into nanoscale dimensions. As a consequence of this technology scaling, functionality density, the intrinsic speed of the devices and the signal processing capability of circuits will continuous increase. Specially, digital signal processing technique is becoming more and more ubiquitous, and digital circuits will continue to benefit from the projected advances in technology feature size. Fig 1.1 shows the projections for the device feature size, supply voltage, and the threshold voltage, based on [1].

However, for nanoscale devices with ultra-thin gate-oxide, the lifetime degrades exponentially with the supply voltage, rather than with the electric field across the oxide layer, as reported in [2][3]. In order to keep reliability, to avoid circuit breakdown, to avoid thermal problems and to reduce power density, the maximum supply voltage has to be scaled down appropriately.

Supply voltage down scaling is mainly driven by the digital circuits since it reduces the power consumption quadratically. Along with a reduction in the supply voltages, the transistor threshold voltage,  $V_T$ , is reduced but not as aggressively, in order to maintain good ON/OFF characteristic of the MOS device, and to reduce static leakage levels in digital logic circuits. Even though the power supply voltage scaling is pushed by digital regime, the analog counterpart still needs relatively high supply to maintain performance.

Fig 1.1 Process feature sizes (left), supply and threshold voltage scaling (right)

Digital circuits benefit from both size and power supply scaling. It is not clear, however, that analog circuits will benefit from further technology scaling. Device scaling lowers the supply voltage, thereby leaving less headroom for analog circuit design. Also, a lowered supply voltage means reduced dynamic range unless the noise floor is also reduced, which typically requires increased analog power dissipation [4][5]. This situation will be exacerbated as state-of-the-art CMOS technologies enter the sub-1V supply regime. Moreover, the ITRS roadmap projects supply voltages down to 0.5V and even 0.45V for low power applications in [1]. For energy constrained applications, such as wireless micro-sensors, implantable devices, and devices relying on ambient energy scavenging, true low supply voltages are desirable to achieve the most energy efficient operation.

Definitely it is indispensable for the interfaces, mainly the analog circuits, such as data converters and filters, servicing as a bridge between digital regime and the real analogous world. Nowadays it is very common that both the digital parts and such analog interfaces circuits are integrated on a single chip, so called SoC (System-on-Chip). For systems-on-chip integrated circuits, it is desirable to develop

analog interfaces that operate with supply voltages that remain compatible with the low supply voltages for extremely scaled technologies.

Scaling down of power supply driven by the complex digital systems brings a big challenge on analog circuit design if the SoC maintains a single supply for both such interface circuits and digital parts. Many interested design techniques are investigated and several analog blocks operating in 0.5V power supply are implemented, such as analog fifth-order ecliptic filter [8], 8-bit 10MSps pipeline Analog-to-Digital converter [7], ultra-low power low speed SAR Analog-to-D converter [6]. The resolutions of such Nyquist-rate low-voltage ADCs are limited to about 5 to 8 bits [6][7] (effective number of bits). On the other hand, over-sampling modulators can offer higher resolutions at the expense of speed. As for delta-sigma ( $\Delta\Sigma$ ) modulators operating below 0.9V, researches reported in [9][10] have pushed the SNDR to as high as 77dB, but only over a very limited signal bandwidth ranging from 8kHz to 25kHz, suitable only for voice/audio applications.

This research investigates the design of wideband analog-to-digital converter operating normally at 0.5V. Due to the challenge of the wideband requirements under low power supply, the analog blocks inside the data converter will suffer from circuit imperfections. Considering this, the over-sampling delta-sigma ADC, which is generally believed to be less sensitive to circuit imperfections, is chosen in this research.

A key challenge in low-voltage modulator design is to realize the low-voltage switches that need to pass signals at a level around Vdd/2, e.g. the switches at the input and at the op-amps' outputs. One popular approach is to use techniques that eliminate signal path switches, which include the switched-opamp [11][12][13][14], and switched-RC techniques [10]. The switched-opamp technique offers good performance, but typically requires internal clock voltage boosting for the input sampling switches and sometimes other switches [10][11], which has the potential of degrading the reliability of the circuits. The switched-RC solution does not need internal clock boosting, but the resistors used in the signal path may impose a limit on the speed of circuit. Another solution is to use low-threshold devices to realize the

low-voltage switches [15]. This approach offers a true low-voltage solution, but the leakage of low threshold devices remains a problem to be addressed to improve the performance of the modulators.

The continuous-time (CT) modulator architecture [9][16] is adopted in this research to avoid some of the problems associated with the low-voltage switches, despite the modulator's higher sensitivity to the clock jitter noise. CT modulators do not need switches except in the clocked comparator and the feedback digital-to-analog converters (DAC). In [9], a return-to-open (RTO) DAC concept was introduced that further removes the switches operating at Vdd/2 in the differential DAC by using RTO signaling.

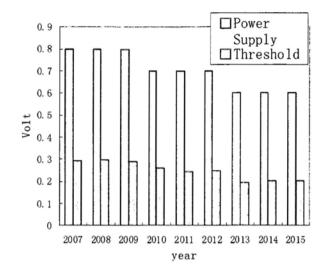

Fig 1.2 A low-IF receiver architecture

The main objective of this research is to develop a true low-voltage delta-sigma modulator with a wide signal bandwidth for analog-digital conversion in wireless receivers. Specifically, we target to design a modulator for direct IF digitization in a Bluetooth receiver that employs a low-IF structure as shown in Fig 1.2. The Bluetooth receiver, which operates in the 2.4 GHz ISM band [25], has a baseband signal bandwidth of 1MHz. In the low-IF receiver structure shown in Fig 1.2, the input of the IF ADC occupies a single-sided band (SSB) from DC to 1MHz, so our modulator will be a complex one. Given that several RF front-ends at low supply voltage have

been demonstrated [17]-[22], the low-voltage modulator presented in this thesis can enable the realization of fully integrated, highly digital low-voltage wireless receivers [23][24].

#### 1.2. Original contribution of this thesis

This thesis is focused on investigating the design techniques of implementing a wideband modulator operating in supply as low as 0.5V. The original contributions of the research work are summarized below.

- i. With a proposed CM level arrangement in system level design and high speed amplifier, a continuous-time complex 1-MHz delta-sigma modulator is designed and implemented in 0.13µm CMOS process with standard threshold transistors, without adopting a voltage boost technique which commonly exists in ultra-low voltage circuits. The demonstrated prototype chip achieves 65.7dB dynamic range and consumes 3.4mW in normal conditions test. The full function and performance against variable supply voltage, different input amplitude and temperature, are also provided in this thesis. To our best knowledge, this research is the first one demonstrating the bandwidth of 1MHz modulator with a supply below 0.8V.

- ii. A miller compensated DC-CMFB loop is proposed to reduce the low-voltage amplifier's power consumption. The amplifier's performance and stability are verified by extensive simulation. The performance and feasibility of proposed topology are verified by silicon chip.

- iii. A CM level shift technique is proposed for low-speed modulator for better performance. The performance of improvement with the proposed technique is verified by simulation.

#### 1.3. Thesis organization

This thesis covers the theoretical analysis of CT delta-sigma A/D converters, the system level and the circuit level design of a wideband, low-voltage CT delta-sigma modulator, and the measurement of the prototype chips.

Chapter 2 reviews the basic concepts of delta-sigma A/D converters and complex signal processing.

Chapter 3 talks about the mapping from discrete time (DT) architecture to CT architecture and discussing the system design of complex CT delta-sigma modulator.

Chapter 4 describes the design issues for delta-sigma modulators with CT implementations. Effects of various non-idealities and potential solutions to deal with them are discussed. Details of the design of the modulator are presented and important simulation results are included.

Chapter 5 covers the layout, measurement setup and measurement results.

Chapter 6 presents a new 0.5V fully differential amplifier topology that does not require replica biasing. Simulation results of the amplifier and the modulator that uses it are included.

Chapter 7 discusses a dynamic common-mode level shift technique proposed for low-voltage CT delta-sigma modulators.

Chapter 8 concludes this thesis and proposes recommendations for future research.

# Chapter 2 Overview of delta-sigma modulator and quadrature signal processing

#### 2.1. Basic of delta-sigma modulator

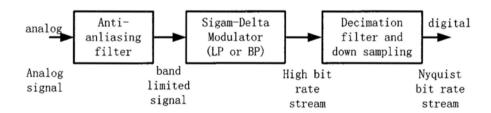

A generic block diagram of oversampling delta-sigma A/D converter (low pass or band pass) is shown in Fig 2.1. For DT modulator, generally an anti-aliasing filter is used to attenuate out-of-band frequency components of the analog input signal so that its output becomes band-limited and the anti-aliasing filter also suppresses the aliasing due to sampling inside the following delta-sigma modulator. For CT modulator, this filter is not necessary because the anti-aliasing is an inherent property of the CT delta-sigma modulator [26]. The delta-sigma modulator converts the input analog signal to a high bit-rate digital signal. The last stage in the Fig 2.1, called the decimation filter and down-sampler, converts the modulator output into a high-resolution digital signal normally at the Nyquist frequency, and the result is signals coded in a large number of bits at the Nyquist rate. This research focuses only on the modulator design and its implementation.

Fig 2.1 Block Diagram of Oversampling Delta-Sigma Modulator

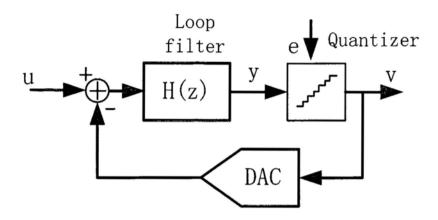

The modulator, as the core of a delta-sigma A/D converter, has a typical topology consisting of a high pass filter, one quantizer and the feedback DAC, shown in Fig 2.2.

Fig 2.2 General architecture of a delta-sigma modulator

#### A. Loop filter, H(z)

For a CT modulator, the DT loop filter H(z) should be replaced by a CT loop filter H(s). The loop filter has large gain within the signal band while it attenuates out-of-band signals. The loop filter can be implemented by a switched-capacitor circuit in DT case and an active RC circuit, for instance, in the CT case.

#### B. Quantizer

The quantizer works as an internal A/D converter to generate the modulator output. Its output can be single-bit or multi-bit (for multi-bit modulator). A single-bit quantizer is realized by a comparator. A multi-bit quantizer is normally realized by a flash ADC for high speed conversion.

#### C. Feedback DAC

The feedback DAC is employed to convert the digital modulator output to analog and subtract it from the modulator input. For a single bit modulator, the output of the feedback DAC switches between two distinct values. For multi-bit modulator, the output switches among a multiple of values depending on the comparator output. The quantizer is essentially a non-linear circuit and the delta-sigma modulator can not be considered as a linear feedback system in a strict sense. However, the quantization

error inherent in quantizing can be modeled as white noise, and the nonlinear quantizer can thus be approximated as an adder and the modulator is modeled as a linear system as shown in Fig 2.3.

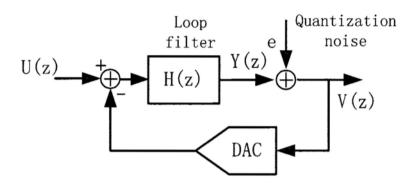

Fig 2.3 z-domain linear model of delta-sigma modulator

In Fig 2.3, U denotes the analog input, and Y is the quantizer's input. V is the modulator output and E is the quantization noise. Considering the DT case, the relationship between U, V and E can be readily derived as

$$V(z) = \frac{H(z)}{1 + H(z)}U(z) + \frac{1}{1 + H(z)}E(z)$$

(2-1)

where the STF(z) and NTF(z) are called signal transfer function and noise transfer function, respectively, of the modulator. From the expression of NTF(z), the zeros of NTF(z) are the poles of the H(z). When the loop filter H(z) has a high gain, i.e., |H(z)| >> 1, in the band of interest, we have

$$V(z) \approx U(z)$$

In other words, the output signal contains almost unchanged input signal plus quantization noise shaped by NTF(z). Since quantization noise is largely pushed out-of-band by NTF, high in-band signal-to-noise ratio (SNR) can be obtained.

#### 2.2. NTF noise shaping of delta-sigma modulator

In Fig 2.3, if the signal active at the input of the quantizer is sufficiently busy, the quantization error e(n) can be approximated as an random number uniformly distributed between  $\pm \Delta$ , where delta is the difference between two consecutive quantization level. The mean square value of the quantization noise, i.e., its power, can be calculated from its probability density function as follows:

$$\mathbf{P}_{e} = \frac{1}{\Delta} \int_{-\frac{\Delta}{2}}^{\frac{\Delta}{2}} e^{2} de = \frac{\Delta^{2}}{12}$$

(2-2)

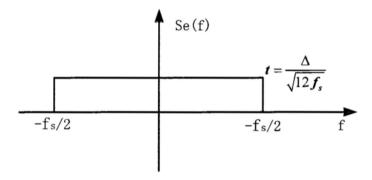

The noise power is independent of the sampling frequency  $f_s$ . Assume the quantization noise is white as shown in Fig 2.4, i.e., having a flat power spectral density (PSD), the PSD can be obtained as:

$$t = \frac{1}{\sqrt{12f_s}} \tag{2-3}$$

Fig 2.4 Power spectral density of uniformly distributed quantization noise

NTF of the modulator pushes much of the quantization into high frequency, normally much higher than the interest bandwidth, resulting in a high in-band signal-to-noise ratio (SNR).

#### 2.3. First-order and second-order low-pass modulators

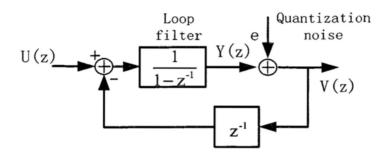

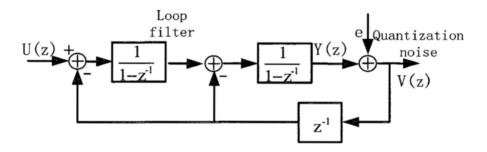

Fig 2.5 shows a first-order  $\Delta$ - $\Sigma$  modulator architecture when the H(z) in Fig 2.3 is replaced with  $\frac{1}{1-z^{-1}}$  and the DAC with  $z^{-1}$ . If the quantizer in Fig 2.5 is replaced with another first-order modulator, a second-order  $\Delta$ - $\Sigma$  modulator is formed, shown in Fig 2.6.

The system transfer function of first-order and second-order  $\Delta$ - $\Sigma$  modulators can be derived from Fig 2.5 and Fig 2.6 in z-domain as,

$$V(z)=U(z)+(1-z^{-1})E(z)$$

(2-4)

for the first-order one, and

$$V(z)=U(z)+(1-z^{-1})^2E(z)$$

(2-5)

for the second-order one.

The signal transfer functions for both modulators are the same, STF(z) = 1. In other words, both modulators do not alter their inputs. The noise transfer functions of the first-order and second-order modulators are  $(1-z^{-1})$  and  $(1-z^{-1})^2$ , respectively. The NTF of the second-order modulator is the square of the first-order's NTF, so we expect increased attenuation of quantization noise at low frequencies for the second-order one.

Fig 2.5 First-order delta-sigma modulator

Fig 2.6 Second-order delta-sigma modulator

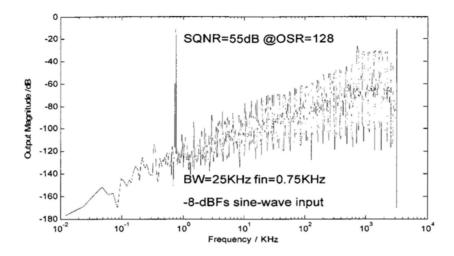

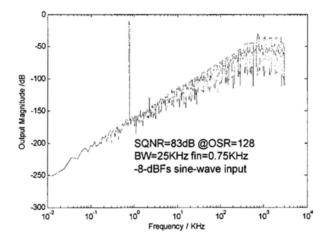

Quantization noise shown Fig 2.4 is shaped by the modulator's NTF. Output spectrums of two modulators are shown in Fig 2.7 and Fig 2.8, respectively. From the simulated output spectrum, NTF noise shaping of first-order and second-order modulator are 20 dB/decade and 40 dB/decade, respectively.

Fig 2.7 Output spectrum of first-order delta-sigma modulator with -8dBFs sine-wave input

Fig 2.8 Output spectrum of second-order delta-sigma modulator with -8dBFs sine-wave input

For an  $L^{th}$  order modulator with a noise transfer function of  $(1-z^{-1})^L$ , the total in-band quantization noise power can be approximately calculated as [27],

$$q_{rms}^2 = \int_{f_B}^{f_B} P_e(f) |NTF|^2 df$$

$$= \int_{f_B}^{f_B} \frac{\Delta^2}{12} \frac{1}{f_s} |NTF|^2 df$$

$$\approx \frac{\pi^2 L}{(2L+1)(OSR)^{2L+1}} \frac{\Delta^2}{12}$$

(2-6)

where  $P_e(f)$  is the quantization noise power spectral density; OSR is the oversampling ratio, defined as the ratio of the sampling frequency to the Nyquist frequency;  $\Delta$  is the quantizer step size; L is the modulator loop order and  $f_B$  is the signal bandwidth.

The dynamic range (DR) is:

$$DR = 10 \log \frac{P_s^2}{q_{rms}^2} = 10 \log \frac{\frac{1}{2} \frac{\Delta^2}{2}}{\frac{\pi^2 L}{(2L+1)(OSR)^{2L+1}} \frac{\Delta^2}{12}}$$

$$=10\log[\frac{3(2L+1)}{2\pi^2L}(OSR)^{2L+1}]$$

(2-7)

where  $P_s^2$  is the signal power and  $P_s^2 = \frac{1}{2} \frac{\Delta^2}{2}$  when considering single bit quantizer.

The ENOB (effective number of bits) of the converter can be derived from the dynamic range:

$$ENOB = \frac{DR - 1.76}{6.02} \tag{2-8}$$

#### 2.4. Topologies of delta-sigma modulators

Depending on the number of quantizers used in the modulator, there two major types of topologies for delta-sigma modulators, single-stage modulator and multi-stage modulator. From (2-7), one way of increasing the DR and the SNR is to raise the order of the modulator. However, for low OSR modulators, it is no longer

possible to obtain high SNR values in a single quantizer modulator since the permissible input signal amplitude is limited due to stability considerations in high-order loops. The limited input range counteracts the improved noise suppression benefited from higher order loop. Another way to improve the SNR is to use multibit quantizer for the modulator, but this requires a flash ADC and also means to insure the in-band linearity of the internal DAC. Also, the complexity of the quantizer grows exponentially with the number of bits used in the quantizer.

The other way to improve the SNR is to use a multi-stage (also called cascade) topology instead of single stage for the modulator. Multi-stage relies on the quantization noise cancellation rather than filtering to improve the SNR performance.

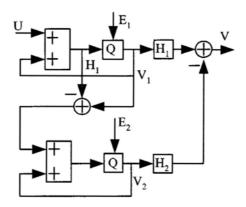

Fig 2.9 Two-stage cascade topology modulator

Fig 2.9 shows a two-stage cascade structure modulator. The output of the first-stage is easily derived from the Fig 2.9

$$V_1(z) = STF_1(z)U(z) + NTF_1(z)E_1(z)$$

(2-9)

where  $STF_1(z)$  and  $NTF_1(z)$  are the signal and noise transfer functions, respectively. The output of signal of the second stage in z-domain is given by

$$V_2(z) = STF_2(z)U(z) + NTF_2(z)E_2(z)$$

(2-10)

where  $STF_2(z)$  and  $NTF_2(z)$  are the signal and noise transfer functions, respectively, of the second stage. The overall output V(z) of the system is

$$V(z) = H_1 V_1 - H_2 V_2 \tag{2-11}$$

with mathematical derivation, if

$$H_1NTF_1 - H_2STF_2 = 0 (2-12)$$

The first-stage error  $E_1(z)$  is cancelled in the overall output V(z) of the system according to (2-12). Considering (2-12),

$$V(z) = H_1 V_1 - H_2 V_2$$

$$= STF_1 \bullet STF_2 \bullet U - NTF_1 \bullet NTF_2 \bullet E_2$$

(2-13)

In typical cases, both stages contain a second-order loop, and their transfer function is

$$STF_1 = STF_2 = z^{-2}$$

(2-14)

And

$$NTF_1 = NTF_2 = (1 - z^{-1})^2$$

(2-15)

The output will become

$$V(z) = z^{-4}U_1 - (1 - z^{-1})^4 E_2$$

(2-16)

From (2-16), the NTF of the overall system is that of a fourth-order single-loop modulator, but the stability is that of a second-order one. Cascade structure increases the signal amplitude while maintain the low order modulator stability so as to achieve high SNR performance. However, the performance of the cascade topology is

contaminated due to the matching problem between mixed-signal (analog and digital) transfer functions  $H_1 \bullet NTF_1$  and  $H_2 \bullet STF_2$ . In reality,  $H_1$  and  $H_2$  are normally implemented in digital circuits and  $NTF_1$  and  $NTF_2$  are realized by analog or mixed-signal circuits. The digital logic can be made very accurately while the analog blocks are always relatively coarse especially in submicron digital process. Consequently, since  $H_1 \bullet NTF_1$  and  $H_2 \bullet STF_2$  are not identical, the first-stage quantization noise  $E_1(z)$  will not be cancelled totally. Some portion of  $E_1(z)$  will leak to the final modulator output V(z) and may eventually limit the performance. Based on this consideration, second-order loops are normally used as the first stage of multistage topology to reduce the amplitude of the leaked quantization noise. Multi-bit quantizers can also be used to further reduce this leaked error, at the cost of adding DAC mismatch errors. Which topology used depends on the specific applications.

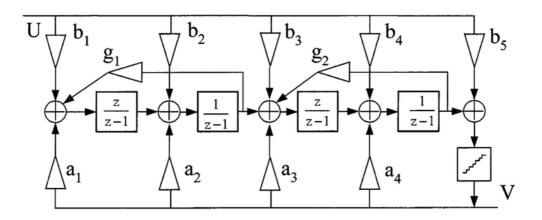

Fig 2.10 Single stage modulator with distributed input and distributed feedback topology

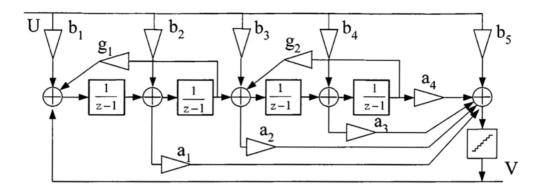

Fig 2.11 Single stage modulator with distributed input and distributed feedforward topology

For single stage modulator topologies, there is only one quantizer. The digital output of the quantizer is the input to the DAC. The output of the DAC is subtracted from the analog input signal and (or) the intermediate integrator outputs.

There are two general single-stage topologies [27]. Cascade of resonators with distributed feedback and distributed input, shown in Fig 2.10; and chain of integrators with feedforward summation and local resonator feedbacks, shown in Fig 2.11.

Both in Fig 2.10 and Fig 2.11, there are two local resonators. The effect of the these resonators is to shift the zeros of the NTF(z), or the poles of the loop filter, to some in-band frequencies other than DC. The overall effect of the zero shift of NTF is to further reduce the in-band quantization noise power and increase the SNR consequently. The optimized zero location of NTF improves the SNR around 3.5dB for second-order modulator and even more for higher order one. This optimum zero-placement technique is very useful especially for wideband high resolution delta-sigma modulators where the oversampling ratios are relatively low.

One shortcoming of these two topologies is that all integrator outputs will contain both input signal as well as filtered quantization noise. This will make the signal swing at each integrator's output large. In many implementation, the distributed input is not used, only the first integrator accepts the input signal; that is  $b_i = 0$ , for i > 1. In this case, since the loop filter does not process the input signal u(n), the requirements

on its linearity will be greatly reduced, and the integrator outputs are considerably reduced, especially if a multi-bit quantizer is used.

It is well known that only first-order modulator is unconditionally stable when single-bit quantizer is used for the single-stage topology. For high order single-stage modulators, the stability can be achieved by methods such as limiting the input signal in stable input range, adding "sensing-and-resetting" circuitry to detect the loop instability and reset the integrators to pull the modulators back to stable status [27].

#### 2.5. Quadrature signal processing

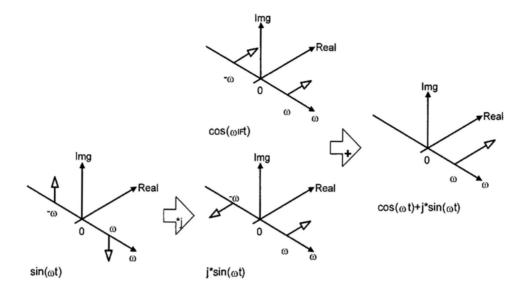

Since this research is to implement a complex CT delta-sigma modulator, a brief review of quadrature, or complex, signal processing is given below.

A quadrature signal is an abstract signal composed of two real signals, I and Q, viewed as a single complex entity u = I + jQ. In the context of communications, the real part and imaginary part will be expressed as in-phase (I) and quadrature phase (Q). Often, a trigonometric form is always used to describe a quadrature signal. Fig 2.12 illustrates how a trigonometric form represents a real signal Error! Reference source not found.

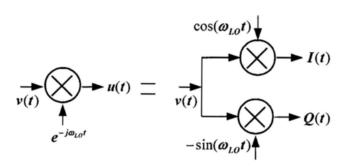

Quadrature analog signals are often created via quadrature mixing. In a quadrature down-conversion mixer, a real signals is multiplied by the quadrature signal  $e^{-j\omega_{LO}t}$ , which we will refer to as the LO (local oscillator), as illustrated in Fig 2.13.

Fig 2.12 Trigonometric format of a real signal

Fig 2.13 Quadrature mixing

Considering that the analog signal input to such a mixer is the real signal  $v(t) = A\cos((\omega_{LO} + \omega)t)$ , then the output of the mixer is

$$v(t) = A\cos((\omega_{LO} + \omega)t) \times e^{-j\omega_{LO}t}$$

$$= A\frac{e^{j(\omega_{LO} + \omega)t} + e^{-j(\omega_{LO} + \omega)t}}{2} \times e^{-j\omega_{LO}t}$$

$$= \frac{A}{2}e^{j\omega t} + \frac{A}{2}e^{-j(2\omega_{L0} + \omega)t}$$

(2-17)

In above expression, the second term will be removed by a low pass filter. A frequency-shifted version of the original signal, will result and center at the angular frequency,  $\omega$ .

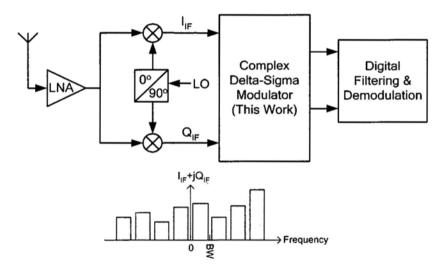

A block diagram of a delta-sigma converter with a built-in quadrature mixer is shown in Fig 2.14. In the upper path the signal is mixed with a cosine function, giving an in-phase output signal. The upper path is referred as I channel. On the other hand, the signal in the lower path is mixed with a sine function, so it results in quadrature-phase and the lower path is referred as Q channel. The two low-pass filters following the mixer are used to remove the high frequency components generating from the mixer and result quadrature signal as

$$v(t) = I_{u} + jQ_{u}$$

Fig 2.14 Diagram of a complex delta-sigma converter including the quadrature mixer

A complex delta-sigma modulator is used to converter the quadrature signal to digital bit. Fig 2.15 shows the spectrum of signals along I and Q channel and by complex adding of their output (I-j\*Q), image are removed and only desired signal remained Error! Reference source not found..

Fig 2.15 Spectrum of signals along the I and Q channels

In summary, this chapter reviews the fundamental of delta-sigma modulators and the basics of quadrature signal processing.

## Chapter 3 System design of complex CT delta-sigma modulator

The focus of this research is on low-voltage delta-sigma modulators. It is mentioned in Chapter one that the CT modulator, which avoids the switching challenge commonly existing in low-voltage DT modulator, is selected. Besides, the single-stage architecture is selected as the SNR performance of the multi-stage modulator is affected by the mismatch between the analog and digital circuits as mentioned in Chapter two. This performance decreasing due to the mismatch is more serious for CT modulator than the DT modulator because the matching in DT multistage modulator normally depends on capacitor matching which can be better than 0.1% in current mainstream digital CMOS process. However, the matching in CT modulator is limited by the very coarse time constant that depends on resistor and capacitor variations, and these variations of resistor and capacitor values are up to 13% [29] or even more depending on the process options. Most CT modulators reported in the open literature are of single stage type instead of multistage type, with only a few exceptions [30] [38]. Nonetheless, this is not to say that CT multi-stage architecture is not possible for low-voltage designs. It is still a good alternative research direction and the aforementioned challenges could be solved by circuit-level and/or system-level innovations.

As we have selected the CT single-stage architecture for the desired complex modulator for use in wireless receivers, we present the system-level synthesis of such type of modulator in this chapter.

#### 3.1. Mapping of CT modulators from DT prototypes

The DT  $\Delta$ - $\Sigma$  modulator has evolved for several decades since its prelude. Many verified loop filters for DT modulators are available in the literature. The loop filter function of a DT modulator can be found in a straightforward way by using

commercial filter design packages, or with the help of a widely used delta-sigma design toolbox [27]. For the CT delta-sigma modulator, the simplest way to get its loop filter is to pick a DT loop filter H(z) meeting the given resolution requirement and then transform it into the equivalent CT loop filter H(s).

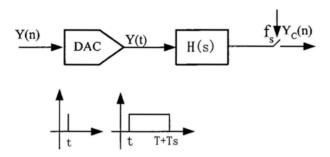

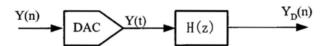

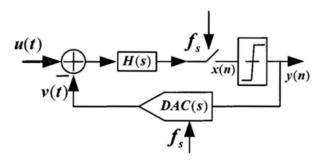

Fig 3.1 Block diagram of DT delta-sigma modulator

Fig 3.2 Block diagram of CT delta-sigma modulator

Block diagrams of a DT modulator and a CT modulator are shown in Fig 3.1 and Fig 3.2, respectively. Suppose that the same input is applied to the two modulators. If both the CT and DT modulator produce the same sequence of bits in the time domain, then we can say these two modulators are equivalent. Assume that each quantizer makes the same decision about what output bit to produce when fed with the same input. It is guaranteed that the two modulators will produce the same output bit sequences if the inputs to their quantizer are the same at the sampling instants.

To find the equivalences between the DT and CT loop filters, we break the modulator loop at the input of quantizer with zeroed modulator input as shown in Fig 3.3 and Fig 3.4 [31]. The DAC operation of CT modulator is also shown in Fig 3.3,

which is thought of as a discrete-to-continuous converter, taking sample v(n), and producing full-period rectangular pulse. The output pulse of DAC in Fig 3.3 is filtered by the H(s) and then sampled, where it becomes the discrete-time output of the open-loop system  $Y_C(t)$ ,  $t = nT_S$ .

Fig 3.3 Block diagram of open loop of CT modulator

Fig 3.4 Block diagram of open loop of DT modulator

This same-input condition at the sampling instants can be described as,

$$Y_D(n) = Y_C(t)\big|_{t=nTs} \tag{3-1}$$

This can be satisfied if the open loop impulse responses are the same at sampling instants, which can be written as [32]

$$Z^{-1}\{H(z)\} = L^{-1}\{H_{DAC}(s)H(s)\}\Big|_{t=nTs}$$

(3-2)

or in the time domain [33]

$$h(n) = \widehat{r(t)} * h_C(t)]|_{t=0.75}$$

(3-3)

where  $\widehat{r(t)}$  is the impulse response of the DAC in CT modulator, and h(n) and  $H_C(t)$  is the impulse response of DT loop filter H(z) and CT loop filter H(s), respectively. This transformation between the DT and CT domains is referred to as the Impulse Invariant Transformation (IIT), as implied by its name [34].

Now if we have a DT modulator with a filter H(z) satisfying the given resolution requirements, we can build a CT modulator with identical noise-shaping behavior by first choosing a DAC pulse shape  $\widehat{r(t)}$ , and then using (3-2) and (3-3) to find H(s).

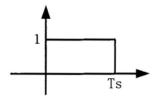

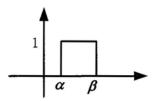

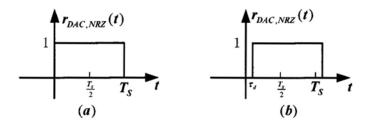

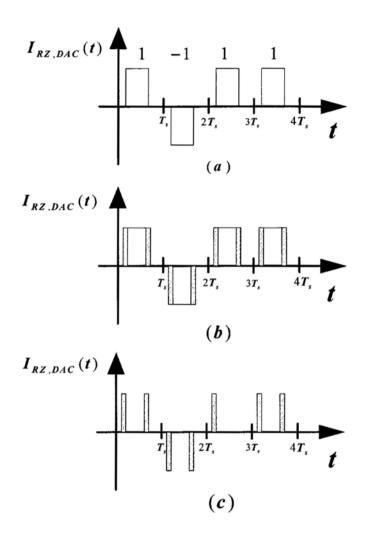

From (3-2) and (3-3), the transformation results depend on the DAC feedback shapes. So we should first define the DAC shapes before performing the mapping from DT to CT. Rectangular-pulsed feedback DAC implementations are predominately incorporated in the CT delta-sigma modulator for several years due to their intrinsic characteristic that their waveforms can be generated simply by switching the feedback current or voltage sources on or off with system clock or its derivative clock. Other possible DAC shapes include linear-decaying DAC and quadratic-decaying DAC [35]. A straight forward way for the mapping is to get their Laplace transform for (3-2). Considering the complexity of their corresponding Laplace transform and the clock generation to control DAC feedback shapes, the rectangular-shaped feedback DAC waveform is most used. Rectangular feedback DAC pulses can be grouped into non-return-to-zero (NRZ) type and return-to-zero (RZ) type, the latter including the special case of half-delay-return-to-zero (HRZ) [36]. The RZ feedback DAC shape produces constant valid output in a certain fraction of a clock period, i.e., from  $\alpha$  ( $0 \le \alpha < Ts$ ) to  $\beta$  ( $\alpha < \beta < Ts$ ). Fig 3.5 and Fig 3.6 show the impulse responses of NRZ and RZ and their corresponding Laplace transform, respectively.

$$\widehat{\mathbf{r}_{NRZ}(t)} = \begin{cases} 1, 0 \le t \le Ts \\ 0, otherwise \end{cases}$$

(3-4)

$$\widehat{R_{NRZ}(s)} = \frac{1 - e^{-sTs}}{s} \tag{3-5}$$

Fig 3.5 NRZ DAC impulse response and corresponding laplace transform

$$\widehat{r_{RZ}(t)} = \begin{cases} 1, \alpha \le t \le \beta, 0 \le \alpha \le \beta \le Ts \\ 0, otherwise \end{cases}$$

(3-6)

$$\widehat{R_{RZ}(s)} = \frac{e^{-\alpha s} - e^{-\beta s}}{s}$$

(3-7)

Fig 3.6 RZ DAC impulse response and corresponding laplace transform

Once the DAC feedback pulse shaped is determined and the DT loop filter H(z) is defined, the mapping from DT to CT can be done with the following two steps.

Firstly, we expand H(z) to a partial fraction expression.

Second, we convert each partial fraction from z-domain to s-domain.

Symbolic mathematical software like Maple [37] can be used to solve (3-2). Table 3-1 summarizes the CT equivalents transformed from DT loop filter from the first to fourth-order when rectangular-shape feedback DACs are used [38].

Table 3-1 CT equivalents for DT loop filter poles

| Table 3-1 CT equivalents for DT loop filter poles |                                                                                                                                                                                                                                                                                           |  |  |

|---------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| z-domain pole                                     | CT equivalent with $f_s = 1$                                                                                                                                                                                                                                                              |  |  |

| $\frac{1}{z-1}$                                   | $\frac{\mathbf{r}_0}{\mathbf{s}}, \mathbf{r}_0 = \frac{f_s}{\beta - \alpha}$                                                                                                                                                                                                              |  |  |

| $\frac{1}{(z-1)^2}$                               | $\frac{\mathbf{r}_1 \mathbf{s} + \mathbf{r}_0}{\mathbf{s}^2}, \ \mathbf{r}_0 = \frac{\mathbf{f}_s^2}{\boldsymbol{\beta} - \boldsymbol{\alpha}}, \ \mathbf{r}_1 = \frac{1}{2} \frac{\mathbf{f}_s(\boldsymbol{\alpha} + \boldsymbol{\beta} - 2)}{\boldsymbol{\beta} - \boldsymbol{\alpha}}$ |  |  |

| $\frac{1}{(z-1)^3}$                               | $\frac{r_2 s^2 + r_1 s + r_0}{s^3},  r_0 = \frac{f_s^3}{\beta - \alpha},  r_1 = \frac{1}{2} \frac{f_s^2 (\alpha + \beta - 3)}{\beta - \alpha}$                                                                                                                                            |  |  |

|                                                   | $r_2 = \frac{1}{12} \frac{f_s(\beta(\beta-9) + \alpha(\alpha-9) + 4\alpha\beta + 12)}{\beta - \alpha}$                                                                                                                                                                                    |  |  |

| $\frac{1}{(z-1)^4}$                               | $\frac{r_3 s^3 + r_2 s^2 + r_1 s + r_0}{s^4},  r_0 = \frac{f_s^4}{\beta - \alpha},  r_1 = \frac{1}{2} \frac{f_s^3 (\alpha + \beta - 4)}{\beta - \alpha}$                                                                                                                                  |  |  |

|                                                   | $r_2 = \frac{1}{12} \frac{f_s^2((\boldsymbol{\beta} - \boldsymbol{\alpha})^2 + 2\alpha\boldsymbol{\beta} - 12(\boldsymbol{\beta} + \boldsymbol{\alpha}) + 22))}{\boldsymbol{\beta} - \boldsymbol{\alpha}}$                                                                                |  |  |

|                                                   | $r_3 = \frac{1}{12} \frac{f_s((\boldsymbol{\beta}^2(\boldsymbol{\alpha}-2) + \boldsymbol{\alpha}^2(\boldsymbol{\beta}-2) - 8\boldsymbol{\alpha}\boldsymbol{\beta} + 11(\boldsymbol{\alpha}+\boldsymbol{\beta}) - 12)}{\boldsymbol{\beta} - \boldsymbol{\alpha}}$                          |  |  |

# 3.2. Synthesis for complex CT modulators

The target of this research is to design a low-voltage complex delta-sigma modulator for analog-to-digital conversion in wireless receivers, as shown in Fig 1.2. As shown in Fig 2.14, the signal fed to the modulator is complex, occupying a single-sided band from DC to BW. In this design, the target application is GFSK receivers, and the input signal band is from DC to +1MHz.

The major problem of rectangular-pulsed feedback realization comes from the purity of the sampling clock. The timing jitter in the sampling clock directly influences the comparator decision point and the rise/fall edges of the DAC output. This shift of rise/falle edges will change the quantity of the DAC feedback signals and result in DAC error. Due to the resulting DAC error introducing directly into the modulator input, the timing jitter limits the overall delta-sigma modulator performance. Even though the other feedback pulse shapes [35] are helpful to reduce the DAC error, the circuits as well as the clock scheme controlling the generation of these kinds of DAC feedback signals are complex and difficult to implement at low supply voltage.

Considering the 0.5V target supply voltage of this work, we adopt the rectangular feedback shape DAC for its simplicity. Though multi-bit modulator has relaxed requirements on the clock jitter, it is very challenging to linearize a multi-bit DAC at 0.5V. Furthermore, a 1-bit modulator is perfectly linear.

# 3.2.1. The DT complex loop filter prototype H(z)

As discussed before, the simplest way of designing H(s) is to map from the loop filter H(z) if the feedback shape DAC is determined.

Now the synthesis of H(s) begins with the selection of a desired DT NTF meeting the requirement. Considering that the achievable unity-gain-bandwidth (UGF) of the 0.5V amplifier, which will be discussed in Chapter 4, is less than 100MHz, the sampling frequency  $f_s$  of the modulator is chosen as 64MHz. The bandwidth of interest is 1MHz and thus the oversampling ratio (OSR) is 64, an integer power of 2 which easies the design of the subsequent decimation filter. To minimize the total noise power in the signal band, the zeros are spread over the bandwidth instead of in DC. In this H(z) design, three zeros of the NTF are evenly placed across the signal band at DC, 0.5MHz, and 1MHz, and the poles are selected as the same frequency of the zeros, located at DC, 0.5MHz and 1MHz. Three poles are added to the NTF to

make the maximum amplitude of the NTF to be 1.5, typical value for a stable high-order 1-bit modulator. The magnitude of the pole is defined by

$$\left|\frac{z-1}{p-1}\right|^{order} \leq 1.5,$$

in this case, the order of the modulator is 3. When z=-1, the above equation reach maximum, the magnitude of the pole is

$$|p| = \frac{2}{1.5^{1/3}} - 1$$

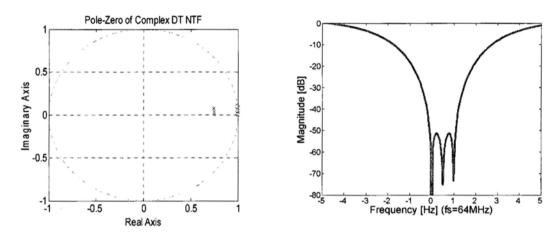

Fig 3.7 shows the pole-zero map and frequency response of the designed NTF.

Fig 3.7 Noise Transfer function H(z) (a) pole-zero map; (b) Frequency response.

With Matlab, based on the defined zeros, the created NTF of the modulator, is shown in below

$$NTF(z) = \frac{z^3 - (2.994 + 0.1471i)z^2 + (2.983 + 0.2938i)z - (0.9892 + 0.1467i)}{z^3 - (2.237 + 0.1099i)z^2 + (1.665 + 0.164i)z - (0.4126 + 0.0612i)}$$

(3-8)

Or in zpk format,

$$NTF(z) = \frac{(z-1)(z-(0.9988+0.0491i))(z-(0.9952+0.0980i))}{(z-0.7472)(z-(0.7463+0.03666i))(z-(0.7436+0.07323i))}$$

(3-9)

With H(z)=1-1/NTF(z), the loop filter H(z) is written in

$$H(z) = \frac{-(0.757 + 0.03719i)z^2 + (1.318 + 0.1298i)z - (0.5766 + 0.08553i)}{z^3 - (2.994 + 0.1471i)z^2 + (2.983 + 0.2938i)z - (0.9892 + 0.1467i)}$$

(3-10)

Or in zpk format

$$H(z) = \frac{(-0.757 - 0.037189i) (z - (0.8763 - 0.0341i))(z - (0.8687 + 0.1199i))}{(z - 1)(z - (0.9988 + 0.0491i))(z - (0.9952 + 0.0980i))}$$

(3-11)

#### 3.2.2. Transformation from H(z) to H(s)

Now the DT loop filter H(z) is defined in (3-11). We need to get the CT H(s) from the designed H(z). For the H(z) described by (3-11), there are two couples of complex zero-poles, and the two poles are out of DC. Table 3-1 describes the transformation from DT to CT from first to fourth order when all poles are located in DC. In this modulator system design, though all poles of the loop filter are out of DC, we can still use the impulse invariant DT to CT transformation described by (3-2) and (3-3) with the defined feedback DAC shape. Applying the transformation described in [31], the CT modulator loop filter H(s) is transformed from (3-10) and the transformed result is shown in (3-12)

$$H(s) = \frac{-(1.351 + 0.03019i)s^2 - (0.3655 - 0.1251i)s - (0.03162 - 0.01726i)}{s^3 - 0.1473is^2 - 0.004819s}$$

(3-12)

Or in zpk format

$$H(s) = \frac{(-1.3509 - 0.030186i) (s + (0.1345 + 0.03755i)) (s + (0.1338 - 0.1362i))}{s (s - 0.04909i)) (s - 0.09817i))}$$

(3-13)

The NTF of CT modulator can be found from

$$NTF(s) = \frac{1}{1 - H(s)} \tag{3-14}$$

In zpk format

$$NTF(s) = \frac{s (s-0.04909i)) (s-0.09817i)}{(s+(1.029-0.01641i)) (s+(0.1614+0.03691i)) (s+(0.1605-0.1376i))}$$

(3-15)

From (3-15), the CT modulator also creates three zeros in the noise transfer function NTF.

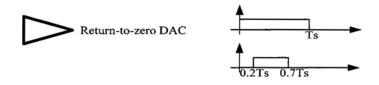

In the above DT to CT transformation, the rectangular feedback DAC pulse shape is adopted, and the RZ type DAC is used for minimizing inter-symbol interference (ISI). The RZ DAC waveform has 50% duty cycle and its rising edge is delayed by 20%Ts (Ts is the clock period) from the starting moment of each clock cycle. According to Fig 3.6,  $\alpha$  and  $\beta$  equal to 0.2 and 0.7, respectively, for the DAC adopted here.

#### 3.2.3. The synthesized complex CT modulator

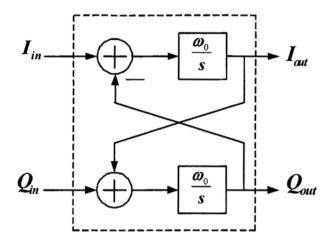

be realized by a quadrature resonator structure shown in Fig 3.8.

Considering the loop filter described in (3-13), the core terms of the loop filter are,  $\frac{1}{s}$ ,  $\frac{1}{(s-j0.04909)}$  and  $\frac{1}{(s-j0.09817)}$ . The first one,  $\frac{1}{s}$ , can be implemented by a regulator integrator. The second and third terms, having complex coefficients, can

The transfer function of the Fig 3.8 is

$$H(s) = \frac{I_{out} + jQ_{out}}{I_{in} + jQ_{in}} = \frac{\omega_0}{s - j\omega_0}$$

(3-16)

In Fig 3.8, real and imaginary parts are cross coupled to implement the imaginary coefficient. The loop filter H(s) given in (3-13) can be implemented by a distributed feedback topology or a feed-forward one. The latter, having smaller signal swing at integrators outputs [39], is not chosen because it requires accurate transconductance cells which are hard to design at 0.5V.

Fig 3.8 Quadrature resonator realizing.

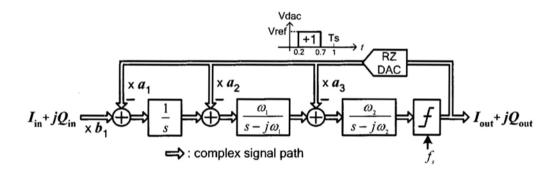

Fig 3.9 Topology of the CT complex modulator with distributed feedback

The signal flow diagram of the synthesized modulator is shown Fig 3.9. The coefficients of the modulators in the Fig 3.9 are

$$\omega_1 = 0.0491, \omega_2 = 0.0982$$

(3-17)

and

$$a_1 = 6.56 + j3.58, a_2 = 7.55 + j12.2, a_3 = 13.76 - j0.307$$

(3-18)

The input coefficient b<sub>1</sub> in Fig 3.9 only scales the signal transfer function and does not affect the NTF. Its value selection is based on criterion of achieving maximum

SNR and maintaining the modulator's stability. From extensive simulation it is chosen to 3 here. It corresponds to the maximum stable input level 0dB. In this single bit modulator design, the maximum stable input level is referred to the feedback DAC reference voltage, which is 0.5V.

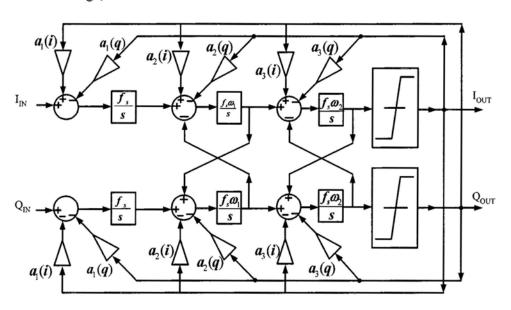

Fig 3.10 The architecture of the complex CT modulator

Fig 3.11 Return-to-Zero DAC and its control clock

# 3.2.4. Simulations of the synthesized modulator

Fig 3.10 shows the architecture of the synthesized CT complex delta-sigma modulator with RZ feedback DAC. The coefficients are given in (3-17) and (3-18).  $a_{x=1,2,3}(i)$  and  $a_{x=1,2,3}(q)$  are the real and imagery part of and (3-18), respectively. The modulator model has been simulated in Matlab Simulink to verify its correctness.

Fig 3.11 shows the control clock for the RZ DAC. Since the sampling frequency  $f_s$  is 64MHz, all variables s in Fig 3.10 must be replaced by  $s/f_s$  in Fig 3.10. The RZ DAC is modeled by the RZ pulse generator following the comparator (not shown in the Fig 3.10).

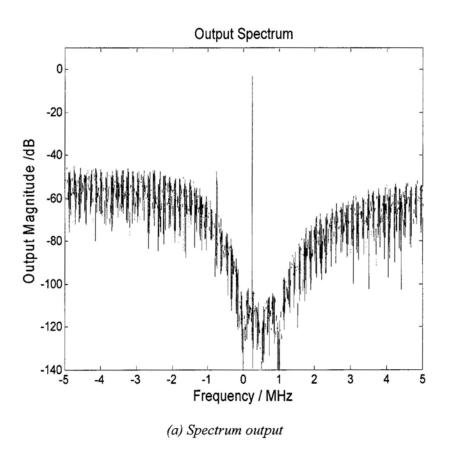

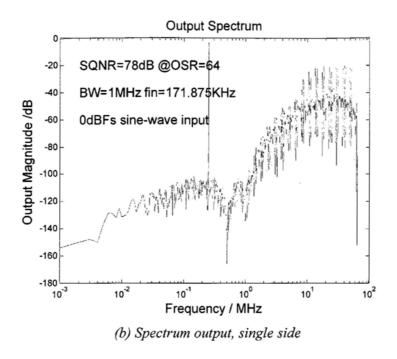

A simulated output spectrum the modulator for a full-scale input is shown in Fig 3.12, where a third-order shape and desired transfer function zeros are clearly observed.

Fig 3.12 Simulated output spectrum of the complex CT modulator.

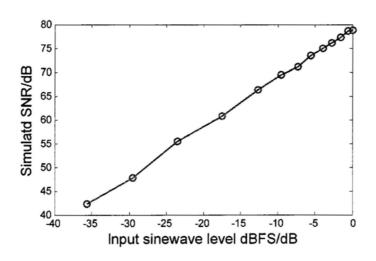

Fig 3.13 Simulated SNR performance versus input level.

Fig 3.13 shows the SNR of the modulator at various input levels. The maximum stable input is found when the highest SNR is achieved. In this case, the simulated maximum SNR of the modulator is 78dB. From the above results, the function of the synthesized modulator is proven correct.

# Chapter 4 Implementation of complex CT delta-sigma modulator

This chapter describes the design and simulation results of the synthesized CT delta-sigma modulator using active RC circuits. The modulator was implemented in a 0.13µm triple-well CMOS process and the regular transistor NMOS/PMOS with threshold voltages of 0.22V/-0.25V was used.

The influence of the components nonidealities is first discussed. The 0.5V circuit blocks are then presented followed by circuit simulation results.

# 4.1. Nonidealities in oversampling delta-sigma modulator

An active-RC implemented modulator mainly consists of op-amps (operational amplifiers), comparators and passive components including resistors and capacitors. The main non-idealities of modulator include: finite gain/bandwidth/slew rate, thermal noise and 1/f noise of opamps, RC time constant variation due to process variation, quantizers' delay/offset/hysteresis/metastability, feedback DAC elements mismatch and their unequal rise/fall time, and clock jitter. All of these nonidealities adversely affect the performance of delta-sigma modulator. However, due to their different mechanisms and different occurring locations inside a modulator, their effects on the performance of the modulator are different. These non-ideal phenomena are discussed before the modulator circuit is presented.

# 4.1.1. Op-amp non-idealities

The loop filter transfer function is the key performance determining factor for a delta-sigma modulator because it defines modulator's noise-transfer function and the quantization noise-shaping behavior. The complete loop filter usually consists of several integrators realized by either RC or gm-C circuits, or even LC-resonators for band-pass modulators. For any architecture modulator, the nonidealities of the

integrator appearing in the first stage are not suppressed by the high loop gain, and thus impact the modulator performance to a large extent. The effects of the opamp's nonidealities on active-RC modulator are discussed next.

### 4.1.1.1 Finite gain and gain bandwidth

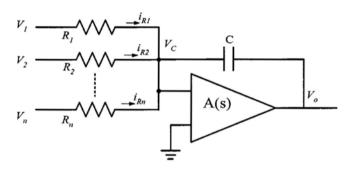

Fig 4.1 shows a typical RC integrator used for CT modulators [40]. The resistor Rn driven by the quantizer, input signal or output of preceding stage, performs a linear V/I conversion. The current charging the integrator capacitor period is a full sampling period for NRZ or half period for RZ.

In ideal case, the transfer function of the RC integrator is

$$\frac{V_o(s)}{V_n(s)} = \frac{-1}{sR_nC} = \frac{f_s \times k_n}{s}$$

(4-1)

where Rn is the value of n-th resistor while C is the value of the integration capacitor,  $k_n$  is the scaling coefficient, which is mapped to RC product and  $f_s$  is the clock frequency. The R and C value of Fig 4.6 is calculated from (4-1) according to the Matlab model shown Fig 3.10.

When considering the amplifier as a one-pole amplifier, we have:

$$A(s) = \frac{A_0}{1 + s/\omega_0} \tag{4-2}$$

The RC integrator transfer function with one-pole amplifier is,

$$\frac{V_o(s)}{V_n(s)} = -\frac{1}{sR_nC} \frac{1}{1 + \frac{1}{A(s)} + \frac{1}{sRC} \frac{1}{A(s)}}$$

(4-3)

With (4-2), the integrator transfer function is rewritten as

$$\frac{V_o(s)}{V_n(s)} = -\frac{1}{s^2 \frac{R_n C}{A_0 \omega_0} + s(\frac{1}{A_0 \omega_0} + R_n C + \frac{R_n C}{A_0}) + \frac{1}{A_0}}$$

(4-4)

When only finite DC gain is considered, (4-4) becomes,

$$\frac{V_o(s)}{V_n(s)} = -\frac{1}{s(R_nC + \frac{R_nC}{A_0}) + \frac{1}{A_0}} \approx -\frac{f_s \times k_n}{s + \frac{1}{A_0R_nC}}$$

(4-5)

Fig 4.1 Typical RC integrator with single pole amplifier used in CT modulators.

Obviously the integrator transfer function has a pole at  $\frac{1}{A_0 R_n C}$ , away from dc.

Following (3-14), the zeros of NTF come from the poles of the loop filter. Thus, all zeros of the NTF are pushed away from dc, which reduces the amount of attenuation of the quantization noise in the base-band. This nonideality is known as leaky integration. The additional in-band noise due to the leaky integrator is not so serious. In case of single-loop architecture, the performance attenuation of SNR is around  $0.2\sim1$  dB with the requirement of the dc gain of the amplifier  $A_0 > OSR$  [41][42]. Usually, this requirement is very easy to satisfy.

Assume  $A_o >> 1$ , formula, (4-5) can be rewritten to [40]:

$$\frac{V_o(s)}{V_n(s)} = -\frac{1}{s^2 \frac{R_n C}{A_0 \omega_0} + s(\frac{1}{A_0 \omega_0} + R_n C)} = -\frac{k_n f_s}{s} \frac{G E_{GBW}}{\frac{s}{\omega_2} + 1}$$

(4-6)

$$GE_{GBW} = \frac{GBW}{GBW + k_n f_s} \tag{4-7}$$

$$\omega_2 = GBW + k_n f_s \tag{4-8}$$

where  $GE_{GBW}$  is the integrator gain error due to finite gain-bandwidth product, and  $\omega_2$  is the additional pole introduced by the limited gain-bandwidth product (GBW).

Equation (4-6) shows that a practical RC integrator can be modeled as an ideal integrator scaled with a gain error and followed by a single-pole roll off. For low values of the GBW, which is the usual case for low-voltage design, the added second integrator pole  $\omega_2$  introduces an extra loop delay in the feedback path, which has the worst influence on the performance degradation of CT modulator.

The effects of the amplifier's finite gain bandwidth on the performance of the modulator can be modeled in simulation. Based on the results in [43] and the simulation results, a GBW of the amplifier around the sampling clock does not give severe degradation on the modulator's SNR performance if the induced extra loop delay is controlled. Even more, the GBW can be chosen lower than the sampling frequency with delay compensation technique in the feedback path [44].

#### 4.1.1.2 Slew rate

Another nonideality of the amplifier incorporated in the integrator is the finite slew rate (SR), which is arisen from the limited current capability of charging the integrating capacitor and the amplifier internal compensation capacitor. In DT implementation, the signal transitions are very fast and the finite slew late results incomplete settling. Unlike the errors due to finite GBW, finite SR is a purely nonlinear effect and signal dependant, which results in distortion as well as an

increase of the noise floor [45]. In single-loop architecture modulator, the distortion is a key performance limiting factor [41].

For DT modulator, the requirement on amplifier's SR is usually high. One way to relax the requirement of SR is by using multi-bit internal quantization to reduce the signal swing feeding into integrator. In CT modulator, the slew rate specifications can be relaxed even for one bit quantization. The reason behind this is the signals in CT modulator are changing much slowly.

Considering a single-bit modulator, from Fig 4.1, the maximum slew rate of integrator can be described as,

$$SR_{\text{max}} = \left| \frac{dV_o}{dt} \right|_{\text{max}} = f_s V_{in} \big|_{\text{max}}$$

(4-9)

$$V_{in}|_{\max} = \sum_{i}^{m} k_{i,fd} V_{fd} + \sum_{l}^{n} k_{l,fb} V_{ref}$$

(4-10)

where  $k_{i,fd}$ ,  $k_{l,fb}$  are the integrator scale coefficient as described in (4-1);  $V_{fd}$  is the forward signal, i.e, the modulator's input signal or the output of preceding integrator; and  $V_{ref}$  is the reference voltage of the modulator.

The first integrator is the most critical one in all kinds of modulator regardless of their architectures because its input referred errors are not suppressed by the loop filter and thus any error caused from limited SR will directly appear in the output spectrum. Errors induced by SR in the integrators after the first one are suppressed by the preceding filters. Taking the first integrator into account, the input signal almost does not change its amplitude during one sampling clock period due to the over-sampling. The feedback signal is assumed to be RZ pulses. During one sampling clock, the feedback signal is changed from  $V_{dd}$  (assume  $V_{ref} = V_{dd}$ ) to zero or vice versa. The slew rate of one-bit modulator in the worst case can be approximated from (4-9), and rewritten as

$$SR\big|_{\text{max intl}} = f_s(k_{in}V_{in} + k_iV_{ref}) \tag{4-11}$$

$k_{in}$  is the input scaling coefficient and  $V_{in}$  is the input signal amplitude, which is around half  $V_{dd}$ . Usually, the value calculated from (4-11) is not hard to satisfy even for amplifier operating at 0.5V.

#### 4.1.2. Time constant variation

For R-C integrator-based CT modulators, the integrator gains are mapped into R-C products. In modern mainstream CMOS processes, the values of resistor and capacitor vary over process, temperature, voltage, etc. For the most of this type of modulators, the resistors are mainly realized by doped poly-silicon. The variation of the absolute resistor component values is up to 13% [29] or even more. Taking the variation of capacitor into account, the possible variation of the RC-product is more than 20%.

Considering the variation of the RC product, (4-1) is rewritten as

$$\frac{V_o(s)}{V_n(s)} = \frac{-1}{sR_nC(1+\delta_{RC})} = \frac{f_s \times k_n}{s} GE_{RC}$$

(4-12)

$$GE_{RC} = \frac{1}{(1 + \delta_{RC})} \tag{4-13}$$

Equation (4-12) shows the integrator transfer function is scaled gain error induced by the variation of RC product.

Obviously, for the last integrator in the modulator, which is in the front of the quantizer, the effect of its gain error induced by RC product variation is negligible because the quantizer makes its decision based on the sign of its input and regardless of whether its inputs is scaled or not.

As for the variation of R-C products, there are two cases, positive variation or negative variations. For the positive one, which yields reduced integrator scaling coefficients  $k_n$  in (4-1), and thus less aggressive noise-shaping behavior is resulted [35]. The less aggressive noise-shaping will increase the in-band noise, but will not affect the stability. A negative shift of the RC product value will increase the scaling coefficients  $k_n$  and thus more aggressive noise shaping, which will slightly increase the performance since more noise will be pushed out of band of interest. But the potential of the instability of the modulator, caused by the more loop gain, is increased [35]. Also the stability of the modulator strongly depends on the input amplitude and the out-of-band gain of the ideal modulator loop filter. In the system design of the modulator, besides meeting the common criterion of  $|NTF| \le 1.5$  for single-bit high order modulators, the modulator need to be extensively simulated with varying RC product and different input amplitude.

### 4.1.3. Comparator nonidealites

Usually, for oversampling modulator, the comparator is the most uncritical building block because it locates at the most insensitive place of the loop. It is preceded with the whole loop filter. The errors induced by the comparator nonidealities, which are usually known as delay, offset, hysteresis, and metastability, are shaped by the high-pass shaping characteristic of NTF. Nonetheless, for high resolution delta-sigma modulator, special attention has still to be paid on the nonidealites of the quantizer.

#### 4.1.3.1. Comparator offset and hysteresis