#### UNIVERSITY OF CALIFORNIA, SAN DIEGO

#### Phase Shifter Approaches for Compact Low-Power Phased Array Transmitters

A dissertation submitted in partial satisfaction of the requirements for the degree

Doctor of Philosophy

in

Electrical Engineering (Electronics Circuits and Systems)

by

Sunghwan Kim

#### Committee in charge:

Professor Lawrence E. Larson, Chair Professor Peter M. Asbeck Professor James F. Buckwalter Professor Brian G. Keating Professor William C. Trogler

2010

UMI Number: 3398530

#### All rights reserved

#### INFORMATION TO ALL USERS

The quality of this reproduction is dependent upon the quality of the copy submitted.

In the unlikely event that the author did not send a complete manuscript and there are missing pages, these will be noted. Also, if material had to be removed, a note will indicate the deletion.

UMI 3398530

Copyright 2010 by ProQuest LLC.

All rights reserved. This edition of the work is protected against unauthorized copying under Title 17, United States Code.

ProQuest LLC 789 East Eisenhower Parkway P.O. Box 1346 Ann Arbor, MI 48106-1346

Copyright

Sunghwan Kim, 2010

All rights reserved.

| The dissertation of Sunghwan Kim is approved, and it is ac-   |

|---------------------------------------------------------------|

| ceptable in quality and form for publication on microfilm and |

| electronically:                                               |

|                                                               |

|                                                               |

|                                                               |

|                                                               |

|                                                               |

|                                                               |

|                                                               |

|                                                               |

|                                                               |

|                                                               |

| Chair                                                         |

University of California, San Diego

2010

#### **DEDICATION**

To my parents, my wife Shohyun and daugher Claire.

#### **EPIGRAPH**

#### TABLE OF CONTENTS

| Signature Pa         | ge                               |

|----------------------|----------------------------------|

| Dedication .         | iv                               |

| Epigraph             |                                  |

| Table of Con         | tents                            |

| List of Figur        | es vii                           |

| List of Table        | s                                |

| Acknowledg           | ements xi                        |

| Vita and Pub         | lications                        |

| Abstract of the      | he Dissertation                  |

| Chapter 1  Chapter 2 | Introduction                     |

| Chapter 3            | 2.4.2 Inductor Design and Layout |

|            | 3.5 Conclusion                                                                                 |

|------------|------------------------------------------------------------------------------------------------|

| Chapter 4  | SiGe HBT SubHarmonic Upconverter for Phased Array Transmitters 4 4.1 Introduction              |

| Chapter 5  | An 8-Element Phased Array Transmitter with an Injection-locked Quadrature Frequency Multiplier |

| Chapter 6  | Conclusion                                                                                     |

| References | 10                                                                                             |

#### LIST OF FIGURES

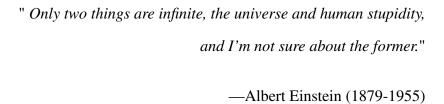

| Figure 1.1:  | An N-element phased array antenna system                                                                                                                                                                           | 3        |

|--------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

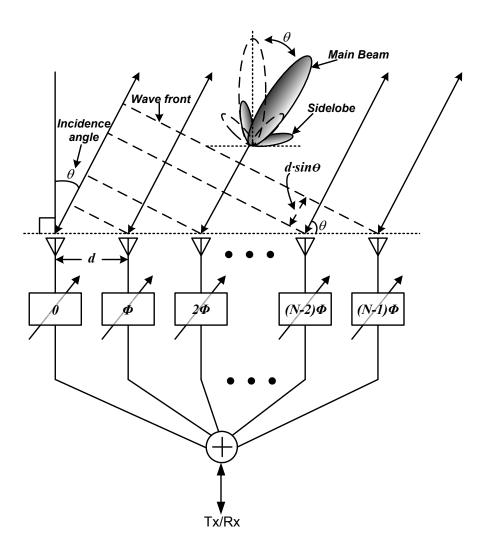

| Figure 1.2:  | The Array Factor of an 8 element linear phased array. The beam angle is from 20° to 160°                                                                                                                           | 5        |

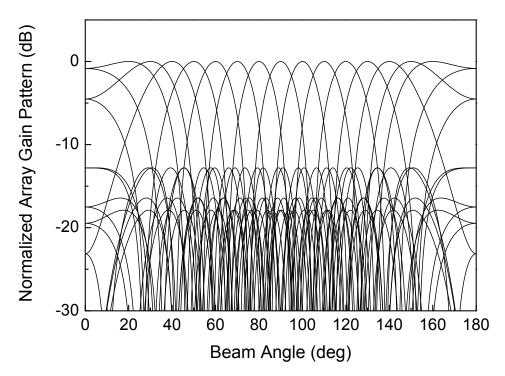

| Figure 1.3:  | (a) RF phase shifting (b) LO phase shifting (c) IF phase shifting (d) baseband phase shifting architectures                                                                                                        | 7        |

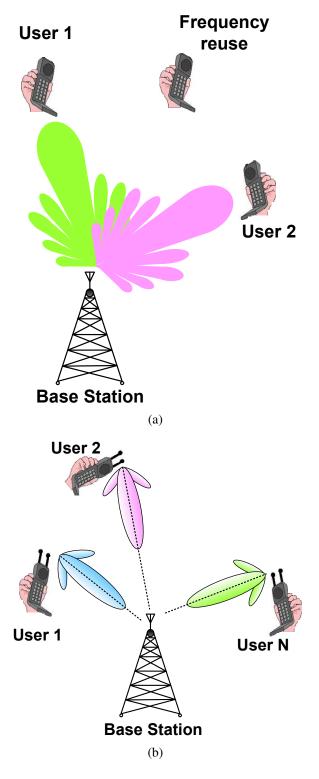

| Figure 1.4:  | (a) Beamforming in cellular wireless communication system. Beam is formed by the base station and (b) handset beamforming in cellular wireless communication system. Dual antennas are adopted in mobile handsets. | 11       |

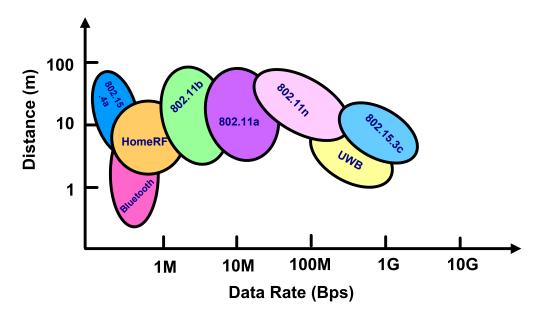

| Figure 1.5:  | Data rates and range requirements for WLAN and WPAN standards and applications. Millimeter wave technology, IEEE 802.15.3c is aiming for very high data rates.                                                     | 13       |

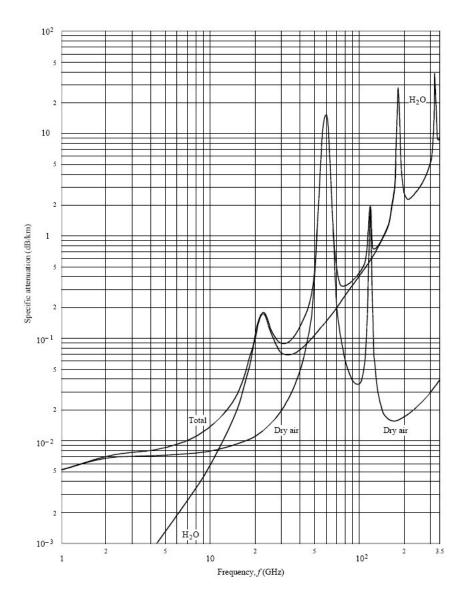

| Figure 1.6:  | Specific attenuation for atmospheric gases as a function of frequency.                                                                                                                                             | 14       |

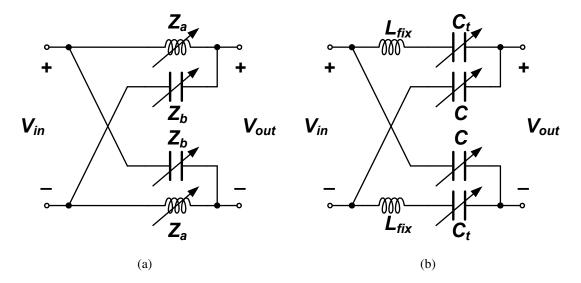

| Figure 2.1:  | (a) Schematic of an all-pass network with LC reactance component and (b) schematic of a proposed all-pass network phase shifter                                                                                    | 19       |

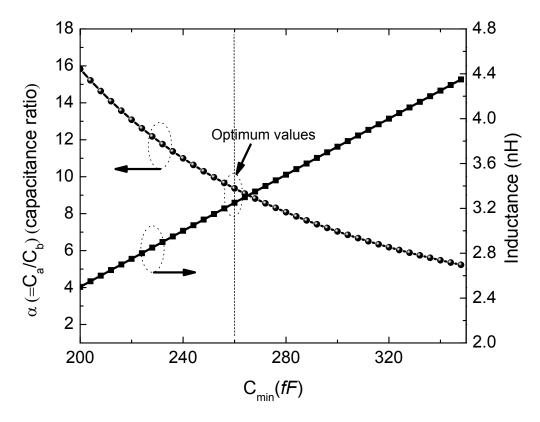

| Figure 2.2:  | Simulated value of $\alpha$ (= $C_t/C$ ) and required inductance as a function of minimum capacitance $C_{min}$ at 2GHz (capacitor tuning ratio $r$ is                                                             | 21       |

| Figure 2.3:  | 4:1)                                                                                                                                                                                                               | 21<br>22 |

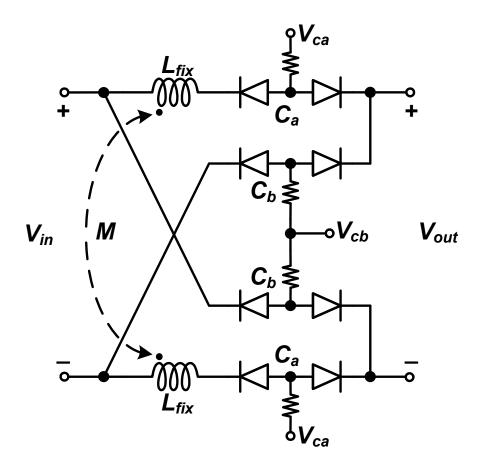

| Figure 2.4:  | Schematic of the phase shifter with distortion-free diode varactors                                                                                                                                                | 22       |

| 1 iguic 2.4. | and magnetically coupled inductors                                                                                                                                                                                 | 23       |

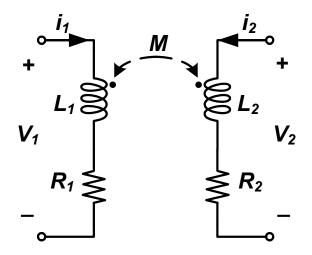

| Figure 2.5:  | Magnetically coupled inductors                                                                                                                                                                                     | 24       |

| Figure 2.6:  | Layout of the magnetically coupled inductors in the phase shifter                                                                                                                                                  | 26       |

| Figure 2.7:  | Four stages phase shifter architecture                                                                                                                                                                             | 27       |

| Figure 2.8:  | Microphotograph of the phase shifter realized in silicon-on-glass                                                                                                                                                  |          |

| _            | technology.                                                                                                                                                                                                        | 27       |

| Figure 2.9:  | (a) Measured phase shift contour lines and (b) measured loss con-                                                                                                                                                  |          |

|              | tour lines as a function of control voltages $V_{ca}$ and $V_{cb}$ at 2GHz                                                                                                                                         | 29       |

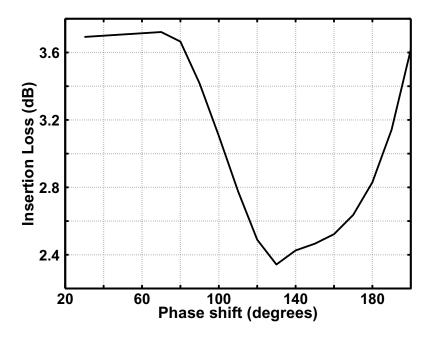

| Figure 2.10: | Minimum loss vs. phase shift at 2GHz                                                                                                                                                                               | 30       |

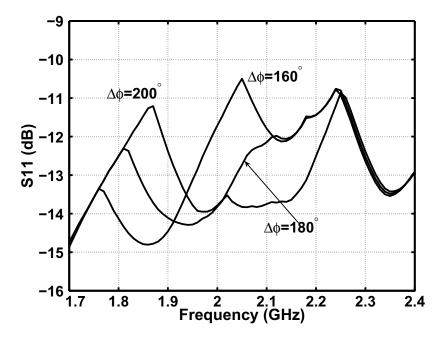

| Figure 2.11: | Measured $ S_{11} $ of the phase shifter at optimum tuning voltage pairs.                                                                                                                                          | 30       |

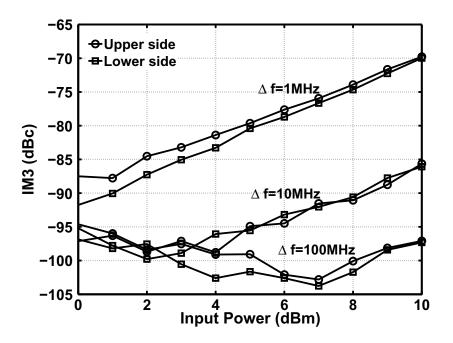

| Figure 2.12: | Measured IM3(dBc) versus frequencies at three different tone-spacings (1MHz, 10MHz and 100MHz)                                                                                                                     | 32       |

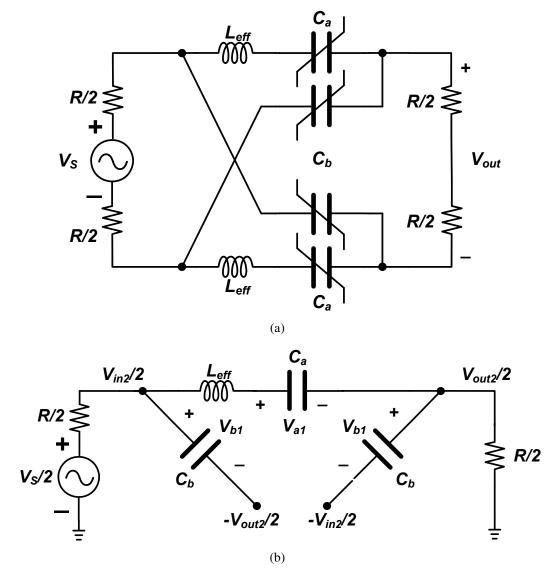

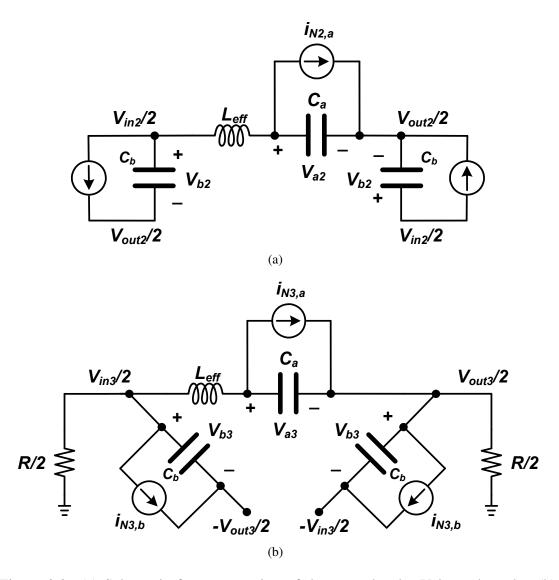

| Figure 3.1:  | (a) A phase shifter with simplified nonlinear capacitors. (b) single-ended equivalent circuit of the phase shifter                                                                                                 | 35       |

| Figure 3.2:  | <ul><li>(a) Schematic for computation of the second-order Volterra kernels.</li><li>(b) schematic for computation of the third-order Volterra kernels.</li></ul>                                                   | 36       |

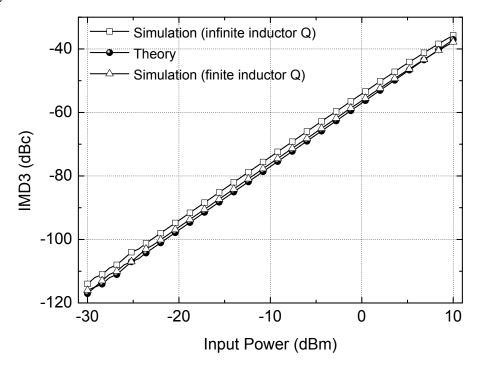

| Figure 3.3:  | Simulated and calculated IMD3 when $\phi = -64^{\circ}$                                                                                                                                                            | 43       |

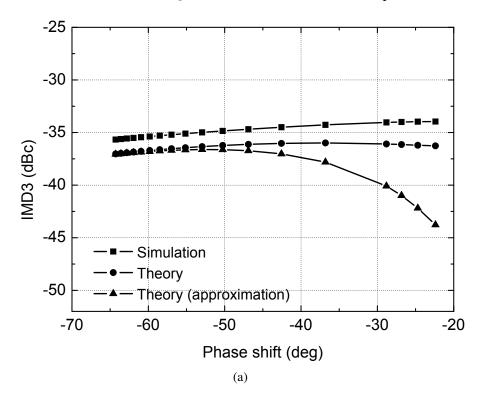

| Figure 3.4:  | (a) Simulated and calculated 3rd order intermodulation distortion and (b) its difference with ideal transformer                                                                                                    | 44       |

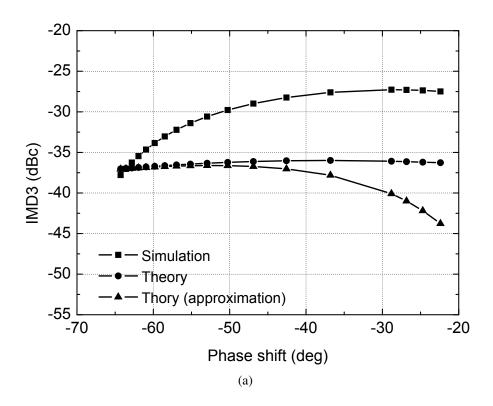

| Figure 3.5:   | (a) Simulated and calculated 3rd order intermodulation distortion and (b) its difference with parasitic extracted transformer | 45         |

|---------------|-------------------------------------------------------------------------------------------------------------------------------|------------|

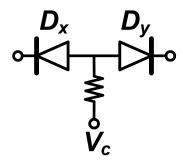

| Figure 3.6:   | Anti-series connection of varactor diodes                                                                                     | 46         |

| Figure 3.7:   | Relative 2nd, 3rd-order distortion and IMD3 on $\eta (= D_x/D_y)$ change                                                      |            |

| C             | $P_{in}=10dBm$ )                                                                                                              | 47         |

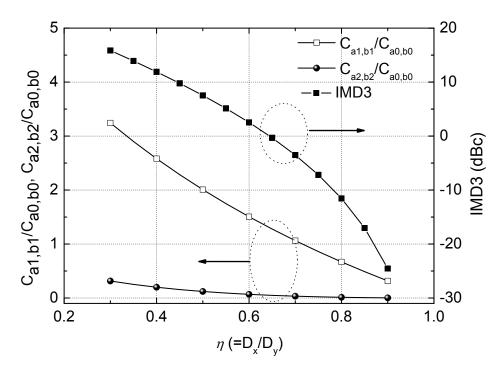

| Figure 4.1:   | Architecture of the phased array transmitter                                                                                  | 51         |

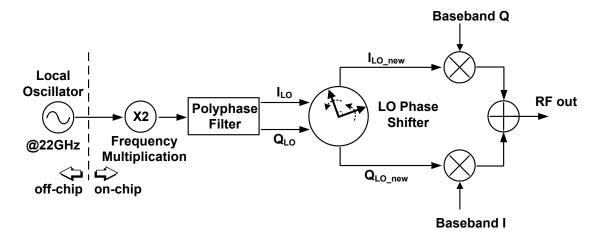

| Figure 4.2:   | Block diagram of the proposed upconverter                                                                                     | 51         |

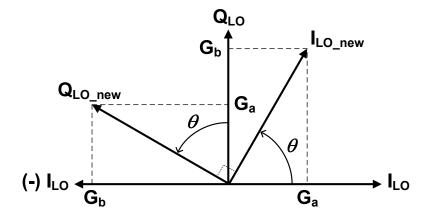

| Figure 4.3:   | A vector with phase $\theta$ can be generated from two quadrature vectors.                                                    | 53         |

| Figure 4.4:   | (a) Block diagram of the vector LO phase shifter and (b) circuit                                                              |            |

| T. 4.5        | implementation of the vector LO phase shifter                                                                                 | 55         |

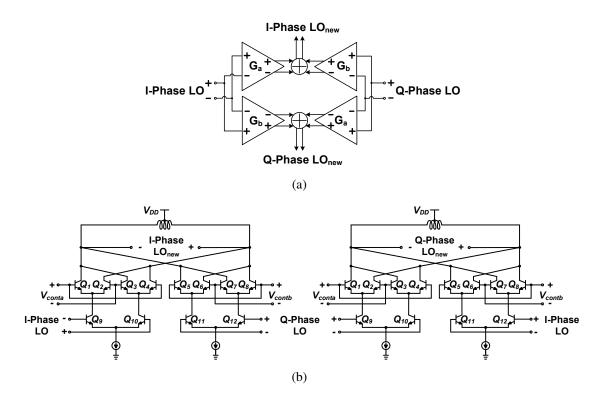

| Figure 4.5:   | Simulated and calculated quadrature phase error at the output of the                                                          |            |

|               | LO phase shifter as a function of the target phase $\theta$ (a) when $\Delta \phi =$                                          | <b>~</b> 0 |

| F' 16         | $2^{\circ}$ , $4^{\circ}$ , $8^{\circ}$ and $10^{\circ}$ and (b) when $\delta_A = 0.03, 0.05$ and $0.1.$                      | 58         |

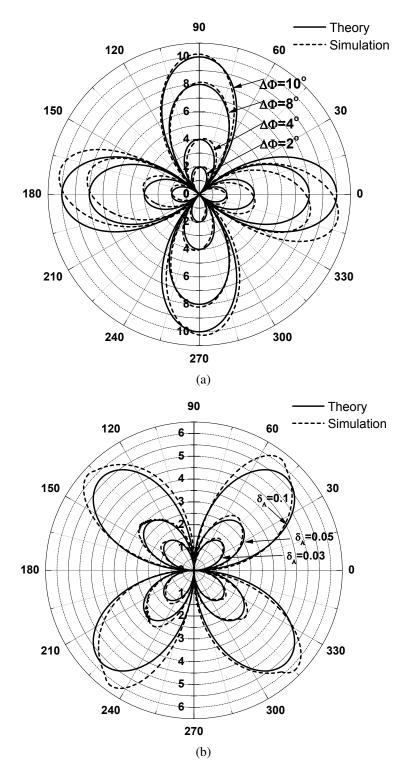

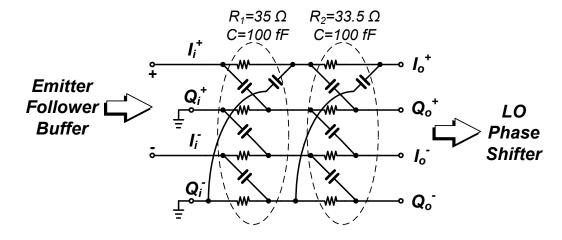

| Figure 4.6:   | Schematic of two stage polyphase filter                                                                                       | 60         |

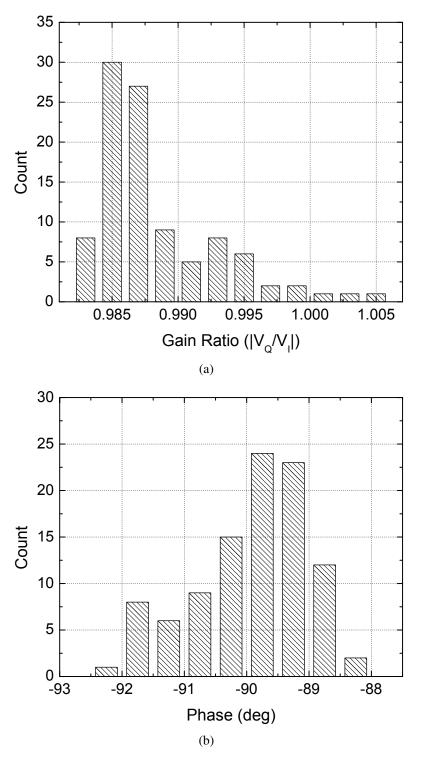

| Figure 4.7:   | Histogram of the relative phase and gain of the polyphase filter at                                                           | 61         |

| Eigung 4 9.   | 44GHz. (a) phase error and (b) gain error                                                                                     | 64         |

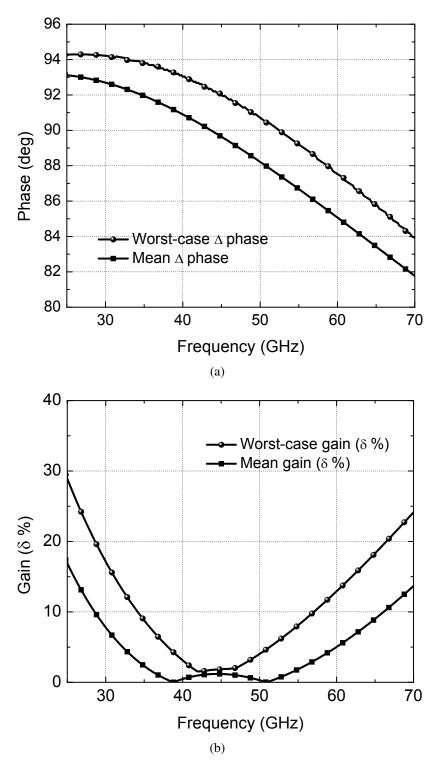

| Figure 4.8:   | Mean and worst-case Monte Carlo simulation results for the polyphase                                                          | 65         |

| Figure 4.9:   | filter. (a) phase error and (b) gain error                                                                                    | 66         |

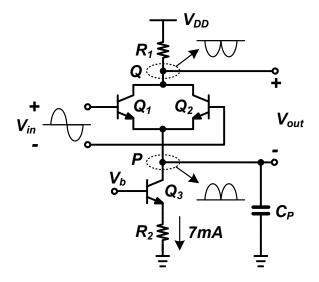

| Figure 4.9.   | Schematic of the frequency doubler                                                                                            | OU         |

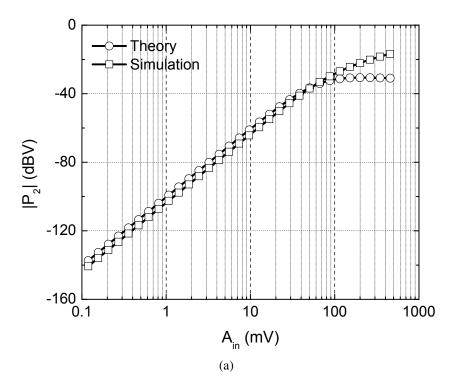

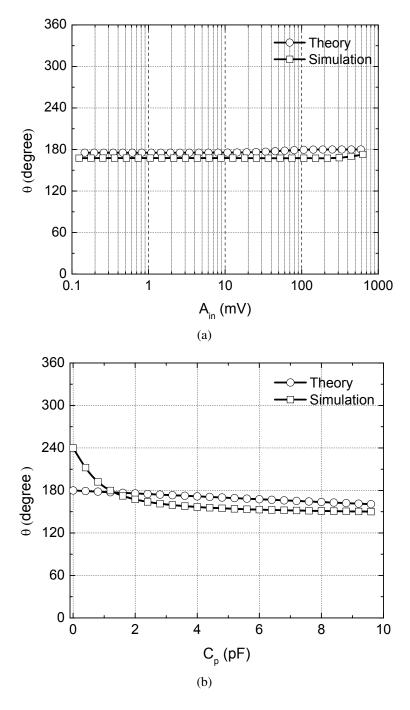

| rigule 4.10.  | Second flatmonic term $T_2$ at node $T$ ( $v_p$ ) as a function of $A_{in}$ with $C_p$ =100fF                                 | 68         |

| Figure 4 11.  | (a) $\theta$ as a function of $A_{in}$ with $C_p$ =2pF and (b) $\theta$ versus $C_p$ with                                     | 00         |

| 1 1guic 4.11. | $A_{in}$ =50mV                                                                                                                | 69         |

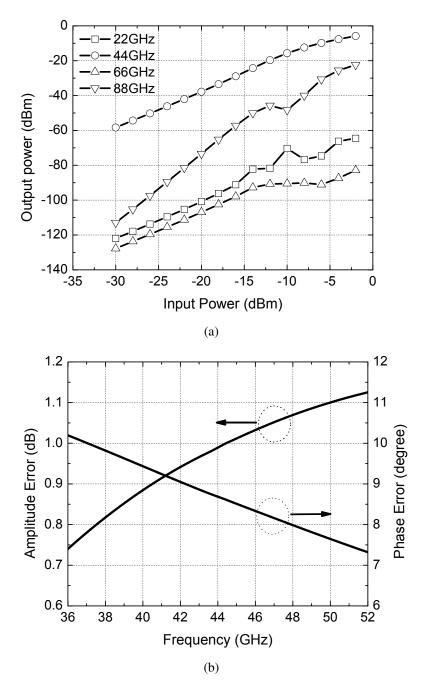

| Figure 4.12:  | (a) Simulated output signal harmonics versus input power in dBm                                                               | 0,         |

| 8             | for the stand-alone frequency doubler test circuit for $f_{in}$ =22GHz and                                                    |            |

|               | (b) simulated amplitude and phase error                                                                                       | 71         |

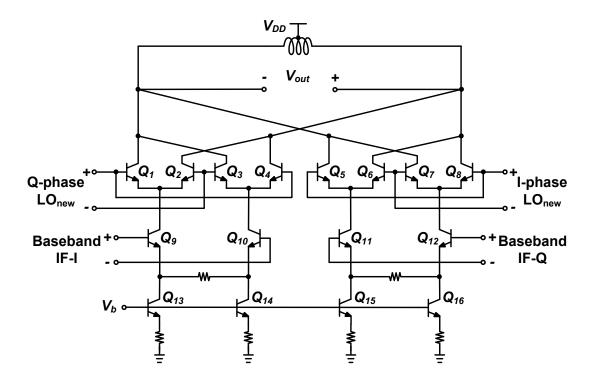

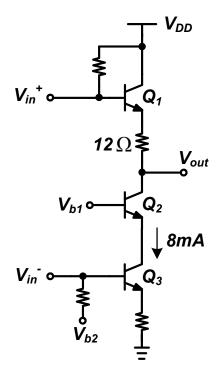

| Figure 4.13:  | I/Q up-conversion mixer schematic diagram                                                                                     | 72         |

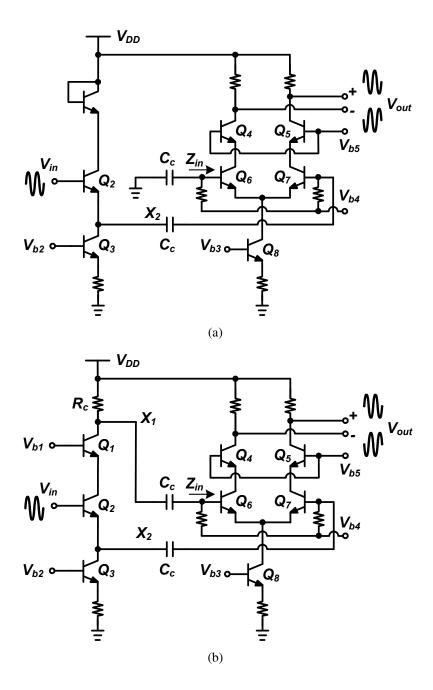

| _             | (a) Typical active balun and (b) modified active balun                                                                        | 73         |

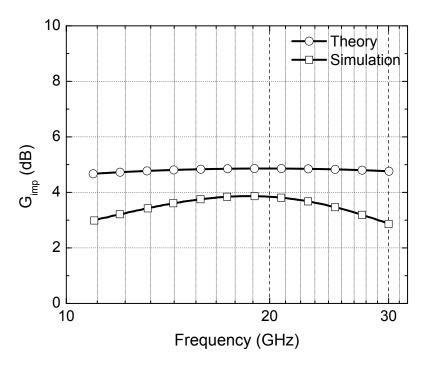

| Figure 4.15:  | Gain improvement of Fig. 4.14(b) compared to Fig. 4.14(a)                                                                     | 75         |

| Figure 4.16:  | Differential-to-single-ended converter at the system output                                                                   | 75         |

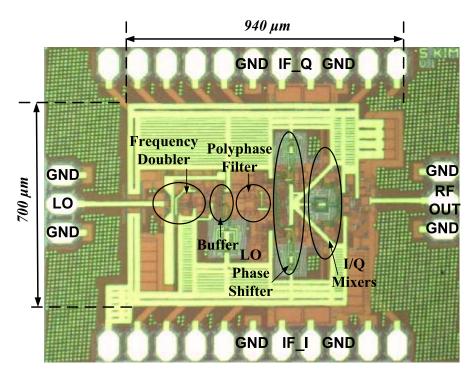

| Figure 4.17:  | Microphotograph of the phase-shifting upconversion mixer                                                                      | 76         |

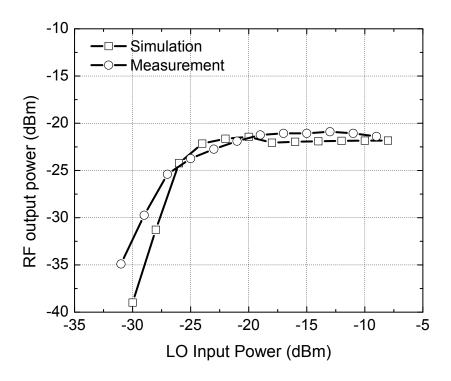

| Figure 4.18:  | Output power(dBm) versus LO power(dBm) at 45GHz, Pif=-38.5dBm,                                                                |            |

|               | $f_{LO}$ =22GHz                                                                                                               | 77         |

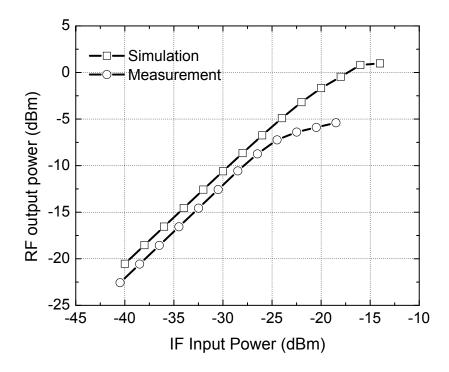

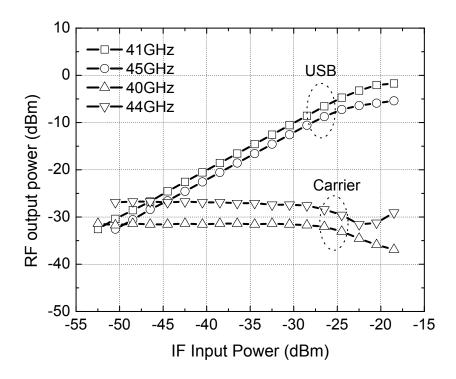

| _             | Output power(dBm) versus input power(dBm) at 45GHz                                                                            | 77         |

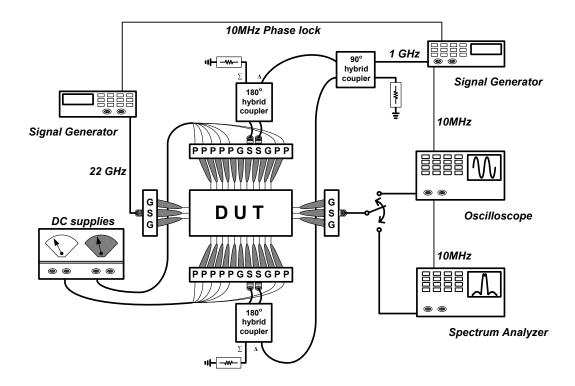

| C             | Measurement setup of the upconverter                                                                                          | 78         |

|               | Probe measurement: probes contacting each pad                                                                                 | 78         |

| Figure 4.22:  | Measured output power(dBm) versus input power(dBm) at LO=22GHz                                                                |            |

| T' 100        | 20GHz                                                                                                                         | 79         |

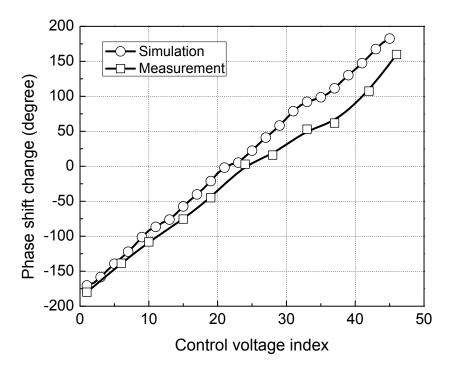

| Figure 4.23:  | Measured and simulated output phase shift at 45GHz as a function                                                              | 70         |

|               | of control voltage                                                                                                            | 79         |

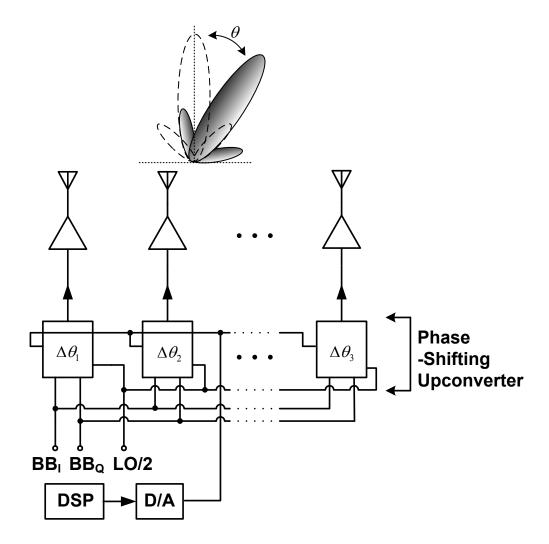

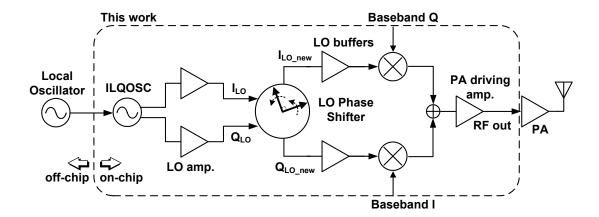

| Figure 5.1:   | Architecture of one proposed transmitter element (of eight)                                                                   | 83         |

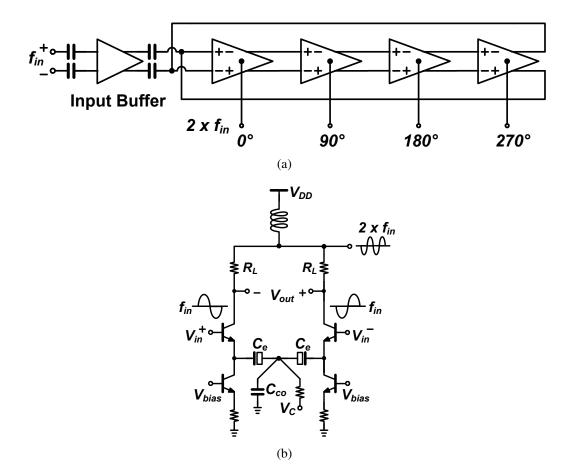

| Figure 5.2:  | (a) Block diagram of the injection-locked quadrature ring oscillator,    |    |

|--------------|--------------------------------------------------------------------------|----|

|              | (b) schematic of a differential gain stage with capacitive degeneration. | 85 |

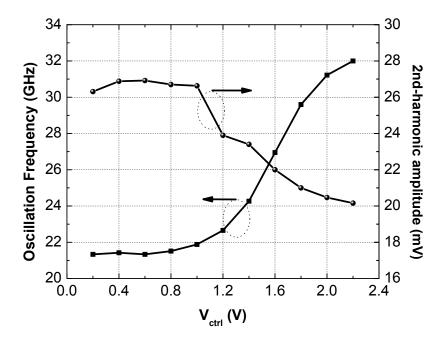

| Figure 5.3:  | Simulated oscillation frequency and second-harmonic output am-           |    |

|              | plitude variation with control voltage                                   | 86 |

| Figure 5.4:  | Schematic of LO boosting amplifier                                       | 87 |

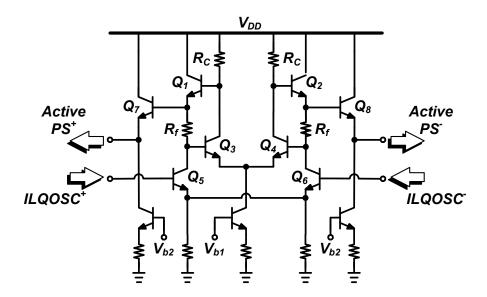

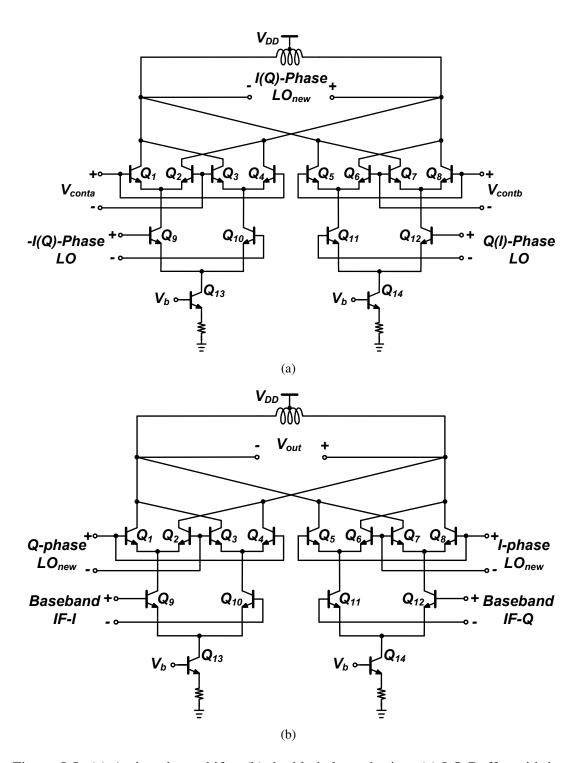

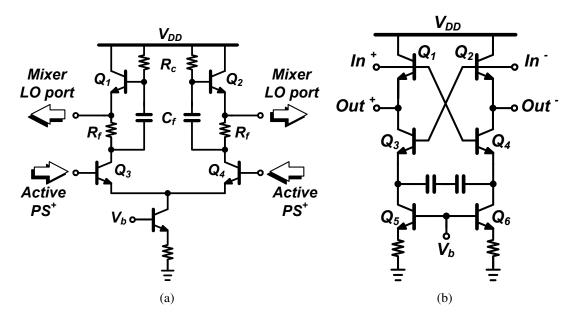

| Figure 5.5:  | (a) Active phase shifter (b) double balanced mixer (c) LO Buffer         |    |

|              | with improved stability and (d) output amplifier                         | 89 |

| Figure 5.6:  | (a) Active phase shifter (b) double balanced mixer (c) LO Buffer         |    |

|              | with improved stability and (d) output amplifier                         | 90 |

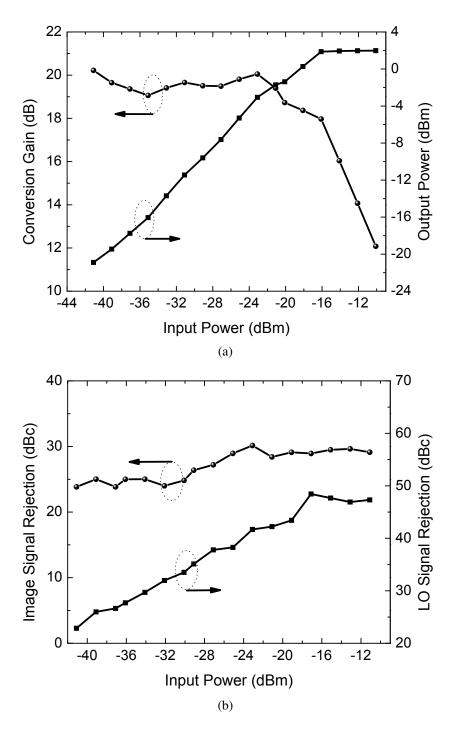

| Figure 5.8:  | (a) conversion gain and RF output power and (b) image and LO             |    |

|              | rejection ratio after calibration with I/Q VGA tuning                    | 92 |

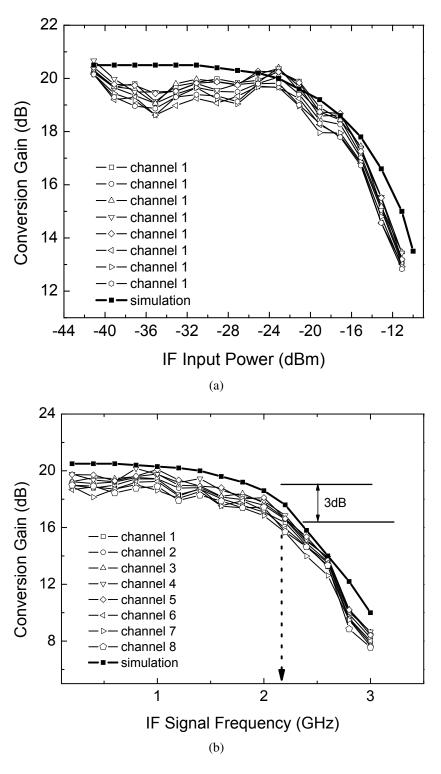

| Figure 5.9:  | Simulated and measured conversion gain at 45GHz with IF input            |    |

|              | (a) power sweep and (b) frequency sweep                                  | 93 |

| Figure 5.7:  | Microphotograph of the phased array transmitter                          | 94 |

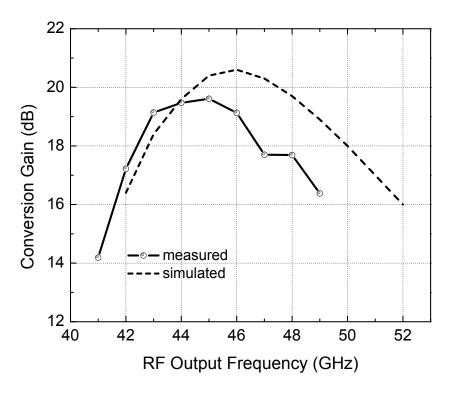

| Figure 5.10: | Conversion gain change with injection-locked LO frequency sweep          |    |

|              | $(f_{if}=1GHz)$                                                          | 95 |

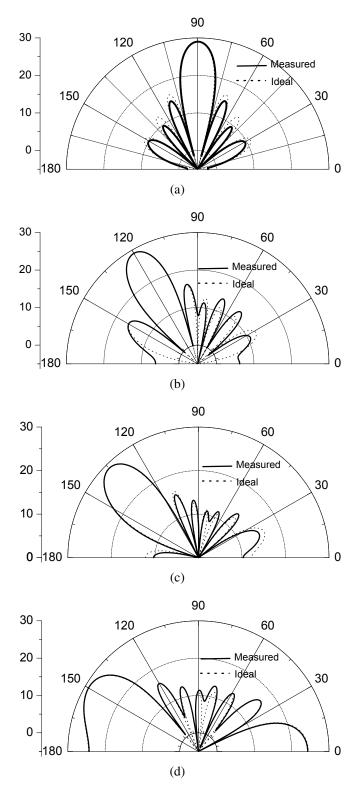

| Figure 5.11: | Calculated array beam scanning pattern (a) 0° (b) 30° (c) 45° (d)        |    |

|              | $60^{\circ}$ scan angle                                                  | 96 |

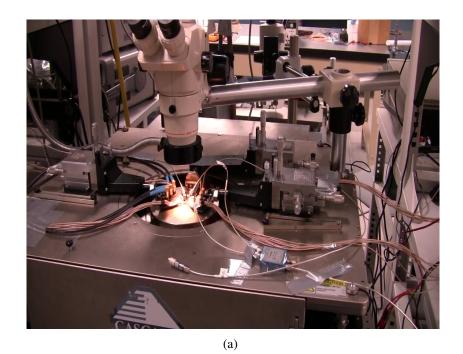

| Figure 5.12: | Measurement setup                                                        | 97 |

#### LIST OF TABLES

| Table 2.1: | Comparison of continuously adjustable phase-shifter | 31 |

|------------|-----------------------------------------------------|----|

| Table 5.1: | Performance Summary                                 | 98 |

#### **ACKNOWLEDGEMENTS**

The completion of my dissertation would not be possible without help and encouragement of many people.

First and foremost, I'd like to offer my sincerest gratitude to my advisor Professor Lawrence E. Larson for his priceless guidance and support throughout my research over the past years. His continuous support, suggestions, valuable discussions and patience were indispensable in making this research and dissertation possible. Especially, our valuable discussions and his suggestions at dawn were like another rising sun in the sea of my knowledge. Also, his sincere, honest and diligent life and research style became the best role model for me. One simply could not wish for a better or friendlier supervisor.

I would also like to thank my committee members, Prof. Peter Asbeck, Prof. James Buckwalter, Prof. Bill Trogler, Prof. Brian Keating, and Dr. Prasad Gudem for their support and crucial comments during preliminary reviews and, additionally, to thank Dr. Donald Kimball and for their generous help with providing test and measurement facilities. I especially appreciate to Prof. Gabriel Rebeiz for his kindly permission to access his lab facilities. Without his help, my high-frequency circuits wouldn't be recognized by the world. I especially value his strong recommendation during my interview with IBM and Intel.

I thank my colleagues and friends for giving me a lot of support and making my long journey more delightful. It is my pleasure to acknowledge my colleagues at UCSD RFIC group for their knowledge and help in my research, especially Mr. Yiping Han, Mr. Marcus Pan, Dr. Sanghoon Park, and former RFIC group members Dr. Joe Jamp, and Dr. Vincent Leung, Dr. Himanshu Khatri, Dr. Farazian Mohammad, Dr. Rahul Kodkani, Mr. Pavel Kolinko. I also extend many thanks to people who are from other

labs and helped me much before: Byung-Wok Min, Jeonggeun Kim, Sangyoung Kim, Jason May, DongWoo Kang, Berke Cetinoneri, Woorim Shin, Donghyup Shin.

I wish to thank DIMES at Delft University of Technology for processing the silicon-on-glass wafers and fabrication of the phase shifters. I also appreciate to Prof. Leo C.N. de Vreede and his group students, Jawad Qureshi, Koen Buisman, Cong Huang, and Mauro Marchetti for the measurement support and valuable discussions.

I also would like to acknowledge the support of the Center for Wireless Communications at UCSD and its member companies, and the University of California Discovery Grant.

It's time to mention the most important people in my life, my parents, who did everything that is humanly possible, so that I could reach any goal I dreamed of throughout my life. They has been doing their best to always provide me with the best education opportunities. My dad showed me how hard work and patience always pays off. I learned not to settle for anything but the best from my mom who has always been the pillar of strength for the whole family. It could not be possible for me to finish this work without their constant help, support, and motivation.

The text of Chapter Two, Three, Four and Five, in part of in full, is a reprint of the material as it appears in the following publications or as it has been submitted for publication in IEEE Transactions on Microwave Theory and Techniques and IEEE Radio Frequency Integrated Circuits (RFIC) Symposium.

- Sunghwan Kim, Jawad H. Qureshi, Koen Buisman, Lawrence E. Larson and Leo

C. N. de Vreede, "A Low-Distortion, Low-Loss Varactor Phase-Shifter Based on

Silicon-on-Glass Technology", IEEE Radio Frequency integrated Circuits (RFIC)

Symposium, June 2008.

- Sunghwan Kim, Jawad H. Qureshi, Koen Buisman, Lawrence E. Larson and Leo

C. N. de Vreede "Analysis of a Low-Distortion, Low-Loss Varactor Phase-Shifter Based on Silicon-on-Glass Technology", submitted to *IEEE Transactions On Microwave Theory and Techniques*, 2010.

- Sunghwan Kim and Lawrence E. Larson "A 44-GHz SiGe BiCMOS Phase-Shifting Sub-Harmonic Up-Converter for Phased Array Transmitters", *IEEE Transactions*.

on Microwave Theory and Techniques, May 2010.

- Sunghwan Kim, Prasad Gudem, and Lawrence E. Larson, "A 44-GHz 8-Element Phased Array SiGe HBT Transmitter RFIC with an Injection-locked Quadrature Frequency Multiplier", IEEE Radio Frequency integrated Circuits (RFIC) Symposium, 2010.

The dissertation author was the primary researcher and the first author listed in these publications. He directed and supervised the research which forms the basis for these chapters.

#### **VITA**

| 2003      | B. S. in Electrical and Compueter Engineering, <i>cum laude</i> , Seoul National University, Seoul |

|-----------|----------------------------------------------------------------------------------------------------|

| 2005      | M.S. in Electrical Enigneering,<br>University of Southern California, Los Angeles                  |

| 2005-2010 | Research Assistant,<br>University of California, San Diego                                         |

| 2009      | RFIC design Intern, Qualcomm, San Diego                                                            |

| 2010      | Ph. D. in Electrical and Computer Engineering,<br>University of California, San Diego              |

#### **PUBLICATIONS**

Sunghwan Kim, P. Gudem, and Lawrence E. Larson, "A 44-GHz 8-Element Phased-Array SiGe HBT Transmitter RFIC with an Injection-locked Quadrature Frequency Multiplier", *IEEEJournal of Solid-State Circuits*, 2010 in preparation.

Sunghwan Kim, Jawad H. Qureshi, Koen Buisman, Lawrence E. Larson and Leo C. N. de Vreede "A Low-Distortion, Low-Loss Varactor Phase-Shifter Based on Silicon-on-Glass Technology", submitted to *IEEE Transactions On Microwave Theory and Techniques*, 2010.

Sunghwan Kim and Lawrence E. Larson "A 44-GHz SiGe BiCMOS Phase-Shifting Sub-Harmonic Up-Converter for Phased-Array Transmitters", *IEEE Transactions. on Microwave Theory and Techniques*, May 2010.

Sunghwan Kim, Prasad Gudem, and Lawrence E. Larson, "A 44-GHz 8-Element Phased-Array SiGe HBT Transmitter RFIC with an Injection-locked Quadrature Frequency Multiplier", *IEEE Radio Frequency integrated Circuits (RFIC) Symposium*, 2010.

Sunghwan Kim, Jawad H. Qureshi, Koen Buisman, Lawrence E. Larson and Leo C. N. de Vreede, "A Low-Distortion, Low-Loss Varactor Phase-Shifter Based on Silicon-on-Glass Technology", *IEEE Radio Frequency integrated Circuits (RFIC) Symposium*, June 2008.

#### ABSTRACT OF THE DISSERTATION

#### Phase Shifter Approaches for Compact Low-Power Phased Array Transmitters

by

#### Sunghwan Kim

Doctor of Philosophy in Electrical Engineering (Electronics Circuits and Systems)

University of California San Diego, 2010

Professor Lawrence E. Larson, Chair

One of the challenges in implementing phased array systems is to implement high performance phase shifters. This dissertation presents highly linear phase shifters for 2GHz wireless mobile applications and millimeter-wave phased array transmitters with active phase shifters. Different architectures of phased array systems pursue different aspects of phase shifters.

In the first part of the dissertation, a low-loss, low-distortion passive variable phase shifter on Silicon-on-Glass (SOG) process will be presented. Schottky diodes in the SOG process enables very high quality factor of varactor diodes and on-chip passive inductors. A novel passive variable phase shifter with varactors and inductors presented in the dissertation has very low third-order intermodulation distortion (IMD3) and low insertion loss, which make it suitable for transmitter front-end applications in mobile devices working at CDMA bands.

In the second part, two generations of integrated phased array upconverters at millimeter-wave frequencies with LO-path phase shifting will be presented. The phase-shifting is achieved by the vector summation of the I/Q LO signals in the LO path. The

first version adopts a frequency doubler followed by a polyphase filter to generate the I/Q basis LO signals. The principal of the active phase shifter operation and frequency doubler are explained. The phase error due to amplitude and phase mismatch of the polyphase filter is discussed. The upconverter can achieve -5dBm maximum output power at 45GHz with 1GHz baseband signal bandwidth.

The eight-element phased-array transmitter is implemented in a  $0.18\mu m$  SiGe BiCMOS process in the later version. To reduce dc power consumption, a localized frequency doubling injection-locked quadrature oscillator is used to ease LO signal distribution. Measured conversion gain over frequency and IF signal is presented. Array beam scanning pattern is also presented based on the measured phase and power for each channel.

# Chapter 1

# Introduction

#### 1.1 The Growth of Wireless Data Communication

A huge growth in the wireless communication market was observed during the last several decades as mobile data and voice become ubiquitous. This explosion has been fueled by the low cost integration of wireless ICs on silicon processes, which provide sufficiently high-frequency performance through device scaling. The integration of RF ICs on silicon with CMOS and BJT devices now dominates in the mobile wireless transceivers market operating below 5GHz.

Nevertheless, the demand for increasing number of subscribers and data rates for data-intensive wireless applications is exploding. Data transfer from high resolution digital cameras, transfer of music and video and other multimedia content between a computer and a portable device, such as the ubiquitous iPod, are some obvious examples. Emerging applications also include transmission of uncompressed video (Wireless HD [1]) between a multimedia device and an HD flat screen television or projector supporting multi-Gb/s data rate. This market demand leads designers to explore frequency reuse with multiple antenna systems and wider frequency bandwidth in the higher fre-

quencies.

Andrew Viterbi – founder of Qualcomm Inc.– stated:

"Spatial processing remains as the most promising, if not the last frontier, in the evolution of multiple access systems." [2]

Spatial processing is one of the most practical solutions to these challenges. Spatial processing — or filtering — is the core idea of "smart antenna" systems, which was first used during World War II with the Bartlett beamformer [3]. Smart antenna systems are used to enhance the performance of wireless communications and radar systems under various names, such as beam-forming arrays, phased arrays, and MIMO transceivers. Even nowadays, the use of phased arrays is the most widespread in the realm of defense, with warships and fighter planes using phased array antennas for communications and radar applications.

# 1.2 Principal of Phased Array Antenna Systems

The fundamental concept of an phase array system is illustrated in Fig. 1.1, which shows a simplified N-element linear phased array system. The principle of operation of phased array antennas system is the same for receivers and transmitters.

For uniformly illuminated phased array, the difference in propagation distance between adjacent elements (mostly antennas) for signals arriving with an incident angle of  $\theta$  is  $d\sin\theta$ . Then, in a narrow band system, the phase difference of the incoming signals between adjacent antenna is given by  $\Delta\phi=\left(\frac{2\pi}{\lambda}\right)d\sin\theta$ , where  $\lambda$  is the wavelength of the signals. The voltage sum of all the signals from the individual elements can be written by

Figure 1.1: An N-element phased array antenna system.

$$S_t = A_m \sum_{k=0}^{N-1} \sin(\omega t + k\Delta\phi). \tag{1.1}$$

The sum can be simplified as

$$S_t = A_m \sin\left(\omega t + (N-1)\frac{\Delta\phi}{2}\right) \left(\frac{\sin\left(N\Delta\phi/2\right)}{\sin\left(\Delta\phi/2\right)}\right). \tag{1.2}$$

The magnitude of (1.2) is given by

$$|S_t(\theta)| = A_m \left| \frac{\sin\left[N\left(\frac{\pi}{\lambda}\right) d \sin \theta\right]}{\sin\left[\left(\frac{\pi}{\lambda}\right) d \sin \theta\right]} \right|, \tag{1.3}$$

which is also called the field-intensity pattern. Eq.(1.3) has its maximum at

$$\theta = \sin^{-1}(n\lambda/d), n = 0, 1, 2, \dots$$

(1.4)

The incoming signal incident angle  $\theta$  can be controlled by placing phase shifters in the signal path to compensate for the phase difference of the path. At its maximum, coherent addition of the signal occurs, and hence there is an increase in the power radiated or received in the desired direction. On the other hand, in other directions, incoherent addition of the signal reduces the transmitting or receiving power. The array pattern can be expressed by a normalized radiation pattern, which is called the *array factor*. For isotropic antennas, the array factor is

$$AF(\theta) = \frac{\left|S_t(\theta)\right|^2}{A_m^2 N^2} = \frac{\sin^2\left[N\left(\frac{\pi}{\lambda}\right) d \sin \theta\right]}{N^2 \sin^2\left[\left(\frac{\pi}{\lambda}\right) d \sin \theta\right]}.$$

(1.5)

The simulated array factor of omnidirectional eight antennas with beam angle from 20°

to  $160^{\circ}$  with antenna spacing of  $\lambda/2$  are shown in Fig. 1.2. The 3dB beamwidth of this

Figure 1.2: The Array Factor of an 8 element linear phased array. The beam angle is from  $20^{\circ}$  to  $160^{\circ}$ .

uniformly illuminated linear phased array of N elements is approximately

$$\theta_B = \left(\frac{50.8\lambda}{N \cdot d}\right)^{\circ}.\tag{1.6}$$

Eq. (1.6) tells us that the azimuth resolution is inversely proportional with the wavelength and hence proportional to the frequency. High-frequency phased arrays systems are suitable for applications that require the ability to differentiate two close objects. The first (and largest) sidelobes for the phased array are 13.2dB below the main beam maximum value. Hence, phased array systems works as a spatial filter.

In transmitters, the effective isotropic radiated power (EIRP) in the main beam

direction is improved by phased array antennas. EIRP is defined as <sup>1</sup>

$$EIRP = P_T - L_c + G_a, (1.7)$$

where  $P_T$  is the transmitting power in dBm,  $L_c$  is the cable loss in dB, and  $G_a$  is the antenna gain expressed in dBi. When each transmitter element radiates X watts through isotropic antennas, roughly  $N^2X$  watts power is radiated in the main beam. Therefore, there is  $10 \log_{10}(N^2)$  improvement in EIRP by phased array antennas. This is particularly useful in high frequency applications since the signal suffers high attenuations in the air and substrate loss in silicon integration.

# 1.3 An Overview of Phased Array Transmitter Architectures

Phased arrays are one of multiple antenna systems that can electronically change the direction of transmission and reception of the electromagnetic beam in a particular direction by constructive signal addition, while simultaneously blocking it to other directions by destructive signal cancellation. This can be done by introducing a variable time delay in each signal path to compensate for the path differences in free space. In narrowband systems, the required variable time delay element can be substituted by a variable phase shifter.

The variable phase shifter required to achieve phased array functionality can be incorporated in different parts of the transmitter/receiver chain. Although all schemat-

<sup>&</sup>lt;sup>1</sup>The amount of power that a theoretical isotropic antenna (which evenly distributes power in all directions) would emit to produce the peak power density observed in the direction of maximum antenna gain.

Figure 1.3: (a) RF phase shifting (b) LO phase shifting (c) IF phase shifting (d) baseband phase shifting architectures.

ics (Fig. 1.3(a)-(d)) represent transmitter arrays, the fundamental principles apply to receiver arrays as well. In fact, the receiver architecture is the reciprocal of transmitter.

Fig. 1.3(a) illustrates the RF phase-shifting architecture for phased array transmitters. In a receiver architecture, the received signals in the distinct channel are phase shifted and combined in the RF territory. Then, this combined signal is downconverted to baseband by frequency conversion blocks (which is usually a mixer). In the transmitter architecture as shown in the Fig. 1.3(a), the upconverted signal from a baseband is divided into each phase shifter in the RF domain. The RF phase shifting architecture has been the most popular phased array architecture in tradition. This is because of its high signal-to-interferer ratio (SIR). When the in-band interferer is incident along a null direction the signal combining occurs prior to downconversion in this architecture, and the interfere is cancelled prior to the downconversion mixer. This high SIR alleviates the linearity and dynamic range requirement of the downconversion mixer and the following blocks such as A/D converter. On the other hand, the performance of the phase shifter directly affects the data signal. The insufficient linearity of the phase shifter often negates the advantage of the RF phase shift architecture. Passive implementations of the phase shifter achieves higher linearity than active phase shifters at the expense of the loss of passive phase shifter. In addition, low noise performance of the phase shifter is essential as the phase shifter lies in the RF signal path and hence, it can degrade the system noise figure. In the transmitter architectures, low-loss, high-linearity performance of the phase shifter at large signal regime is demanded, in order not to degrade the system linearity and output signal power level. High performance passive phase shifters can be implemented with the power amplifier unit, which typically uses compound (III-V) process technologies such as GaAs or InP, or silicon-on-insulator (SOI) process technologies.

Fig. 1.3(b) illustrates the LO phase-shifting architecture for phased arrays. Phase-shifting of the LO of each signal path is equivalent to phase-shifting the RF signal since the mixing of the RF signal with the LO results in an addition or subtraction of their phases. In this architecture, in both receiver and transmitter, the linearity, gain and noise performance of the phase shifter no longer directly affect the system performance. However, in receivers, in-band interferers are cancelled after the downconversion mixer, which requires the high dynamic range of the mixers to tolerate the interferers. In millimeter-wave applications, on-chip implementations of the high performance passive phase shifter are much harder than in lower frequency, e.g. below 10GHz. For that reason, the LO phase-shifting architecture is sometimes preferred in mm-wave frequency ICs, since the required performance specification of the active phase shifters in the LO path is relaxed.

In the IF phase-shifting architecture, the phase shifters are implemented in the IF band (Fig. 1.3(c)). Due to low operating frequency, the circuit implementation can be relatively easier. However, the size of passive component in the phase shifters are consequently large.

In the baseband phase shifting architecture (Fig. 1.3(d)), a digital signal processor synthesize the phase shift at baseband frequency. It it a very versatile architecture for receivers and transmitters, since the system can be configured for different types of signals. However, the required processing power of the digital signal processor and high dynamic range of the A/D converters makes designers to hesitate to use this architecture.

# 1.4 Phased Array Applications

Recently, phased arrays are gaining the spotlight for consumer mobile communications such as cellular telephones, WiMax/Wi-Fi wireless networking and internet

access (802.11 and IEEE 802.16 standards). One example of phased array antenna systems to improve spectral efficiency in a conventional cellular wireless communication system is shown in Fig. 1.4(a). The high directional beam pattern in phased array antenna systems allows interference reduction/mitigation and allows increased number of subscribers to share or reuse the same available resources such as frequency, time and codes [4]. This improved spectral efficiency introduces a new multiple access scheme that exploits the space domain, space division multiple access (SDMA).

Phased array antenna systems have been considered mostly for base stations so far due to high system complexity and high power consumption. Recently, phased array antenna techniques begin to be applied to mobile stations or handsets [5, 6] to further suppress the interference signal and improve multipath fading problem (Fig. 1.4(b)). Also, one of the third generation wireless personal communication systems, third generation partnership project (3GPP), WCDMA system [7], requires antenna diversity at base stations and optionally at mobile stations. Because of the compact size and the limited battery capacity of the handset, phased array antennas at handsets should dissipate low power with simple circuity without compromising high performance gain.

In satellite communication systems such as IRIDIUM ([8]) and Globalstar([9]) (personal communication) and Military Strategic and Tactical Relay (Milstar) (Defense satellite communications), the same problem — interference and multipath fading — remain challenges for reliable reception of signals [10, 11, 12]. Hence, phased array antennas were adopted earlier than cellular communication systems to tackle those problems.

Figure 1.4: (a) Beamforming in cellular wireless communication system. Beam is formed by the base station and (b) handset beamforming in cellular wireless communication system. Dual antennas are adopted in mobile handsets.

#### 1.5 Millimeter-wave Wireless Communication

Shannon's theorem tells us that channel capacity is proportional to bandwidth and a logarithmic function of SNR [13].

$$C = BW \cdot \log_2(1 + SNR) \tag{1.8}$$

The thirst for higher data rate encouraged wider bandwidth and complex modulation schemes to compress as many bits-per-second/Hz as possible. Low GHz wireless communications standards such as the IEEE 802.11(a,b,g,n), Bluetooth, and Zigbee suffer from the limited data transfer rate — a few hundreds of Mega Bits Per Second (Mbps) — in its 2.4GHz and 5GHz frequency band. Fig. 1.5 shows the data rates and range requirements for number of wireless local area network (WLAN) and wireless personal area network (WPAN) systems [14]. IEEE802.15.3c group developed a millimeter-wave-based alternative physical layer for the existing 802.15.3 WPAN standard operating in clear band including 57-64 GHz unlicensed band defined by FCC 47 CFR15.225.

The key advantage of mm-wave wireless communications comes from the wide unlicensed bandwidth available in the 60GHz range, e.g. 57-64GHz unlicensed band in the U.S. Millimeter-wave frequencies also have a wider bandwidth than lower carrier frequencies for the same fractional bandwidth; hence, higher data rate transmission is possible. This increased bandwidth can also simplify the signal modulation hardware, since a sophisticated baseband signal modulation scheme is less demanding.

The wavelength of an electromagnetic wave decrease with increasing frequency. For example, a 60 GHz quarter-wave length ( $\lambda/4$ ) electromagnetic wave in silicon diox-

Figure 1.5: Data rates and range requirements for WLAN and WPAN standards and applications. Millimeter wave technology, IEEE 802.15.3c is aiming for very high data rates.

ide dielectric is  $600\mu m$ , whereas it is 15mm at 2.4 GHz. In mm-wave wireless systems, the size of antenna and passive elements can be reduced, decreasing the size of the form factor and the manufacturing cost.

However, mm-wave signal propagation at the 60GHz band highly is attenuated due to oxygen absorption (Fig. 1.6) [15]. Short range applications, such as WPAN, benefit from this atmospheric absorption, which provides natural spatial isolation. The spatial isolation/direction leads to less interference and hence higher data rates of transmission. On the other hand, the high atmospheric attenuation can be an obstacle for long range applications. Phased array antennas are an attractive solution to expand the range by directional beamforming to the desired target direction. In another point of view, by combining the signals from different channels in the air, directivity can be increased. This directional beamforming is an attractive solution to expand its range for high frequency, long range applications. In particular, power amplifier output power

Figure 1.6: Specific attenuation for atmospheric gases as a function of frequency.

requirement can be relieved by distributing the total output power to smaller distributed power amplifiers (PAs) in each channel. This is also beneficial for PAs with CMOS technology with low breakdown voltages as the size of the transistors is reduced.

# 1.6 Dissertation Objectives and Organization

This dissertation can be divided into two broad sections. The first part of this dissertation focuses on phase shifter implementation in the RF path. While it is implemented with passive components, it has a superior performance in terms of gain and linearity, which again makes it suitable for the RF path phase shifting architecture of phased array transmitter, in conjunction with its scalability over phase shift variation. While the linearity has been studied extensively for active phase shifters, the linearity analysis of passive phase shifter with varactor diodes has not been explored thus far. The third-order intermodulation distortion was analyzed by a Volterra series considering memory components in the passive phase shifters such as variable capacitors and inductors.

In Chapter 2, a new variable passive phase shifter based on an all-pass network is presented. The variable phase shifter was implemented on silicon-on-glass technology, which accommodates a high quality factor varactor diode. Circuit design procedure and the linearity and phase variation measurement are presented. Its high-linearity and low-loss performance is compared with recently published phase shifters.

In Chapter 3, the linearity of the phase shifter introduced in Chapter 2 is discussed and extensively analyzed for the several cases of configuration of diodes. A closed-form third-order intermodulation distortion is presented and compared with simulation results.

The second part of this dissertation focuses on the design of a mm-wave phased

array upconverter with an active phase shifter implemented in the LO path.

In Chapter 4, a 44GHz phase-shiting sub-harmonic upconverter implemented in  $0.18\mu m$  SiGe BiCMOS is presented. For active phase shifting functionality, variable gain amplifiers are designed. For quadrature signal generation, a two-stage RC polyphase filter followed by a frequency doubler is presented. The Chapter discusses the design, optimization, and performance trade-offs of each building block. The Phase error out of the RC polyphase filter and the operation of the frequency doubler is analyzed.

In Chapter 5, an eight-element phased array transmitter with an injection-locked quadrature frequency multiplier is presented. This novel architecture help to reduce the required LO signal power from the phase-locked loop (PLL) and provides wider frequency tunability through wide frequency locking range of the ring oscillator. Its measured result and calculated array patterns are presented.

Chapter 6 summarize the whole research work.

# Chapter 2

# A Low-Distortion, Low-Loss Varactor

# **Phase-Shifter**

### 2.1 Introduction

A phase-shifter is a critical component in the transmit and receive paths of phased-array radar and communication systems, which requires high data rates such as multiple-input multiple-output (MIMO) technology [16, 17, 18, 19]. The performance requirements in these systems are stringent; the phase shifters should be highly linear to prevent signal distortion and they should be compact for a small form factor. They are also required to have low dc power consumption and low insertion loss. MEMS phase shifters are excellent candidates for phased array antenna systems, since they demonstrate outstanding performance in many applications in terms of low insertion loss and high linearity [20, 21].

However, phase shifters based on MEMS varactor loaded transmission lines still suffer from relatively high cost due to non-standard processing and hermetic packaging. An alternative to MEMS varactors would be varactor diodes, and the linearity and loss

of varactor diodes were recently improved using uniformly doped Schottky diodes in anti-series configuration associated with a dedicated silicon-on-glass technology [22, 23].

A varactor-loaded transmission-line based phase-shifters are one popular type, and were presented in [24, 25]. Lumped element transmission-lines are widely used in this type of phase shifters to reduce chip size. However, the size of transmission-line inevitably becomes large inversely proportional to the desired working frequency.

Active variable resonance circuits based and vector-modulator type phase shifters [26, 27] have fairly good gain at the expense of dc power consumption. Typically, its linearity was reported relatively low.

In this work, a high-performance varactor based phase shifter is introduced. Section 2.2 shows the properties of all-pass networks. Section 2.4 explains the circuit design of the phase shifter based on an all-pass network. Section 3.1 analyze the linearity of the phase shifter with Volterra series approach. The measured results and conclusion are followed in Sections 2.5 and 2.6.

## 2.2 Design Theory

Lossless all-pass networks are ideal candidates for phase shifters, since they vary the phase of a signal without affecting its magnitude. One simple implementation is shown in Fig. 2.1(a) [28, 29]. If the reactance components are designed such that

$$Z_a \cdot Z_b = R_L^2, \tag{2.1}$$

Figure 2.1: (a) Schematic of an all-pass network with LC reactance component and (b) schematic of a proposed all-pass network phase shifter.

where  $R_L$  is the load resistance, then the input impedance of the circuit is  $R_L$  and the voltage transfer function of the circuit is

$$\frac{V_o\left(s\right)}{V_{in}\left(s\right)} = \left(\frac{1 - Z_a\left(s\right)/R_L}{1 + Z_a\left(s\right)/R_L}\right) \tag{2.2}$$

From (2.2), the phase shift of this network is given by

$$\angle \left(\frac{V_o}{V_{in}}\right) = \Delta \phi = -2 \arctan\left(\omega R_S C\right),$$

(2.3)

where  $L/C = R_S^2$ .  $R_S$  is the source impedance and the phase shifter is designed such that  $R_L = R_S$ . From (2.3), a variable phase shift can be achieved by tuning the capacitance and inductance. Over a small frequency bandwidth, a variable inductance can be approximated by a fixed inductor in series with a variable capacitance  $C_t$ . The proposed circuit is introduced in Fig. 2.1(b).

In order to find appropriate values of capacitors, we set the capacitance  $C_t$  to be

$\alpha$  times larger than C. The capacitance tuning ratio r, given by  $C_{max}/C_{min}$ , is limited by the process technology. The reactance of the series combination of  $L_{fix}$  and  $C_t$  can be expressed as

$$X_L = \omega L_{fix} - \frac{1}{\omega C_t}. (2.4)$$

The reactance  $X_L$  and  $1/\omega C$  change in the opposite direction satisfying the condition (2.1), i.e.,

$$X_L|_{max} \cdot \frac{1}{\omega C}\Big|_{min} = X_L|_{min} \cdot \frac{1}{\omega C}\Big|_{max} = R_S^2$$

(2.5)

For a given  $C_{min}$  and capacitance tuning range (r),

$$\alpha = r^{-1} \left( \omega R_S C_{min} \right)^{-2} \tag{2.6}$$

$$L_{fix} = (1+r)R_S^2 C_{min} (2.7)$$

For a  $50\Omega$  source and load impedance, and a varactor tuning ratio r of 4:1 given by the process technology, the ratio of  $C_t$  to C, and the necessary inductance L, can be obtained as a function of the minimum capacitance  $C_{min}$  as shown in Fig. 2.2. As  $C_{min}$  decreases, the achievable phase shift increases by (2.3) and the lower inductance shrinks the entire chip size. However, it also increases the size of  $C_t$ . An optimum value of  $C_{min}$  of 260fF is chosen in this case. The corresponding maximum achievable change in phase shift per section can be calculated from (2.3), which is approximately  $48^{\circ}$ .

Figure 2.2: Simulated value of  $\alpha$  (= $C_t/C$ ) and required inductance as a function of minimum capacitance  $C_{min}$  at 2GHz (capacitor tuning ratio r is 4:1).

#### 2.3 Process Technology

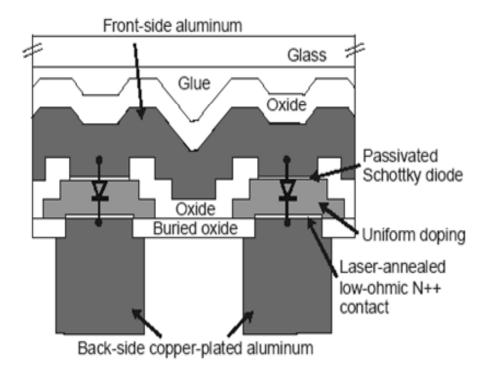

In order to design a phase shifter based on the all-pass network, high-performance variable capacitors are necessary. In this study, a dedicated silicon-on-glass technology, which was developed at the Delft University of Technology is employed [30]. This technology provides a low-loss substrate and patterning of both the front and back sides of the wafer, so the intrinsic varactor can be directly contacted by thick metal on both sides (Fig. 2.3). This removes the need for a buried layer or finger structures, as would be the case in conventional integrated varactor implementations [22]. Moreover, this technology presents a very high performance Schottky varactor diode; quality (Q) factor ranges typically from 50 to 300 at 2GHz and the effective capacitance tuning range

Figure 2.3: Cross section of the silicon-on-glass varactor technology.

of the uniformly doped diodes is approximately 4:1.

#### 2.4 Phase Shifter Circuit Design

#### 2.4.1 Variable Capacitor Design

A schematic of a single phase shifter stage based on anti-series varactors is shown in Fig. 2.4. As was explained in [22, 24, 31, 32], for uniformly doped anti-series diodes with a sufficiently high center-tap impedance, the varactor is ideally "distortion-free". The impedance of the dc biasing network should be significantly larger than the reactance of the varactor diodes at baseband. Otherwise, RF current will leak through the dc biasing network.  $120k\Omega$  center-tap resistors are used. Anti-parallel diode pairs can be used to further increase the center-tap impedance.  $120k\Omega$  resistors are also con-

Figure 2.4: Schematic of the phase shifter with distortion-free diode varactors and magnetically coupled inductors.

nected at the input and output of each stage to provide dc ground for the varactor diodes. Varactor diode pairs  $C_a$  and  $C_b$  have zero bias capacitance of 10pF and 1pF, respectively.

#### 2.4.2 Inductor Design and Layout

Figure 2.5: Magnetically coupled inductors.

The two separated fixed inductors are substituted with magnetically coupled inductors in order to increase the *effective* inductance. The V-I relationship for two magnetically coupled inductors (Fig. 2.5) can be written as

$$\begin{bmatrix} V_1(s) \\ V_2(s) \end{bmatrix} = \begin{bmatrix} sL_1 + R_1 & sM \\ sM & sL_2 + R_2 \end{bmatrix} \begin{bmatrix} I_1(s) \\ I_2(s) \end{bmatrix}, \tag{2.8}$$

where  $M=k\sqrt{L_1L_2}$ , k is the coupling coefficient, and  $R_1$  and  $R_2$  are parasitic resistances. For 1:1 coupled inductors in the phase shifter, we can assume  $L_1=L_2=L_{fix}$  and  $R_1=R_2=R$ . If  $i_2/i_1=Ae^{j\theta}$ , then the V-I relationship at the primary and

secondary ports can be expressed as

$$V_{1} = \left[j\omega L_{fix}(1 + kA\cos\theta) + (R - \omega kAL_{fix}\sin\theta)\right]I_{1}$$

$$V_{2} = \left[j\omega L_{fix}(1 + kA^{-1}\cos\theta) + (R + \omega kA^{-1}L_{fix}\sin\theta)\right]I_{2}$$

(2.9a)

For a balanced differential signal applied at the input of the phase shifter, A=1,  $\theta=180^{\circ}$ . Consequently, (2.9) becomes

$$V_1 = [j\omega L_{fix}(1-k) + R] I_1$$

(2.10a)

$$V_2 = [j\omega L_{fix}(1-k) + R] I_2$$

(2.10b)

Therefore, the effective inductance is given by

$$L_{eff} = L_{fix}(1 - k) (2.11)$$

By substituting  $L_{fix}$  in (2.7) with  $L_{eff}$  in (2.11),

$$L_{fix} = \left(\frac{1+r}{1-k}\right) R_S^2 C_{min} \tag{2.12}$$

For k < 0, the required inductance  $L_{fix}$  decreases as |k| increases.

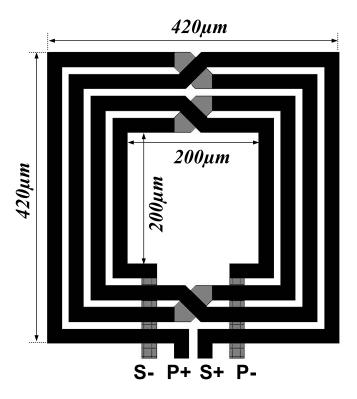

As shown in Fig. 2.6, the 1:1 interleaved transformer is designed on the toplevel metal layer of the process. This type of transformer is best suited for four-port

Figure 2.6: Layout of the magnetically coupled inductors in the phase shifter.

applications that demand symmetry, since the electrical characteristics of the primary and secondary are identical when they have the same number of turns [33, 34]. The outer diameter of the transformer is  $420\mu m$  and the inner diameter is  $200\mu m$ . A full EM-simulation was performed, and a coupling coefficient of -0.6, with self-inductance of 2.1nH, was obtained.

#### 2.4.3 Cascaded Phase Shifter Architecture

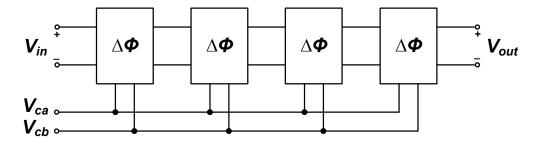

As discussed earlier, the proposed all-pass network phase shifters have a limited phase variation of approximately 48°. Four identical phase shifters, which are connected in sequence as shown in Fig. 2.7 to achieve a total phase variation of 180°, can overcome the limited phase shift of each stage. Since (2.1) is maintained during normal operation,

Figure 2.7: Four stages phase shifter architecture.

the input impedance of the first stage duplicates the load resistance  $R_L$ . Tuning voltage nodes  $V_{ca}$  and  $V_{cb}$  are connected separately so that only two tuning voltages are required.

#### 2.5 Experimental Results

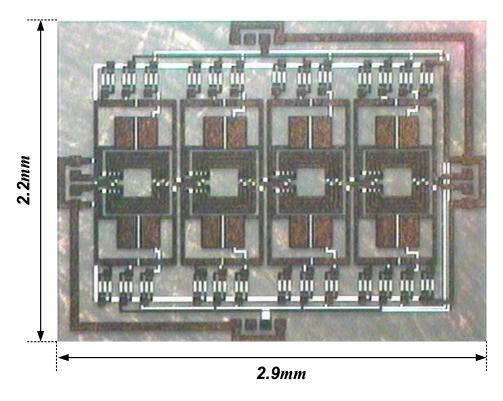

A microphotograph of the phase shifter is shown in Fig. 2.8. Differential two-

Figure 2.8: Microphotograph of the phase shifter realized in silicon-on-glass technology.

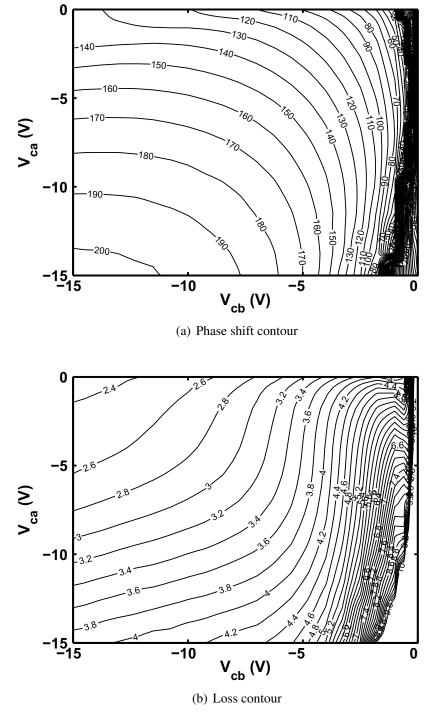

port S-parameter measurements were performed after LRM calibration. The two dc control voltages were swept to find optimum pairs of  $V_{ca}$ ,  $V_{cb}$ . The measured phase shift (= $\angle S_{21}$ ) and insertion loss at 2GHz are shown in Fig. 2.9(a) and (b) in the form of contour lines. It must be noted that although the dc control voltages are quite high, very little dc current (on the order of  $10\mu A$ ), which is the total leakage current of the realized varactor diodes, is required. This phase shifter can achieve continuous phase shift up to  $180^{\circ}$  with insertion loss less than 3.7dB as shown in Fig. 2.10.

The variation of the insertion loss with phase shift is due to the Q factor variation of the varactors with bias. The higher than expected insertion loss is due to the Q factor of the varactor diodes being slightly lower than the desired value for this wafer. The measured phase shifter return losses for three different phase shifts  $(\Delta\phi=160^{\circ}, 180^{\circ})$  and  $200^{\circ}$  are shown in Fig. 2.11 and are better than -10dB.

A two-tone test was performed on the phase shifter at 2GHz using a  $50\Omega$  differential two-port measurement fixture. For the calibrated power measurement of all frequency components of interest, the linearity of the phase shifter was measured with the load pull system of [40]. Fig. 2.12 gives the measured IM3 components as function of input power for three different tone-spacings ( $\Delta f$ =1MHz, 10MHz and 100MHz) for a target phase shift of 80°. IM3 components are less than -70dBm and -85dBm for 1MHz and 10MHz tone-spacing at  $P_{in}$ =10dBm, respectively.

This corresponds to an IIP3 better than +45dBm for 1MHz tone-spacing and +52dBm for 10MHz tone-spacing. The phase shifter circuit has been fabricated in the high performance silicon-on-glass technology. A performance summary of this variable phase shifter and its comparison to other works in the same band is shown in Table 2.1.

Figure 2.9: (a) Measured phase shift contour lines and (b) measured loss contour lines as a function of control voltages  $V_{ca}$  and  $V_{cb}$  at 2GHz.

Figure 2.10: Minimum loss vs. phase shift at 2GHz.

Figure 2.11: Measured  $\mid S_{11} \mid$  of the phase shifter at optimum tuning voltage pairs.

Table 2.1: Comparison of continuously adjustable phase-shifter

| Ref.                                                                | [26]                                                                                                                                     | [27]                                                                                                           | [35]                                                                                                         | [36]                                                     | [37]                                                                |

|---------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------|----------------------------------------------------------|---------------------------------------------------------------------|

| Freq.                                                               | 2.4GHz                                                                                                                                   | 0.GHz8                                                                                                         | 2.4GHz                                                                                                       | 2.4GHz                                                   | 2.4GHz                                                              |

| Phase var.                                                          | 360°                                                                                                                                     | 120°                                                                                                           | 105°                                                                                                         | 120°                                                     | 255°                                                                |

| Gain                                                                | $2\pm0.7$ dB                                                                                                                             | $1.6 \pm 0.6 dB$                                                                                               | -4.6dB                                                                                                       | -5dB                                                     | -3.75dB                                                             |

| Linearity                                                           | -12dBm                                                                                                                                   | -2.5dBm                                                                                                        | 10dBm                                                                                                        | 6dBm                                                     | n.a.                                                                |

|                                                                     | (IIP3)                                                                                                                                   | (IIP3)                                                                                                         | (P1dB)                                                                                                       | (P1dB)                                                   |                                                                     |

| Power con.                                                          | 90mW                                                                                                                                     | 9mW                                                                                                            | 18mW                                                                                                         | 111mW                                                    | $\sim 0 \mathrm{mW}$                                                |

| Circuit area                                                        | $2.3mm^{2}$                                                                                                                              | $0.81mm^{2}$                                                                                                   | $1.08mm^{2}$                                                                                                 | $0.357mm^2$                                              | $5.72mm^2$                                                          |

| Technology                                                          | $0.3 \mu \mathrm{m}$                                                                                                                     | $0.6 \mu \mathrm{m}$                                                                                           | $0.18 \mu \mathrm{m}$                                                                                        | $0.18 \mu \mathrm{m}$                                    | BST on                                                              |

|                                                                     | GaAs                                                                                                                                     | GaAs                                                                                                           | CMOS                                                                                                         | CMOS                                                     | sapphire                                                            |

|                                                                     | MESFET                                                                                                                                   | MESFET                                                                                                         |                                                                                                              |                                                          |                                                                     |

| Principle                                                           | active vari-                                                                                                                             | active vec-                                                                                                    | reflective                                                                                                   | reflective                                               | active                                                              |

|                                                                     | able reso-                                                                                                                               | tor modu-                                                                                                      | type                                                                                                         | type                                                     | all-pass                                                            |

|                                                                     | nance cir-                                                                                                                               | lator                                                                                                          |                                                                                                              |                                                          | network                                                             |

|                                                                     | cuit                                                                                                                                     |                                                                                                                |                                                                                                              |                                                          |                                                                     |

|                                                                     |                                                                                                                                          |                                                                                                                |                                                                                                              |                                                          |                                                                     |

| Ref.                                                                | [38]                                                                                                                                     | [24]                                                                                                           | [39]                                                                                                         | This                                                     | work                                                                |

| Ref. Freq.                                                          | [38]<br>2.4/5.5GHz                                                                                                                       | [24]<br>1GHz                                                                                                   | [39]<br>2.4/3.5/5.8G                                                                                         |                                                          | work<br>Hz                                                          |

|                                                                     |                                                                                                                                          |                                                                                                                |                                                                                                              | Hz 2G                                                    |                                                                     |

| Freq.                                                               | 2.4/5.5GHz                                                                                                                               | 1GHz                                                                                                           | 2.4/3.5/5.8G                                                                                                 | 6Hz 2G                                                   | Hz                                                                  |

| Freq. Phase var.                                                    | 2.4/5.5GHz<br>360°                                                                                                                       | 1GHz<br>180°                                                                                                   | 2.4/3.5/5.8G<br>180°                                                                                         | GHz 2G<br>18<br>-3±0                                     | Hz<br>80°                                                           |

| Freq. Phase var. Gain                                               | 2.4/5.5GHz<br>360°<br>4dB<br>1dBm<br>(IIP3)                                                                                              | 1GHz<br>180°<br>-1.2dB                                                                                         | 2.4/3.5/5.8G<br>180°<br>-6.6dB                                                                               | GHz 2G<br>18<br>-3±0                                     | Hz<br>80°<br>).7dB                                                  |

| Freq. Phase var. Gain Linearity Power con.                          | 2.4/5.5GHz<br>360°<br>4dB<br>1dBm<br>(IIP3)<br>28.8mW                                                                                    | 1GHz<br>180°<br>-1.2dB<br>45dBm                                                                                | 2.4/3.5/5.8G<br>180°<br>-6.6dB<br>n.a.<br>45mW                                                               | 6Hz 2G<br>18<br>-3±0<br>53dBm<br>~0n                     | Hz<br>30°<br>).7dB<br>n (IIP3)<br>mW                                |

| Freq. Phase var. Gain Linearity                                     | 2.4/5.5GHz<br>360°<br>4dB<br>1dBm<br>(IIP3)                                                                                              | 1GHz<br>180°<br>-1.2dB<br>45dBm<br>(IIP3)                                                                      | 2.4/3.5/5.8G<br>180°<br>-6.6dB<br>n.a.                                                                       | 6Hz 2G<br>18<br>-3±0<br>53dBm<br>~0n                     | Hz<br>30°<br>).7dB<br>n (IIP3)                                      |

| Freq. Phase var. Gain Linearity  Power con. Circuit area            | 2.4/5.5GHz<br>360°<br>4dB<br>1dBm<br>(IIP3)<br>28.8mW<br>6mm <sup>2</sup>                                                                | 1GHz<br>180°<br>-1.2dB<br>45dBm<br>(IIP3)<br>~0mW<br>n.a.                                                      | 2.4/3.5/5.8G<br>180°<br>-6.6dB<br>n.a.<br>45mW<br>2.76mm <sup>2</sup>                                        | 6Hz 2G<br>18<br>-3±0<br>53dBm<br>~0n<br>6.38             | Hz<br>30°<br>0.7dB<br>n (IIP3)<br>mW<br>mm <sup>2</sup>             |

| Freq. Phase var. Gain Linearity  Power con. Circuit                 | 2.4/5.5GHz<br>360°<br>4dB<br>1dBm<br>(IIP3)<br>28.8mW<br>6mm²                                                                            | 1GHz<br>180°<br>-1.2dB<br>45dBm<br>(IIP3)<br>~0mW<br>n.a.<br>Schottky                                          | 2.4/3.5/5.8G<br>180°<br>-6.6dB<br>n.a.<br>45mW<br>2.76mm <sup>2</sup>                                        | 6Hz 2G<br>18<br>-3±0<br>53dBm<br>~0n<br>6.38             | Hz<br>30°<br>).7dB<br>n (IIP3)<br>mW                                |

| Freq. Phase var. Gain Linearity  Power con. Circuit area Technology | 2.4/5.5GHz<br>360°<br>4dB<br>1dBm<br>(IIP3)<br>28.8mW<br>6mm <sup>2</sup><br>0.18μm<br>CMOS                                              | 1GHz<br>180°<br>-1.2dB<br>45dBm<br>(IIP3)<br>~0mW<br>n.a.<br>Schottky<br>on SOI                                | 2.4/3.5/5.8G<br>180°<br>-6.6dB<br>n.a.<br>45mW<br>2.76mm <sup>2</sup><br>0.18μm<br>CMOS                      | 3Hz 2G<br>18<br>-3±0<br>53dBm<br>~0n<br>6.38<br>Schottky | Hz<br>30°<br>0.7dB<br>1 (IIP3)<br>mW<br>mm <sup>2</sup><br>y on SOI |

| Freq. Phase var. Gain Linearity  Power con. Circuit area            | $2.4/5.5 \mathrm{GHz}$ $360^{\circ}$ $4\mathrm{dB}$ $1\mathrm{dBm}$ (IIP3) $28.8 \mathrm{mW}$ $6mm^2$ $0.18 \mu\mathrm{m}$ CMOS forward- | 1GHz<br>180°<br>-1.2dB<br>45dBm<br>(IIP3)<br>~0mW<br>n.a.<br>Schottky<br>on SOI<br>lumped                      | 2.4/3.5/5.8G<br>180°<br>-6.6dB<br>n.a.<br>45mW<br>2.76mm <sup>2</sup><br>0.18µm<br>CMOS<br>lumped            | 3Hz 2G<br>18<br>-3±0<br>53dBm<br>~0n<br>6.38<br>Schottky | Hz<br>30°<br>0.7dB<br>n (IIP3)<br>mW<br>mm <sup>2</sup>             |

| Freq. Phase var. Gain Linearity  Power con. Circuit area Technology | 2.4/5.5GHz<br>360°<br>4dB<br>1dBm<br>(IIP3)<br>28.8mW<br>6mm <sup>2</sup><br>0.18μm<br>CMOS                                              | 1GHz<br>180°<br>-1.2dB<br>45dBm<br>(IIP3)<br>~0mW<br>n.a.<br>Schottky<br>on SOI<br>lumped<br>element           | 2.4/3.5/5.8G<br>180°<br>-6.6dB<br>n.a.<br>45mW<br>2.76mm <sup>2</sup><br>0.18μm<br>CMOS<br>lumped<br>element | 3Hz 2G<br>18<br>-3±0<br>53dBm<br>~0n<br>6.38<br>Schottky | Hz<br>30°<br>0.7dB<br>1 (IIP3)<br>mW<br>mm <sup>2</sup><br>y on SOI |

| Freq. Phase var. Gain Linearity  Power con. Circuit area Technology | $2.4/5.5 \mathrm{GHz}$ $360^{\circ}$ $4\mathrm{dB}$ $1\mathrm{dBm}$ (IIP3) $28.8 \mathrm{mW}$ $6mm^2$ $0.18 \mu\mathrm{m}$ CMOS forward- | 1GHz<br>180°<br>-1.2dB<br>45dBm<br>(IIP3)<br>~0mW<br>n.a.<br>Schottky<br>on SOI<br>lumped<br>element<br>trans- | $2.4/3.5/5.8G$ $180^{\circ}$ $-6.6dB$ $n.a.$ $45mW$ $2.76mm^{2}$ $0.18\mu m$ CMOS lumped element trans-      | 3Hz 2G<br>18<br>-3±0<br>53dBm<br>~0n<br>6.38<br>Schottky | Hz<br>30°<br>0.7dB<br>1 (IIP3)<br>mW<br>mm <sup>2</sup><br>y on SOI |

| Freq. Phase var. Gain Linearity  Power con. Circuit area Technology | $2.4/5.5 \mathrm{GHz}$ $360^{\circ}$ $4\mathrm{dB}$ $1\mathrm{dBm}$ (IIP3) $28.8 \mathrm{mW}$ $6mm^2$ $0.18 \mu\mathrm{m}$ CMOS forward- | 1GHz<br>180°<br>-1.2dB<br>45dBm<br>(IIP3)<br>~0mW<br>n.a.<br>Schottky<br>on SOI<br>lumped<br>element           | 2.4/3.5/5.8G<br>180°<br>-6.6dB<br>n.a.<br>45mW<br>2.76mm <sup>2</sup><br>0.18μm<br>CMOS<br>lumped<br>element | 3Hz 2G<br>18<br>-3±0<br>53dBm<br>~0n<br>6.38<br>Schottky | GHz GO° 0.7dB n (IIP3) mW mm² y on SOI                              |

Figure 2.12: Measured IM3(dBc) versus frequencies at three different tone-spacings (1MHz, 10MHz and 100MHz).

This phase shifter shows superior linearity performance.

#### 2.6 Conclusion

This Chapter presented a low-distortion phase shifter design based on transformers and low-loss varactor diodes. A very compact, low-power, differential phase shifter has been implemented, which shows a very high linearity of IIP3  $\geq$  52dBm. Limited phase variation can be overcome cascading additional phase shifter block without buffering circuits between phase shifters. Linearity analysis of the phase shifter is presented in the next Chapter. This makes it possible for this phase shifter to be applied to various demanding applications such as phased array transmitter systems.

This chapter, in part or in full, is a reprint of the material as it appears in the following publications:

- Sunghwan Kim, Jawad H. Qureshi, Koen Buisman, Lawrence E. Larson and Leo

C. N. de Vreede "Analysis of a Low-Distortion, Low-Loss Varactor Phase-Shifter

Based on Silicon-on-Glass Technology", submitted to *IEEE Transactions On Microwave Theory and Techniques*, 2010.

- Sunghwan Kim, Jawad H. Qureshi, Koen Buisman, Lawrence E. Larson and Leo

C. N. de Vreede, "A Low-Distortion, Low-Loss Varactor Phase-Shifter Based on

Silicon-on-Glass Technology", IEEE Radio Frequency integrated Circuits (RFIC)

Symposium, June 2008.