## Cost-effective Designs for Supporting Correct

## Execution and Scalable Performance in Many-core

### Processors

by

### Bogdan Florin Romanescu

Department of Electrical and Computer Engineering

Duke University

| Date:                    |

|--------------------------|

| Approved:                |

| Daniel J. Sorin, Advisor |

| Alvin R. Lebeck          |

| Christopher Dwyer        |

| Romit Roy Choudhury      |

| Landon Cox               |

Dissertation submitted in partial fulfillment of the requirements for the degree of Doctor of Philosophy in the Department of Electrical and Computer Engineering in the Graduate School of Duke University

### ABSTRACT

(Computer engineering)

## Cost-effective Designs for Supporting Correct Execution and Scalable Performance in Many-core Processors

by

### Bogdan Florin Romanescu

Department of Electrical and Computer Engineering Duke University

| Date | e:                       |

|------|--------------------------|

|      |                          |

|      | Approved:                |

|      |                          |

|      |                          |

|      | Daniel J. Sorin, Advisor |

|      |                          |

|      | Al ' D I d d             |

|      | Alvin R. Lebeck          |

|      |                          |

|      | Christopher Dwyer        |

|      | 1                        |

|      |                          |

|      | Romit Roy Choudhury      |

|      |                          |

|      |                          |

|      | Landon Cox               |

An abstract of a dissertation submitted in partial fulfillment of the requirements for the degree of Doctor of Philosophy in the Department of Electrical and Computer Engineering

in the Graduate School of Duke University 2010

## Abstract

Many-core processors offer new levels of on-chip performance by capitalizing on the increasing rate of device integration. Harnessing the full performance potential of these processors requires that hardware designers not only exploit the advantages, but also consider the problems introduced by the new architectures. Such challenges arise from both the processor's increased structural complexity and the reliability issues of the silicon substrate. In this thesis, we address these challenges in a framework that targets correct execution and performance on three coordinates: 1) tolerating permanent faults, 2) facilitating static and dynamic verification through precise specifications, and 3) designing scalable coherence protocols.

First, we propose CCA, a new design paradigm for increasing the processor's lifetime performance in the presence of permanent faults in cores. CCA chips rely on a reconfiguration mechanism that allows cores to replace faulty components with faultfree structures borrowed from neighboring cores. In contrast with existing solutions for handling hard faults that simply shut down cores, CCA aims to maximize the utilization of defect-free resources and increase the availability of on-chip cores. We implement three-core and four-core CCA chips and demonstrate that they offer a cumulative lifetime performance improvement of up to 65% for industry-representative utilization periods. In addition, we show that CCA benefits systems that employ modular redundancy to guarantee correct execution by increasing their availability.

Second, we target the correctness of the address translation system. Current

processors often exhibit design bugs in their translation systems, and we believe one cause for these faults is a lack of precise specifications describing the interactions between address translation and the rest of the memory system, especially memory consistency. We address this aspect by introducing a framework for specifying translation-aware consistency models. As part of this framework, we identify the critical role played by address translation in supporting correct memory consistency implementations. Consequently, we propose a set of invariants that characterizes address translation. Based on these invariants, we develop DVAT, a dynamic verification mechanism for address translation. We demonstrate that DVAT is efficient in detecting translation-related faults, including several that mimic design bugs reported in processor errata. By checking the correctness of the address translation system, DVAT supports dynamic verification of translation-aware memory consistency.

Finally, we address the scalability of translation coherence protocols. Current software-based solutions for maintaining translation coherence adversely impact performance and do not scale. We propose UNITD, a hardware coherence protocol that supports scalable performance and architectural decoupling. UNITD integrates translation coherence within the regular cache coherence protocol, such that TLBs participate in the cache coherence protocol similar to instruction or data caches. We evaluate snooping and directory UNITD coherence protocols on processors with up to 16 cores and demonstrate that UNITD reduces the performance penalty of translation coherence to almost zero.

To my grandparents

Bunicilor mei

# Contents

| A            | bstra | act                                                                                  | iv        |

|--------------|-------|--------------------------------------------------------------------------------------|-----------|

| Li           | st of | Tables                                                                               | xi        |

| Li           | st of | Figures                                                                              | xii       |

| Li           | st of | Abbreviations                                                                        | xv        |

| $\mathbf{A}$ | ckno  | wledgements                                                                          | xvi       |

| 1            | Intr  | roduction                                                                            | 1         |

|              | 1.1   | Processor Availability in the Presence of Hard Faults                                | 3         |

|              | 1.2   | Checking Correctness of Address Translation and Translation-Aware Memory Consistency | 5         |

|              | 1.3   | Scalable Translation Coherence Protocol Design                                       | 7         |

|              | 1.4   | Thesis Statement and Contributions                                                   | 9         |

|              | 1.5   | Thesis Structure                                                                     | 11        |

| 2            | _     | proving Lifetime Performance of Many-core Processors in the sence of Hard Faults     | <b>12</b> |

|              | 2.1   | Baseline System Model                                                                | 14        |

|              |       | 2.1.1 Core Model                                                                     | 14        |

|              |       | 2.1.2 Core Shutdown Design                                                           | 15        |

|              | 2.2   | CCA Concept                                                                          | 15        |

|              | 2.3   | CCA Design Decisions                                                                 | 17        |

|              | 2.4   | CCA Implementations                                                                  | 18        |

|   |     | 2.4.1   | Baseline CS and CCA Cores            | 19 |

|---|-----|---------|--------------------------------------|----|

|   |     | 2.4.2   | CCA3: 3-Core CCA Implementation      | 20 |

|   |     | 2.4.3   | CCA4: 4-Core CCA Implementations     | 22 |

|   |     | 2.4.4   | Many-core CCA Chips                  | 27 |

|   | 2.5 | Evalua  | ation                                | 27 |

|   |     | 2.5.1   | CCA Chip Area Overhead               | 28 |

|   |     | 2.5.2   | Lifetime Performance                 | 29 |

|   |     | 2.5.3   | Performance of Chips Using TMR/DMR   | 37 |

|   | 2.6 | Relate  | ed Work                              | 39 |

|   |     | 2.6.1   | Multicore-Specific Self-Repair       | 39 |

|   |     | 2.6.2   | Self-Repair for Superscalar Cores    | 39 |

|   |     | 2.6.3   | Pooling of Core Resources            | 40 |

|   |     | 2.6.4   | Lifetime Reliability                 | 40 |

|   | 2.7 | Concl   | usions                               | 40 |

| 3 | Add | dress T | Translation-Aware Memory Consistency | 42 |

|   | 3.1 | AT Fu   | indamentals and Assumptions          | 43 |

|   | 3.2 | Memo    | ory Consistency Levels               | 45 |

|   | 3.3 | Specif  | ying PAMC                            | 49 |

|   | 3.4 | Specif  | ying VAMC                            | 50 |

|   |     | 3.4.1   | Synonyms                             | 50 |

|   |     | 3.4.2   | Mapping and Permission Changes       | 52 |

|   |     | 3.4.3   | Load/Store Side Effects              | 53 |

|   | 3.5 | AT-av   | vare VAMC Specifications             | 54 |

|   | 3.6 | Comn    | nercial VAMC Models                  | 56 |

|   | 3 7 | Concl   | usions and Future Work               | 57 |

| 4 | Dyn | amica   | lly Verifying Address Translation                                            | 59 |

|---|-----|---------|------------------------------------------------------------------------------|----|

|   | 4.1 | AT Mo   | odel: $AT_{SC}$ , a Provably Sufficient Sequential AT Model                  | 60 |

|   | 4.2 | A Fran  | nework for Specifying AT Correctness                                         | 61 |

|   |     | 4.2.1   | Page Table Integrity                                                         | 62 |

|   |     | 4.2.2   | Translation Coherence                                                        | 63 |

|   | 4.3 |         | : Proposed Solution for Dynamic Verification of Address Trans-               | 65 |

|   |     | 4.3.1   | System Model                                                                 | 66 |

|   |     | 4.3.2   | $\mathrm{DVAT}_{SC}$ Overview                                                | 66 |

|   |     | 4.3.3   | Implementation Details                                                       | 69 |

|   | 4.4 | Evalua  | tion                                                                         | 70 |

|   |     | 4.4.1   | Methodology                                                                  | 71 |

|   |     | 4.4.2   | Error Detection Ability                                                      | 72 |

|   |     | 4.4.3   | Performance Impact                                                           | 74 |

|   |     | 4.4.4   | Hardware Cost                                                                | 76 |

|   | 4.5 | Relate  | d Work                                                                       | 76 |

|   | 4.6 | Conclu  | asions and Future Work                                                       | 78 |

| 5 | Uni | fied In | struction, Data and Translation Coherence Protocol                           | 80 |

|   | 5.1 | Existin | ng Solutions for Maintaining Address Translation Coherence                   | 81 |

|   |     | 5.1.1   | TLB Shootdown                                                                | 82 |

|   |     | 5.1.2   | Performance Impact of TLB Shootdown                                          | 84 |

|   | 5.2 | UNITI   | O Coherence                                                                  | 87 |

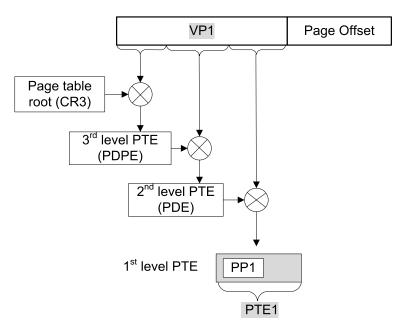

|   |     | 5.2.1   | Issue 1: Discovering the Physical Address of a Translation's PTE             | 88 |

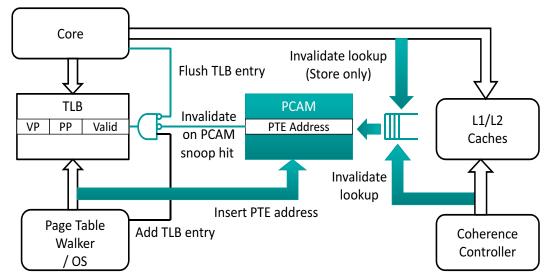

|   |     | 5.2.2   | Issue 2: Augmenting the TLBs to Enable Access Using a PTE's Physical Address | 91 |

|   | 5.3 | Platfor | rm-Specific Issues, Implementation Issues, and Optimizations                 | 94 |

| Bi | ogra  | phy    |                                         | 134 |

|----|-------|--------|-----------------------------------------|-----|

| Bi | bliog | graphy |                                         | 121 |

| 6  | Con   | clusio | ns                                      | 116 |

|    | 5.7   | Conclu | usions and Future Work                  | 113 |

|    | 5.6   | Relate | ed Work                                 | 112 |

|    | 5.5   | UNIT   | D Hardware Cost                         | 111 |

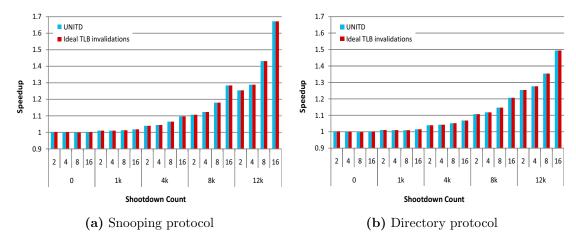

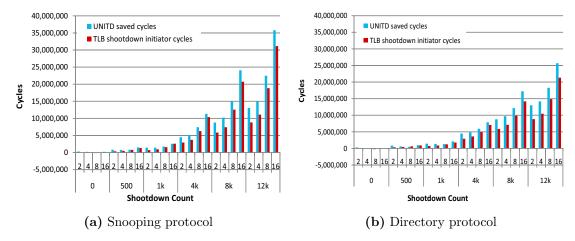

|    |       | 5.4.2  | Performance                             | 103 |

|    |       | 5.4.1  | Methodology                             | 100 |

|    | 5.4   | Exper  | imental Evaluation                      | 100 |

|    |       | 5.3.4  | Reducing TLB Coherence Lookups          | 100 |

|    |       | 5.3.3  | UNITD's Non-Impact on the System        | 97  |

|    |       | 5.3.2  | Handling PTEs in Data Cache and TLB     | 95  |

|    |       | 5.3.1  | Interactions with Speculative Execution | 94  |

# List of Tables

| 1.1 | Examples of Published Address Translation Design Bugs                                                                                                                                                                                                                          | 6   |

|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 2.1 | Number of Inputs/Outputs per Stage for OR1200                                                                                                                                                                                                                                  | 21  |

| 3.1 | SC PAMC. Loads and stores are to physical addresses. An X denotes an enforced ordering                                                                                                                                                                                         | 49  |

| 3.2 | Weak Order PAMC. Loads and stores are to physical addresses. Mem-Bar denotes a memory barrier. An X denotes an enforced ordering. An A denotes an ordering that is enforced if the operations are to the same physical address. Empty entries denote no ordering               | 49  |

| 3.3 | SC VAMC. Loads and stores are to synonym sets of virtual addresses. An X denotes an enforced ordering                                                                                                                                                                          | 55  |

| 3.4 | Weak Order VAMC. Loads and stores are to synonym sets of virtual addresses. MemBar denotes a memory barrier. An X denotes an enforced ordering. An A denotes an ordering that is enforced if the operations are to the same physical address. Empty entries denote no ordering | 55  |

|     |                                                                                                                                                                                                                                                                                |     |

| 3.5 | Address Translation in Commercial Architectures                                                                                                                                                                                                                                | 56  |

| 4.1 | Target System Parameters for $DVAT_{SC}$ Evaluation                                                                                                                                                                                                                            | 71  |

| 4.2 | Scientific Benchmarks for DVAT $_{SC}$ Evaluation                                                                                                                                                                                                                              | 72  |

| 5.1 | Target System Parameters for UNITD Evaluation                                                                                                                                                                                                                                  | 101 |

| 5.2 | Microbenchmarks for UNITD Evaluation                                                                                                                                                                                                                                           | 101 |

# List of Figures

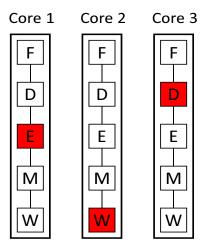

| 2.1  | 3-core CS Chip. Generic cores have five pipe stages: Fetch, Decode, Execute, Memory, and Writeback. Each core has one fault (Core 1 in the Execute stage, Core 2 in Writeback and Core 3 in Decode), rendering the chip useless | 15 |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

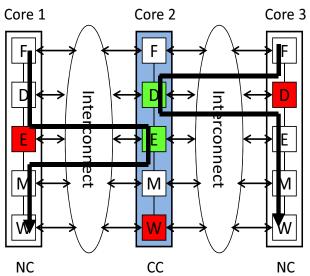

| 2.2  | 3-core CCA Chip. Cores 1 and 3 are NC, Core 2 is a CC. The 2 NCs are functional leading to a non-zero chip performance                                                                                                          | 16 |

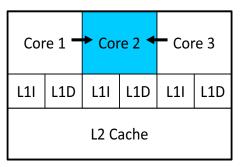

| 2.3  | CCA3(2/1) Chip. Cores 1 and 3 are NCs, Core 2 is a CC. Arrows indicate the CC that provides spare components for each NC                                                                                                        | 21 |

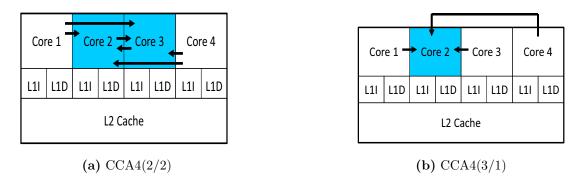

| 2.4  | CCA4 Chips. CCs are colored. Arrows indicate the CCs that provide spare components for each NC                                                                                                                                  | 23 |

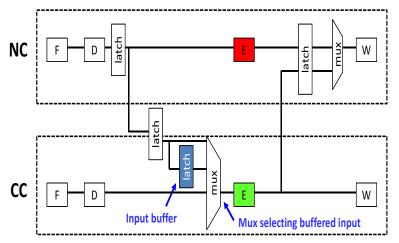

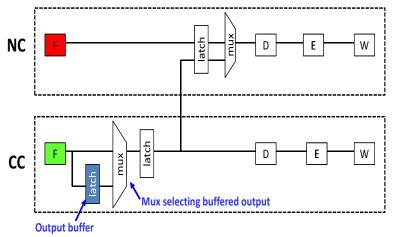

| 2.5  | Input Buffering for CC's Execute Stage                                                                                                                                                                                          | 26 |

| 2.6  | Output Buffering for CC's Fetch Stage                                                                                                                                                                                           | 27 |

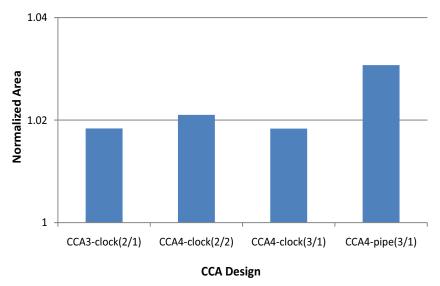

| 2.7  | CCA Designs Area Overhead. Results are normalized with respect to the areas of CS designs with the same number of cores                                                                                                         | 28 |

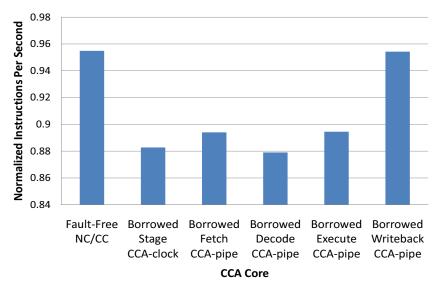

| 2.8  | Performance of CCA Cores                                                                                                                                                                                                        | 31 |

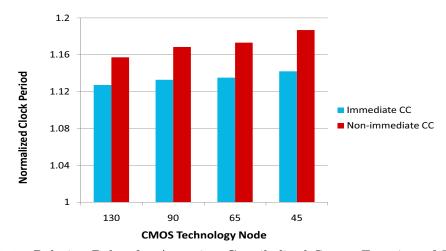

| 2.9  | Relative Delay for Accessing Cannibalized Stages Function of Technology Node. Results are normalized with respect to the clock periods of the baseline core for the corresponding technology                                    | 32 |

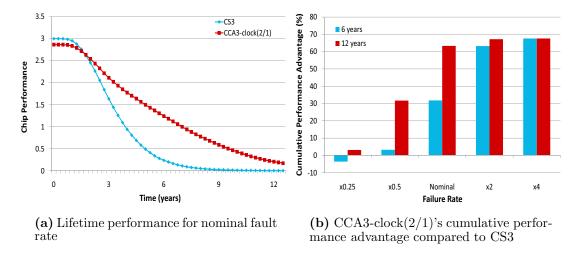

| 2.10 | Lifetime Performance of 3-core Chips                                                                                                                                                                                            | 33 |

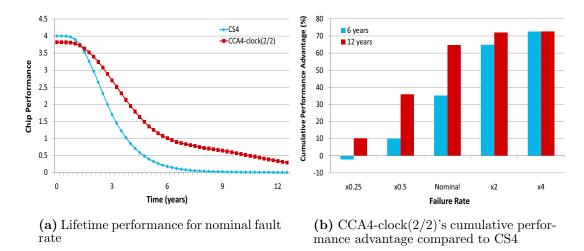

| 2.11 | Lifetime Performance of CCA4-clock(2/2) Chips                                                                                                                                                                                   | 34 |

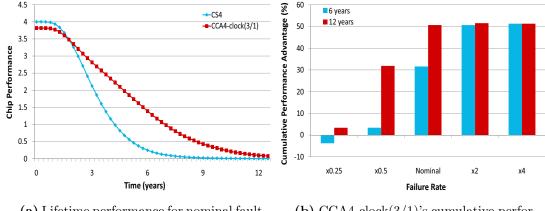

| 2.12 | Lifetime Performance of CCA4-clock(3/1) Chips                                                                                                                                                                                   | 35 |

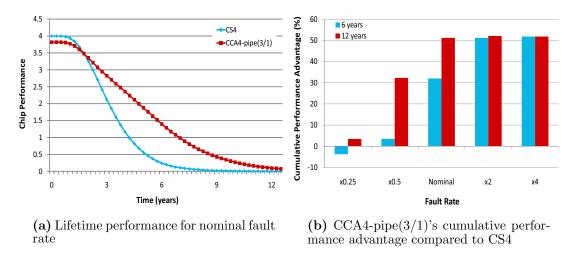

| 2.13 | Lifetime Performance of CCA4-pipe(3/1) Chips                                                                                                                                                                                    | 35 |

| 2.14 | Lifetime Performance of Equal-Area Chips                                                                                                                                                                                        | 36 |

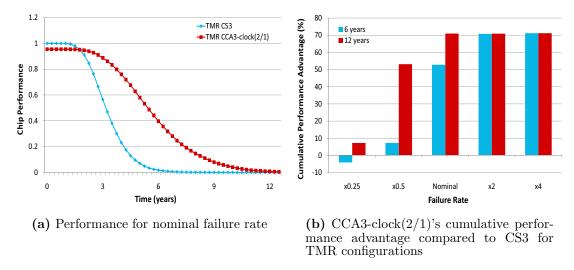

| 2.15 | Lifetime Performance of TMR Chips                                                                                                                                                                                                                      | 37  |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

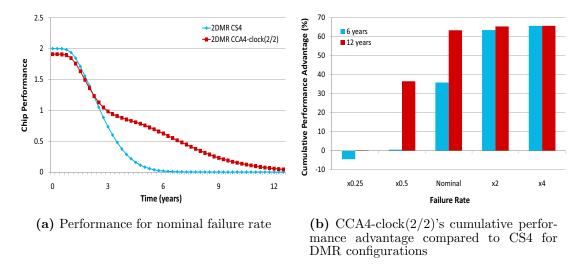

| 2.16 | Lifetime Performance of DMR Pair Chips                                                                                                                                                                                                                 | 38  |

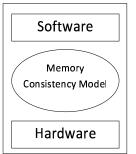

| 3.1  | Pseudo-code for a Generic MRF                                                                                                                                                                                                                          | 44  |

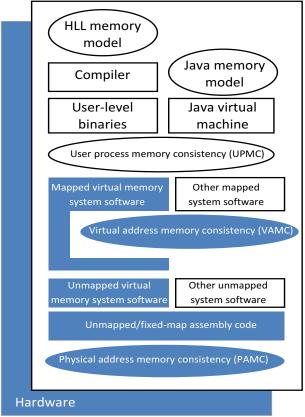

| 3.2  | Address Translation-Oblivious Memory Consistency                                                                                                                                                                                                       | 46  |

| 3.3  | Address Translation-Aware Memory Consistency. Shaded portions are the focus of this chapter                                                                                                                                                            |     |

| 3.4  | Example of Synonym Problem. Assume VAMC sequential consistency and that VA1 and VA2 map to PA1. Assume that PA1 is initially zero. A naive VAMC implementation incorrectly allows $(x,y)=(2,1)$                                                        | 51  |

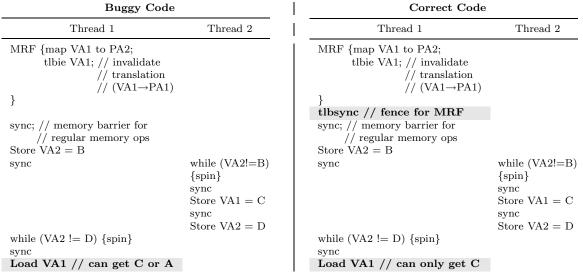

| 3.5  | Power ISA Code Snippets to Illustrate the Need to Consider MRF Ordering. Initially, VA1 is mapped to PA1, and the value of PA1 is A. Enforcing MRF serialization through <i>tlbsync</i> (right-hand side) eliminates result ambiguity (left-hand side) | 52  |

| 3.6  | Code Snippet to Illustrate the Need to Consider Load/Store Side Effects. If the two instructions are reordered, a Dirty bit set by the store could be missed and the page incorrectly not written back                                                 | 54  |

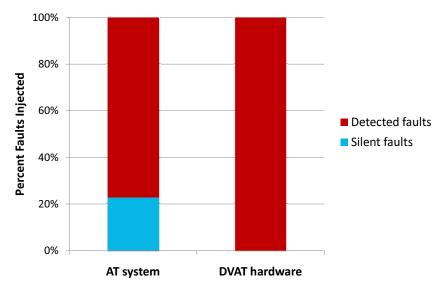

| 4.1  | $\mathrm{DVAT}_{SC}$ 's Fault Detection Efficiency                                                                                                                                                                                                     | 73  |

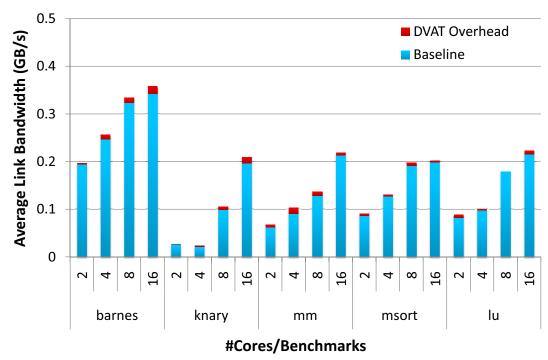

| 4.2  | $\mathrm{DVAT}_{SC}$ 's Bandwidth Overhead Compared to Baseline System                                                                                                                                                                                 | 74  |

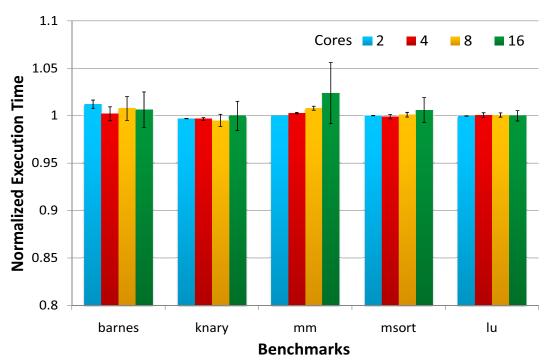

| 4.3  | $\mathrm{DVAT}_{SC}$ 's Performance Impact. Results are normalized to baseline system. Error bars represent standard deviation                                                                                                                         | 75  |

| 5.1  | TLB Shootdown Routines for Initiator and Victim Processors                                                                                                                                                                                             | 82  |

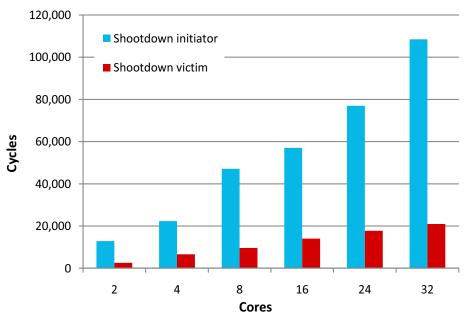

| 5.2  | Average TLB Shootdown Latency on Xeon Processors/Linux Platform.                                                                                                                                                                                       | 85  |

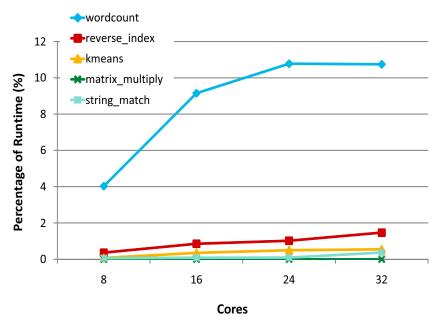

| 5.3  | TLB Shootdown Performance Overhead on Phoenix Benchmarks                                                                                                                                                                                               | 86  |

| 5.4  | 3-level Page Table Walk in IA-32. UNITD associates PTE1 with the VP1 $\rightarrow$ PP1 translation                                                                                                                                                     | 89  |

| 5.5  | PCAM's Integration with Core and Coherence Controller. UNITD introduced structures are colored                                                                                                                                                         | 92  |

| 5.6  | PCAM Operations. PA represents physical address                                                                                                                                                                                                        | 93  |

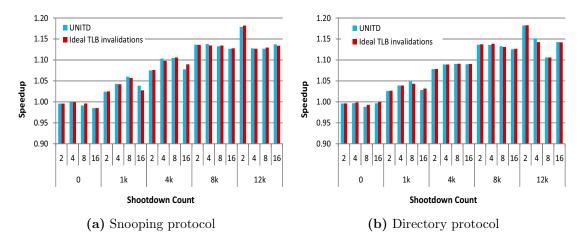

| 5.7  | UNITD Speedup Over Baseline System for Single_unmap Benchmark.                                                                                                                                                                                         | 104 |

| 5.8  | for Single_unmap Benchmark                                                                                                               | 105 |

|------|------------------------------------------------------------------------------------------------------------------------------------------|-----|

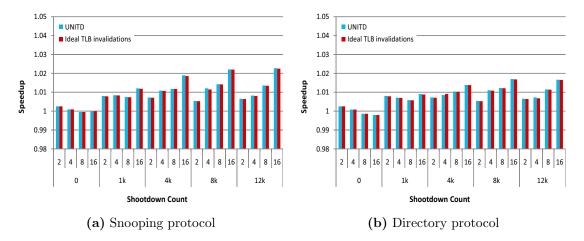

| 5.9  | UNITD Speedup Over Baseline System for Multiple_unmap Benchmark.                                                                         | 106 |

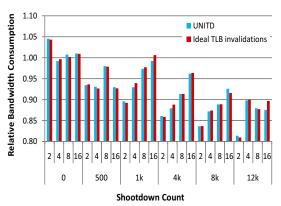

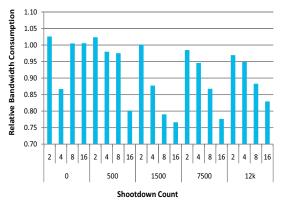

| 5.10 | UNITD Relative Bandwidth Consumption For Multiple_unmap Benchmark with Snooping Coherence. Results are normalized to the baseline system | 107 |

| 5.11 | UNITD Speedup Over Baseline System for Single_cow Benchmark                                                                              | 108 |

| 5.12 | UNITD Speedup Over Baseline System for Multiple_cow Benchmark.                                                                           | 109 |

| 5.13 | UNITD Relative Bandwidth Consumption for Multiple_cow Benchmark with Snooping Coherence. Results are normalized to the baseline system   | 109 |

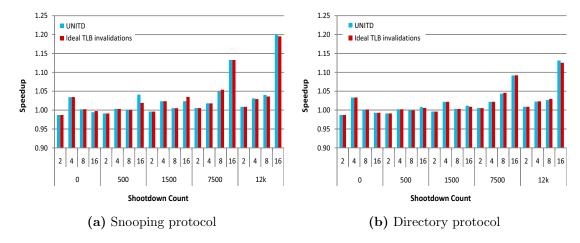

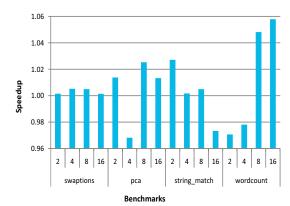

| 5.14 | UNITD Speedup on Real Benchmarks                                                                                                         | 110 |

| 5.15 | Percentage of TLB Coherence Lookups Filtered with a Simple JETTY Filter                                                                  | 111 |

## List of Abbreviations

AT Address translation

CC Cannibalizable core

CS Core shutdown

DMR Dual modular redundancy

MRF Map/remap function

NC Normal core

PTE Page table entry

TLB Translation lookaside buffer

TMR Triple modular redundancy

SC Sequential consistency

## Acknowledgements

First and foremost, I want to thank my parents for their support throughout my graduate studies.

My advisor, Prof. Daniel Sorin, has been a continuous source of motivation and mentoring. I learned from Dan the art of abstracting concepts, analyzing problems rigorously, and meaningful communication. I thank Dan for his patience and guidance in my development as a researcher. I am grateful to Prof. Alvy Lebeck for the decision to join our research, as his vast experience on architecture and systems proved invaluable.

I benefited from being part of a great computer architecture group at Duke. The reading group discussions helped me become a better critic and a sharper thinker. I was also fortunate to have two fantastic mentors during my summer internships, Jaidev Patwardhan and Anne Bracy. Both Jaidev and Anne showed me the importance of being a good mananger in addition to being a skillful engineer.

My student life would have certainly been duller if it weren't for my colleagues and friends. In particular, Vincent Mao has been a great office mate and I thank him for all the time spent discussing not just research. I am also grateful to Ionut Constandache for sharing memories and thoughts.

Finally, I am forever in debt to Prof. Călin Caşcaval from TU Iaşi for introducing me to research and supporting me in pursuing my graduate studies.

1

### Introduction

Architects look ahead to many-core designs as the next standard of cost-effective performance [53]. Leveraging the still increasing rate of on-die transistor integration, many-core processors are expected to feature hundreds to thousands of cores [24]. This order of magnitude increase in core count over existing processors offers tremendous performance opportunities, but also introduces new challenges for hardware designers [15]. Consequently, architects must address issues such as scalability, power-efficiency, and unreliability of the device substrate.

This thesis proposes architectural solutions for some of these problems that affect a processor's correct execution and performance. In particular, we focus on dependability and scalability issues. Dependability encompasses a vast area of topics, including reliability, maintanability, and security. We restrict our dependability approach to two aspects, availability and error detection. Thus, we address the challenges of many-core processors on three directions: 1) availability in the presence of permanent faults, 2) supporting error detection through precise specifications, and 3) designing scalable coherence protocols.

Availability characterizes a system's capacity to function properly at a specific

time, and is a function of the resources the system can provide to support correct execution. Availability is a primary concern for many-core processors given the increased impact of permanent hardware faults (*i.e.*, hard faults) and manufacturing defects for deep-submicron technologies [25]. Considering the increased density of on-chip transistor integration, these types of faults are expected to impact multiple processor resources. Designers must assume that such faults will occur during the processor's lifetime, and propose architectural solutions to maximize the available on-chip resources. In Section 1.1, we describe a case for increasing processor availability by tolerating hard faults in cores. We propose handling such faults through a reconfiguration mechanism that aggregates functional units from neighboring faulty cores. Our solution provides sustained availability and increases the processor's expected lifetime performance.

A fundamental prerequisite for our availability solution is the system's ability to detect incorrect execution in any of the processor's components. Incorrect execution can be caused by either hardware faults, or design faults which are introduced during the design process. Several efficient solutions exist for detecting faults in cores and parts of the memory system [16, 86, 89]. However, in Section 1.2, we identify address translation as one system for which no error detection solutions are currently available. One possible cause for this lack of error detection mechanisms is the absence of precise specifications of how the address translation system interacts with the rest of the memory system, and especially memory consistency. We address this lack of specifications by proposing a framework for specifying translation-aware consistency models. The critical role played by address translation in supporting memory consistency motivates us to propose a set of invariants that characterizes the address translation system. Based on these invariants, we develop a dynamic verification solution for address translation which facilitates the runtime verification of memory consistency.

The last part of the thesis addresses the issue of scalable performance, arguably one of the most critical aspects of many-core processors design. Integrating hundreds of cores on the same die requires scalable interconnects and inter-core communication mechanisms such as coherence protocols [15]. Although architects have proposed scalable solutions with respect to these components [96, 50, 8, 84], we identify translation coherence as one area that has been generally neglected. Software-based solutions for maintaining translation coherence are performance costly and non-scalable, and no alternatives are currently available. Section 1.3 argues that the time has come to move translation coherence into hardware. We propose one such solution by integrating translation coherence into the regular cache coherence protocol. We implement our solution on systems with both snooping and directory cache coherence protocols, and demonstrate that it reduces the performance penalty associated with translation coherence to almost zero.

Next, we discuss in detail the motivation for the three research directions of this thesis.

### 1.1 Processor Availability in the Presence of Hard Faults

Deep-submicron technologies are characterized by an increased likelihood of hard faults [42, 120]. Smaller transistors and wires are more susceptible to permanent faults. For pre-90nm technologies, the degradation caused by such faults was small enough to be accounted for in the component's testing margin such that it would not affect the device functionality [25]. However, Srinivasan et al. [120] demonstrated that there is a sharp decrease in reliability beyond 90nm due to physical wearout induced by time-dependent dielectric breakdown, electromigration, and stress migration. Furthermore, as we continue to add more transistors and wires, there are more opportunities for hard faults to occur either during fabrication or in the field [25].

Although current chips already incorporate mechanisms for addressing hard faults,

most of them target SRAM structures. This is a consequence of the memory cells being more prone to faults than regular logic for pre-90nm technologies [52]. Such solutions for tolerating hard faults in memory structures include error correcting codes and provisioning spare rows/columns [77, 26]. The spare components can be used to replace or remap few memory blocks transparently to the software such that processor's performance is virtually unaffected.

In contrast, processors have few, if any, solutions for tolerating hard faults in cores. The most common method of handling such faults is to disable either the affected component or the entire core. The former requires however that the faulty component can be precisely identified, and that the core contains replicas of the unit. The latter condition is difficult to satisfy even by superscalar cores as few structures are replicated within the core [97]. Consequently, chip designers prefer disabling the entire core, a technique that is prevalently used by industry to increase the chip's manufacturing yield. For example, IBM markets Cell processors for Sony Playstations with just 7 out of 8 functional SPEs [80].

The main drawback of disabling cores is that it reduces the availability of on-chip resources, leading to decreased overall processor performance. Thus, highly-available systems rely instead on spare cores for delivering performance in the presence of hard faults [17]. Unfortunately, spare components (either cold or hot) [10, 117] consume hardware resources that provide no performance benefit during fault-free operation. If we provision spares for all components, then we achieve approximately half the fault-free performance of an equal-area chip without spares. The sparing cost increases for systems that must tolerate multiple hard faults such as triple modular redundant (TMR) systems [68].

In this thesis, we address the inefficiencies of current solutions in providing costeffective availability in the presence of hard faults in cores by proposing the Core Cannibalization Architecture (CCA). The CCA concept builds on the observation that despite multiple hard faults in cores, a chip provides enough fault-free resources that can be aggregated to yield functional cores. In Chapter 2, we propose and evaluate various CCA designs that reuse components at the granularity of pipeline stages. We demonstrate that CCA significantly improves lifetime chip performance compared to processors that rely on disabling cores. In addition, CCA can be combined with solutions using redundant cores for increased processor availability.

### 1.2 Checking Correctness of Address Translation and Translation-Aware Memory Consistency

In addition to permanent faults, many-core processors face dependability concerns due to transient faults and design faults [42, 25]. Similar to permanent faults, transients are a consequence of the smaller transistor sizes which render chips more susceptible to faults caused by neutrons and alpha particles [42]. In contrast, design faults represent human errors, and are "facilitated" by increased design complexities, reduced testing time and imperfect coverage of random testing [66]. Despite different causes, both types of faults have the same effect on a circuit, resulting in incorrect behavior.

One of the systems that is currently vulnerable to these faults is address translation (AT). Representative of AT's vulnerability is the disproportionate fraction of published bugs in shipped processors [2, 3, 4, 59, 61, 62, 63] that involve AT hardware, including the infamous TLB coherence bug in AMD's quad-core Barcelona processor [131]. Table 1.1 lists a few examples of these bugs.

We believe that one of the underlying causes for AT's reliability problems is the designers' tendency to over-simplify memory consistency and to neglect AT's impact on consistency models. Current specifications do not provide a precise description of the interactions between AT and the rest of the memory system. Such clear specifications of correctness are a fundamental prerequisite for detecting incorrect

Table 1.1: Examples of Published Address Translation Design Bugs.

| Processor                    | Design Bug                                                                                                                                  | Effect                                                            |

|------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------|

| AMD Athlon64/<br>Opteron [2] | TLB flush filter may cause coherency problem in multicore systems                                                                           | Unpredictable system failure (possible use of stale translations) |

| AMD Athlon64/<br>Opteron [2] | INVLPG instruction with address prefix does not correctly invalidate the translation requested                                              | Unpredictable system<br>behavior (use of stale<br>translation)    |

| Intel Core Duo [62]          | One core is updating a page ta-<br>ble entry while the other core is<br>using the same translation entry<br>may lead to unexpected behavior | Unexpected processor<br>behavior                                  |

| Intel Core Duo [62]          | Updating a PTE by changing R/W, U/S or P bits without TLB shootdown may cause unexpected processor behavior                                 | Unexpected processor<br>behavior                                  |

#### behavior.

In Chapter 3, we propose a framework for precise, implementation-independent specification of AT-aware memory consistency. We discuss in depth the memory consistency levels that closely interact with the AT system. We identify one particular level that requires AT support and analyze the AT aspects that affect the consistency specifications at this level.

Our framework benefits both hardware designers and programmers. Precisely specifying the interactions between AT and the memory system reduces the probability of designers introducing design faults at this interface. Second of all, our specifications help system programmers in writing software that involves AT by clearly stating the requirements for correct execution. Finally, the proposed framework facilitates static verification and allows architects to develop checkers for runtime verification of address translation.

The important role that AT plays in supporting some levels of memory consistency implies that a correct AT system is required for correct memory consistency implementations. To facilitate checking AT correctness, we propose a framework

for AT specifications (Chapter 4). Based on this framework, we create DVAT, an efficient dynamic verification scheme for AT coherence that can detect errors due to design bugs and runtime faults. We demonstrate that DVAT detects design bugs similar to the ones reported in processor errata, and supports comprehensive dynamic verification of memory consistency.

#### 1.3 Scalable Translation Coherence Protocol Design

Our analysis of the AT system reveals that maintaining translation coherence has a significant performance cost even for systems with few cores. Translation caches are just one of multiple types of caches that shared memory processors or multiprocessor systems must maintain coherent, including instruction and data caches. While instruction and data cache coherence has been the focus of extensive research on scalable coherence protocols [96, 50, 8, 1, 84, 9], few solutions have been proposed for scalable translation coherence [125]. Designing a scalable protocol for translation coherence requires us to first understand what essentially differentiates translation coherence from instruction/data coherence.

For caches that hold instructions or data, coherence is almost generally maintained with an all-hardware cache coherence protocol. Hardware controllers at the caches coordinate amongst themselves using snooping or directories to ensure that instructions and data are kept coherent, and this coherence is not software-visible. However, for caches that hold address translations (*i.e.*, TLBs), coherence is almost always maintained by an OS-managed software coherence protocol. Even for architectures with hardware control of TLB fills and evictions, when an event occurs that affects the coherence of TLB entries (*e.g.*, eviction of a page of virtual memory), the OS ensures translation coherence through a software routine called TLB shootdown [19].

Performing cache coherence in hardware provides two major advantages: per-

formance and microarchitectural decoupling. Performance-wise, hardware is much faster than software. For coherence, this performance advantage grows as a function of the number of caches. Although using software for local activities (e.g., TLB fills and replacements) might have acceptable performance, even some architectures that have traditionally relied on software for such operations (e.g., SPARC) are now transitioning to hardware support for increased performance [95]. In contrast, activities with global coordination are painfully slow when performed in software. For example, Laudon [75] mentions that for a page migration on the SGI Origin multiprocessor, the software routine for TLB shootdown is three times more time-consuming than the actual page move. The second reason for performing cache coherence in hardware is to create a high-level architecture that can support a variety of microarchitectures. A less hardware-constrained OS can easily accommodate heterogeneous cores as it does not have to be aware of each core's particularities [71]. Furthermore, hardware coherence enables migrating execution state between cores for performance, thermal, or reliability purposes [34, 51] without software knowledge.

Given that hardware seems to be an appropriate choice for cache coherence, why has TLB coherence remained architecturally visible and under the control of software? We believe that one reason architects have not explored hardware TLB coherence is that they already have a well-established mechanism that is not too costly for systems with a small number of processors. For previous multiprocessor systems, Black [19] explains that the low overhead of maintaining TLB coherence in software on current machines may not justify a complete hardware implementation. As we show in the Section 5.1.2, this conclusion is likely to change for future many-core chips.

This motivates us to consider a hardware approach for translation coherence. A hardware TLB coherence protocol provides three primary benefits. First, it drastically reduces the performance impact of TLB coherence. While this performance

benefit is worthwhile on its own, it also lowers the threshold for adopting features that incur a significant amount of TLB coherence activity, including: hardware transactional memory (e.g., XTM [40]), user-level memory management for debugging [43], and concurrent garbage collection [39]. Second, hardware TLB coherence provides a cleaner interface between the architecture and the OS, which could help to reduce the likelihood of bugs at this interface, such as the recent TLB coherence bug in the AMD Barcelona chip [131]. Third, by decoupling translation coherence from the OS, hardware TLB coherence can be used to support designs that use TLBs in non-processor components such as network cards or processing elements [82, 102]. This might facilitate a globally-shared address space among all components of a computing system.

Considering these advantages, in Chapter 5 we propose UNITD, a hardware coherence protocol that integrates translation coherence within the regular cache coherence protocol. UNITD "snoops" TLBs on regular coherence requests, such that any change to the page tables automatically triggers TLB coherence. Relying on small additional hardware, UNITD successfully eliminates the performance cost associated with the TLB shootdowns routines. In addition, UNITD does not affect the complexity or performance of the regular cache coherence protocol.

#### 1.4 Thesis Statement and Contributions

The imminent adoption of many-core processors as the next computing standard will make these designs ubiquitous in our daily lives. Such processors will have to support a wide variety of applications, ranging from systems that require correct execution above all, to applications that demand performance. This observation motivates the following thesis statement:

The characteristics of many-core processors enable the design of cost-effective solutions for supporting correct execution and performance, given the reliability and

scalability challenges of these processors.

To support this statement, this thesis makes the following contributions in the context of many-core processors:

- Proposes a solution to improve processor's lifetime performance in the presence of hard faults. The dissertation introduces a low-cost and efficient self-repair mechanism for many-core processors with simple cores by enabling sharing of resources. The reconfiguration solution provides sustained performance and availability, that outweigh the slight performance overhead in fault-free scenarios over the processor's lifetime.

- Develops a framework for specifying address translation-aware memory consistency models. The framework analyzes the consistency levels that closely interact with the address translation system, and identifies the translation-related aspects that impact consistency models. Providing a thorough, multi-level specification of consistency enables programmers, designers, and design verifiers to more easily reason about the memory system's correctness.

- Proposes a dynamic verification scheme for address translation. We support the dynamic verification solution with an implementation-independent framework for specifying address translation. In addition to checking the correctness of the address translation system, the proposed mechanism facilitates comprehensive verification of memory consistency.

- Introduces a hardware coherence protocol for translation coherence.

The proposed protocol integrates translation coherence into the existing cache coherence protocol, with TLBs participating in the protocol like instruction or data caches. Our hardware coherence protocol provides scalable performance

compared to existing software-based solutions for maintaining translation coherence.

#### 1.5 Thesis Structure

Chapter 2 describes CCA, our solution for improving the lifetime performance of many-core processors in the presence of hard faults. Chapter 3 introduces the framework for specifying translation-aware consistency models, and analyzes the impact of address translation on virtual address memory consistency. Chapter 4 proposes a framework for specifying address translation and details DVAT, a dynamic verification mechanism for checking the correctness of the address translation system. Chapter 5 describes UNITD coherence, a unified hardware coherence framework that integrates instruction, data and translation coherence in the same coherence protocol. Finally, Chapter 6 summarizes the thesis' contributions.

## Improving Lifetime Performance of Many-core Processors in the Presence of Hard Faults

Technology trends are leading to an increasing likelihood of hard (permanent) faults in processors [120]. Traditional approaches to this problem include provisioning spare components or simply disabling cores. Unfortunately, spare components (either cold or hot) consume hardware resources that provide no performance benefit during fault-free operation. If we provision spares for all components, then we achieve approximately half the fault-free performance of an equal-area chip without spares. In turn, core shutdown (CS) disables an entire core if any of its components has a hard fault and thus wastes much fault-free circuitry.

Motivated by the deficiencies of existing solutions, our goal is to tolerate hard faults in many-core processors without sacrificing hardware for dedicated spare components. There are two aspects to many-core processors that distinguish the issue of self-repair from the case for single-core processors. First, power and thermal constraints motivate the use of simple, in-order cores, perhaps in conjunction with one or two superscalar cores. Examples of chips with simple, narrow cores include the UltraSPARC T1 [70] and T2 [112], Cray MTA [31], empowerTel MXP processor [54],

Renesas SH-2A-Dual [122], and Cisco Silicon Packet Processor [41], and we expect this trend to continue for many-core processors. Unfortunately, simple cores have little intra-core redundancy of the kind that has been leveraged by superscalar cores to provide self-repair [27, 113, 119]. Just one hard fault in the lone ALU or instruction decoder renders a simple core useless, even if the entire rest of the core is fault-free. The second aspect of self-repair that is distinct to many-core processors is the opportunity to use resources from fault-free cores.

We propose the Core Cannibalization Architecture (CCA), the first design of a low-cost and efficient self-repair mechanism for many-core processors with simple cores. The key idea is that one or more cores can be cannibalized for spare parts, where parts are considered to be pipeline stages. The ability to use stages from other cores introduces some slight performance overhead, but this overhead is outweighed by the improvement in lifetime chip performance in the presence of multiple hard faults. Furthermore, CCA provides an even larger benefit for many-core chips that use cores in a triple modular redundancy (TMR) or dual modular redundancy (DMR) configuration, such as Aggarwal et al.'s approach [10]. CCA enables more cores to be operational, which is crucial for supporting TMR or DMR.

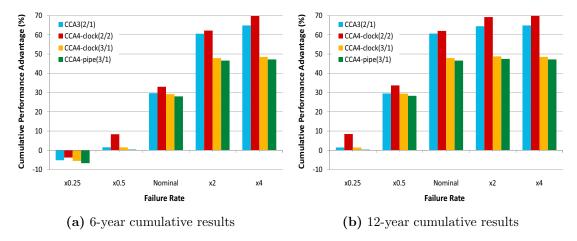

We develop several concrete implementations of CCA in the context of processors that consist of up to four simple OpenRISC 1200 cores [74]. We also present a straightforward extension of these designs to many-core processors. We show that CCA achieves better performance than CS over the chip's lifetime. After only 2 years, CCA chips outperform CS chips. Over a lifetime of 12 years, CCA achieves a 63% improvement in cumulative performance for 3-core chips and a 64% improvement for 4-core chips. Furthermore, if cores are used redundantly (e.g., TMR or DMR), then CCA's improvement is 70% for 3-core chips and 63% for 4-core chips.

In this chapter, after describing the baseline system model (Section 2.1), we detail the CCA concept (Section 2.2) and discuss design-related aspects (Section 2.3). We describe our CCA implementations in Section 2.4. We then evaluate CCA (Section 2.5) and compare it to prior research (Section 2.6). Finally, we draw conclusions in Section 2.7.

#### 2.1 Baseline System Model

In this section, we present our core model and discuss core shutdown, the natural design point against which we compare.

#### 2.1.1 Core Model

In our analysis we focus on simple, in-order cores with little redundancy. We present CCA in the context of 1-wide (scalar) cores, but CCA also applies to many cores that are wider but still have numerous single points of failure. There are many k-wide cores that cannot tolerate a fault by treating the core as being k-1-wide. For example, the Renesas SH-2A [122] is dual-issue, but it has only one shifter and one load/store unit. Any fault in either of those units renders the entire core unusable. Other simple cores are susceptible to numerous single faults (e.g., in the PC update logic) that affect all lanes of the processor. Many commercial cores fit our core model [70, 112, 31, 41]. In addition, Powell et al. [97] show that non-redundant structures represent the vast majority of core area even for superscalar cores.

Our model assumes that the core has mechanisms for detecting errors and diagnosing hard faults (i.e., identifying the locations of hard faults). Detection and diagnosis are orthogonal issues to self-repair, and acceptable schemes already exist, such as the built-in self-test (BIST) used by the BulletProof pipeline [114]. CCA may require additional BIST test vectors than a baseline system to distinguish faults that are in different pipeline stages and that would otherwise be exercised by the same test vector. CCA can also rely on software-based diagnosis solutions such as the ones proposed by Hari et al. [110], which eliminate the need for additional test

**Figure 2.1:** 3-core CS Chip. Generic cores have five pipe stages: Fetch, Decode, Execute, Memory, and Writeback. Each core has one fault (Core 1 in the Execute stage, Core 2 in Writeback and Core 3 in Decode), rendering the chip useless.

vectors.

#### 2.1.2 Core Shutdown Design

As mentioned in the chapter's introduction, a multicore processor with C simple cores can tolerate hard faults in F (F < C) distinct cores by simply not using the faulty cores. A single fault in a core renders the entire core useless. Additional faults in the same core (e.g., multiple faults can occur during the manufacturing process) do not matter, since the core has already been shut off. The performance of a chip with CS is proportional to the number of fault-free cores, C-F. Figure 2.1 illustrates a 3-core processor with core shutdown. In the presence of three hard faults, one in each core, the processor achieves zero performance because none of its cores are operable.

### 2.2 CCA Concept

The CCA concept is based on the tight integration of the neighboring cores in a many-core processor. The key idea is that cores can be cannibalized for spare parts by on-die adjacent cores to replace their own defective components, and thus become

**Figure 2.2:** 3-core CCA Chip. Cores 1 and 3 are NC, Core 2 is a CC. The 2 NCs are functional leading to a non-zero chip performance.

fault-free. Thus, a CCA system consists of a number of normal cores (NCs) that cannot be cannibalized as well as some number of cannibalizable cores (CCs). We use the notation CCAX(Y/Z) to refer to a CCA chip with a total of X cores, out of which Y are NCs and Z are CCs, where X=Y+Z. Similarly, we use the notation CSX to refer to a CS chip with X cores.

At a high level, a CCA processor resembles the system in Figure 2.2. The figure illustrates a CCA system with three cores, where Core 2 is a CC. CCA enables Core 1 to overcome a faulty Execute stage and Core 3 to overcome a faulty Decode stage, by cannibalizing these stages from Core 2. The cannibalization process is facilitated by a dedicated interconnect. The result is that, despite the presence of three hard faults (including the fault in Core 2's Writeback stage), Core 1 and Core 3 continue to function correctly.

The performance of both cores is somewhat degraded, though, because of the delay in routing to and from the cannibalized stages. However, comparing the chips in Figures 2.1 and 2.2, which both have three faults, we see that CS offers zero performance, yet CCA provides the performance of two slightly degraded cores.

In general, as the number of faults increases, CCA outperforms CS. For chips with zero or very few faults that do not allow CCA-type reconfigurations, a processor with CS outperforms CCA because CCA's reconfigurability logic introduces some performance overhead into the cores. This performance overhead is similar to that incurred by schemes that provide spare components. However, as the number of faults increases, CCA can tolerate more of them and provide a graceful performance degradation. We demonstrate in Section 2.5 that over the chip's lifetime, the expected performance of CCA chips exceeds the expected performance of CS chips.

#### 2.3 CCA Design Decisions

There are three important issues involved in a CCA design: the granularity at which to cannibalize cores, the sharing policy between CCs and NCs, and the assignment of the chip's cores to be either an NC or a CC. After analyzing the first two issues, spare granularity and sharing policy, we make fixed decisions for both of them. For the third issue, chip layout, we explore several options.

Spare Granularity. We cannibalize cores at the granularity of pipeline stages. The coarsest possible granularity is spare cores (i.e., CS), but coarse granularity implies that a single fault in a core renders the entire core useless. Finer granularity avoids wasting as much fault-free hardware, but it complicates the design, especially the routing to and from spare components. For example, one recent scheme for fine-grain redundancy [93] has an area overhead that is greater than 2x. We choose a granularity of pipeline stages because it offers a good balance between complexity and performance. Our choice is confirmed by Gupta et al. [48] that, in a concept similar to CCA, determined that providing spares at pipeline stages granularity offers the most cost-effective performance.

**Sharing Policy.** Another issue to resolve is whether to allow multiple cores to simultaneously share a given component (*i.e.*, pipeline stage for our implementation).

There are three options. First, at one extreme, a core with a faulty component of type Z "borrows" (time multiplexes) a component of type Z from a neighboring core that continues to function (*i.e.*, is not cannibalized). A second option is to allow multiple cores to time multiplex a single cannibalized component. Both of these first two options introduce resource contention, require arbitration logic, and complicate pipeline control logic. For these reasons, we choose a third option, in which any given component can only be used by a single core.

Chip Layout. Categorizing the chip's cores into CCs and NCs is crucial for the increased performance of the CCA chip. There are two aspects that influence CCA's performance given a fixed core count. The first is the number of cores that are CCs. Underprovisioning CCs leaves NCs without spare components, while overprovisioning CCs can lead to wasteful allocation of resources, as the interconnection required for providing access to CCs increases in complexity and size. The second aspect is the arrangement of NCs and CCs such that we minimize the distance between NC stages and potential CC spare stages. We must carefully balance the two aspects in order to provide the best area-performance tradeoff. Consequently, we implement several CCA designs based on different CCs-NCs configurations and compare them in terms of performance and cost.

#### 2.4 CCA Implementations

In this section, we first describe the cores used in our CS and CCA chips (Section 2.4.1). We then describe two concrete CCA implementations, with three cores (Section 2.4.2) and four cores (Section 2.4.3), respectively. Based on these designs, we discuss how to extend CCA to chips with greater numbers of cores (Section 2.4.4).

A fundamental aspect in any CCA implementation is the latency of the interconnect required for cannibalizing components. The characteristics of this interconnect are a function of low-level issues such as chip layout and wire delay. Therefore, a proper evaluation of CCA requires us to implement the designs at a low level detail. We construct Verilog models for all designs we evaluate, including systems with and without CCA. To evaluate area and delays, we floorplan and layout chips using Synopsys Design Compiler [123] and Cadence Silicon Ensemble [28]. We use a proprietary TSMC 90nm standard cell library for the synthesis flow. Unfortunately, the library does not include memory cells, and using regular flip-flops in synthesis creates unrealistically large RAM structures and diminishes the impact of our changes. In order to provide a fair evaluation, we estimate the size of the memory structures using CACTI [92].

#### 2.4.1 Baseline CS and CCA Cores

The core of the baseline CS processor is the OpenRISC 1200 (OR1200) [74]. The OR1200 core is a scalar, in-order, 32-bit core with 4 pipeline stages: Fetch, Decode, Execute, and Writeback. Each core has 32 registers and separate instruction and data L1 caches (I-cache and D-cache). Implemented in our 90nm technology, we can clock the core at a maximum frequency of roughly 400MHz.

The analysis of CCA cores is impacted by the implications of stage borrowing. An NC's use of a cannibalized CC's stage introduces issues that are specific to that particular stage, so we discuss next the cannibalization of each stage.

**Fetch.** The Fetch stage involves I-cache accesses. If an NC uses a CC's Fetch stage, it also uses the CC's I-cache instead of its own cache.

**Decode.** The Decode stage is responsible for instruction decoding, accessing the register file and determining the destination address for jump/branch instructions. A particularity of this stage is the branch destination (BD) block. The OR1200 core has a one-instruction delay slot for branches and jumps, and the BD block is responsible for computing the address during the delay slot and communicating the destination to the Fetch stage. This block is tightly coupled with the Fetch stage

while operating independently from the rest of the decode logic. Therefore, due to this tight coupling, we consider the BD block as part of the Fetch stage. An NC that reuses the Fetch stage of a CC also reuses the CC's BD block. In addition to the BD block, the Decode stage includes the register file such that an NC that uses a CC's Decode stage also uses that CC's register file. In this case, the NC must route back to the CC's register file during Writeback.

**Execute.** The Execute stage is where computations occur and where loads and stores access the D-cache. An NC that uses a CC's Execute stage also uses that CC's D-cache; the NC no longer uses its own D-cache.

Writeback. CCA does not require modifications for the Writeback logic, but it motivates a small change for register writing. Because the register writing logic is extremely small, it is preferable, in terms of area and performance, to simply replicate it (as a cold spare) in the original Writeback stage. Intuitively, forcing an NC to go to a CC for a tiny piece of logic is not efficient. If replication is not possible due to possible area constraints, this logic can be considered to be a component of the Decode stage.

#### 2.4.2 CCA3: 3-Core CCA Implementation

We first consider a 3-core chip that we refer to as CCA3(2/1): 2 cores are NCs and 1 is CC. Our CCA3(2/1) implementation arranges the cores as shown in Figure 2.3, and we designate only the middle core, Core 2, as a CC. By aligning the cores in the same orientation, we facilitate routing from an NC to a CC. By provisioning one CC, we obtain better chip performance than if we had implemented CCA3(1/2), which would have 1 NC and 2 CCs. With more than one CC, the fault-free performance of each core decreases, due to added wires and multiplexing, and the ability to tolerate more faults does not increase much.

If a single fault occurs in either Core 1 or Core 3, it is preferable to just not

**Figure 2.3:** CCA3(2/1) Chip. Cores 1 and 3 are NCs, Core 2 is a CC. Arrows indicate the CC that provides spare components for each NC.

Table 2.1: Number of Inputs/Outputs per Stage for OR1200.

| Stage     | # Input signals | # Output signals |

|-----------|-----------------|------------------|

| Fetch     | 56              | 65               |

| Decode    | 38              | 115              |

| Execute   | 110             | 61               |

| Writeback | 87              | 52               |

use that core, rather than cannibalize Core 2. Not using a core leads to a total chip performance of an NC and a CC combined, while borrowing a stage yields a chip performance of an NC and a borrowing NC. As we show in Section 2.5.2, the performance of an NC borrowing a stage is always lower than a fault-free CCA core, which is why we favor not using the faulty core.

CCA3(2/1)'s reconfigurability requires some extra hardware and wires, similar to the overhead required to be able to use spare components. Each NC (Core 1 and Core 3) has multiplexors (muxes) at the input to each stage that allow it to choose between signals from its own other stages (the majority of which are from the immediate predecessor stage) and those from the CC (Core 2). Similarly, Core 2 has multiplexors at the input to each stage that allow it to choose between signals from its other stages and signals from the two NCs. Table 2.1 shows the number of wires that are the inputs and outputs of each stage.

In CCA3(2/1)'s chip layout, the distance to route from Core 1 or Core 3 to Core

2 and back is short. The cores are small, and the distance each way is approximately 1mm in 90nm technology. Furthermore, because these simple cores are designed for power efficiency rather than for maximum clock frequency, we do not expect them to be clocked aggressively. Thus, given a clock frequency in the 400 MHz range and such short wires, the penalty of routing to and from a cannibalized stage is a relatively small fraction of the clock period (as we show in Section 2.5.2). Rather than add wire delay pipe stages to avoid lengthening the clock period (which we consider for our 4-core implementations in Section 2.4.3), we simply slow the clock slightly. For chips with larger cores, adding wire delay pipe stages may be preferable.

One way to mitigate the impact of lengthening the clock period is to use clock borrowing [129]. Consider a fault in Core 1. If Core 1's normal clock period is T and its extra wire delay to and from Core 2 is W (for our CCA chips W is twice the distance to access a spare component), then a simplistic solution is to increase Core 1's clock period to T'=T+W. Clock borrowing can mitigate this performance impact by amortizing time sharing W across the two neighboring stages [129]. By sharing this delay, we can reduce the clock period penalty to 1/3 of W, i.e., T'=T+W/3. As a concrete example, if Core 1 has a 50ns clock period (T=50ns) when fault-free and W=15ns, then we can use time borrowing to achieve a clock cycle of T'=55ns. We borrow 5ns from both of the neighboring stages, pushing them from 50ns to 55ns. Thus, we have 65ns-10ns=55ns for the longer stage.

#### 2.4.3 CCA4: 4-Core CCA Implementations

For the 4-core CCA chips we consider two viable CCA4 arrangements as illustrated in Figure 2.4. CCA4(3/1) chips are natural extensions of the CCA3(2/1) chip. In addition, we also propose the CCA4(2/2) configuration, which has two cannibalizable cores, and differs from CCA4(3/1) in how CCs share stages. In CCA4(2/2) Core 1 can use a stage from Core 2 or Core 3, Core 2 and Core 3 can use stages from each

**Figure 2.4:** CCA4 Chips. CCs are colored. Arrows indicate the CCs that provide spare components for each NC.

other, and Core 4 can use a stage from Core 3 or Core 2. This sharing policy allows CCs to share with each other, and it allows the NCs to share from their more distant CCs.

An important distinction between CCA3 and CCA4 chips (of any kind) is that, in a CCA4 chip, an NC may have to borrow a stage from a CC that is not an immediate neighbor. For example, in Figure 2.4(b), Core 4 is approximately twice as far from a CC as Core 3 is. Furthermore, as shown in Figure 2.4(a), a given NC might have different distances to the two CCs (e.g., Core 4's distance to Core 2 and Core 3).

The increase in distance from an NC to a CC may, for some core microarchitectures, discourage the simple approach of lengthening the clock period of an NC that is using a cannibalized stage. In Figure 2.4(a), for example, there might be an unacceptable clock frequency penalty if we slow Core 1 to accommodate using a cannibalized stage from Core 3. Based on this clock penalty, we consider two approaches: the clock period lengthening we have already discussed and adding clock cycles to the pipeline. The first approach sacrifices clock frequency while the second approach sacrifices IPC and chip area. The preferred approach, in terms of overall performance, depends on the details of the core, so we discuss both configurations next.

#### CCA4-clock

The CCA4-clock design relies on increasing the clock period for distant CC accesses. This design is advantageous when the performance penalty of slowing the clock is preferable to adding pipeline stages. The only new issue for CCA4-clock, with respect to CCA3, is that it is possible that we want to have different pipeline stages of the same CC operate at different frequencies. For example, in Figure 2.4(b), if Core 1 is using Core 2's Decode stage and Core 4 is using Core 2's Execute stage, then we want Core 2's Decode stage to be at a higher frequency than its Execute stage. This difference results from Core 4 being further from the CC than Core 1 is from the CC. Prior work has shown how to provide different clocks within a single core [67]. However, if such a solution is considered too costly, then Core 2's clock frequency must be lowered to match the lowest frequency needed, such as the one imposed by Core 4 in the example. We use the CCA4-clock design for both CCA4(2/2) and CCA4(3/1) configurations. We refer to the latter as CCA4-clock(3/1) to differentiate it from its CCA4-pipe implementation that we describe next.

#### CCA4-pipe

The CCA4-pipe design, like CCA3, assumes that routing from an NC to an immediately neighboring CC can be efficiently accommodated by lengthening the clock period of the NC and the CC. However, it allows routing from an NC to a CC that is not an immediate neighbor to take one additional cycle, and routing back from the CC to the NC to account for another cycle. We do not lengthen the clock, because the wire and mux delays fit well within a cycle for a simple, relatively low-frequency core. To avoid adding too much complexity to the NC's control, we do not allow a single NC to borrow more than one stage that requires adding cycles.

When we add wire delay pipeline stages to a core's pipeline, we must add extra pipeline latches and solve four problems:

- 1. Conditional Branch Resolution. In the OR1200, the decision to take a branch is determined by a single signal, BranchFlag, that is continuously propagated from Execute back to Fetch. This BranchFlag is explicitly set/unset by instructions. Because the OR1200 has a single delay slot, the Fetch stage expects to see a BranchFlag signal that corresponds to the instruction that is exactly two instructions ahead of the current instruction in program order. However, adding cycles between Fetch and Execute can cause the BranchFlag signal seen by Fetch to be stale because it corresponds to an instruction that is more than two cycles ahead of it. To address this issue, we slightly modify the pipeline to predict that the stale BranchFlag value is the same as the value that would have been seen in the unmodified pipeline. We add a small amount of hardware to remember the program counter of a branch in case of a misprediction. If the prediction is correct, there is no penalty. A misprediction causes a penalty of two cycles.

- 2. Branch/Jump Target Computation. The target address is computed using a small piece of logic in the Decode stage, and having this unit close to the Fetch stage is critical to performance. As mentioned in Section 2.4.1, we treat this logic separately from the rest of the Decode stage, and we consider it to be logically associated with Fetch. Thus, if there is a fault in the rest of the NC's Decode stage, it still uses its original target address logic. This design avoids penalties for jump address computation.

- 3. Operand Bypassing. When an NC uses a CC's Execute stage, there are some additional bypassing possibilities. The output of the CC's Execute stage may need to be bypassed to an instruction that is in the wire delay stage of the pipeline right before Execute. Instead of adding a bypass path, we simply latch this data and bypass it to this instruction when it reaches the usual

Figure 2.5: Input Buffering for CC's Execute Stage.

place to receive bypassed data (*i.e.*, when it reaches the Execute stage). We also slightly modify the Decode stage to set the correct values for the signals selecting the sources of the instruction's operands.

4. Pipeline Latch Hazards. The extra stages introduce two structural hazards for pipeline latches. First, if a cannibalized stage can incur an unexpected stall, then we must buffer this stage's inputs so they do not get overwritten. For the OR1200, Fetch and Execute require input buffering as illustrated in Figure 2.5, due to I-cache and D-cache misses, respectively. Second, if a cannibalized stage is upstream from (closer to Fetch than) a stage that can incur an unexpected stall, then the stall will reach the cannibalized stage late. To avoid overwriting the output of that stage, we buffer its output. For the OR1200, the Fetch and Decode stages require output buffering (Figure 2.6), because the Execute stage can stall on D-cache misses.

If the area costs of buffering are considered unacceptably high, it is possible to squash the pipeline to avoid the structural hazards. For example, a D-cache miss triggers a squash of younger instructions. In our evaluation of CCA's area, we pessimistically assume the use of buffering rather than squashes, even

Figure 2.6: Output Buffering for CC's Fetch Stage.

though squashing on D-cache misses would have no IPC impact on the OR1200 because the pipe would refill before the D-cache miss resolves.

#### 2.4.4 Many-core CCA Chips

Although we described until now CCA configurations with just three or four cores, CCA is easily extendable to many-core chips. One feasible and straightforward way to apply CCA to chips with more cores is to design these chips as groups of CCA3 or CCA4 clusters. We leave for future work the exploration and evaluation of unclustered designs for chips with greater numbers of cores.

#### 2.5 Evaluation

Evaluating CCA designs requires us to consider two aspects. First, what is CCA's design impact over the baseline chip in terms of area and clock period? Second, how well do processors consisting of CCA3 and CCA4 clusters perform, compared to CS processors? In this section, we address both of these issues.

**Figure 2.7:** CCA Designs Area Overhead. Results are normalized with respect to the areas of CS designs with the same number of cores.

#### 2.5.1 CCA Chip Area Overhead

CCA's area overhead is due to the logic and wiring that enable stages from CCs to be connected to NCs. In Figure 2.7, we plot the area overheads (compared to a CS chip with same number of cores) for various CCA chip implementations in 90nm technology. These areas include the entire chip: cores and the L1 I-caches and D-caches, which are both 8KB and 2-way set-associative (we do not consider L2 caches for our chips). We consider all of the following CCA designs: CCA3(2/1), CCA4-clock(3/1), CCA4-pipe(3/1), and CCA4-clock(2/2).

We observe that no CCA chip has an area overhead greater than 3.5%. CCA3(2/1) incurs less than 2% overhead, which is a difference so small that it requires more than 50 cores on the chip (*i.e.*, approximately 18 CCA3(2/1) clusters), before the additional area is equivalent to a single baseline core. The CCA4 overheads are comparable to the CCA3 overhead, except for CCA4-pipe, which requires some input/output buffering and modified control logic in the cores.

#### 2.5.2 Lifetime Performance

The primary goal of CCA is to provide better lifetime chip performance than CS. We demonstrate in this section that CCA achieves this goal, despite the small per-core performance overheads introduced by CCA. To better understand these results, we first present our fault model, then evaluate fault-free single core performance (for both NCs and CCs) and the performance of an NC using a cannibalized stage.