# Technology Impacts of CMOS Scaling on Microprocessor Core Design for Hard-Fault Tolerance in Single-Core Applications and Optimized Throughput in

Throughput-Oriented Chip Multiprocessors

by

Fred Allison Bower III

Department of Computer Science

Duke University

Dotai

| Date                               |

|------------------------------------|

| Approved:                          |

| Professor Daniel J. Sorin, Advisor |

| Dr. Steven W. Hunter               |

| Professor Alvin R. Lebeck          |

| Professor Christopher L. Dwyer     |

| Professor Landon P. Cox            |

Dissertation submitted in partial fulfillment of the requirements for the degree of Doctor of Philosophy in the Department of Computer Science in the Graduate School of Duke University

#### **ABSTRACT**

Technology Impacts of CMOS Scaling on

Microprocessor Core Design for Hard-Fault Tolerance

in Single-Core Applications and Optimized Throughput in

Throughput-Oriented Chip Multiprocessors

by

Fred Allison Bower III

Department of Computer Science

Duke University

| Date:                              |

|------------------------------------|

| Approved:                          |

| Professor Daniel J. Sorin, Advisor |

| Dr. Steven W. Hunter               |

| Professor Alvin R. Lebeck          |

| Professor Christopher L. Dwyer     |

|                                    |

An abstract of a dissertation submitted in partial fulfillment of the requirements for the degree of Doctor of Philosophy in the Department of Computer Science in the Graduate School of Duke University

Professor Landon P. Cox

Copyright © 2010 by Fred Allison Bower III All rights reserved

#### **Abstract**

The continued march of technological progress, epitomized by Moore's Law provides the microarchitect with increasing numbers of transistors to employ as we continue to shrink feature geometries. Physical limitations impose new constraints upon designers in the areas of overall power and localized power density. Techniques to scale threshold and supply voltages to lower values in order to reduce power consumption of the part have also run into physical limitations, exacerbating power and cooling problems in deep sub-micron CMOS process generations. Smaller device geometries are also subject to increased sensitivity to common failure modes as well as manufacturing process variability.

In the face of these added challenges, we observe a shift in the focus of the industry, away from building ever-larger single-core chips, whose focus is on reducing single-threaded latency, toward a design approach that employs multiple cores on a single chip to improve throughput. While the early multicore era utilized the existing single-core designs of the previous generation in small numbers, subsequent generations have introduced cores tailored to multicore use. These cores seek to achieve power-efficient throughput and have led to a new emphasis on throughput-oriented computing, particularly for Internet workloads, where the end-to-end computational task is dominated by long-latency network operations. The ubiquity of these workloads makes a compelling argument for throughput-oriented designs, but does not free the microarchitect fully from latency demands of common workloads in enterprise and desktop application spaces.

We believe that a continued need for both throughput-oriented and latency-sensitive processors will exist in coming generations of technology. We further opine that making effective use of the additional transistors that will be available may require different techniques for latency-sensitive

designs than for throughput-oriented ones, since we may trade latency or throughput for the desired attribute of a core in each of the respective paradigms.

We make three major contributions with this thesis. Our first contribution is a fine-grained fault diagnosis and deconfiguration technique for array structures, such as the ROB, within the microprocessor core. We present and evaluate two variants of this technique. The first variant uses an existing fault detection and correction technique whose scope is the processor core execution pipeline to ensure correct processor operation. The second variant integrates fault detection and correction into the array structure itself to provide a self-contained, fine-grained, fault detection, diagnosis, and repair technique.

In our second contribution, we develop a lightweight, fine-grained fault diagnosis mechanism for the processor core. In this work, we leverage the first contribution's methods to provide deconfiguration of faulty array elements. We additionally extend the scope of that work to include all pipeline circuitry from instruction issue to retirement.

In our third and final contribution, we focus on throughput-oriented core data cache design. In this work, we study the demands of the throughput-oriented core running a representative workload and then propose and evaluate an alternative data cache implementation that more closely matches the demands of the core. We then show that a better-matched cache design can be exploited to provide improved throughput under a fixed power budget.

Our results show that typical latency-sensitive cores have sufficient redundancy to make finegrained hard-fault tolerance an affordable alternative for hardening complex designs. Our designs suffer little or no performance loss when no faults are present and retain nearly the same performance characteristics in the presence of small numbers of hard faults in protected structures. In our study of the latency-sensitive core, we have shown that SRAM-based designs have low latencies that end up providing less benefit to a throughput-oriented core and workload than a better-fitted data cache composed of DRAM. The move from a high-power, low-latency technology to a lower-power, high-latency technology allows us to increase L1 data cache capacity, which is a net benefit for the throughput-oriented core.

# **Dedication**

To the Doctors Bower that precede me, those that may follow, and for Ronnie.

# **Table of Contents**

| Abstı | act       |           |                                                  | iv    |

|-------|-----------|-----------|--------------------------------------------------|-------|

| List  | of Figure | s         |                                                  | xiii  |

| List  | of Tables |           |                                                  | XV    |

| Ackn  | owledge   | ments     |                                                  | xvi   |

| Сору  | right Ac  | knowledg  | gements                                          | xviii |

| 1     | Introd    | luction   |                                                  | 1     |

|       | 1.1       | Single    | Core Trends in Latency Sensitive Applications    | 3     |

|       | 1.2       | Throu     | ghput-Oriented CMP Trends                        | 4     |

|       | 1.3       | Thesis    | s Statement and Contributions                    | 6     |

|       | 1.4       | Thesis    | s Outline                                        | 7     |

| 2     | Fine-     | Grained 1 | Hard Fault Tolerance in Single Core Applications | 8     |

|       | 2.1       | Fault 7   | Tolerance Background                             | 10    |

|       |           | 2.1.1     | Hard Faults in Submicron CMOS Technology         | 11    |

|       |           |           | 2.1.1.1 Fault Models                             | 11    |

|       |           |           | 2.1.1.2 Underlying Physical Phenomena            | 11    |

|       |           | 2.1.2     | Existing Fault Tolerance Techniques              | 14    |

|       | 2.2       | Self-R    | Lepairing Arrays                                 | 16    |

|       |           | 2.2.1     | Microprocessor Array Structures                  | 18    |

|       |           |           | 2.2.1.1 Reorder Buffer                           | 18    |

|       |           |           | 2.2.1.2 Branch History Table                     | 19    |

|       |           | 2.2.2     | Design Space                                     | 20    |

|     | 2.2.3  | SRAS-CheckRow (SRAS-CR)                            | 21 |

|-----|--------|----------------------------------------------------|----|

|     |        | 2.2.3.1 Detection and Diagnosis                    | 21 |

|     |        | 2.2.3.2 Recovery                                   | 23 |

|     |        | 2.2.3.3 Mapping Out Faulty Sub-arrays              | 23 |

|     |        | 2.2.3.4 ROB Remapper                               | 24 |

|     |        | 2.2.3.5 BHT Remapper                               | 25 |

|     | 2.2.4  | SRAS-CR Costs                                      | 27 |

|     | 2.2.5  | Limitations of SRAS-CR                             | 28 |

|     | 2.2.6  | SRAS-EDC: Self-Repair Design Without DIVA Backstop | 29 |

|     |        | 2.2.6.1 Detection and Diagnosis                    | 31 |

|     |        | 2.2.6.2 Recovery                                   | 34 |

|     |        | 2.2.6.3 Remapping                                  | 34 |

|     |        | 2.2.6.4 SRAS-EDC Costs                             | 35 |

|     |        | 2.2.6.5 Limitations of SRAS-EDC                    | 35 |

|     | 2.2.7  | Applicability of SRAS to Specific Structures       | 35 |

|     |        | 2.2.7.1 Instruction Buffer                         | 35 |

|     |        | 2.2.7.2 Instruction Scheduling Window              | 36 |

|     |        | 2.2.7.3 Load-Store Queue                           | 37 |

|     |        | 2.2.7.4 Branch History Table                       | 38 |

|     |        | 2.2.7.5 Reorder Buffer                             | 38 |

| 2.3 | Online | Diagnosis of Hard Faults in Microprocessors        | 38 |

|     | 2.3.1  | Fault Diagnosis                                    | 39 |

|     | 2.3.2  | A New Online Diagnosis Mechanism                   | 40 |

|     |        | 2.3.2.1 Design Issues                              | 41 |

|     |        |                                                    |    |

|   |        |         | 2.3.2.2 Heuristics for Choosing Error Counter Values               | 43 |

|---|--------|---------|--------------------------------------------------------------------|----|

|   |        |         | 2.3.2.3 Discussion                                                 | 45 |

|   |        |         | 2.3.2.4 Alternative Design Options                                 | 47 |

|   |        | 2.3.3   | Deconfiguring Faulty Components                                    | 49 |

|   |        | 2.3.4   | Costs and Limitations                                              | 51 |

|   |        |         | 2.3.4.1 Hardware Costs                                             | 51 |

|   |        |         | 2.3.4.2 Limitations                                                | 51 |

|   | 2.4    | Evaluat | tion                                                               | 53 |

|   |        | 2.4.1   | Experimental Methodology and System Model                          | 53 |

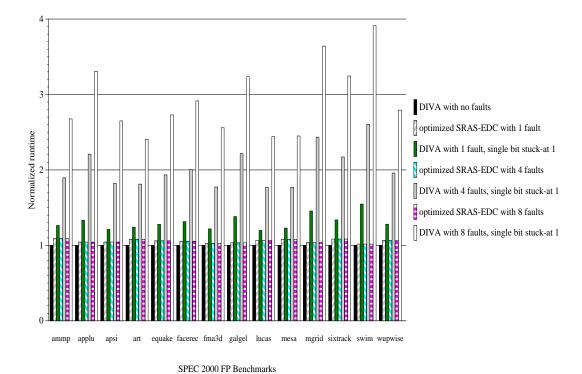

|   |        | 2.4.2   | SRAS-CR and SRAS-EDC                                               | 56 |

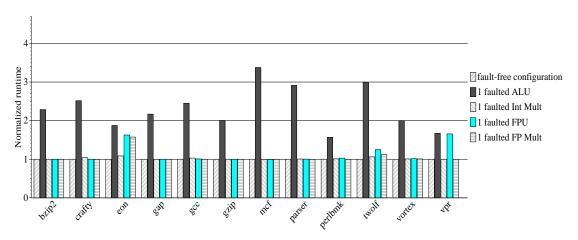

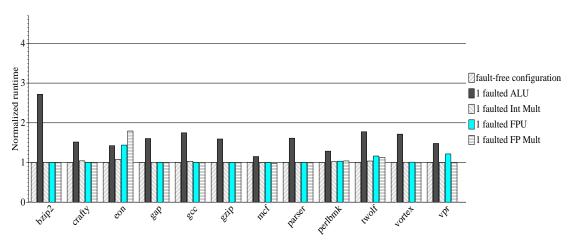

|   |        |         | 2.4.2.1 Fault-Free Performance                                     | 56 |

|   |        |         | 2.4.2.2 Performance in Presence of Faults                          | 57 |

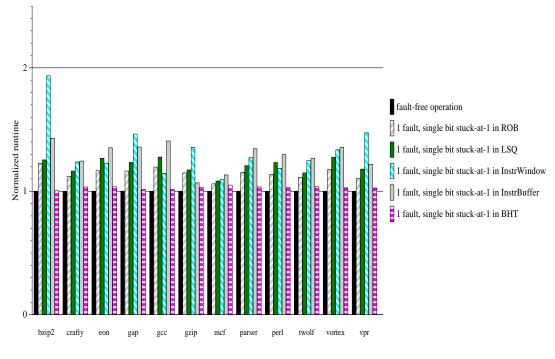

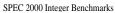

|   |        |         | 2.4.2.3 Relative Performance Impact of Protecting Different Arrays | 60 |

|   |        |         | 2.4.2.4 Implementation Costs 62                                    |    |

|   |        | 2.4.3   | Online Diagnosis                                                   | 63 |

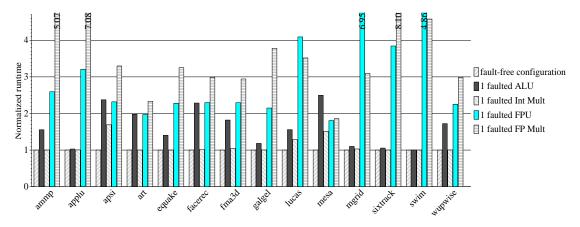

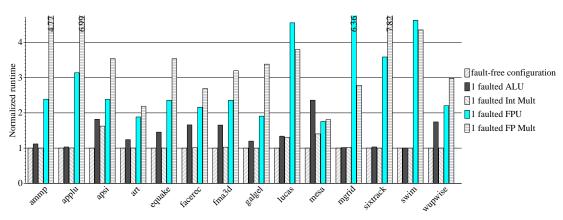

|   |        |         | 2.4.3.1 Detection and Diagnosis of Hard Faults                     | 64 |

|   |        |         | 2.4.3.2 Performance After Deconfiguring FDU                        | 70 |

|   |        |         | 2.4.3.3 Performance with Just DIVA Recovery (But No Diagnosis)     | 71 |

|   |        | 2.4.4   | Summary and Discussion of Results                                  | 77 |

|   |        | 2.4.5   | Related Work                                                       | 80 |

| 3 | Extend | ing DRA | AM Use to the Level 1 Data Cache in Throughput-Oriented CMPs       | 83 |

|   | 3.1    | Experin | mental Methodology                                                 | 85 |

|        | 3.2   | Demar   | nds of Throughput-Oriented Workloads                               | 88  |

|--------|-------|---------|--------------------------------------------------------------------|-----|

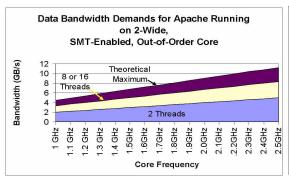

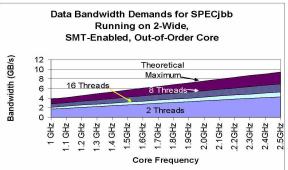

|        |       | 3.2.1   | Bandwidth Demands of the Throughput-Oriented Core                  | 88  |

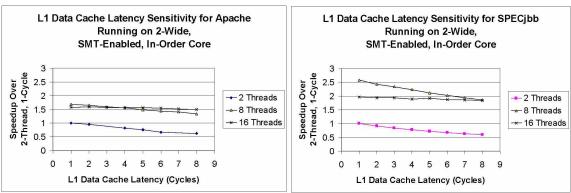

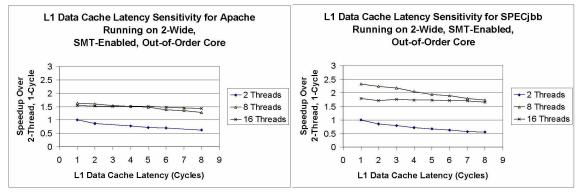

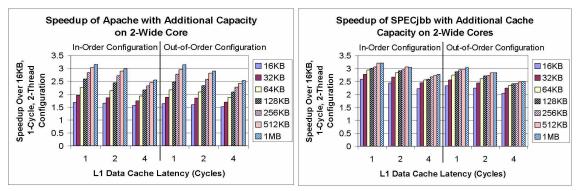

|        |       | 3.2.2   | L1 Data Cache Latency Sensitivity                                  | 90  |

|        |       | 3.2.3   | Throughput-Oriented Cache Demand Summary                           | 92  |

|        | 3.3   | Cache   | Building Block Technology Alternatives                             | 92  |

|        |       | 3.3.1   | Build a Better SRAM Cell                                           | 93  |

|        |       | 3.3.2   | Embedded DRAM as an Alternative to SRAM                            | 94  |

|        |       | 3.3.3   | Hybrid Caches                                                      | 94  |

|        | 3.4   | Experi  | mental Cache Design Space Exploration                              | 95  |

|        |       | 3.4.1   | L1 Data Cache Evaluation                                           | 96  |

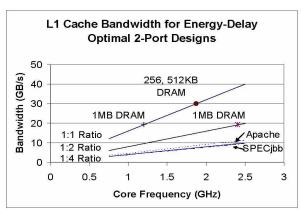

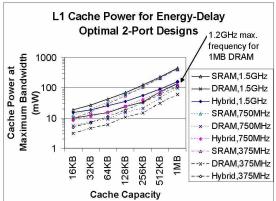

|        |       |         | 3.4.1.1 Bandwidth and Power                                        | 96  |

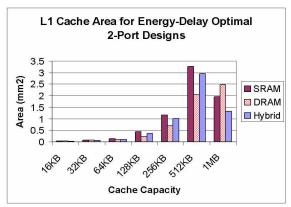

|        |       |         | 3.4.1.2 Cache Area                                                 | 100 |

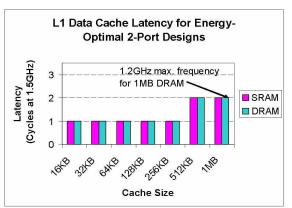

|        |       |         | 3.4.1.3 Cache Latency                                              | 101 |

|        |       |         | 3.4.1.4 Summary of L1 Data Cache Evaluation                        | 102 |

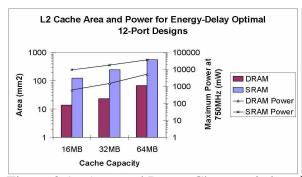

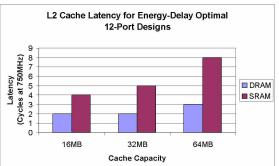

|        |       | 3.4.2   | L2 Cache Evaluation                                                | 102 |

|        |       | 3.4.3   | Putting it All Together: Evaluation of a Throughput-Oriented Cache | 104 |

|        |       |         | 3.4.3.1 Improvements in the L1 Data Cache                          | 105 |

|        |       |         | 3.4.3.2 Opportunities in the L2 Cache                              | 107 |

|        | 3.5   | Relate  | d Work                                                             | 108 |

| 4      | Summa | ary and | Conclusions                                                        | 109 |

|        | 4.1   | Summ    | ary of Results                                                     | 110 |

|        | 4.2   | Conclu  | asions                                                             | 112 |

| Refere | nces  |         |                                                                    | 114 |

|        |       |         |                                                                    |     |

Biography 123

# **List of Figures**

| Figure 2-1.  | Oxide Breakdown Process and its Circuit Level Implications                                                          | 12 |

|--------------|---------------------------------------------------------------------------------------------------------------------|----|

| Figure 2-2.  | Broader Impact of OBD in the Circuit                                                                                | 12 |

| Figure 2-3.  | Array Remapping                                                                                                     | 24 |

| Figure 2-4.  | Deconfiguration of Entries in a Circular Buffer (e.g., Reorder Buffer)                                              | 24 |

| Figure 2-5.  | Deconfiguration of Entries in a Tabular Structure (e.g., Reservation Station)                                       | 24 |

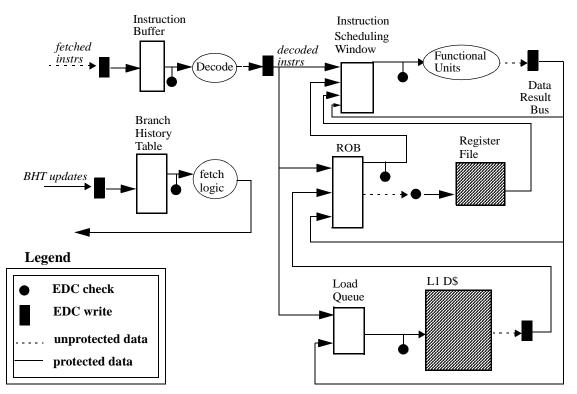

| Figure 2-6.  | Datapath Design with SRAS-EDC                                                                                       | 30 |

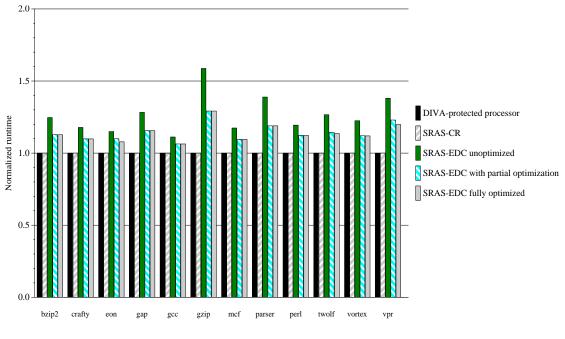

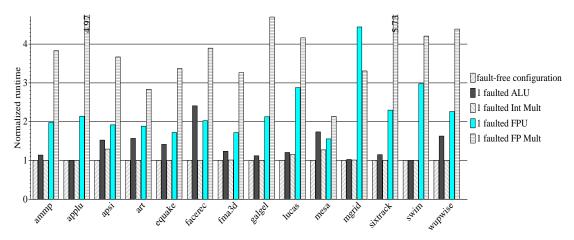

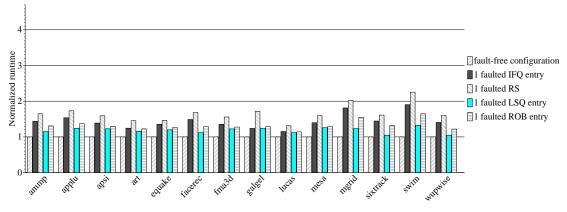

| Figure 2-7.  | Fault-Free Runtime                                                                                                  | 58 |

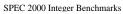

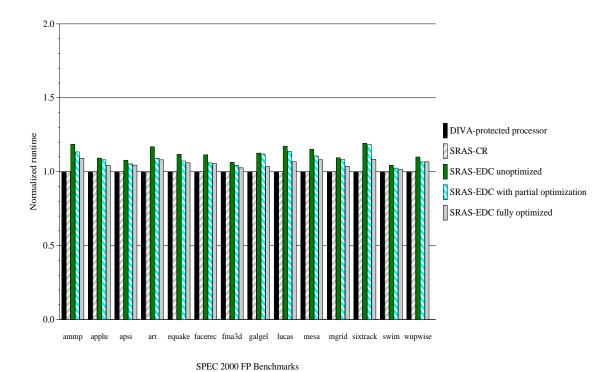

| Figure 2-8.  | Runtime with Hard Faults Injected into the Reorder Buffer                                                           | 59 |

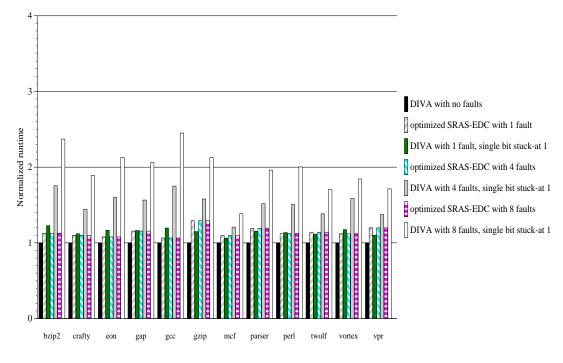

| Figure 2-9.  | Impact on Runtime of Hard Faults on Other Array Structures                                                          | 61 |

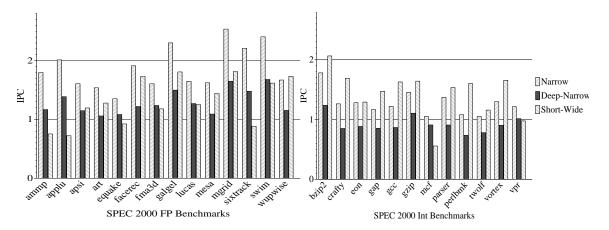

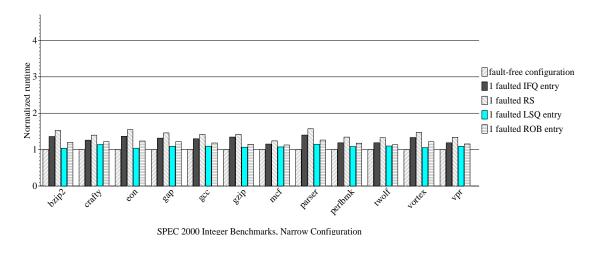

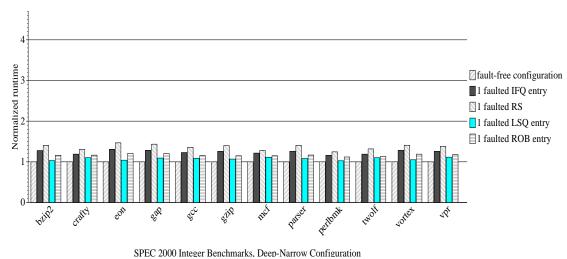

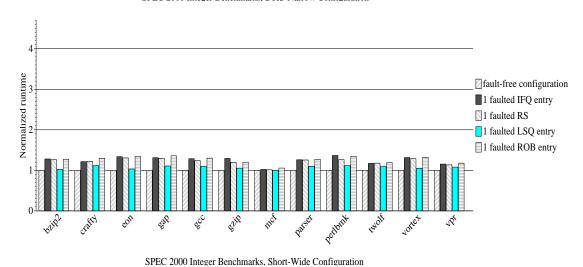

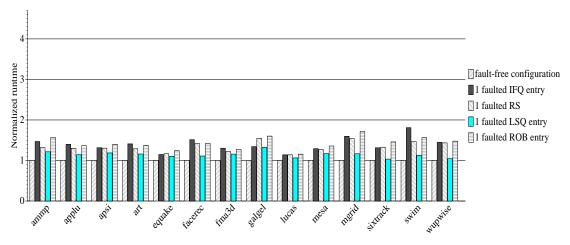

| Figure 2-10. | Error-Free Performance (SPECfp and SPECint) for Each of the Three Evaluated Processor Configurations                | 64 |

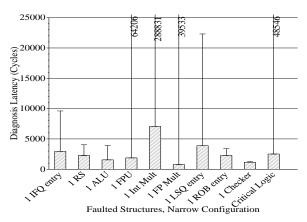

| Figure 2-11. | Hard Fault Diagnosis Latency, Averaged Over All Benchmarks, for<br>Narrow Configuration                             | 65 |

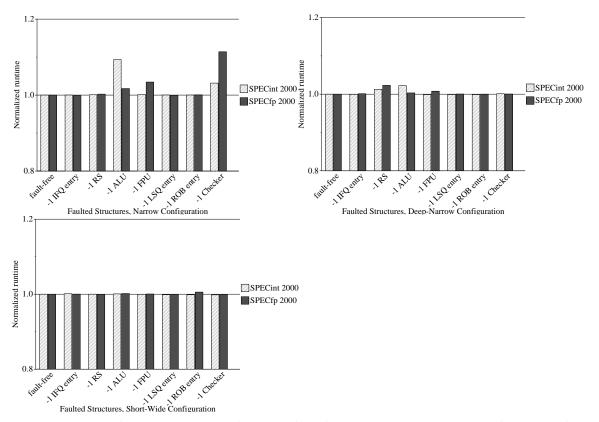

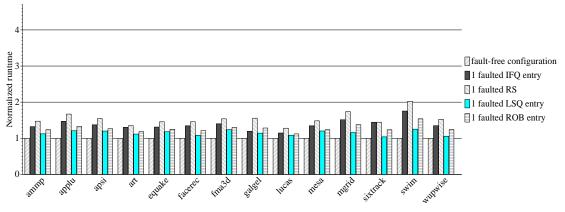

| Figure 2-12. | Performance Impact of Losing One Component to a Hard Fault for Each of the Three Evaluated Processor Configurations | 67 |

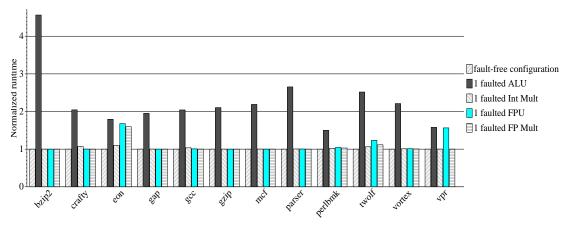

| Figure 2-13. | Performance of DIVA-Only Correction for Combinational Logic Units (SPECint)                                         | 72 |

| Figure 2-14. | Performance of DIVA-Only Correction for Combinational Logic (SPECfp)                                                | 73 |

| Figure 2-15. | Performance of DIVA-Only Correction for Array Logic Units (SPECint)                                                 | 74 |

| Figure 2-16. | Performance of DIVA-Only Correction for Array Logic Units (SPECfp)                                                  | 75 |

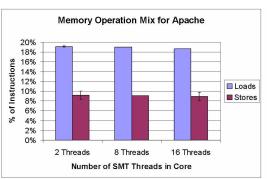

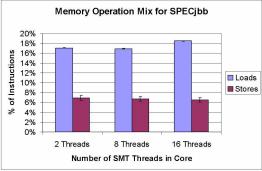

| Figure 3-1.  | Dynamic Instruction Stream Memory Instruction Mix                                                                   | 89 |

| Figure 3-2.  | Throughput-Oriented Core Bandwidth Demands on L1 Data Cache                                                         | 89 |

| Figure 3-3.  | Apache Web Server and SPECjbb Normalized Throughput on Out-of-Order, Multithreaded Cores with Varying L1 Data Cache Latency                                          | 91  |

|--------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Figure 3-4.  | Apache Web Server and SPECjbb Normalized Throughput on In-Order,<br>Multithreaded Cores with Varying L1 Data Cache Latency                                           | 91  |

| Figure 3-6.  | Power Comparison of SRAM, 1T1C DRAM, and Hybrid [77] L1 Data Cache Designs                                                                                           | 97  |

| Figure 3-5.  | L1 Data Cache Bandwidth for Selected Designs as Core Frequency is Varied                                                                                             | 97  |

| Figure 3-8.  | Latency of SRAM and DRAM-Based L1 Data Cache Implementations                                                                                                         | 100 |

| Figure 3-7.  | L1 Data Cache Area for Energy-Delay Optimized Designs Implemented with SRAM, DRAM, or Hybrid Cells                                                                   | 100 |

| Figure 3-9.  | Area and Power Characteristics of Large L2 Cache Configurations for Large-Scale CMPs                                                                                 | 104 |

| Figure 3-10. | Latency to Access SRAM and DRAM L2 Caches at 750MHz Operating Frequency                                                                                              | 104 |

| Figure 3-11. | Speedup by 8-Thread Configurations Over 2-Thread Core with 16 KB, 1-Cycle L1 Data Cache at L1 Data Cache Capacities From 16KB to 1MB and 1, 2, and 4-Cycle Latencies | 106 |

# **List of Tables**

| Table 2-1. | Fault Tolerance Techniques: Design Points and Limitations           | 17  |

|------------|---------------------------------------------------------------------|-----|

| Table 2-2. | Error Counter Thresholds                                            | 45  |

| Table 2-3. | SRAS Target System Parameters                                       | 54  |

| Table 2-4. | Parameters of Target Systems for Online Diagnosis Evaluation        | 55  |

| Table 2-5. | Number of Diagnoses Needed to Identify Correct Failing Unit         | 68  |

| Table 3-1. | Processor Configuration for L1 Data Cache Latency Sensitivity Study | 86  |

| Table 3-2. | L1 Data Cache Configurations Explored                               | 87  |

| Table 3-3. | L2 Cache Configurations Explored                                    | 103 |

| Table 3-4. | Cache Power, in Milliwatts at Maximum Throughput                    | 105 |

#### Acknowledgements

There are many people to whom I owe a debt of gratitude for their support of my work. I would like to acknowledge that support here. First and foremost, I am grateful for the support of my parents, who have provided me with an upbringing that values education and who have backed my efforts fully. I am also thankful for the support of my extended family throughout my long journey. I am most appreciative of the patience of my wife, son, and dogs, all of whom have had to often come in second place as I have worked toward this goal. They share this accomplishment, though their contributions are not directly written here.

I am appreciative of the patience of my advisor, Dan Sorin, and my IBM advisor, Steve Hunter, both of whom have helped me achieve this goal, despite the many challenges that presented themselves along the way. Gauging the abilities and motivators of another is a skill that Dan has acquired new depth in throughout his tenure advising this dissertation, and I am grateful that he has endured through the process to my definition of success.

I have many IBM colleagues to thank, but those that have been the most instrumental to my success are Celia Schreiber, Bill Ott, and Steve Levesque. Celia and Bill supported me at the beginning and Steve has supported me at the end, when time has been hard to come by. The understanding and commitment on the part of the company, as personified by the support of these three has made this accomplishment possible.

To my extended Durham community, I am also thankful. My Duke Architecture office mates, Dr. Tong Li, Dr. Albert Meixner, and Dr. Anita Lungu all precede me in the alumni ranks and their example has helped to guide me to completion. My village of coffee shop denizens has been supportive in ways that they could not have possibly recognized the value of at the time, but their constant presence has been part of my success here.

My final note of gratitude is due to Diane Riggs, my personal guide through the administrative maze that is the Duke Graduate School and Computer Science Department. More so than for a typical student, Diane has been a constant shepherd of my progress and guide through the process of completing my degree requirements. Without her help, I would not be writing these words now. I wish her the best in her life after Duke and can only hope that those that may follow have as good a guide as Diane has been.

#### **Copyright Acknowledgements**

Content found in Chapter 2 has been previously published and is republished here with permission from ACM and IEEE. The following copyright notices apply to the applicable content in Chapter 2.

©ACM, 2007. This is the author's version of the work. It is posted here by permission of ACM for your personal use. Not for redistribution. The definitive version was published in ACM Transactions on Architecture and Code Optimization (TACO), {4, 2, (June 2007)} http://doi.acm.org/10.1145/1250727.1250728

This material is posted here with permission of the IEEE. Such permission of the IEEE does not in any way imply IEEE endorsement of any of Duke University's products or services. Internal or personal use of this material is permitted. However, permission to reprint/republish this material for advertising or promotional purposes or for creating new collective works for resale or redistribution must be obtained from the IEEE by writing to pubs-permissions@ieee.org. By choosing to view this material, you agree to all provisions of the copyright laws protecting it.

#### 1 Introduction

As computer architects, we continue to benefit from the decades-long progression of Moore's Law [46]. Increasing device densities into deep sub-micron feature geometries have enabled further performance gains in latency-sensitive single-core applications, and have also ushered in the generation of throughput-oriented computing. Chip multiprocessors (CMPs) now are ubiquitous in personal computers and servers. With the technological advances that enable these increased densities comes a set of additional challenges.

First, with smaller device geometries and lower operating voltages, devices are more sensitive to many of the fault causing effects. These effects stem from manufacturing defects, such as particle contamination or process variation, and from wearout effects due to gate oxide breakdown and electromigration [13, 30, 51, 68]. Increased sensitivity presents additional challenges in process yield at the factory. It also makes parts more sensitive to progressive field wearout effects [8] and the phenomena that incur transient faults.

This increased sensitivity has caused device reliability in high-performance to become a greater concern with smaller geometries. Techniques that help to maintain or improve manufacturing yields, extend part lifetimes, and provide graceful degradation in the presence of common faults in critical structures are increasingly important in these designs as they incorporate ever-more transistors and per-transistor fault rates fail to keep pace with these increases.

Next, while we continue to lower operating voltages to reduce power consumption, we are approaching a point where the ability to scale voltage further is limited by physical limits. Until recent technology generations, scaling of voltage provided an effective means to keep chip power from growing as we add more devices to the same area. With this technique losing its ability to keep pace with further scaling, we now face a challenge to reduce power via other means, such as

reducing the average activity factor of transistors on the part. Reduction of threshold voltage has also brought with it an increase in the leakage component of the power consumption by traditional device designs such as the six-transistor (6T) SRAM cell commonly employed as a building block for on-chip storage, both within the core and in the cache hierarchy.

Finally, as densities have increased, basic cooling limits of the total microprocessor package have not. This is due to the fact that maximum die area has remained relatively fixed at roughly 400 mm<sup>2</sup> and advances in heatsink technology have not provided significant additional gains in heat dissipation from the package. With a physical cap on power dissipation, power has become a first-class design constraint.

These challenges present a new set of boundaries that constrain the microarchitect in extracting additional value from the ever-increasing transistor budget. At the same time, efforts to improve single-threaded performance have been thwarted by challenges with scalability of performance-critical structures in the core and the power challenges of increasing chip frequency. This has led the microarchitecture community away from techniques that seek to increase ILP in single-threaded applications. Instead, we are now seeing increased focus on optimizing energy-delay to achieve balanced throughput per unit power with reasonable latency in many applications, particularly in the commercial application space of the Internet.

As a result of these trends, we develop techniques to cope with these fundamental challenges in both latency-sensitive and throughput-oriented paradigms. In latency-sensitive core design space, we propose and evaluate fine-grained hard fault tolerance mechanisms within the core. In the throughput-oriented CMP design space, we study the demands of the throughput-oriented core and data cache alternatives that provide a better match to these demands than traditional cache designs.

The rest of this chapter is organized as follows. In Section 1.1, we discuss trends that motivate our research in the latency-sensitive core design space. In Section 1.2, we explore how these general trends impact the throughput-oriented core design space. Section 1.3 presents our thesis statement and the hypotheses that we test in this work. We conclude in Section 1.4 with an outline of the rest of the dissertation.

#### 1.1 Single Core Trends in Latency Sensitive Applications

As technological trends continue to lead toward smaller device and wire dimensions in integrated circuits, the probability of hard (permanent) faults in microprocessors increases. These faults may be introduced during fabrication, as defects, or they may occur during the operational lifetime of the microprocessor. Well-known physical phenomena that lead to operational hard faults are gate oxide breakdown, electromigration, and thermal cycling. Microprocessors become more susceptible to all of these phenomena as device dimensions shrink [68], and the semiconductor industry's roadmap has identified both operational hard faults and fabrication defects (which we will collectively refer to as "hard faults") as critical challenges [28]. In the near future, it may no longer be a cost-effective strategy to discard a microprocessor with one or more hard faults, which is what, for the most part, we do today.

Traditional approaches to tolerating hard faults have masked them using macro-scale redundancy, such as triple modular redundancy (TMR). TMR is an effective approach, but it incurs a 200% overhead in terms of hardware and power consumption. There are some other, lightweight approaches that use marginal amounts of redundancy to protect specific portions of the microprocessor, such as the cache [49, 84], but none of these are comprehensive.

Our goal in this work is to create a microprocessor design that can tolerate hard faults without adding significant redundancy. The key observation, made also by previous research [64, 67, 69],

is that modern latency-sensitive, superscalar microprocessors, particularly those supporting simultaneously multithreading (SMT) [76], already contain significant amounts of redundancy for purposes of exploiting ILP and enhancing performance. We want to use this redundancy to mask hard faults, at the cost of a graceful degradation in performance for microprocessors with hard faults. In this work, we do not consider adding extra redundancy strictly for fault tolerance, because cost is such an important factor for commodity microprocessors. The viability of our approach depends only on whether, given a faulty microprocessor core, being able to use it with somewhat degraded performance provides any utility over having to discard it.

To achieve our goal, the microprocessor core must be able to do three things while it is running.

- 1) It must detect and correct errors caused by faults (both hard and transient).

- 2) It must diagnose where a hard fault is, at the granularity of the field deconfigurable unit (FDU).

- 3) It must deconfigure a faulty FDU in order to prevent its fault from being exercised.

While previous work in this area has explored aspects of this problem, none has developed an integrated solution. Some work has used deconfiguration to tolerate strictly fabrication defects and thus assumed pre-shipment testing instead of online error detection and diagnosis [64]. Other work has explored deconfiguration and has left detection and diagnosis as open problems [69]. We will discuss integrated design options for microprocessors that achieve all three of these goals in Chapter 2.

# 1.2 Throughput-Oriented CMP Trends

Multicore processors are now the standard commodity computing platform. Many researchers argue that Moore's law will lead to exponential increases in the number of cores per chip. In this scenario the memory system that serves these cores becomes a crucial system component in terms

of performance and power. As power and energy efficiency become first-class design constraints, the ability to increase clock frequencies as the primary means for improved performance becomes infeasible.

The response by system designers has been to place greater emphasis on exploiting coarse-grained, thread-level parallelism (TLP) by increasing the number of cores on a single chip. This new paradigm represents an opportunity to revisit single-chip designs. Specifically, for many server workloads, throughput is the primary performance metric. The realization that a more energy-efficient design point can be achieved for throughput-oriented computing led to a redesign of the cores. Recent chip multiprocessors (e.g. UltraSparc T2 [62]) have a large number of simpler low-power processor cores, often with multithreading for tolerating long latency events, instead of a small number of sophisticated high-power cores.

Although *core* microarchitectures have been re-designed for throughput-oriented computing, the *memory systems* are still tailored to the demands of high-performance, latency-centric cores. Instead, designs should seek to balance latency, bandwidth, and capacity for optimum throughput. The aim of the work we present in Chapter 3 is to identify and exploit mis-matches in the capabilities of the on-chip data cache and the throughput-oriented core. The first part of this work is to show that the low latency caches of the late single-core and early multicore era over-emphasize the criticality of latency for a throughput-oriented workload. With the magnitude and nature of the miss-match better understood, we explore ways in which we can trade over-provisioned attributes, such as latency, for attributes that will benefit the throughput-oriented CMP, namely additional cache capacity and power savings.

#### 1.3 Thesis Statement and Contributions

With this thesis, our goal is to validate two primary hypotheses motivated by the high-level trends we have reviewed in this introduction: 1) fine-grained techniques for detecting, diagnosing, and tolerating hard faults in latency-sensitive cores can provide performance of a fault-free core in both fault-free and fault-present states at a fraction of the hardware and power costs of traditional coarse-grained fault-tolerance methods and 2) a throughput-oriented cache design, better matched to core demands, enables additional throughput gains over present designs under a fixed power budget.

In support of these hypotheses, we make three primary contributions:

- 1) Our first contribution is a fine-grained fault diagnosis and deconfiguration technique for array structures, such as the ROB, within the microprocessor core. We present and evaluate two variants of this technique. The first variant uses an existing fault detection and correction technique scoped to the processor core execution pipeline to ensure correct processor operation. The second variant integrates fault detection and correction into the array structure itself to provide a self-contained, fine-grained, fault detection, diagnosis, and repair technique.

- 2) In our second contribution, we develop a lightweight, fine-grained fault diagnosis mechanism for the processor core. In this work, we leverage the first contribution's methods to provide deconfiguration of faulty array elements. We additionally extend the scope of that work to include all pipeline circuitry from instruction-issue to retirement.

- 3) In our third and final contribution, we study the demands of the throughput-oriented core running a representative workload and then propose and evaluate an alternative data cache implementation that more closely matches the demands of the core. We then show that a better-

matched cache design can be exploited to provide improved throughput under a fixed power budget.

#### 1.4 Thesis Outline

We begin our presentation of contributions in Chapter 2, with a presentation of our fine-grained fault tolerance and diagnosis techniques. In Chapter 3, we present our work on throughput-oriented cache design. The thesis concludes with a summary of contributions and conclusions in Chapter 4.

# 2 Fine-Grained Hard Fault Tolerance in Single Core Applications<sup>1</sup>

In this chapter we develop and evaluate techniques to provide fine-grained hard-fault tolerance in the high-performance microprocessor core. With large, complex core implementations, fine-grained techniques afford the designer with a way to provide graceful degradation of performance in the presence of small numbers of faults, even in critical structures. With the methods that we develop, our evaluation shows that performance losses can be mitigated to a point where utility of the part is retained for extended periods of operation after faults are encountered. The chapter begins with a definition of the fault models that we use and a discussion of existing techniques for providing fault tolerance in the microprocessor core.

We then discuss the design space for self-repairing microprocessor array structures, and we present two specific designs. Array structures include the reorder buffer, load-store queue, instruction queue, branch history table, etc. Our goal is to develop self-repairing arrays that enable autonomic execution. In both of our designs for self-repairing array structures (SRAS), spare rows are built into each array structure and are mapped in to replace faulty rows using a level of indirection. This approach is similar to how disks map out faulty sectors and how hard faults in DRAMs can be tolerated with schemes that map out faulty locations [19, 44, 59]. Our first design, SRAS-Check-Row (SRAS-CR), uses dedicated check rows to detect and diagnose hard faults. SRAS-CR relies upon DIVA [6] to recover from transient errors and errors due to hard faults that have not yet been classified as hard. Our second design, SRAS-EDC, uses error detecting codes (EDC) for error

<sup>1.</sup> This chapter contains previously published work that is covered by the following copyrights:

<sup>©2005</sup> IEEE. Reprinted, with permission, from IEEE Transactions on Dependable and Secure Computing, Autonomic Microprocessor Execution via Self-Repairing Arrays, Fred A. Bower, Sule Ozev, and Daniel J. Sorin.

<sup>©</sup>ACM, 2007. This is the author's version of the work. It is posted here by permission of ACM for your personal use. Not for redistribution. The definitive version was published in ACM Transactions on Architecture and Code Optimization (TACO), {4, 2, (June 2007)} http://doi.acm.org/10.1145/1250727.1250728

detection/diagnosis, and it uses the pre-existing branch misprediction recovery mechanism to recover from transient errors and errors due to hard faults that have not yet been classified as hard. After a hard fault has been diagnosed and mapped out, neither SRAS-CR nor SRAS-EDC incurs a performance penalty due to that fault, unlike lightweight schemes that incur a costly recovery for every manifestation of a hard fault.

Our experimental results show that SRAS-EDC adds some performance overhead in the fault-free case, but that both SRAS-CR and SRAS-EDC mask hard faults (a) without the hardware costs of high-level redundancy (e.g., IBM mainframes [66]) and (b) without the per-error performance penalty of existing low-cost techniques (e.g., DIVA). When hard faults are present in arrays, due to operational faults or fabrication defects, then our SRAS schemes outperform low-cost techniques that require a pipeline recovery per error. Given the increasing frequencies of fabrication defects and operational hard faults, the likelihood of wanting to be able to operate correctly with one or more hard faults makes array self-repair appealing.

With our two SRAS implementations defined, we expand our scope to develop an online, fine-grained fault diagnosis and deconfiguration mechanism for the microprocessor core. In this work, we utilize SRARS-style methods for deconfiguration of faulty array structures. We also extend our ability to diagnose faults to include functional units and data paths within the processor pipeline. Our experimental results show that our new diagnosis mechanism quickly and accurately diagnoses hard faults. Moreover, our reliable microprocessor can function quite capably in the presence of hard faults, despite not using redundancy beyond that which is already available in a modern microprocessor. This technique can turn otherwise useless microprocessors into microprocessors that can function at a gracefully degraded level of performance. This capability can improve reliability by tolerating operational hard faults. We can improve yield by shipping micro-

processors with defects that we have tolerated—it is as if they are regular microprocessors that will get "binned" into a lower performance bin. Although binning is typically by clock frequency, recent proposals have suggested more general performance binning [64]. As long as these bins are not so low-performing as to be useless, then our improvement in yield is a benefit. Our scheme also vastly outperforms a system with only DIVA or a comparable recovery-based scheme, since the performance cost of recoveries is quite high for hard faults that get exercised frequently; moreover, our scheme can tolerate a hard fault in a DIVA checker.

The rest of this chapter is organized as follows. Section 2.1 provides background on our hard fault model. The underlying physical phenomena that lead to hard faults are discussed in some detail to familiarize the reader with these mechanisms as well as to further motivate the case for providing hard-fault tolerance in coming microprocessor core designs. Section 2.2 presents SRAS-CR and SRAS-EDC in detail, explaining the mechanisms, how they operate, and their limitations and advantages in the application of providing hard-fault tolerance to microprocessor core array structures. In Section 2.3, we present our fine-grained diagnosis and deconfiguration framework for high-performance microprocessor cores. We conclude this chapter in Section 2.4, with the experimental evaluation of these techniques.

### 2.1 Fault Tolerance Background

In this section, we first define terminology around fault tolerance that we will utilize throughout the rest of the chapter. We also present the historical progression of designs that has led up to this point and motivated the work in this chapter.

#### 2.1.1 Hard Faults in Submicron CMOS Technology

We start with a presentation of existing high-level models for hard faults (Section 2.1.1.1) and then we delve into the underlying physical phenomena that cause hard faults (Section 2.1.1.2). In this process, we show that existing fault models are applicable to the physical faults that we consider in this work

#### 2.1.1.1 Fault Models

To facilitate fault tolerant design and testing for physical faults that lead to errors at the circuit level, several structural fault models have been developed for logic circuits and storage components over the past few decades [1]. The *stuck-at fault model* is the most commonly used model in VLSI testing and fault tolerance schemes. In this model, a physical defect manifests itself as a signal consistently having a certain value (either zero or one) independent of the input. For example, an unintended short circuit between the two inputs of an XOR gate results in a stuck-at-zero fault at the output signal. The *coupling fault model*—in which a write to a certain memory location always prompts a write to a neighboring location or locations—has been defined for storage components [18]. The recently defined *transition fault model* represents a slow charging or discharging of a circuit node [53, 60, 75]. This delay can cause incorrect logic values to be latched.

Next, in Section 2.1.1.2, we see that stuck-at and coupling fault models will be sufficient for the hard faults that we consider.

#### 2.1.1.2 Underlying Physical Phenomena

The reliability of electronic devices under discrete environmental stress, such as radiation [70], and continuous functional stress due to the applied electric field [11, 57, 72] has been a topic of vast research since the early days of semiconductor manufacturing. Extensive research has been conducted on the failure-causing physical phenomena, such as electromigration [11, 34, 72] and

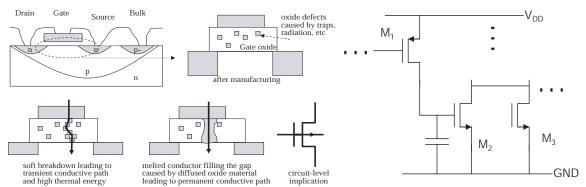

Figure 2-1. Oxide Breakdown Process and its Circuit Level Implications

Figure 2-2. Broader Impact of OBD in the Circuit

transistor gate oxide breakdown (OBD) [23]. There have been several recent studies of operational hard faults [30, 68], that is, hard faults that occur over the lifetime of the microprocessor. Srinivasan et al. [68] determine that electromigration and gate oxide breakdown are likely to be the two dominant phenomena that cause operational hard faults, thus we focus on them in developing our fault models in this work. Electromigration results in highly resistive interconnects or contacts and eventually leads to open circuits. Such defects are typically modeled as transition faults during manufacturing testing, but they become stuck-at faults during operation due to their progressive nature.

Gate oxide breakdown (OBD) results in the malfunction of a single transistor due to the creation of a highly conductive path between its gate and its bulk. As illustrated in Figure 2-1, a newly manufactured oxide contains inherent electron traps due to imperfections in the fabrication process. Over the lifetime of the device, the number of such traps increases due to electric field stress and electron tunneling. At some point, the electron traps may line up and constitute a conductive path between the gate and the bulk of the device. The onset of this phenomenon is called a soft breakdown (SBD). OBD increases switching delay. It can lead to delay faults that manifest themselves as bit flips [16]. Initially, the conductive path may be transient since the high heat

caused by high current density may relocate some of the traps. However, after several SBD incidents, the oxide layer diffuses and highly conductive melted metal fills the void and solidifies into a consistent path. This phenomenon is called hard breakdown (HBD). Similar to the electromigration case, the initial circuit level manifestation of SBD is a transition fault, whereas the effect of the subsequent HBD is a stuck-at fault. OBD defects are potentially more dangerous than electromigration defects due to the consistent path between a charged node and ground or supply. For the circuit illustrated in Figure 2-2, an OBD defect in transistor M2 forms a conductive path between the drain of M1 (and the gate of M2) and the ground node. As long as the logic value at the gate of M1 is LOW, there is a sustained resistive path from the supply to the ground, resulting in sustained current flow through transistor M1. Since the resistance of this transistor for a LOW input is typically small, the current can be large, potentially damaging M1 or causing regional drops in the supply. Thus, detection and isolation of memory locations with OBD defects is essential for the operational health of computing devices.

Both the electromigration and OBD defects are progressive in nature. The mean time to failure (MTTF) for both defects depends on the thickness and the initial health of the structure. Reported laboratory data on OBD indicates that MTTF is on the order of four million seconds (around 46 days) for 15Å gate oxides under constant stress of 2.1V [40] (scaling the supply voltage down to 1.0V, we can estimate the MTTF for this oxide thickness to be 375 days). However, MTTF also depends heavily on the number and location of initial traps within the oxide; thus it can be much shorter for some transistors with inherent weaknesses. A similar analysis can be made for electromigration defects [12].

In the early stages of the progression of both electromigration defects and OBD defects, bit errors only occur if the defects are sequentially excited. However, in later stages, both defects resemble stuck-at faults. Moreover, in addition to affecting the output node to which the defective transistor is connected, the OBD defects may result in coupling faults due to their current driving nature. Thus, in our evaluation experiments, we inject stuck-at faults and coupling faults since they correspond to the manifestations of electromigration and OBD defects.

Defects introduced during chip fabrication are another source of hard faults. Their causes differ from those of operational hard faults, but they often manifest themselves in a similar fashion. For example, a fabrication defect could result in a discontinuity in a wire, which is equivalent to the situation in which electromigration leads to an open circuit. A fabrication defect could also lead to the growth of an insufficiently thick gate oxide, which is functionally equivalent to OBD. The impact of technology trends on fabrication defects is less clear than it is for operational faults. In general, though, smaller wire and device dimensions are more prone to defects, since the margin for error is smaller.

#### 2.1.2 Existing Fault Tolerance Techniques

A canonical design for autonomic operation is the IBM mainframe [66]. Mainframes not only have redundant processors, but they also incorporate redundancy within the processor in order to seamlessly tolerate hard faults. The IBM G5 microprocessor, for example, has redundant units for fetch/decode and for instruction execution. Some other traditional fault-tolerant computers, such as the Stratus [82] and the Tandem S2 [31], simply replicate entire processors. While these systems all provide excellent reliability, such heavyweight redundancy incurs significant costs in terms of hardware and power consumption.

As a low cost and low power alternative to heavyweight redundancy, DIVA [6] dynamically verifies an aggressive microprocessor core with a simple, provably correct checker core. DIVA sacrifices some amount of reliability in order to greatly reduce these costs. DIVA's small amount

of redundancy uses far less power than mainframe redundancy, but it incurs significant performance and energy penalties for each error that it must correct. Each error detected and corrected by the checker core triggers a pipeline flush of the aggressive core. Since DIVA was designed primarily for soft faults (not the hard faults we target), these flushes are not a performance problem. However, permanent faults in frequently accessed structures, such as the reorder buffer, will frequently manifest themselves as errors and will thus greatly degrade performance. Researchers have also proposed using redundant threads to achieve lightweight redundancy, primarily for soft faults. Of these schemes, the ones that perform recovery as well as error detection include AR-SMT [58], Slipstream [71], and SRTR [78]. All of these schemes share the same drawback as DIVA, with respect to hard faults, since they incur a pipeline squash (and its corresponding performance and energy penalty) every time a hard fault manifests itself. Redundant thread schemes, unlike DIVA, may not be able to guarantee forward progress in the presence of hard faults.

One option for array structures is to protect them with error correcting codes (ECC), as in IBM mainframes [66]. Combining ECC for arrays with DIVA avoids costly DIVA recoveries. However, ECC protection of arrays is on the critical path for array access (both read and write). Current ECC implementations can calculate ECC on a representative datum in 4 cycles on a 2 GHz Itanium2 [81]. Since ECC must be calculated on the microprocessor's critical path, a 4-cycle penalty per ECC calculation results in highly-degraded performance, even in the fault-free case. This lost performance makes ECC inappropriate for application in the timing-critical microprocessor pipeline.

With the advent of chip multi-processing (CMP) in commodity microprocessor designs, another hard-fault tolerance option is to disable any core that is detected to have a hard fault. While this works, we seek to provide a more cost-effective option than to lose 1/Nth (for an N-core design) of the chip's capacity for each hard fault that is detected. Aggarwal et al. [2, 3] extend this

idea to include other shared CMP structures, such as memory controllers and on-chip busses. In their presented methodology, a designer can add on-chip wiring complexity and mulitplexor delay to gain the ability to route around faulty shared components. Shivakumar et al. [64] propose a more cost-effective, fine-grained solution that utilizes inherent redundancy in CMP and SMT designs. This work is limited to manufacturing-time detection (i.e., testing) and deconfiguration. The methods that we present in this work, SRAS-CR, SRAS-EDC, and our new online fault diagnosis mechanism, provide a means for both manufacturing-time and in-situ operational detection and deconfiguration of sub-units within the microprocessor core, giving the designer additional options in designing for hard-fault tolerance.

Table 2-1 summarizes all of these techniques, including our SRAS-CR, SRAS-EDC, and online diagnosis (labeled Microarchitectural Redundancy Exploitation) designs. Included are the original fault-tolerance targets of the techniques (soft, hard, or design), and notes on the limitations of using these in a commodity microprocessor design. Note that our online fault isolation design extends previous work [2, 3, 64] to provide a finer-granularity of redundancy exploitation within the core.

As can be seen in the table, each technique has certain advantages and certain disadvantages. The characteristics of a given technique make it more or less appropriate for application to a given design space.

## 2.2 Self-Repairing Arrays

Technology and microprocessor architecture trends are leading towards larger array structures within microprocessors. These structures include the instruction queue, reorder buffer (ROB), register file, reservation stations, register map table, branch history table (BHT), etc. These structures

**Table 2-1. Fault Tolerance Techniques: Design Points and Limitations**

| Technique                                        | Primary Fault<br>Target(s) | Limitations of Use for Hard-Fault Tolerance In the<br>Microprocessor Core                                                                                            |

|--------------------------------------------------|----------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DIVA                                             | Soft, Design               | Excessive performance penalty for frequent pipeline flushes due to faults in frequently-accessed structures                                                          |

| Redundant                                        | Soft                       | May be subject to livelock                                                                                                                                           |

| Multithreading                                   |                            | Excessive performance penalty for frequent pipeline flushes due to faults in frequently-accessed structures                                                          |

| Triple Modular<br>Redundancy (TMR)               | Soft, Hard                 | Over 3x cost in terms of die area and power consumption over unprotected core design point                                                                           |

| CMP Core<br>Sparing                              | Hard                       | High performance penalty per hard fault (1 of $N$ cores) in designs where $N$ is relatively small                                                                    |

| ECC                                              | Soft, Hard                 | Adds excessive latency to critical path of microprocessor                                                                                                            |

|                                                  |                            | Only localized fault tolerance                                                                                                                                       |

| Microarchitectural<br>Redundancy<br>Exploitation | Hard                       | Manufacturing-time only, as described in [64], coarse-grained in [2, 3], extended in this work to include faults in the field at a finer granularity within the core |

|                                                  |                            | Only localized fault tolerance                                                                                                                                       |

| SRAS-CR                                          | Hard                       | Requires fault detection mechanism to trigger hard-fault tolerance                                                                                                   |

|                                                  |                            | Only localized fault tolerance                                                                                                                                       |

| SRAS-EDC                                         | Hard                       | Adds latency to fault-free operation of microprocessor                                                                                                               |

|                                                  |                            | Only localized fault tolerance                                                                                                                                       |

are the single-largest consumer of microprocessor core die area, comprising up to 33% of the area of microprocessor core (i.e., not including caches) in recent microprocessor designs [64]. We would like to protect these structures from hard faults as the probability of hard faults continues to increase, but we cannot afford to fully replicate these structures. Thus, our SRAS schemes protect array structures in a fashion similar to the way in which existing on-line (dynamic) techniques protect large memory storage structures. The basic idea is to use a level of indirection to map out faulty portions of the structure. Especially as structures grow larger, the probability of a hard fault within them increases. Disk sizes, for example, long ago reached the point at which hard faults were expected and had to be tolerated. Whole disk failures were addressed by RAID [52]. For disk faults that did not incapacitate the entire disk, the solution was to map out faulty portions at the

sector granularity. Thus, a faulty disk could continue to operate correctly in the presence of hard faults. Similar approaches have been developed for DRAM main memory. Whole chip failures are tolerated by chipkill memory and RAID-M [22, 27], and partial failures are tolerated with schemes that map out faulty locations [19, 44, 59]. For SRAM caches, techniques have been developed to map out defective locations during fabrication [84] and, more recently, during execution [49]. While providing insight for the use of spare memory locations for repair, direct application of the aforementioned methods to array structures within the processor bears little hope due to the performance criticality within microprocessors.

In the rest of this section, we discuss the arrays that we will protect (Section 2.2.1), and we present the design space for self-repairing arrays (Section 2.2.2). We then present two specific implementations (Section 2.2.3 and Section 2.2.6).

#### 2.2.1 Microprocessor Array Structures

We can classify array structures within the microprocessor core into two categories: non-addressable buffers for which the data location is determined at the time of access, and randomly addressable tables for which the data location is determined before access. In order to allow timing efficient implementation of the repair logic, we exploit these distinct features of each type of array structures. Without loss of generality, we focus the discussion of SRAS on one specific array structure from each of the two categories: the reorder buffer (ROB) and the branch history table (BHT). The ROB and BHT are representative of the kinds of array structures found in modern microprocessors, and thus the arguments and results here apply broadly.

#### 2.2.1.1 Reorder Buffer

The ROB is a circular buffer that is used in dynamically scheduled (a.k.a. "out-of-order") processors to implement precise exceptions by ensuring that instructions are committed in program

order. There is an entry in the ROB for each in-flight instruction, and there are pointers to the head and tail entries in the ROB. An entry is added to the tail of the ROB once it has been decoded and is ready to be scheduled. An entry is removed from the head of the ROB when it is ready to be committed. We focus on processors that perform implicit register renaming with reservation stations—such as the Intel PentiumPro, IBM PowerPC, and AMD K6—in which an ROB entry contains the physical register tags for the destination register and the data result of the instruction. When an instruction commits from the head of the ROB, the data in the head entry is written to the destination register. Alternative ROB designs exist, in which ROB entries do not hold the data results of completed instructions (data is instead held in the physical registers). Designing SRAS for these alternative designs is straightforward and actually simpler (but not discussed in this work).

ROB sizes are on the order of 32-128 entries, which is large enough to have a non-negligible probability of a hard fault. The ROB has a high architectural vulnerability factor [48], in that a fault in an entry is likely to cause an incorrect execution. A fault in an ROB entry is not guaranteed to cause an incorrect execution for its instruction, though, since the fault might not change the data (i.e., logical masking) or the ROB entry might correspond to a squashed instruction (i.e., functional masking).

### 2.2.1.2 Branch History Table

The BHT is a table that is accessed during branch prediction. Common two-level branch predictor designs [83] use some combination of the branch program counter (PC) and the branch history register (BHR) to index into a BHT. The BHR is a *k*-bit shift register that contains the results of the past *k* branches. The indexed BHT entry contains the prediction (i.e., taken or not taken, but not the destination). A typical BHT entry is a 2-bit saturating counter [65] that is incremented

(decremented) when the corresponding branch is taken (not taken). A BHT value of 00 or 01 (10 or 11) is interpreted as a not-taken (taken) prediction.

BHRs and/or BHTs can be either local (one per branch PC), global (shared across all branch PCs), or shared (by sets of branch PCs). In this paper, we focus on the gshare two-level predictor [45], in which the BHT is indexed by the exclusive-OR of the branch PC and a global BHR. Since the BHT is a table, our remapper implementation for it is fairly similar to the logical abstraction presented earlier. The BHT has an architectural vulnerability factor of zero, in that no fault in it can ever lead to incorrect execution. However, a BHT fault can lead to incorrect branch predictions, which can degrade performance.

## 2.2.2 Design Space

Self-repairing arrays require three features, and the designs of each collectively comprise the design space:

• Detection of errors and diagnosis of faults

How does the hardware detect an error in an array, and then how does it isolate which part of the array is faulty? While there are several schemes for dynamically verifying microprocessor execution as a whole [6, 55, 58], they sacrifice diagnosis capability in order to not degrade performance.

### • Recovery from errors

How does the hardware recover from an error such that it can ensure that the error does not propagate corrupted data into committed architectural state? The most basic option for recovery is to halt the system when an error is detected (fail-stop), thereby protecting system state from being corrupted, at the cost of more downtime and thus less availability. Other alternatives exist, such as using the microprocessor's branch misprediction recovery mechanism.

## • Mapping out faulty sub-arrays

Once the faulty sub-array (e.g., row, column) has been diagnosed, how does the hardware map it out and thus avoid future manifestations of this fault? The design choices for this aspect mainly involve the granularity of mapping, e.g., row, column, or even the whole array. Another design decision is the number of spares to provide. These design decisions may be influenced by the array's position in the microprocessor pipeline, particularly if accessing the array is on the critical path and performance is thus crucial.

There are numerous design decisions for each of these three aspects, but the decisions for each aspect are not completely independent. For example, ECC protection of arrays would serve as the detection and recovery mechanism, and it does not require remapping, provided that the errors do not exceed the correction abilities of the chosen correction code.

The design decisions, particularly for the recovery mechanism, also determine which array structures can be protected. For example, since SRAS-EDC uses the misprediction recovery mechanism, it thus cannot tolerate errors in the recovery state (i.e., committed architectural state, such as the register file or condition codes).

# 2.2.3 SRAS-CheckRow (SRAS-CR)

The first SRAS design that we present, SRAS-CheckRows (SRAS-CR) uses dedicated check rows to detect and diagnose errors in array rows. SRAS-CR protects each array structure in isolation, i.e., the decision to protect an array with SRAS does not affect the decision to protect any other array. We will see in Section 2.2.6 that SRAS-EDC differs in that it is an integrated approach for protecting multiple arrays.

## 2.2.3.1 Detection and Diagnosis

SRAS-CR uses DIVA for end-to-end error detection and correction. However, DIVA cannot isolate the row or even the structure that is faulty. Thus, SRAS-CR combines DIVA with a simple scheme for detecting row errors and diagnosing which row is faulty. SRAS-CR adds a handful of check rows (some are spares, which are used to avoid a single point of failure) to each structure we wish to protect. For buffer structures such as the ROB, each time an entry is allocated, initialization data is written to both the entry and the check row. This initialization data consists of the available target data for the entry (for example, the source and destination register tags for an ROB entry) and pseudo-random data for the parts of the entry that will be written later (for example, the actual result value for an ROB entry). Where pseudo-random data is needed, the tick counter is used, with appropriate scaling to provide the proper number of bits to fully populate the entry. For tables, every write to a location will have a mirrored write to the structure's affiliated check row. Any partial write to a row must be implemented as a read-modify-write (RMW) action in order to support SRAS-CR checking. The issue here is that the check row and array entry to be checked must have identical data written into their contents in order for a meaningful comparison to be made. Immediately after the two writes, both locations are read and their data are compared (all off the critical path of execution). If the data differ, then one of the rows is faulty. Several options exist for determining which one is faulty, and we will explain a simple one after we first describe the mechanism we exploit for distinguishing hard faults from soft faults. SRAS-CR maintains small saturating counters for each row, which are periodically reset, and a counter value above a threshold identifies a hard fault. Now, to determine if the operational row or the check row is faulty, we can simply increment both of their counters in the case of a mismatch in their values, as long as we initially set the threshold for check row counters to be much higher than that for operational rows.

Detection and diagnosis is the same for both tables and buffers. While we logically need only *k* check rows in a *k*-way superscalar processor to detect and diagnose faults, the SRAS-CR imple-

mentation may necessitate having even more check rows. Having only k check rows could lead to an unreasonably long delay to transfer the data along wires from one end of the array to the other. Wire delays are already a problem in multi-GHz microprocessors—for example, the Intel Pentium4 has multiple pipeline stages allocated strictly to wire delay—and we cannot ignore them in our design. A simple option is to divide the array into sub-arrays, each of which has k check rows.

#### 2.2.3.2 Recovery

If an error is detected, but the hard fault threshold has not yet been reached, then the fault is considered to be transient and it is tolerated with a DIVA recovery and its associated performance penalty. If the detected error raises the counter to the hard fault threshold, then DIVA also tolerates this fault, but the system then repairs itself so as to prevent this hard fault from being exercised again.

## 2.2.3.3 Mapping Out Faulty Sub-arrays

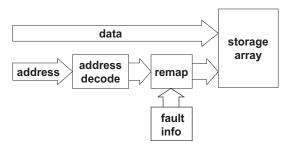

We logically add a level of indirection that can map out faulty rows in microprocessor array structures, as shown in Figure 2-3. The remapper serves as the interface between the array and the rest of the microprocessor.

The repair actions taken depend on whether the faulty row is a non-check row or a check row. If it is a non-check row, then it can be immediately mapped out and a spare row can be mapped in to take its place. The spare row can get the correct data from the check row. If the faulty row is a check row, then SRAS-CR maps in a spare check row.

While remapping with a level of indirection is straightforward in the abstract, implementing it in a high performance microprocessor pipeline requires careful consideration. We now present remapper implementations for the ROB and BHT.

Figure 2-3. Array Remapping

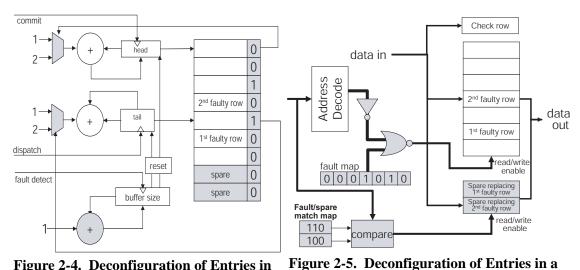

Figure 2-4. Deconfiguration of Entries in a Circular Buffer (e.g., Reorder Buffer)

**Tabular Structure (e.g., Reservation Station)**

deconfiguration purposes.

Shading indicates hardware added for entry Shading indicates hardware added for entry deconfiguration purposes.

## 2.2.3.3.1 ROB Remapper

In buffer structures, as in the case of the ROB, the address of the data to be accessed is determined at the time of the access. Typically, two pointers are used to mark the head and the tail location of the active rows. When a new ROB entry is allocated, the tail pointer is advanced and the corresponding address becomes the physical address of the data. Similarly, when an entry is removed, the head pointer is advanced. Thus, the physical as well as logical address of the data is abstracted and all rows have the same functionality. The faulty row can easily be mapped out by modifying the pointer advancement logic when a hard fault is detected. Figure 2-4 illustrates the implementation of the self-repair mechanism for buffers, with SRAS-CR hardware shaded in gray. SRAS-CR uses a shifted fault map bit-array to track faulty rows. If a row is determined to contain a hard fault, the faulty bit in the previous row is set to 1. The fault map is used by the pointer advancement circuit to determine how far the pointer needs to be advanced. Upon the reception of a dispatch signal, the pointer is advanced by one or two depending on whether the next row is fault or not. The shifted faulty row information enables the preprocessing of the pointer advance logic. Upon the reception of the commit signal, the head pointer is advanced in the same manner. Once the pointer is updated accordingly, reads and writes of the buffer entries proceed unmodified. Since the pre-processing for pointer advancement can be done off the critical path, the proposed modification does not impact the read or write access time.

In order to avoid a reduction in the effective buffer capacity due to hard faults, spare rows can be used. Since there is no need to replace the faulty row with any particular spare row, the detection of the faulty row prompts incrementing the total buffer capacity by one entry (by adding the spare) while maintaining the same effective capacity. SRAS-CR can tolerate as many hard faults as there are spares without any degradation of buffer performance. If the number of faulty rows exceeds the number of spare rows, then the effective buffer capacity is allowed to shrink, resulting in graceful degradation of the buffer performance. Assuming that adding one or two to the pointers does not dramatically change timing or power consumption, the only overhead of this repair mechanism is the small additional area taken by the fault map and the additional power consumed for pointer pre-processing, updating fault map entries, and updating the buffer size. Section 2.2.4 discusses the overall overhead of the complete SRAS-CR architecture in more detail.

#### 2.2.3.3.2 BHT Remapper

In tables, the logical address of the data is determined by the program execution prior to accessing the data. Since rows do not have equal functionality in tables, a faulty row needs to be replaced by a specific spare row. In this case, we need a logical indirection to map out the faulty rows. This problem is quite similar to the memory repair problem, and many on-line repair mechanisms have been proposed [11, 21]. However, in microprocessor array structures, logic inserted into the critical path directly impacts performance, so we must implement a timing-efficient repair mechanism. In SRAS-CR, we distribute spare rows over sub-arrays of the table, and a spare can only replace a row within its own sub-array. This choice may make the use of spares inefficient for highly localized faults, but it enables timing efficient implementation of the repair logic, as shown in Figure 2-5. Once again, hardware for SRAS-CR is shown in gray.

Similar to the buffer case, we keep the fault map information in a table. However, we also use a fault/spare match map which contains information on which functional row each spare row is replacing. If a row is identified faulty and an unused spare is found to replace it, the faulty entry of the row is set to 1. In addition, the physical address of the faulty row is written into the corresponding entry of the fault/spare match map. In the example shown in Figure 2-5, we can see that the 1st spare is allocated to the 6th entry and the 2nd spare is allocated to the 4th entry, hence the 1 in the fault map at the 6th position of the 1st column and the 4th position of the 2nd column. The address decode logic, which is present in all tables, enables a row of the table to be read or written by generating the individual read/write enable signals for the table rows. During a read or write access, these signals are modified by the remap logic to generate the updated read/write enable signals for the table entries as well as the read/write enable signals for the spare entries. The remap logic consists of n inverters and n 2-input NOR gates, where n is the size of the subarray. To generate the read/write enable signals for the spare rows,  $k \log(n)$  2-input XOR gates and the equivalent of k  $\log(n)$ -input NOR gates (denoted by the compare block in Figure 2-5) are needed, where k is the

number of spares assigned to the subarray. Note that, the fault/spare match map will contain one more bit than the physical address of the table to indicate whether the spare rows are active or not. This bit is not shown in the figure to avoid confusion with the address value.

Assuming the compare logic can execute faster than the address decode logic, SRAS-CR will add two gate delays (one INV and one NOR gate delay) to the table access time. Since the additional level of indirection for accessing the physical table entries is on the critical path, this additional time cannot be ignored. In order to avoid set-up or hold time violations, we very conservatively use a second pipeline stage to access the table entries. This additional pipeline stage will impose a penalty in the normal mode of operation. While we expect that the actual performance penalty would be far less than a pipeline stage (e.g., if BHT access latency is not the determining factor in pipeline stage latency), we choose this pessimistic design point as a lower bound on SRAS's benefit. In Section 2.4.1, we run experiments to assess the impact of this additional pipeline stage on the execution time in the absence of hard faults.

### 2.2.4 SRAS-CR Costs

The cost of a fault tolerance scheme has three aspects: hardware (area) overhead, performance (timing) overhead, and power consumption overhead. For aggressive microprocessor architectures, the performance overhead during fault-free execution is often the most critical parameter.

In order to keep the performance overhead at a minimum, buffers and tables are handled differently in SRAS. The distinct nature of buffers that makes all of their rows have equal functionality enables a no-timing-overhead implementation. Tables, however, require a definitive logical address for the data, which results in a need for an additional level of indirection. This indirection results in two gate delays in access times (e.g., for the Pentium4, an inverter delay is about 1-2% of the clock period [73]). Since gate delay will be larger than inverter delay, and since we cannot