# MEMORY REGION: A SYSTEM ABSTRACTION FOR MANAGING THE COMPLEX MEMORY STRUCTURES OF MULTICORE PLATFORMS

A Thesis Presented to The Academic Faculty

by

Min Lee

In Partial Fulfillment of the Requirements for the Degree Doctor of Philosophy in the School of Computer Science

Georgia Institute of Technology December 2013

Copyright © 2013 by Min Lee

# MEMORY REGION: A SYSTEM ABSTRACTION FOR MANAGING THE COMPLEX MEMORY STRUCTURES OF MULTICORE PLATFORMS

## Approved by:

Professor Karsten Schwan, Advisor School of Computer Science Georgia Institute of Technology

Professor Sudhakar Yalamanchili School of Electrical and Computer Engineering Georgia Institute of Technology

Professor Ada Gavrilovska School of Computer Science Georgia Institute of Technology Professor Sham Navathe School of Computer Science Georgia Institute of Technology

Dr. Rob F Van Der Wijngaart Intel Corporation

Date Approved: October 31, 2013

This dissertation is dedicated to my wife, Hyunsuk Kim.

## ACKNOWLEDGEMENTS

It has been a great privilege to spend several years at the Georgia Institute of Technology. I still remember the day when I arrived at the Atlanta airport, but now it's already time to leave the school. Atlanta has become a special city to me, where I met my wife, started my Ph.D. program, and where my son was born. I will always miss Atlanta, and Georgia Tech, and all the good days I have spent there.

It was my pleasure to meet all of my great friends and fellow students – Minsung Jang, Minjang Kim, Jingu Kim, Vishakha Gupta, Mukil Kesavan, Vishal Gupta, Priyanka Tembey, Hrishikesh Amur, Chengwei Wang, Fang Zheng, Alex Merritt, and many others.

I'd like to thank my committee members, Professor Sudhakar Yalamanchili, Professor Ada Gavrilovska, Professor Sham Navathe, and Dr. Rob F Van Der Wijngaart for all of their help. I have been fortunate to work with them. Special thanks to Dr. Rob F Van Der Wijngaart for his warm support and assistance.

Above all, I would like to express my sincere gratitude to my advisor Prof. Karsten Schwan for his continuous support of my Ph.D. studies and research. He has always supported me and guided me whenever I was struggling with various problems. My idea about the memory-centric scheduler has been guided by him, and he always helped me understand the systems perspective in pursuing it. Thank you for all for your support.

Also I thank Rob Knauerhase at Intel for accepting me as an intern. I thank A. S. Krishnakumar, P. Krishnan, Navjot Singh, Shalini Yajnik at Avaya Labs, as well. It was my privilege to be able to work with you.

I would never have been able to finish my dissertation without the guidance of

my advisor, Karsten Schwan, help from my friends, and support from my family and wife. I would like to thank all of them. Most of all, I dedicate this dissertation to my wife, Hyunsuk Kim. Without her support and encouragement, this work would not have been possible.

# TABLE OF CONTENTS

| DE            | DIC  | ATIO   | N                                | iii  |

|---------------|------|--------|----------------------------------|------|

| AC            | CKNO | OWLE   | DGEMENTS                         | iv   |

| LIS           | вт о | F TAE  | BLES                             | ix   |

| LIS           | вт о | F FIG  | URES                             | x    |

| $\mathbf{SU}$ | MM.  | ARY .  |                                  | xiii |

| Ι             | INT  | rodi   | UCTION                           | 1    |

|               | 1.1  | New I  | Execution Model                  | 1    |

|               | 1.2  | Region | n Scheduling                     | 2    |

|               | 1.3  | Disagg | gregated OS Services             | 6    |

|               | 1.4  | Memo   | bry Heterogeneity                | 6    |

| II            | RE   | GION   | SCHEDULING                       | 8    |

|               | 2.1  | Introd | luction                          | 8    |

|               | 2.2  | Region | ns                               | 12   |

|               |      | 2.2.1  | Software Framework and Methods   | 12   |

|               |      | 2.2.2  | Life Cycle of a Memory Region    | 15   |

|               |      | 2.2.3  | Region Scheduling Implementation | 17   |

|               | 2.3  | Region | ning                             | 25   |

|               |      | 2.3.1  | Cache Unification                | 26   |

|               |      | 2.3.2  | Bottom-up Regioning              | 29   |

|               |      | 2.3.3  | Region Types                     | 31   |

|               |      | 2.3.4  | Global Regions                   | 34   |

|               | 2.4  | Worki  | ng Set Tracking                  | 35   |

|               | 2.5  | Exper  | imental Evaluation               | 36   |

|               |      | 2.5.1  | Overhead                         | 37   |

|               |      | 2.5.2  | Microbenchmarks                  | 38   |

|               |      | 2.5.3  | SPEC Benchmarks                  | 40   |

|     |     | 2.5.4  | Media Benchmark                   | 46 |

|-----|-----|--------|-----------------------------------|----|

|     |     | 2.5.5  | Cache Sharing                     | 47 |

|     |     | 2.5.6  | Reducing Noise for Parallel Codes | 48 |

|     | 2.6 | Relate | ed Work                           | 50 |

|     | 2.7 | Conclu | usions And Future Work            | 51 |

| III | DIS | AGGI   | REGATED OS SERVICES               | 53 |

|     | 3.1 | Introd | luction                           | 53 |

|     |     | 3.1.1  | Kernel Disaggregation             | 54 |

|     | 3.2 | Memo   | ry-centric Scheduling             | 57 |

|     |     | 3.2.1  | Region scheduler                  | 57 |

|     |     | 3.2.2  | Regioning                         | 58 |

|     | 3.3 | Guest- | -defined Region                   | 58 |

|     | 3.4 | Load 1 | Balancer Conflict                 | 61 |

|     | 3.5 | Micro- | -Benchmarks                       | 66 |

|     |     | 3.5.1  | Kernel cores                      | 67 |

|     |     | 3.5.2  | File system cores                 | 74 |

|     |     | 3.5.3  | Discussion                        | 76 |

|     | 3.6 | Globa  | lization                          | 81 |

|     |     | 3.6.1  | VM Consolidation                  | 81 |

|     | 3.7 | Evalua | ation                             | 82 |

|     |     | 3.7.1  | Memcached                         | 82 |

|     |     | 3.7.2  | VM Consolidation                  | 84 |

|     | 3.8 | Relate | ed Work                           | 87 |

|     | 3.9 | Conclu | usions And Future Work            | 87 |

|     |     | 3.9.1  | Discussion                        | 88 |

| IV  | ME  | MORY   | Y HETEROGENEITY                   | 91 |

|     | 4.1 | Introd | uction                            | 91 |

|     |     | 4.1.1  | Heterogeneous memory              | 95 |

|   | 4.2 | Heterogeneous Memory Management      | 98 |

|---|-----|--------------------------------------|----|

|   |     | 4.2.1 Memory Access Tracking         | 98 |

|   |     | 4.2.2 Memory Allocation Policy       | )7 |

|   | 4.3 | Experimental Evaluation #1           | )8 |

|   |     | 4.3.1 Heterogeneous Memory Emulation | )8 |

|   |     | 4.3.2 Workloads                      | .0 |

|   |     | 4.3.3 Results                        | .0 |

|   | 4.4 | Experimental Evaluation #2           | .2 |

|   |     | 4.4.1 Experimental Setup             | .2 |

|   |     | 4.4.2 Workloads                      | .3 |

|   | 4.5 | Related Work                         | .7 |

|   | 4.6 | Conclusions And Future Work          | .7 |

| V | CO  | NCLUSIONS AND FUTURE WORK            | 0  |

|   | 5.1 | The Memory Region                    | 20 |

|   | 5.2 | Hardware Support and Codesign        | 21 |

|   | 5.3 | Conclusions and Future Work          | 23 |

|   | T 4 |                                      | _  |

## LIST OF TABLES

| 1 | System-level representation of regions      | 20  |

|---|---------------------------------------------|-----|

| 2 | Regioning process                           | 32  |

| 3 | APIs for guest-defined region               | 61  |

| 4 | Three PHP codes for dynamic page generation | 82  |

| 5 | VM Consolidation                            | 84  |

| 6 | Hot page management actions                 | 102 |

| 7 | Three PHP codes for dynamic page generation | 108 |

| 8 | Workload summary                            | 111 |

| 9 | page migration evaluation using memlat      | 112 |

## LIST OF FIGURES

| 1  | Unbalanced cache usage                                   | 3 |

|----|----------------------------------------------------------|---|

| 2  | VCPU view                                                | 4 |

| 3  | VCPU view                                                | 5 |

| 4  | Xen and region framework                                 | 3 |

| 5  | Physical pages and regions                               | 3 |

| 6  | Life of region – born                                    | 6 |

| 7  | Life of region – new process                             | 7 |

| 8  | Life of region – shared region                           | 8 |

| 9  | Life of region – another process with bigger working set | 8 |

| 10 | Life of region – death                                   | 9 |

| 11 | How regions interact with caches and address spaces      | 9 |

| 12 | Page touch and cache switch                              | 1 |

| 13 | Per-cache page table                                     | 2 |

| 14 | Microscheduling with 1VCPU                               | 3 |

| 15 | Microscheduling with 4 VCPUs                             | 4 |

| 16 | Mappings among regions, caches, and VCPUs                | 4 |

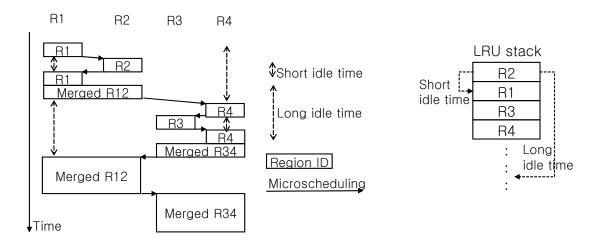

| 17 | Two region memlats access and idle times                 | 6 |

| 18 | Two-region memlat across caches                          | 7 |

| 19 | Cache working sets and cache sizes                       | 9 |

| 20 | Regioning run $(p = 1\%)$                                | 0 |

| 21 | Regions and region merging via LRU stack                 | 0 |

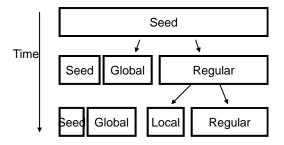

| 22 | Types of regions                                         | 2 |

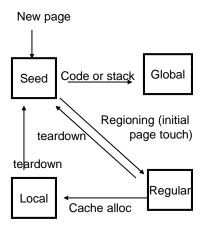

| 23 | Region state transitions                                 | 2 |

| 24 | System view                                              | 3 |

| 25 | Portion of shared pages                                  | 4 |

| 26 | Access bit history and regions working set size          | 5 |

| 27 | Tracking working set size                                | 6 |

| 28 | Overhead                                         | 37 |

|----|--------------------------------------------------|----|

| 29 | Speedup with cache balancing                     | 39 |

| 30 | Cache-unification for two-region memlat          | 39 |

| 31 | SPEC 2006 memory accesses                        | 41 |

| 32 | SPEC 2006 regioning                              | 42 |

| 33 | SPEC benchmark cache unifying                    | 43 |

| 34 | Micro-scheduling rates on Clovertown             | 44 |

| 35 | Regioning details (Clovertown)                   | 45 |

| 36 | Asterisk server and clients                      | 46 |

| 37 | Media server+SPEC consolidation on Clovertown    | 47 |

| 38 | Parallel code VM consolidated with SPEC VM       | 49 |

| 39 | User/Kernel cores and caches                     | 56 |

| 40 | Region layer and CPU scheduler                   | 57 |

| 41 | Region scheduling                                | 57 |

| 42 | Guest-defined regions                            | 59 |

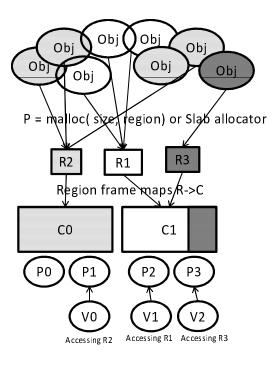

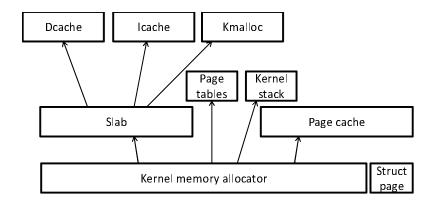

| 43 | Linux memory and slab allocator                  | 60 |

| 44 | Load balancer conflict                           | 63 |

| 45 | Load balancer conflict                           | 64 |

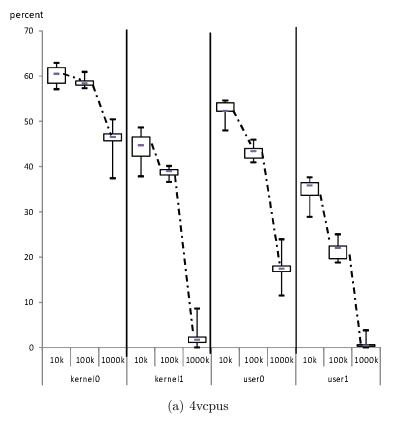

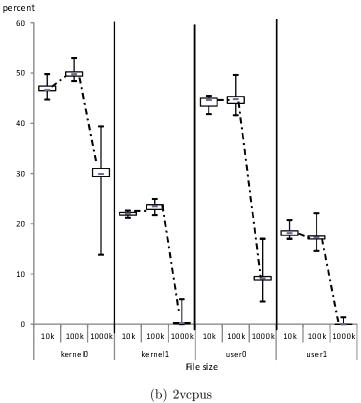

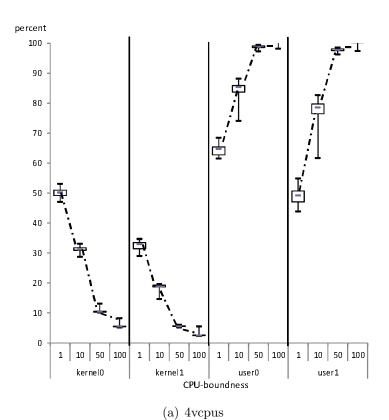

| 46 | Web-static CPU utilization                       | 68 |

| 47 | Web-static stats                                 | 69 |

| 48 | Web-php CPU utilization                          | 70 |

| 49 | Web-php stats                                    | 72 |

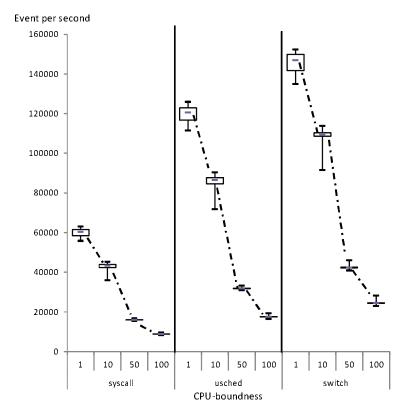

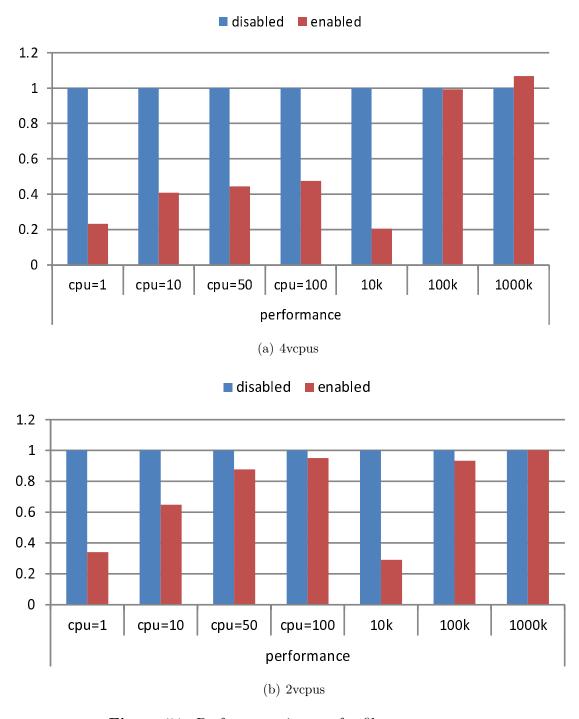

| 50 | Performance impact                               | 73 |

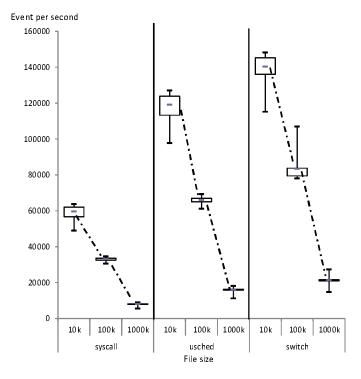

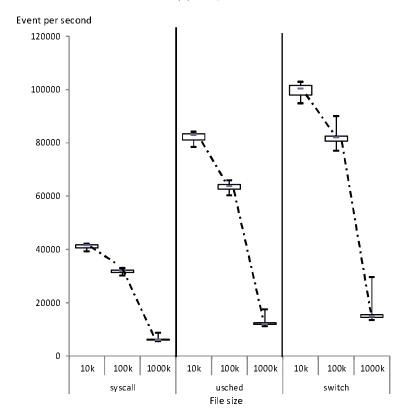

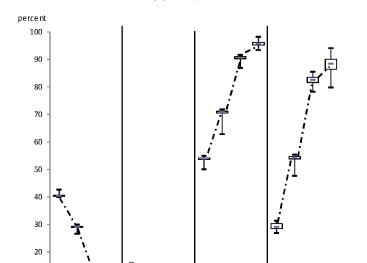

| 51 | Performance impact for file system core          | 75 |

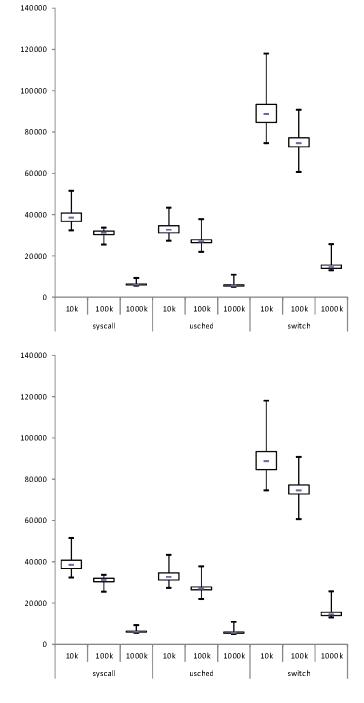

| 52 | Reduced usched (file system core)                | 77 |

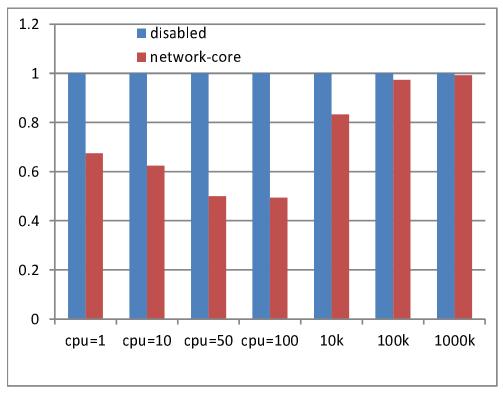

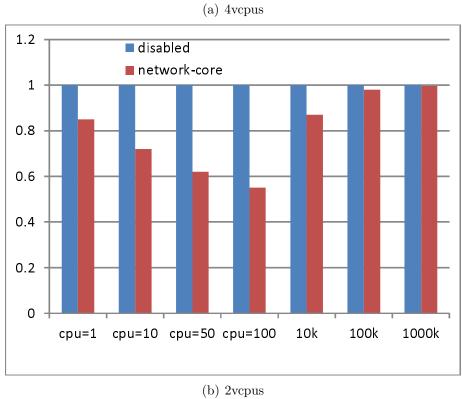

| 53 | The case of network core                         | 78 |

| 54 | The case of file system and network (fsnet) core | 79 |

| 55 | API call overhead                                | 80 |

| 56 | Single VM. WordPress+memcached                   | 83 |

| 57 | VM consolidation                                                                     | 85  |

|----|--------------------------------------------------------------------------------------|-----|

| 58 | Performance impacts                                                                  | 86  |

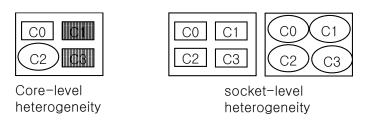

| 59 | Platforms consisting of heterogeneous resources                                      | 89  |

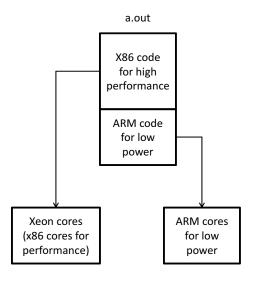

| 60 | Runs across heterogeneous ISA architecture                                           | 90  |

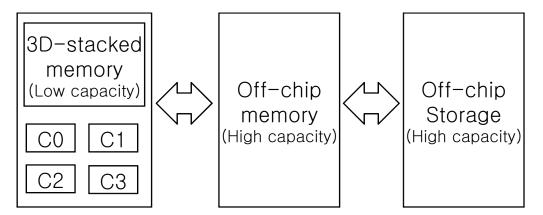

| 61 | Hetero memory                                                                        | 94  |

| 62 | Tracking hot pages using access-bits                                                 | 99  |

| 63 | Tracking virtual time                                                                | 100 |

| 64 | Extended frame table with a-bit history and reverse maps                             | 101 |

| 65 | Hot page management and associated actions                                           | 104 |

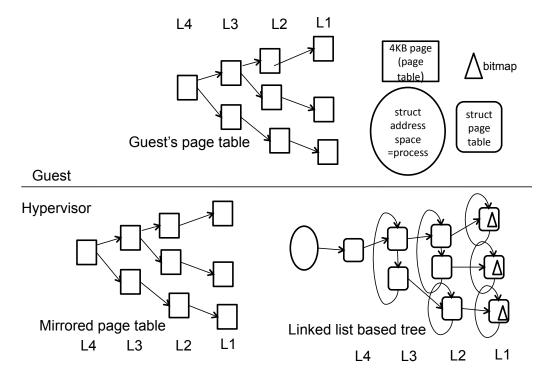

| 66 | Page table mirroring and linked-list-based tree for quick scan                       | 105 |

| 67 | WSS curve for SPEC CPU2006                                                           | 108 |

| 68 | Histograms of pages and corresponding access counts                                  | 109 |

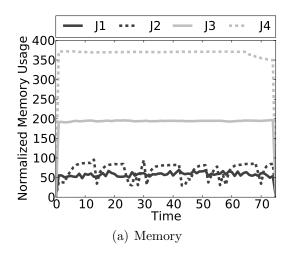

| 69 | Workload traces based on Google cluster data [59]                                    | 113 |

| 70 | Impact of memory performance on several data<br>center applications $\ .$ .          | 114 |

| 71 | Working set size detection using access-bit history                                  | 114 |

| 72 | Impact of the fine-grained memory scaling on the performance of memstore application | 115 |

| 73 | Experimental results for memory E-state scaling                                      | 116 |

#### SUMMARY

The performance of modern many-core systems depends on the effective use of their complex cache and memory structures, and this will likely become more pronounced with the impending arrival of on-chip 3D stacked and non-volatile off-chip byte-addressable memory. Yet to date, operating systems have not treated memory as a first class schedulable resource, embracing memory heterogeneity. This dissertation presents a new system abstraction, called 'memory region', which denotes the current set of physical memory pages actively used by workloads. Using this abstraction, memory resources can be scheduled for applications to fully exploit a platform's underlying cache and memory system, thereby gaining improved performance and predictability in execution, particularly for the consolidated workloads seen in virtualized and cloud computing infrastructures. The abstraction's implementation in the Xen hypervisor involves the run-time detection of current memory regions, the scheduled mapping of those regions to caches to match performance goals, and maintaining region-to-cache mappings using per-cache page tables.

This dissertation makes the following contributions. First, its region scheduling method proposes that the location of memory blocks, rather than CPU utilization is the principal determinant for where workloads are run. It develops a new scheduling method, region scheduling, which determines the placement of memory blocks to the caches associated with workloads' processors. Second, treating memory blocks as first-class resources, new methods for efficient cache management are shown to improve application performance as well as the performance of certain operating system functions. Third, explicit memory scheduling makes it possible to disaggregate

operating system functions, without the need to change OS sources and with only small markups of a target guest OS. With this method, OS functions can be mapped to specific desired platform components, an example being a file system confined to running on specific cores and using only certain memory resources designated for its use. This can improve performance for applications heavily dependent on certain OS functions, by dynamically providing those functions with the resources needed for their current use, and it can prevent performance-critical application functionality from being needlessly perturbed by OS functions used for other purposes or by other jobs. Fourth, extensions of region scheduling can also help applications deal with the heterogeneous memory resources present in future systems, including on-chip stacked DRAM and NUMA or even NVRAM memory modules. More generally, regions scheduling is shown to apply to memory structures with well-defined differences in memory access latencies.

## CHAPTER I

## INTRODUCTION

As heterogeneous and many-core architectures are emerging, new approaches are required to obtain performance scalability in liey of their complex memory subsystems.

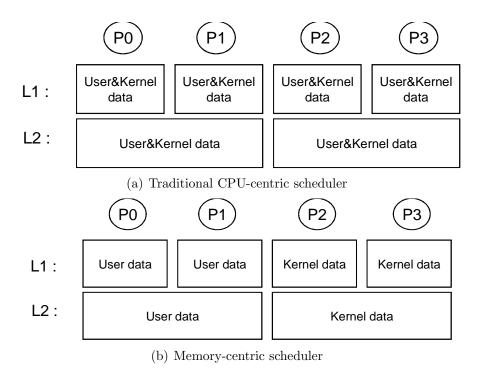

On modern computer systems, memory subsystems like caches are extremely important for application performance. Contrasting existing practice in operating systems with their focus on CPU scheduling, this thesis posits that the memory subsystems in future multicore systems should be treated as first-class schedulable resources. Departing from traditional CPU-centric scheduling, we propose memory-centric scheduling methods for using the caches and other components of future memory subsystems. In doing so, we ensure careful consideration of memory subsystem characteristics like NUMAness (non-uniform memory access-ness), and we anticipate future different types of memory, such as on-chip stacked DRAM or NVRAM (non-volatile RAM), which are emerging as cost-effective alternative to current DRAM memory configurations.

## 1.1 New Execution Model

This thesis contributes a software approach that embraces future memory systems with a new programming and runtime abstraction, termed 'memory region'. In doing so, it contributes an execution model that moves computation to where data is located, vs. the traditional model of moving data to where the computation occurs. The model is motivated by the fact that in the mult-core era, data movements are expensive, inhibiting performance scalability. The alternative memory-centric execution model developed in our work schedules data placements and then moves computation to where data is located. Its strengths include the following. First, it can efficiently

use caches because by eliminating duplicate cache lines and avoiding cache coherency traffic. This can increase the effective cache sizes seen by application. Second, it avoids data movements by moving small computation contexts vs. larger data footprints, also benefiting system power usage. Its potential weaknesses addressed in this thesis are (i) frequent migration of execution threads, requiring controls on migrations to limit consequent runtime overheads, and (ii) the need to carefully place data across a platform's memory hierarchy.

Concretely, the 'memory region' software abstraction introduced, developed, and used in this thesis may be defined as a set of physical memory pages with good spatial and temporal locality. We next outline the development and use of this abstraction in the remainder of this thesis.

## 1.2 Region Scheduling

Region scheduling can be viewed as a cache-aware scheduler for the CMP environment, where the last level cache is performance-critical, but even on modern processors, is not typically well utilized. This has caused hardware researchers to propose approaches like Adaptive Spill-Receive [120], NUCA (non-uniform cache architecture)[119], or Intel's smart cache [118]. Unfortunately, such approaches are limited in their ability to predict workloads' cache behavior. The region scheduling methods developed in this thesis constitute a novel, software-based approach to detecting a workload's cache footprint and then using that information to better schedule the workload.

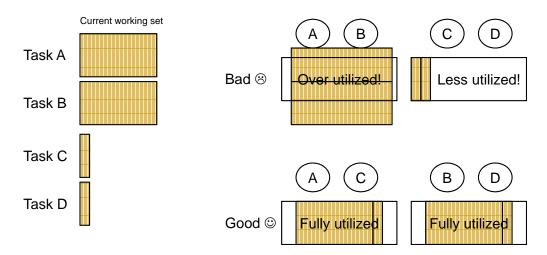

Figure 1 depicts a simple scenario in which the two LLCs (last level caches) present on a SMP platform are not well utilized. Assume there are 4 tasks A, B, C, and D, where A and B have large working sets that fit into one LLC, while C and D have very small working sets. Existing CPU schedulers might well schedule A and B onto cache-sharing CPU cores, resulting in one LLC being over-utilized, the other being

Figure 1: Unbalanced cache usage

under-utilized. This is because a scheduler that is not aware of workloads' working set sizes will schedule tasks based on CPU utilization rather than their efficient cache usage. An easy remedy for this situation, of course, is to schedule tasks A and C onto the same cache-sharing CPU cores.

The purpose of region scheduling is to schedule tasks in cache-efficient ways. To do so requires online information about workloads' working sets, to answer questions about (i) how large of these working sets, (ii) what are they comprised of, e.g., what pages do they contain, and (iii) how much content do they share?. The 'regions' identified in this work constitute such information, which is then used to appropriately schedule the tasks using them.

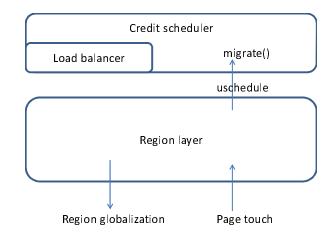

Region scheduling is implemented for virtualized systems using the popular Xen open source hypervisor, to realize guest-level online cache management and scheduling. Its use can substantially improve application performance and in addition, it provides hypervisor with new abilities to control guests' memory accesses.

In the remainder of this thesis, we first introduce the memory region abstraction and region scheduling. Its basic goal is to move computation to data vs. moving data to where computations are run. While this runs counter to traditional cache and memory subsystem designs that move data to where computations take place,

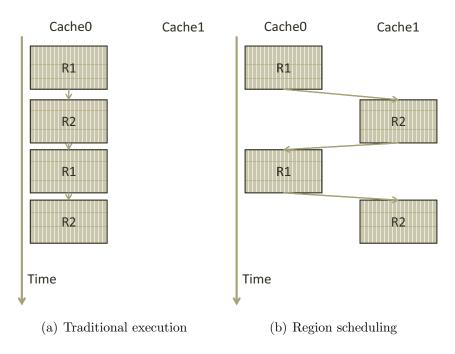

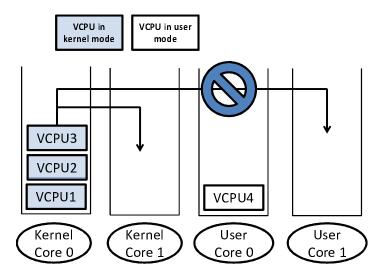

Figure 2: VCPU view

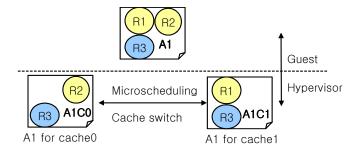

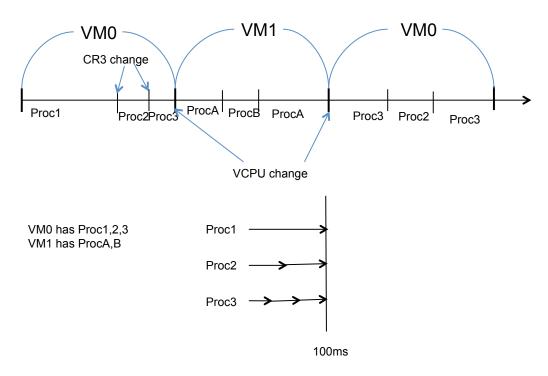

the approach is justified by several architecture trends. First, on modern processor architectures, the expense of data movement continues to increase relative to the cost of computation. Second, data movement is subject to problems like ping-ponging and false sharing, and such problems are aggrevated by the fact that the hardware level is not informed about software decisions like work migration across different runqueues. Specifically, if software (e.g., the load balancer) moves a task that has run for a while on one cache to another cache's core, the task will experience cache misses to warm up the new cache, involving large numbers of cache line movements. Region scheduling avoids such issues by using appropriate, higher level information about tasks to reduce the effects of load balancing, to better balance the performance benefits of task migration against the costs such migrations incur. We next outline the concept of microscheduling used in the region scheduling approach, but refer the reader to the next chapter for additional detail.

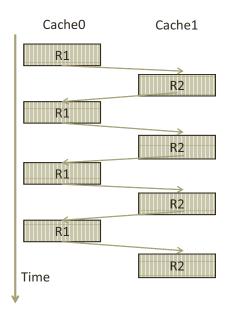

Figure 2 shows how tasks are run when controlled by the region scheduler. Unlike the traditional execution model 2a, the execution under region scheduling controls

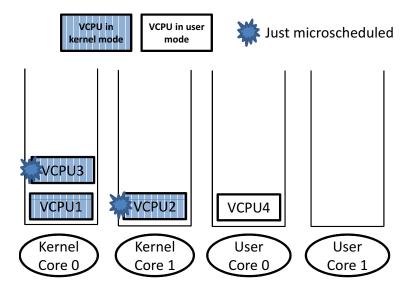

Figure 3: VCPU view

where tasks are run based on what data, i.e., which memory regions, they touch, e.g., for region switches such as R1->R2. In this context, microscheduling (usched) is defined as a switch to some region located in a different cache, initiated in response to a page touch of a page in that region. It is the page touch that triggers a page fault, due to illegal access to memory resident on a 'not-allowed' cache that triggers microscheduling. Page touch faults are handled by the hypervisor, along with appropriately setting page protection information to cause page faults as and when needed.

Figure 3 depicts the effects of frequent microscheduling. Since the overhead of microscheduling increases with short access times to a region, the effectiveness of microscheduling is governed by region access times. If those access times are too short, frequent microscheduling results in increased overhead. The challenge, therefore, is to create regions with suitably large access times but with sufficiently small granularity to capture a workload's current cache behavior. Region creation, therefore, is an inherent component of the region scheduling approach.

## 1.3 Disaggregated OS Services

An interesting side-effect of our ability to map certain pages to certain caches is the resulting control over the data structures contained in those pages. For operating system data structures and the services using them, this means that with region scheduling, we can directly and without the need to rewrite them, control where certain services are run. The outcome is kernel service disaggregation, to isolate some services from the effects of others and/or to protect applications from OS service activities on the cores and caches they use. Sample OS services considered in our work are file systems, networks, and scheduling, with experimental results obtained for file system and network services. For example, if the file system's inode data structures are mapped to one specific cache, file system calls are serviced only through the core group that shares that cache. We implement OS service disaggregation as a natural extension to the region scheduler, to cover all of a guest's memory, including its kernel data structures. The outcome is per guest application-level regioning coupled with kernel level service disaggregation.

In this chapter, the region framework is extended to cover the OS kernel space, and we explore not only page-to-cache mappings but also the appropriate mapping of meaningful kernel objects to pages. Object to page mappings are established via hypercalls informing the region scheduler.

## 1.4 Memory Heterogeneity

As new memory technologies are emerging [96], researchers have begun to study the resulting heterogeneous memory systems and their characteristics [97], with goals that include obtaining lower memory latencies and higher access bandwidths. While cost-effective, such new technologies pose challenges to operating systems regarding their effective use. This thesis explores the space of heterogeneous memory by developing a memory management scheme based on the region abstraction. Using

3D-stacked DRAM as target heterogeneous memory, with its greater bandwidth and lower latency compared to off-chip DRAM, region-based memory management aims to make best use of limited 3D DRAM capacity in conjunction with large, but slower off-chip DRAM. Specifically, the region concept is used to identify 'hot' memory pages, automatically and without user or system input, and it is those hot pages that are moved to 3D DRAM, via software-based data movement implemented in the hypervisor. Memory regions, thus, are the concept needed to identify sets of hot pages, with region movements implemented by software. Implementation of this functionality required extensions of the region scheduling framework, including hot page tracking, page movements performed in ways that are transparent to guest VMs and applications, and automation of such movements in ways that benefit application performance. An interesting side effect of this work is the ability to better manage the memory resources used by individual VMs. With current hypervisor implementations, e.g., in Xen, a single VM's memory must reside in some specific 'memory node' (there are NUMA generalizations of Xen, but those do not give explicit control to programmers [125]. Using the re-mapping methods implemented for region scheduling provides systems with the finer-grain controls needed to map VM memory to wherever appropriate.

## **CHAPTER II**

## REGION SCHEDULING

## 2.1 Introduction

The performance of modern many-core platforms strongly depends on the effectiveness of using their complex cache and memory structures. This indicates the need for a memory-centric approach to platform scheduling, in which it is the locations of memory blocks in caches rather than CPU idleness that determines where application processes are run. Using the term memory region to denote the current set of physical memory pages actively used by an application, this chapter presents and evaluates region-based scheduling methods for multicore platforms. This involves (i) continuously and at runtime identifying the memory regions used by executable entities, and their sizes, (ii) mapping these regions to caches to match performance goals, and (iii) maintaining region to cache mappings by ensuring that entities run on processors with direct access to the caches containing their regions. Region scheduling can implement policies that (i) offer improved performance to applications by unifying the multiple caches present on the underlying physical machine and/or by balancing cache usage to take maximum advantage of available cache space, (ii) better isolate applications from each other, particularly when their performance is strongly affected by cache availability, and also (iii) take advantage of standard scheduling and CPUbased load balancing when regioning is ineffective. This chapter describes region scheduling and its system-level implementation and evaluates its performance with micro-benchmarks and representative multi-core applications. Single applications see performance improvements of up to 15\% with region scheduling, and we observe 40\% latency improvements when a platform is shared by multiple applications. Superior isolation is shown to be particularly important for cache-sensitive or real-time codes.

For modern computer architectures, memory access times and caching effectiveness are key determinants of program and system performance. This is evident not only from a rich set of research on caches in computer architecture [12, 13, 14, 15, 18, 19, 20, 21, 22, 23], but also from the wide variety of cache structures found on modern multi- and many-core platforms, ranging from single last level caches shared by from 2 (e.g., in Intels Dual-core Xeon chips) to 8 cores (e.g., in Intels Nehalem chips), to the distributed caches seen in the Larrabee chip [1].

Recognizing the importance of caching, modern methods for thread scheduling take into account cache affinity [9], avoid cache thrashing [10, 11], and/or carefully select the threads that are permitted to share a common cache [2, 3]. Leveraging such insights and in expectation of the increased importance of memory structures to the performance of future multicore platforms, our research is exploring a new approach that departs from prior process- or thread-centric scheduling methods to instead, create a memory-centric scheduler that first allocates to caches the sets of pages used by executable entities and then schedules those entities to the processors that use those caches. The schedulable sets of memory pages are termed memory regions, defined as the sets of physical pages within address spaces that currently exhibit good locality, which means that an executable entity spends significant time within each such page set region before changing its locality to reside elsewhere, i.e., in another region.

Making regions first class entities states as an explicit goal the optimization of how memory is accessed, by controlling the map-pings of regions to caches. Region-based scheduling:

- tracks the regions (and their associated physical pages) being used by each executable entity; where

- each entity can have multiple regions, but at any one time, a physical page

resides in exactly one region;

- regions are mapped onto caches by system-defined mapping policies; and

- the system enforces the resulting cache-centric constraints on executable entities like processes.

This chapter presents a hypervisor-level implementation of region-based scheduling in which the VMM identifies and tracks the memory regions used in each address space, estimates working set sizes and consequent cache occupancies, and then maps regions onto caches. Mapping policies can minimize duplicate cache lines and/or cache contention or interference (e.g., to lower cache misses [32] or to improve isolation or reduce interference [26]), or they can balance cache usage across multiple processes. To attain these ends, three different scheduling policies are devised and evaluated in this chapter: (1) cache-balancing, where the system ensures high aggregate performance for the current processes running on a multi-core platform, (2) cache unification, in which the different regions used by a process are distributed across multiple caches to maximize the performance of cache-sensitive codes, and (3) cache partitioning, where software methods approximately partition the caches used by different processes to reduce interference or improve isolation. With region scheduling, it is also possible to unfairly allocate caches across different processes, perhaps to provide additional cache space to those that need it, but other than to demonstrate improvements in isolation, we do not further experiment with such techniques in this chapter.

In order to make its performance advantages available to arbi-trary applications and operating systems, region-based scheduling is implemented at hypervisor level, controlling VCPU to PCPU mappings and interacting with the hypervisors page table structures (using the Xen open source hypervisor [27]). An alternative operating system-level implementation would apply region sched-uling methods to the processes and their address spaces manipulated by OS schedulers and memory managers (i.e.,

via page tables).

The outcome is a system with the following properties:

- cache-awareness the hypervisor understands the cache structure of the underlying machine, i.e., it knows which caches are associated with which P(hysical)CPUs;

- runtime region tracking low overhead runtime methods identify and track the memory regions used by the address spaces in virtual machines;

- region-based scheduling maps the V(irtual)CPUs used by a VM to PCPUs so as to match the VMs region mappings to cach-es; and performs runtime micro-scheduling, which forces a VCPU-PCPU switch to prevent the hardware from re-mapping a region when it is accessed from a PCPU associated with a different cache.

Finally, region scheduling strictly improves upon existing cache-unaware scheduling methods like those used in Unix or implemented in current hypervisors. This is because their imple-mentation reverts to unaware methods whenever regioning is deemed ineffective.

We evaluate the performance implications of region-based scheduling with representative multi-core and server applications. Experiments with the SPEC benchmark suite diagnose the potential utility and limitations of region scheduling, resulting in runtime conditions based on which we determine when region scheduling should revert to Xens standard credit-based methods. Significant performance improvements are seen for VMs running memory- and cache-intensive codes, in part by mapping their regions in ways that better leverage the combined cache sizes of multiple on-chip caches, termed cache unification. More predictable levels of performance due to improved isolation are observed for server applications with strong constraints, such as parallel codes using barriers [26] and the enterprise level VoIP codes [25] (e.g., achieving up to 40% response time improvement for the latter).

We view region-based scheduling as a first step toward design-ing schedulers that recognize the importance, if not predominance, of cache and memory structures for the performance of future multi-core applications. Complementing prior work on NUMA awareness in operating systems or hypervisors [28], region sched-uling offers system-level methods that improve and control application performance by explicitly managing their cache usage, without requiring additional hardware support [23] or inputs from applications [29]. Region scheduling can also be viewed as a first step toward systems that better support modern compiler runtimes that wish to explicitly manage the memory units places used by applications [30].

In the remainder of this chapter, Section 2.2 describes the software architecture underlying the region scheduling approach, called the region framework. Section 2.3 presents the analysis regarding regioning process. It establishes the region tracking algorithm, and working set tracking is presented in Section 2.4. Next, Section 2.5 presents performance evaluations. Section 2.6 details related work. The last Section 2.7 summarize results and future work, including speculations on potential hardware support to reduce tracking costs.

## 2.2 Regions

This section explains regions and the page touch methods used to implement region tracking, micro-scheduling, and the mapping of regions to caches.

### 2.2.1 Software Framework and Methods

A region is a set of physical pages. Regions partition memory, since at any one time; each page can belong to only one region. A region is private when its pages are accessible from only one address space, with typical private regions being those that contain heap or stack data. Shared regions, i.e., those shared among multiple address spaces, usually contain shared pages like code. Region scheduling addresses private regions, whereas shared regions are handled by standard caching hardware.

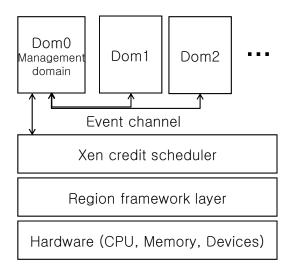

Figure 4: Xen and region framework

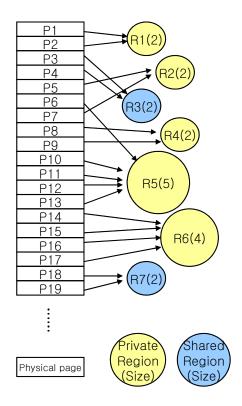

**Figure 5:** Physical pages and regions. (Size) is the number of pages that belong to (static) or the measured working set size at run time (dynamic).

Region-based scheduling explicitly places private regions into caches. Such mappings are maintained by having the scheduler restrict from where the regions pages can be accessed, in ac-cordance with the hardware-level association of caches with PCPUs. Access restrictions are based on specifications associated with page tables, which state, for instance, that the physical frame numbers in a region, say, 10, 11, and 12, shall be accessed only through PCPUs 0 or 2 (on our machine, both of these share access to the same cache). With such specifications, we must ensure that a region can only be accessed through the cache to which it has been mapped. This is done by raising page touch faults whenever this restriction is violated. When a fault occurs, the thread or process attempting the access is moved to one of the allowable PCPUs (i.e., 0 or 2 in this example) – termed micro-scheduling. Of course, regions may also be unmapped, and when such unmapped regions are accessed, beyond micro-scheduling, the additional option is to once again map the region to the cache used by the PCPU in question – termed opening the region.

Via page touch faults and with micro-scheduling, one can en-sure that the memory blocks in a region, e.g., pages 10, 11, and 12, exist only on cache 0, which is private to PCPUs 0 and 2. Note that this technique also minimizes the number of duplicate cache lines found in caches and in addition, it may potentially reduce cache coherency traffic and false sharing of cache lines. Further, an understanding of page to cache mappings provides approximate information about cache load, which region-based scheduling uses to better utilize the cache resources present on multicore platforms, as discussed in more detail in Section 2.4.

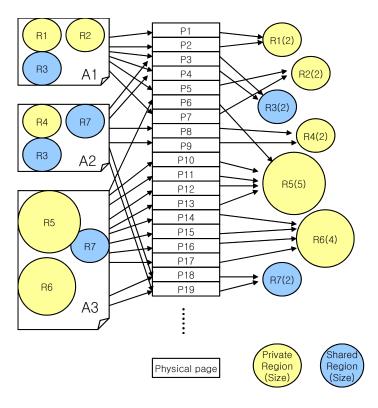

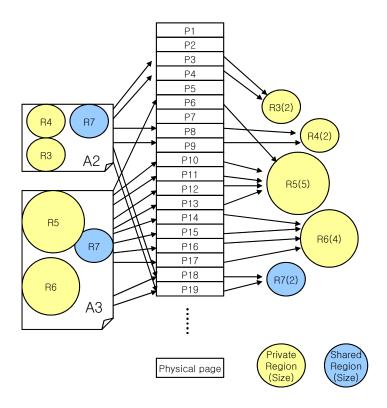

Figure 5 depicts a sample scenario in which the physical pages of an address space are located in different regions, private and shared ones. Each private region may be mapped to a single cache. A shared region typically exists in all caches – termed global region – an example being R7 in the figure. When there are a large number of global regions, there are fewer restrictions concerning how executable entities are run

(since they can run anywhere). This means that in the extreme case of there being only global regions, the region framework layer is not active, and region scheduling reverts to standard methods, like the credit scheduler in our Xen implementation. Figure 4 illustrates this by showing how region scheduling is implemented in a layer residing between the hardware and the standard VMM scheduler.

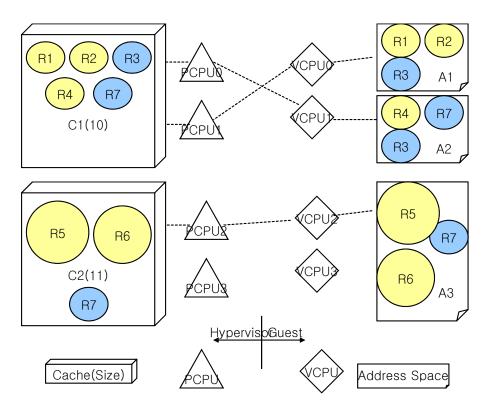

Regions change over time, as address mappings (page table en-tries) are created or destroyed and with changes in the behaviors of the executable entities using the address space. An address spaces dynamic size its working set is the sum of the dynamic sizes of its regions, and its cache load is the sum of the mapped regions sizes. Working set size is measured at runtime (see Section 2.4). C2(11) in Figure 11 shows the working set size of C2 is measured 11, which is sum of those for R5,R6 and R7 (5,4,2 respectively in Figure 1(a)). Regions, the address spaces in which they occur, and their mappings to caches are depicted in Figure 11, which shows that regions can differ in size, that VCPU to PCPU mappings are controlled to maintain region to cache mappings, and that a single address space can be mapped across multiple caches. The latter is particularly useful for memory- and cache-intensive applications able to benefit from such cache unification.

Figure 11 also shows how region scheduling packs regions into caches, where the two address spaces A1 and A2 run on cache C1, while A3 runs on C2 because its working set is larger. Cache load is shown in parentheses, the cache with a lower load being considered emptier when regions are bin-packed into caches.

#### 2.2.2 Life Cycle of a Memory Region

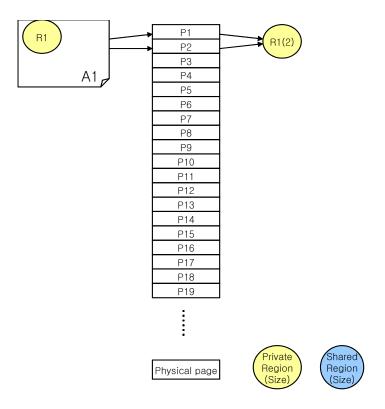

Figure 6 to 10 shows the life cycle of a memory region, using an example. When a new virtual-to-physical mapping to a physical page is created, a region is born. In Figure 6, R1 is born with first page table entry (mapping, the first arrow) and it increases its size (the number of physical pages it manages) to 2 with the second arrow. Now

Figure 6: Life of region – born

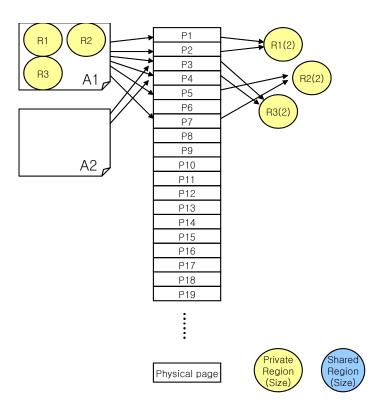

assume that this process (or address space) creates more mappings in page table by requesting more physical pages, then we see more arrows from A1 as in Figure 7. New physical pages may be combined to existing region, or can create new region. Initially it can be merged to the existing one and such regions are called 'seed' region. It just plays role of a initial pool of pages. Later it may be split into regular regions once it goes through some learning phase. For now, we assume that we have two new regions R2 and R3 somehow in this example. Therefore, the address space A1 now has three private regions R1, R2, R3. Now if another process creates mappings to two pages P3, P4, then R3 becomes a shared region between two processes A1 and A2. To be exact, the first mapping would split R3 into new shared region R3' and existing R3 and second mapping would create new shared region R3", then R3' and R3" get merged which effectively turns the private region R3 into the shared region R3.

Figure 7: Life of region – new process

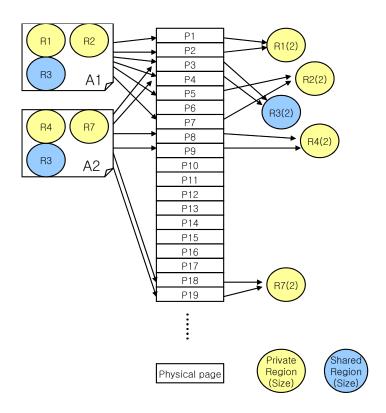

In Figure 8, A2 creates more mappings and it results more private regions R4, R7. Similarly A3 may come into picture and create more mappings as in Figure 9. This process, A3, has bigger working set size and naturally the private regions are bigger in its sizes. If A1 terminates and removes its mappings to pages as in Figure 10, their private regions dies accordingly and it may potentially turn a shared region into a private region.

This example not only shows the life of a region, but it also indicates different region types. The seed region plays the role of a pool of pages, and it splits into regular regions later. Sometimes, such regions may be merged to form bigger region. That is, regions can dynamically change as per the guest's behavior.

### 2.2.3 Region Scheduling Implementation

Table 1 describes the data structure maintained for each region

• pgd: if a region is private, it belongs to a certain address space and pgd points

Figure 8: Life of region – shared region

Figure 9: Life of region – another process with bigger working set

Figure 10: Life of region – death

Figure 11: How regions interact with caches and address spaces

```

struct region_t {

struct page_dir *pgd; // address space if private region

atomic_t vr_refcnt; // reference count

struct list_head list[MAX_CACHE]; // mapping to caches

spinlock_t lock; // lock

struct list_head rmaps_list; // reverse maps

unsigned short int frame_count; // static size

unsigned short int rmap_count; // # of reverse map

unsigned short int flags; // flags

unsigned short abit[MAX_CACHE][32]; // histogram

};

```

**Table 1:** System-level representation of regions

to the address space.

- refcnt: a region has a reference count, which is used to deallocate a region when it is no longer used.

- list: a region is mapped to some number of caches (typically, to only one)

- lock: a region structure is protected by basic locking primitives

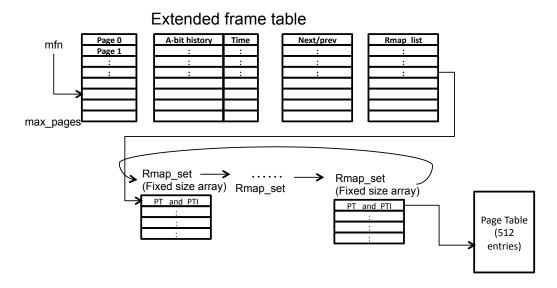

- rmaps\_list: a region has a reverse map to the page table so that region to page mappings are easily changed

- frame\_count : the number of pages a region manages.

- rmap\_count: the number of reverse map to the page table for optimization

- flags: flags that indicates current state of a region

- abit: tracks the access bits

The reverse map is important because when a region is mapped to a cache, all page table entries to all pages in the region must be modified in order to ensure that only those address spaces running on the right cores are permitted to access it. It is easy to maintain because Xen must already intercept all page table modifications.

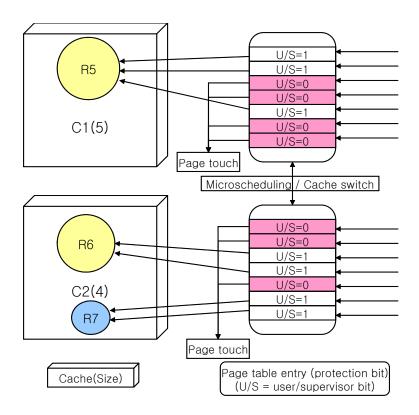

Figure 12: Page touch and cache switch

For other address spaces, we simply clear the protection bit in the page table, thereby causing an access fault when any of them attempts to use the page. Such page touches are not propagated to guests, but are transparently handled by the region scheduling framework. Figure 12 depicts this. Note that without a reverse map, these actions would require an expensive complete page table scan.

#### 2.2.3.1 Page touch and cache switch

As indicated in Section 2.2, upon page touch, the region scheduler has two options:

(i) to allow the access, which requires mapping the touched region to the current cache, termed opening the region; or (ii) to move the executable entity to the CPU whose cache is currently allocated to the region, termed micro-scheduling. An entity is micro-scheduled in order to force it to run on a different cache. For such a cache switch, we inspect all of the regions used by that entity, set the protection bits for the mapped regions to the target cache—opening the regions—and clear it for the

Figure 13: Per-cache page table

other regions closing them. Figure 12 shows how page tables are manipulated for each cache switch. Global regions, which are already mapped into both caches, are skipped since there is no need to manipulate them.

Page table manipulations are also used to collect information about an applications behaviour in terms of memory accesses and to track its working set. By simply closing a region, one can detect when a VCPU enters it, for instance, which we use to help assess working set size. By 'closing regions that have not been accessed for a while, region management is optimized in terms of the number of open regions it must consider.

#### 2.2.3.2 Micro-scheduling and cache switches

As evident from the description above, micro-scheduling involves cache switching. This could be expensive if it required the hyper-visor to explicitly touch all of the address spaces private regions and their page table entries. We eliminate this overhead by main-taining per-cache page tables. This is shown in Figure 13, where the hypervisors page tables A1C0 and A1C1 jointly have the same contents as the guests cache table A1; they differ only in the protection bits used to ensure that regions are open or closed with respect to certain caches. This also enables multiple threads in a process to run across caches.

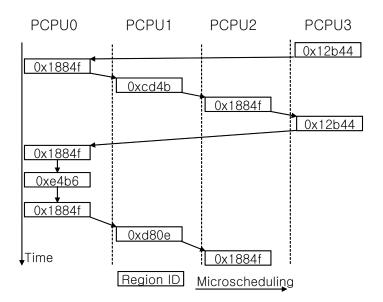

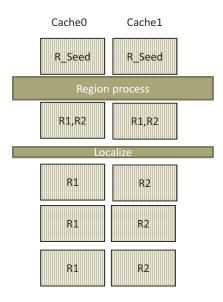

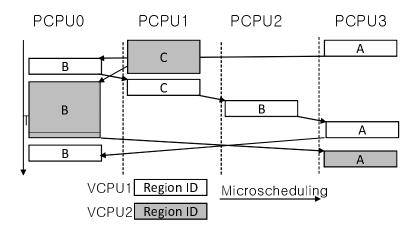

Beyond cache switching, the other costs of micro-scheduling con-cern VCPU/PCPU re-mappings. Figure 14 depicts a case in which one VCPU runs on four PCPUs, where

Figure 14: Microscheduling with 1VCPU

the hexadecimal in each rectangle is the unique ID for each region used by the VCPU. In this hardware configuration, Cache 0 is shared by (or local to) PCPUs 0, 2, and Cache 1 is shared by (local to) PCPUs 1, 3. Cache 0 is allocated to Regions 0x1884f, 0xe4b6, and Cache 1 is allocated to Regions 0xcd4b, 0xd80e, and 0x12b44. For example, since Region 0x1884f is mapped only to Cache 0, when the VCPU tries to access this region, it is scheduled onto PCPU0 or PCPU2. Note that it is the standard scheduler (such as Xens credit scheduler) that determines which PCPUs are allocated to them. Micro-scheduling, then, simply makes sure that VCPUs always run on those PCPUs that are associated with the caches allocated to the regions they are currently accessing. Potential performance opportunities and liabilities derived from these constraints are discussed next.

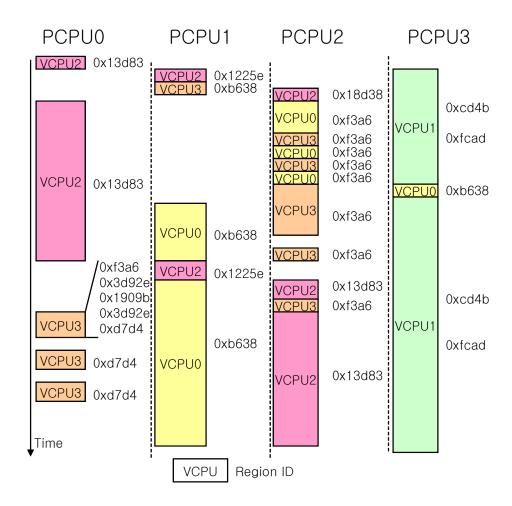

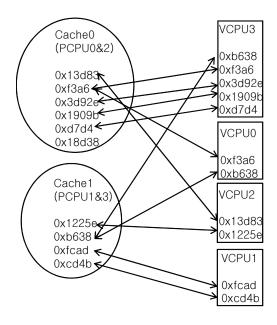

Figure 15 depicts a more complex case in which 4 VCPUs run on 4 PCPUs, where VCPUs access some regions only through PCPUs 0, 2 and others through PCPUs 1, 3. For example, the region 0x13d83 is mapped to Cache0, and 0x1225e is mapped to Cache1 (see Figure 16 for the associated region-to-cache mapping). We can see how the region framework balances cache loads from these figures. We discuss cache

Figure 15: Microscheduling with 4 VCPUs

Figure 16: Mappings among regions, caches, and VCPUs

balancing in Section 2.4.

A potential side effect of cache balancing is that PCPUs may experience additional idle time. This is illustrated by the idle time observed on PCPU1 in Figure 15, which occurs because VCPUs 0, 3, 2 are running on Cache 0 (PCPU0, 2) while only VCPU1 is running on Cache 1 (PCPU1, 3). In fact, VCPUs 0, 3 are competing for PCPU2, while PCPU1 is idle. This transient imbalance of VCPUs on two caches is due to restrictive region-to-cache map-pings. Such an imbalance is desirable if VCPU1 greatly benefits from its exclusive access to its cache (e.g., for cache-intensive codes), but at the same time, it may increase the latencies experi-enced by other VMs due to the effectively smaller cache sizes made available to them. The conflict is mitigated (1) when there are more VCPUs (due to VM-internal parallelism or consolidated VMs), so that it is likely that other VCPUs can be found to fill this gap, or (2) when there are more PCPUs per cache. Further, we use an additional method to prevent CPU idleness, in which instead of micro-scheduling VCPUs, we manage regions in order to handle this conflict between CPU and cache workload balancing. Results on such cache balancing appear in Section 2.5.3. Our final solution is to simply permit the region framework to make regions global (region opening) to prevent CPU idleness. Such degeneration to standard scheduling is useful for codes that do not depend much in performance on efficient cache use.

# 2.3 Regioning

This section explains region identification and tracking. At two extreme ends, all (private) physical pages in an address space could be placed (1) into a single region (too coarse-grained) or (2) into many single-page regions (too fine-grained). The first says that only entire address spaces can be mapped onto caches, whereas the second states that we have little information regarding its locality. To determine page-to-region associations, therefore, requires runtime methods that analyze the benefits and

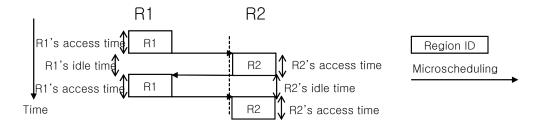

Figure 17: Two region memlats access and idle times

overheads of region formation and management, and of the micro-scheduling actions necessary to enforce region to cache mappings. This section identifies such regioning conditions and uses them to construct regioning algorithm.

### 2.3.1 Cache Unification

A simple single-threaded micro-benchmark, termed memlat (memory latency) based on [4], is used to assess the potential utility of cache unification. This memlat has two identically sized regions, which it traverses randomly for some given number of memory references and across a given number of pages, termed region access time, before its execution switches to the other region, which results in a consequent value of region idle time (see Figure 17).

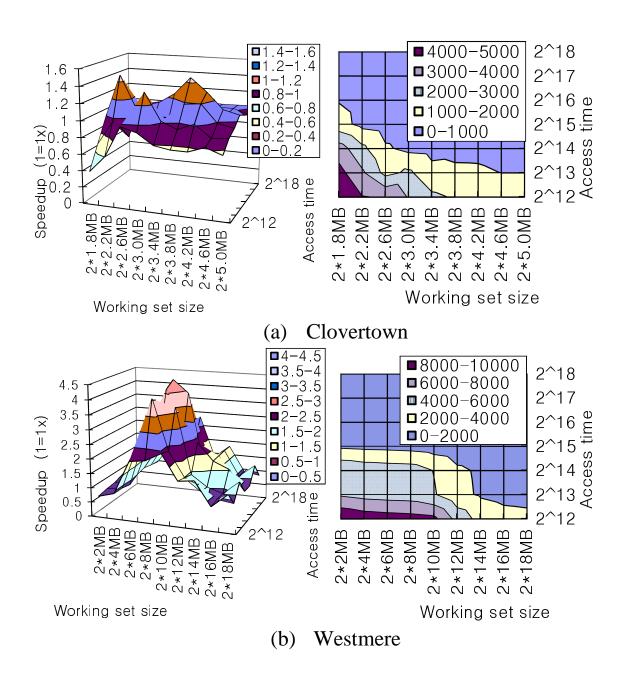

In the experiment, instead of confining the memlats regions and thus, its execution to one cache, we map its two regions to two different caches and micro-schedule it across the associated PCPUs, then compare it to the cache confining case. This is done for two different generations of machines (Clovertown and Westmere – see Section 2.5 for additional detail)

Figure 18 shows the normalized performance of the two region memlat when caches are unified, where values greater than 1 denote improved performance compared to the case of cache confinement. The x axis is working set sizes (2\*2MB means two 2MB regions), and the y axis is access time in the number of elements touched before a region switch occurs. In this section, access time is expressed in memory access

**Figure 18:** Two-region memlat across caches. Normalized performance (3D) and microscheduling rate per second (contour view)

count rather than actual time. The figure shows that improved performance appears in the center, not at the edges of the graphs.

There are several interesting insights from these simple experiments. First, substantial opportunities exist for gaining perfor-mance improvements from using cache unification, up to 45% for Clovertown and over 300% for Westmere. This is despite significant numbers of micro-scheduling actions in Figure 18, with rates ranging from 295 to 2240 per second for successful cache-unification near the center for Clovertown, and with rates ranging from 180 to 5100 per second for Westmere. Second, Westmere has a greater range in which improvements are seen (>1), and this is because of its relatively lower cost of micro-scheduling (see Section 2.5). This reflects the fact that computer architects have taken great pains to reduce the overheads of context switching on modern CPUs. Also, third, we can see that the microscheduling rate in-creases as region size and access time decrease.

Second, on Clovertown, performance improvements are mar-ginal when access times are high ( $\geq 2^16$ ) because in those cases, there are relatively few microscheduling actions that permit applications to benefit from cache unification. Third, as expected, when access times are too short ( $\leq 2^12$ ), the large number of microscheduling actions create overheads that outweigh the utility of cache unification. The outcome is Condition 1, which states that access time must be in some platform-specific range (i.e., these normative experiments have to be performed for each platform used) in order for region-based scheduling to benefit from cache unification.

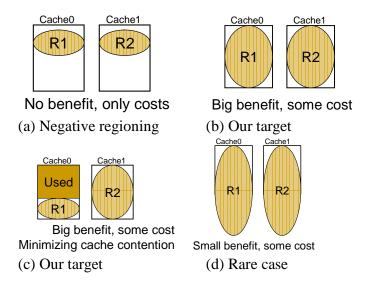

Conditions 2 and 3 concern cache working set sizes (recall that a cache working set is defined as the sum of the sizes of all of the regions being used). First, there are negative effects when working sets are too small (<=2\*1.8MB for Clovertown, <=2\*4MB for Westmere), because placing working sets that would fit into a single cache into two different caches simply causes the added overheads of micro-scheduling. Second, when a working set is so large that it does not fit into the unified two caches,

Figure 19: Cache working sets and cache sizes

then again, there are no benefits from region scheduling, since there would be cache misses both with region scheduling (and the additional overheads associated with it) and without region scheduling. Condition 2, then, states that the total working set size must be larger than that of a single cache, and Condition 3 states that each working set must fit into the unified space provided by both caches. Conditions 1-3 are shown pictorially in Figure 19. As stated earlier, actual benefits and costs vary across platforms, but from the Westmere vs. Clovertown results shown here, it appears that future platforms will likely further tilt the playing field toward our more explicit methods for cache management.

### 2.3.2 Bottom-up Regioning

We are now ready to explain how regioning is performed. Re-gions are captured at runtime. There are two extremes: (1) random regioning where physical pages are placed into regions randomly, which would cause high rates of micro-scheduling, and (2) single regioning, where all pages are placed into a single region, thereby effectively disabling region-based scheduling and entirely avoiding micro-scheduling

Figure 20: Regioning run (p = 1%)

Figure 21: Regions and region merging via LRU stack

overheads. Between these two extremes, we use Conditions 1-3 formulated above to assess the utility of regioning, and we identify and track regions using a sampling-based clustering technique, a bottom-up approach based on the notions of access and idle times.

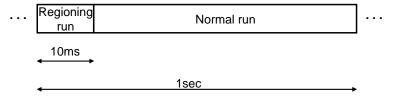

Each address space runs for 1% of its time in regioning mode (see Figure 20), in which initially, there are only single-page regions that are then repeatedly merged to form suitably sized regions to contain application locality. In addition, at the end of each regioning phase, some regions are torn down in order to prevent them from becoming too large and/or to capture substantial changes in application behavior (e.g., phase changes). Finally, for accuracy, regioning performed across interrupt handlers and system timers is adjusted to correctly consider such system activities.

Figure 21 depicts a scenario in which multiple smaller regions with longer vs. shorter inter-region idle times are merged into a smaller number of larger regions. This

is done as follows. First, during the regioning phase, all region switches are detected because initially, all regions are closed (except for global regions). This means that entering a region causes a page touch that is visible to the system. This makes it possible to construct a stack of regions based on the (prev\_region =>next\_region) occurrences. Second, when a new region is entered, the previous region is closed, so that only one region (the current region) is open at any given time. This makes it easy to measure the access and idle times for all regions.

As Figure 21b shows, the idle times correspond to the LRU distance between regions. Therefore, a long idle time indicates a locality change, whereas a short idle time between two regions is a strong indicator for merg-ing them, both of which are shown in Figure 21. Using a threshold q to determine short idle times based on the memlat measurements explained earlier, we merge regions when idle time is less than q and take no action otherwise. Note that a low threshold results in fine (small) regions, while a high threshold creates coarse (bigger) regions.

All regions are opened to resume normal execution after the regioning phase has completed. This entering/exiting of the re-gioning phase could be expensive, however, because all regions in the address space should be closed/opened when this occurs. This is optimized by introducing per-mode page tables in ways similar to what is discussed in Section 2.2. As a result, the regioning phase can be entered by simply switching to separate regioning-phase page table that already has closed entries.

### 2.3.3 Region Types

There are several types of regions. Initially, all regions are seed regions. When locality is captured in the regioning phase, they become regular regions and once mapped to some cache, they are termed local regions. As stated earlier, there are also global regions not subject to region scheduling.

Differentiating global from other regions is done as follows. At each page-touch

Figure 22: Types of regions

Figure 23: Region state transitions

- (1) Start regioning (close all regions except global regions)

- (2) Regioning phase (merging)

- (3) End regioning (open all regions)

- (4) Cache balancer does cache allocation, cache balancing.

- (5) Teardown (pick largest local region from regioning phase and make it into a seed region.)

Table 2: Regioning process

Figure 24: System view

from a seed region, the new page is determined as code if the faulting address equals the eip (program counter) register. If the faulting address is near the stack pointer, it is de-termined to be a stack page. Both code and stack pages are classified into global regions, and thus, do not further participate in the regioning process. The type transitions shown in Figure 23 apply to all other pages. In summary, the process in Table 2 is used for regioning. Figure 24 depicts region state transitions over time.

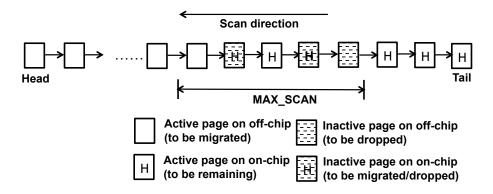

We have not yet explained when large regions are destroyed (by turning them into seed regions). This is done in conjunction with cache allocation to regions. Specifically, cache allocation is performed after regioning is completed, by picking a regular region and making it into a local region (i.e., mapping the region to some cache). Next, we select the largest local region determined in the regioning phase (which is marked in that phase, so this is an O(1) operation), and denote it as a seed region, thereby initiating the process of tearing it down. We never consecutively tear down the same region, however. In this fashion, we incrementally build (and tear down) regions in response to observed program behavior. Finally, a region may shrink during a run when an abnormally high microscheduling rate is detected, by

Figure 25: Portion of shared pages (observed min/max value)

excluding from the region the page that causes it.

Regioning is independently conducted for each core, the current policy doing it at every 1 second of CPU time for each address space. Thus, long-lived processes will experience more regioning actions, whereas short-lived ones may not experience any regioning at all (i.e., if they live less than 1sec). For multithreaded applications sharing an address space, each of the different threads (i.e., the cores on which they run) enter the regioning phase at a different time, thereby avoiding concurrent use of the shared page table.

### 2.3.4 Global Regions

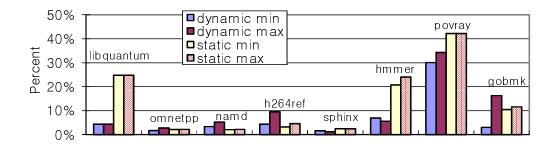

Inappropriate placement of shared pages and stack pages can cause unnecessary micro-scheduling overheads. An example is to map the glibc code onto only one cache, which would cause virtually all processes to frequently micro-schedule to glibcs cache. To address this issue, we declare all code pages (and similarly, the stack pages) to be global, which causes some level of cache line duplication. The resulting overheads in terms of cache space usage are moderate, however, as shown by the measurements in Figure 25 assessing the portion of shared pages in the SPEC benchmark suite. The figure shows the percentage of observed shared pages at runtime, both actually accessed (dynamic) percentage and the static percentage seen in page tables.

Figure 26: Access bit history and regions working set size

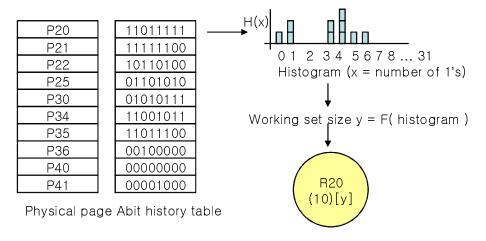

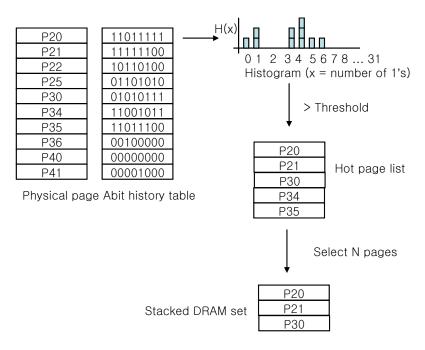

## 2.4 Working Set Tracking

Working set sizes are determined dynamically, using the access bits (A-bits) in page table entries. Specifically, every 100ms (as virtual time for each address space), the page table is scanned, and the access-bit history is recorded in a 32bit word. Only currently open regions are scanned to minimize overhead. For the example shown in Figure 12, if it is running on C2, only the part of the page table corresponding to R6 and R7 would be scanned, for instance. The access bits gathered over time form an access bit history (i.e., 3.2 seconds worth of access history) for each page. This is also termed the pages access pattern recorded as region histograms based on their pages access histories.

Figure 26 shows region R20s details. From its 10 pages ac-cess histories, it builds a histogram by counting the number of 1s, and it calculates its working set size y using a heuristic moving average function F below that takes the histogram as its input. The weights are determined experimentally.

$$y = \sum_{i=26}^{31} H(i) + \sum_{i=20}^{25} \frac{3}{4} H(i) + \sum_{i=14}^{19} \frac{1}{2} H(i) + \sum_{i=8}^{13} \frac{1}{4} H(i)$$

(1)

Consistent with this function, we define cache load as the sum of the dynamic sizes of mapped regions. Interpreting this value as cache occupancy, the cache balancer

Figure 27: Tracking working set size

uses it to determine cache imbalance; a simple greedy algorithm periodically balances cache usage in conjunction with the regioning process.

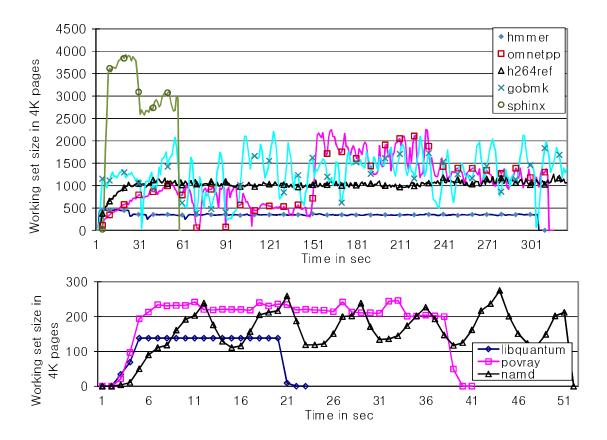

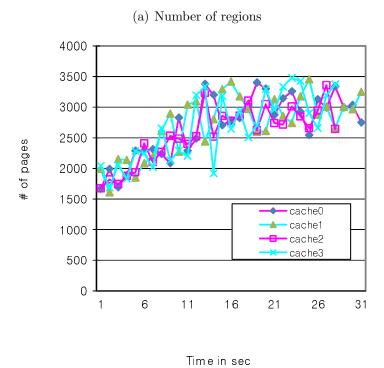

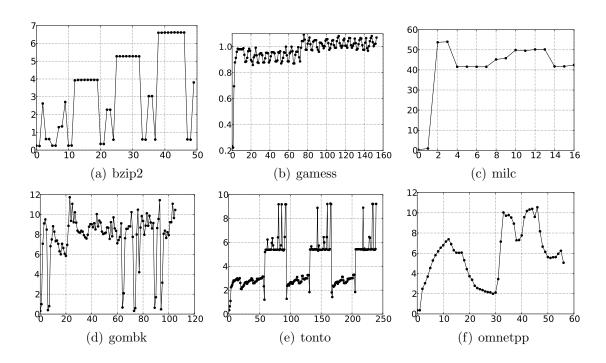

Since access bits are gathered every 100ms, and a 32bit word is used to store its history, roughly the past 3.2 seconds are reflected in the working set sizes used for region scheduling. Figure 27 shows the evolution of cache working set sizes observed over time for select benchmark codes, which the cache balancer would use.

## 2.5 Experimental Evaluation

Region scheduling is evaluated on two generations of Intel plat-forms. The first, labelled Clovertown in all figures below, is an older machine with Intel quad-core Xeon X5365@3.00GHz cores with 1GB RAM. The caches are an 8-way L1 cache (32K Da-ta+32K Instruction) and a 16-way 2x4MB L2 cache. The cache line size is 64bytes. The second, labelled Westmere in all figures below is a newer machine with

Figure 28: Overhead

two Intel six-core Xeon X5660@2.80GHz sockets with 12GB RAM. The caches are a 4-way 32KB L1I, 8-way 32KB L1D, 8-way 256KB L2, and shared 16-way 12288KB L3.

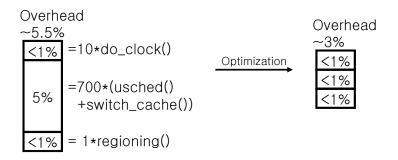

#### 2.5.1 Overhead

Regions are enforced by the hardware MMU. Once page protection bits are set during opening/closing regions, no additional runtime overheads are incurred during execution for enforcing regions. Full TLB flushes are avoided by using optimized instructions like invlpg.

Four major overhead sources are the do\_clock(), usched(), switch\_cache(), and regioning() calls, which perform page table scanning, microscheduling, page table updates, and regioning respectively. Using the two-region memlat with a small working set size, we conduct an extreme case experiment to assess these overheads, by choosing working sets that perfectly fit into the two different machines caches, thereby eliminating all potential benefits derived from micro-scheduling. When not using the per-cache page table optimization, total overhead is measured to be roughly 5.5% with 700 microscheduling per second. Performing the do\_clock() call ten times and making one regioning() call results in less than 1% overhead, but the switch\_cache() call constitutes over 90% of total overhead, which is effectively eliminated using said optimization. This results in constant-time micro-scheduling, its composite time comprised of page fault, context switch, runqueue manipulation, IPI, and TLB flush.

Figure 28 briefly shows this. Micro-scheduling is measured as 47600 cycles (i.e., 15.86 us, 1.5% for 1000 uschedule actions) for Clovertown, and 17800 cycles (i.e. 6.357 us, 0.6% for 1000 uschedule) for Westmere. Do\_clock() has some overheads de-pending on page table size, but it is several milliseconds in most cases (less than 1%). Regioning overheads benefit from the optimization that uses per-mode page tables, where an upper bound on these costs is defined by the sampling rate p. Naturally, over-heads are even lower, close to two TLB flushes, for codes that operate with stable regions, like libquantum. That overall overhead is measured to be less than 3%, typically 2% on both machines.

### 2.5.2 Microbenchmarks

To reduce cache contention, the cache balancer dynamically re-maps regions based on cache loads. For example, on machine Clovertown, when running two processes of 4MB working set size and two processes of 16KB working set size, with region scheduling, the cache balancer ensures that the cache is shared by the pair of 4MB+16KB processes. This improves performance by more than 50% for all processes compared to a region unaware mapping in which two 4MB processes share a cache. Similar results are observed on machine Westmere, using 12MB and 512KB working set sizes, respectively.

Figure 29 shows simple experiments on both machines, in which we run two 4MB memlats + 16KB memlat + a SPEC benchmark on the machine Clovertown, and two 12MB memlats + 512KB memlat + a SPEC benchmark on the machine Westmere. Depending on scheduling, the SPEC benchmark experiences different levels of cache contention. The cache balancer improves performance by correctly pairing processes onto caches and miti-gating cache contention. The figure shows that there is substantial potential for performance improvement for all SPEC benchmarks. Or stated negatively, without cache balancing, SPEC programs experience significant levels of

Figure 29: Speedup with cache balancing

Figure 30: Cache-unification for two-region memlat

disturbance by the presence of other cache-intensive codes.

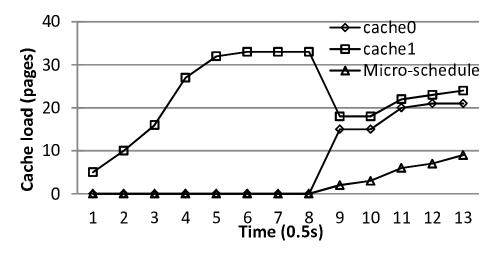

Conversely, performance can be improved for cache-intensive codes by giving them access to multiple caches, termed cache unification. The initial effects of cache unification on cache loads for the simple memlat micro-benchmark on machine Clovertown are shown in Figure 30.

The first half of the figure shows unbalanced cache loads, and the second half shows balanced loads plus micro-scheduling. Similar results are obtained on machine Westmere and for brevity, are not shown here. We evaluate the performance implications of such actions in more detail below.

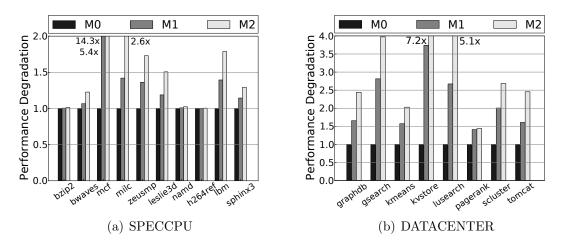

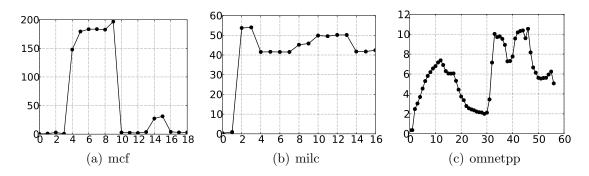

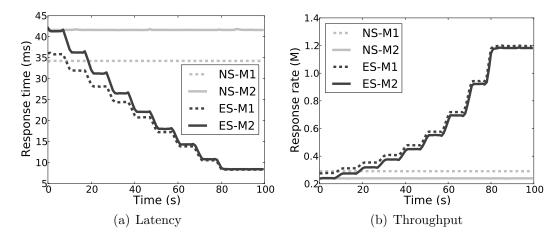

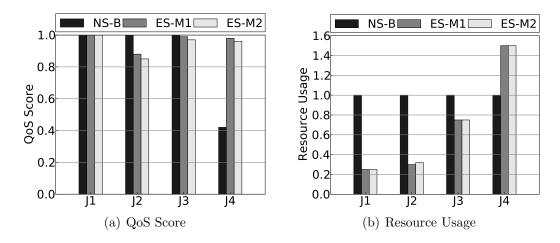

#### 2.5.3 SPEC Benchmarks

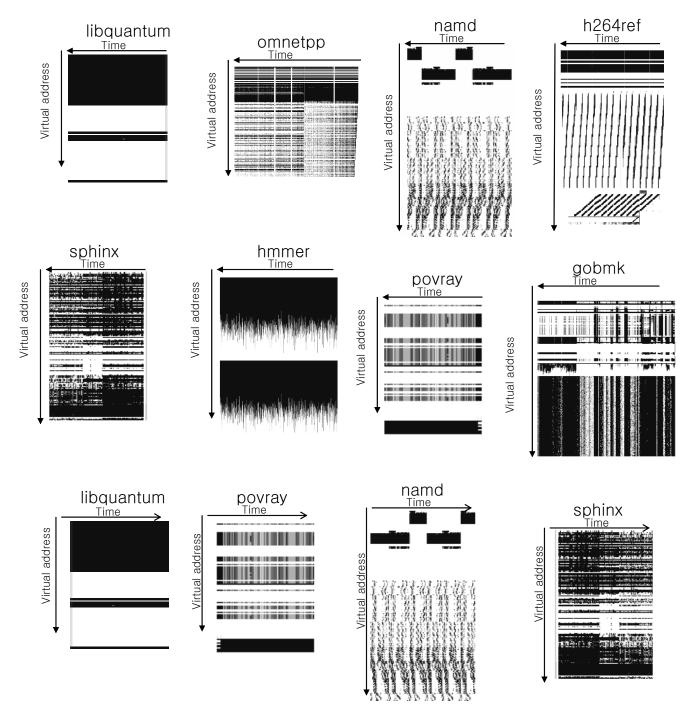

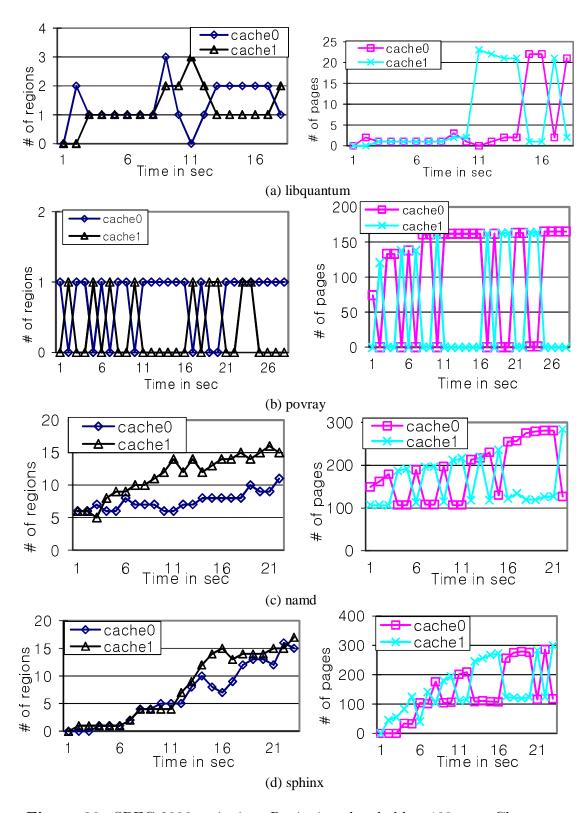

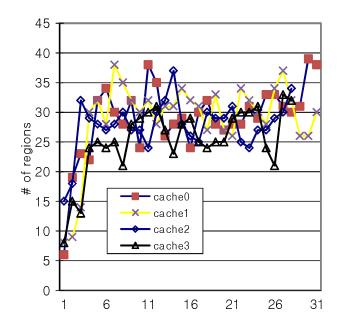

Figure 31 depicts measured results for experiments that assess the memory access pattern of the SPEC 2006 benchmark, which is obtained by collecting their access bit history over a test run (see Figure 26). From these runs, it is clear that libquantum and povray have simple access patterns, resulting in very stable regions, whereas sphinx and namd regions are more dynamic. This is verified by Figure 32, showing just a few regions in each cache for the first two, and a much larger number of regions for the latter two. Results obtained on machine Westmere are consistent, except that it tends to have bigger region sizes due to its higher performance (not reported for brevity).

Considering the access patterns depicted in Figure 31, these measurements show that the regioning methods correctly identify the memory region-based execution behavior of these codes, where e.g., libquantum and povray have few regions while named and sphinx have many regions.

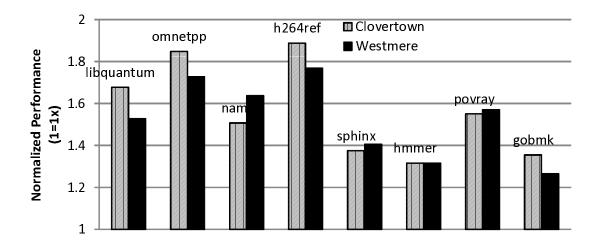

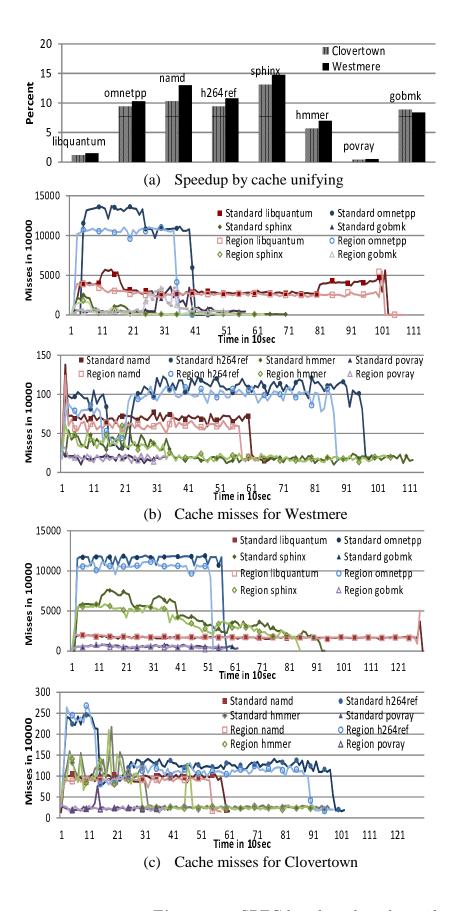

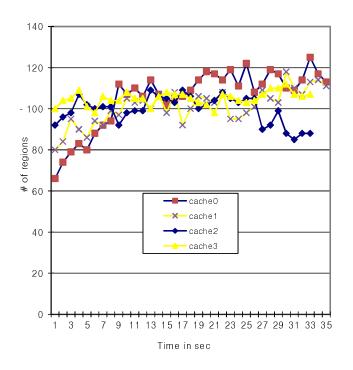

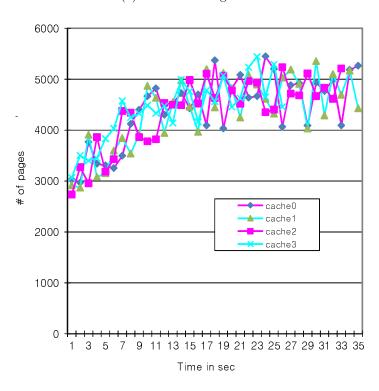

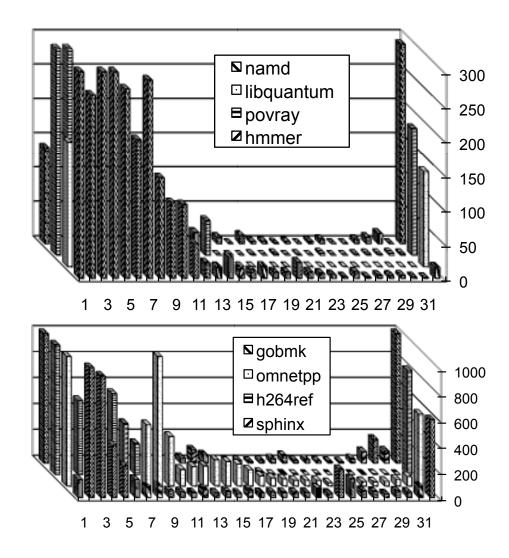

Another set of results in Figure 32 (the graphs on the right) de-pict the cache load (sum of region sizes for each cache) imposed by these codes. First, note that in the case of namd and sphinx, cache balancing succeeds in balancing both caches. This is in part because the number of regions for these codes is relatively large, which then permits the cache balancer to advantageously pack these regions into caches. In contrast, libquantum and povray show poor cache balancing, in part due to their small numbers of regions. Second, and as shown in Figure 33, successful cache balancing always improves performance, with an almost 15% gain for the Sphinx benchmark.

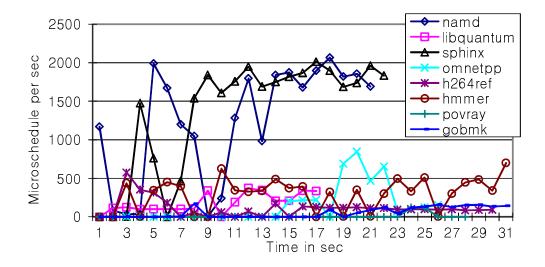

The outcome from these experiments is that regioning and cache balancing result in performance improvements even when the number of micro-scheduling actions is high. In fact and as shown in Figure 34, improved performance is seen even for very large numbers of micro-scheduling actions, e.g., the 10% improvement seen for named on machine Clovertown is attained with up to 2000 micro-scheduling actions

Figure 31: SPEC 2006 memory accesses

Figure 32: SPEC 2006 regioning. Regioning threshold = 100us on Clovertown

Figure 33: SPEC benchmark cache unifying

Figure 34: Micro-scheduling rates on Clovertown

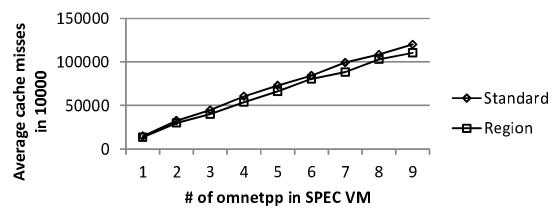

per second! Further, Westmere shows better performance due to its cheaper microscheduling. The measured cache misses in Figure 33 demonstrate why this is the case. In many workloads, such as omnetpp, sphinx, h264ref, the measured cache miss rates are lower with region-based scheduling.

The fact that performance benefits are seen even with high micro-scheduling rates (up to 2000 context switches per second) is a key result of this research. This demonstrates that given the rela-tively low cost context switching on modern architectures, there is an almost overwhelming importance of caching to program per-formance. We view results like these as an important motivation for carrying out and continuing our research into memory- and cache-centric methods for processor scheduling.

We also note that these SPEC-based results are consistent with the memlat-based ones shown in Section 2.3, thereby demonstrating that the potential behaviors we diagnosed with the memlat micro-benchmark are realistic in that they occur in actual codes. From the memlat-based diagnostic measurements, we also note that unduly high micro-scheduling rates can reduce or eliminate the potential performance gains derived from cache unification. This places constraints on the granularities of regions and region mappings that must be observed and taken into account by region

Figure 35: Regioning details (Clovertown)

scheduling.

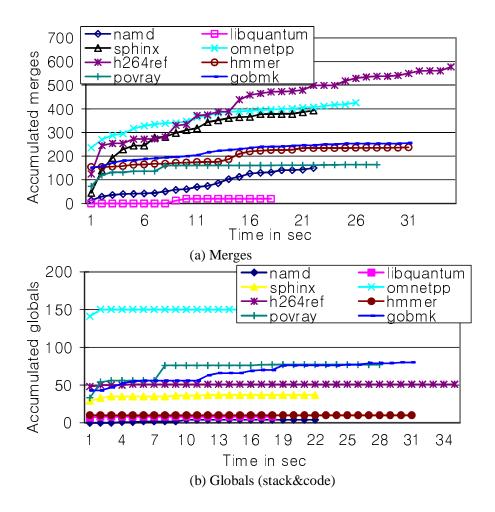

Finally, the results in Figure 35 confirm that the bottom-up ap-proach to regioning used in our research is viable. First, since we start with many small regions, initially, there are many merge actions, but second, there is sufficient stability that the number of merges quickly subsides, along with the number of re-regioning actions, as evident from the number of global regions seen in these codes. We deduce that memory regions are sufficiently stable to warrant their runtime detection and use, even without special hardware support for doing so.

Figure 36: Asterisk server and clients

### 2.5.4 Media Benchmark

Region scheduling can help improve performance, as shown in Section 2.5.3, but it can also improve other important metrics, such as noise [26] for parallel codes or timing perturbation for real-time applications. We demonstrate the latter on machine Clovertown by measuring the response times seen for high performance IP telephony software, Asterisk [25].

Asterisk is a complete IP PBX, comprised of a voice commu-nication server featuring voice mail, conference calling, interactive voice response, etc. It supports VoIP protocols such as SIP, MGCP, and H.323. It acts as a signalling server (SIP server) and a media server. When it handles signalling, it deals with call set-up/teardown, etc. When it is used as a media server, it takes a voice stream, processes it (including transcoding, if needed), and then sends the stream to the recipient. Figure 36 shows the configuration for Asterisk. This real-time media server requires low latencies to process voice streams, and it requires that those latencies remain within certain upper bounds to protect voice quality.

Figure 37: Media server+SPEC consolidation on Clovertown

Using the SIPp traffic generator for the SIP protocol, we run experiments exercising the system at 10 calls per second with RTP traffic. Signalling is initiated from SIPp, and an 8 second pcap file (RTP stream of G.711 encoded) is sent to the media server after call establishment. The call hold time is 10 seconds. The parameters above imply that there are at most 200 RTP streams flowing into the media server at any point of time (100 streams from the caller and 100 streams from the callee).

## 2.5.5 Cache Sharing

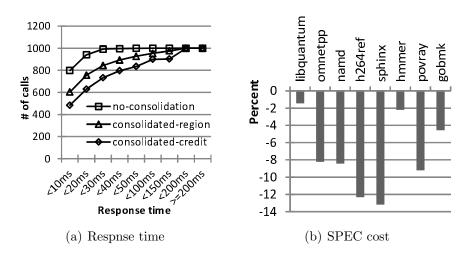

To demonstrate the utility of cache balancing, the VOIP experiment uses unfair policies that offer additional cache space to a preferred virtual machine. This is particularly important, of course, when there are multiple applications that share access to the platforms CPU and cache/memory resources.

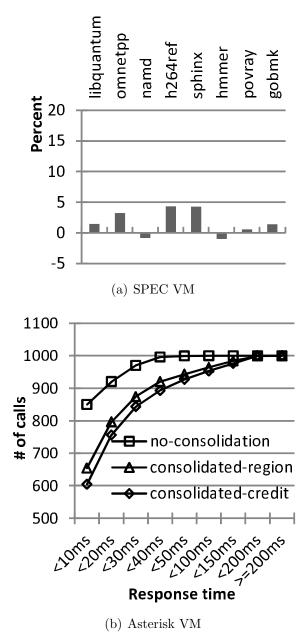

Figure 37 shows the media servers improved response time on machine Clover-town when it is the only application running (denoted no consolidation), when no region scheduling is used (denoted consolidated-credit), or when region scheduling is employed and the media server is the preferred VM (denoted consolidated-region). Results show that the servers response times are much more consistent for the region-based vs. credit-based scheduling approaches, and both are worse, of course, than

the non-shared scenario. The figure shows the cumulative number of calls with various durations observed during the runs, with a flat line being best. We also note that the overall average response time is 7.765ms for no-consolidation, 19.415ms for consolidated-region, and 32.535ms for consolidated-credit, re-spectively. The almost 40% improvement in the average response time seen for the server comes at a moderate cost for the other applications running on the platform, with an up to 15% detriment observed for the sphinx code. Degradation occurs because the cache balancer is instructed to provide additional cache to the media server, which is known to be cache-sensitive.

## 2.5.6 Reducing Noise for Parallel Codes

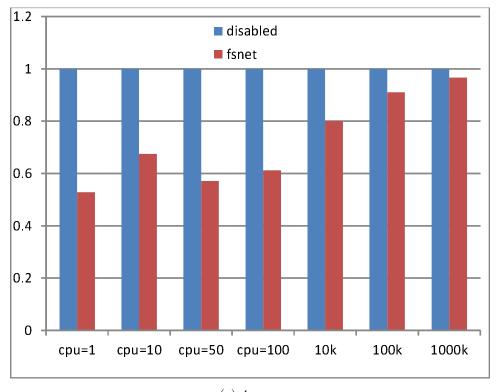

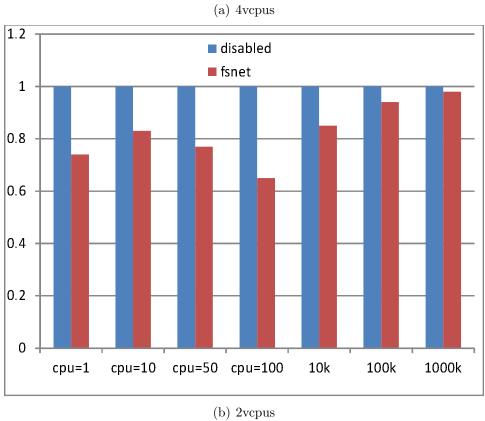

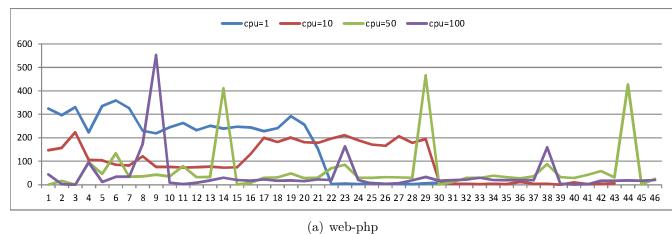

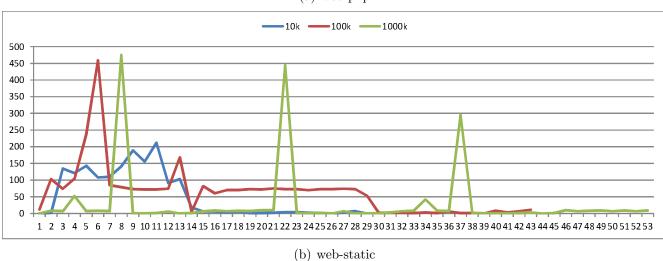

We next explore the use of region scheduling to protect parallel codes (e.g., OpenMP codes) running on a shared platform from each other and/or from the effects other codes on the same platform may impose on them. This is particularly important as we move toward many-core systems where the platforms on which parallel simulation computations take place will be shared with other applications (as in consolidated and cloud computing systems) or will be shared with additional codes that analyze simulation output data as it is being produced [35]. One could, of course, strictly partition nodes and their caches, but an approach like region scheduling that explicitly understands memory usage and can better isolate codes from each other, as evident from the results shown in the previous section, should result in improved levels of node utilization and permit richer and more finer-grain ways of using and sharing the node resources of future machines.