# SIGE BICMOS RF FRONT-ENDS FOR ADAPTIVE WIDEBAND RECEIVERS

A Thesis Presented to The Academic Faculty

by

Prabir K. Saha

In Partial Fulfillment

of the Requirements for the Degree

Doctor of Philosophy in the

School of Electrical and Computer Engineering

Georgia Institute of Technology August 2013

Copyright © 2013 by Prabir K. Saha

# SIGE BICMOS RF FRONT-ENDS FOR ADAPTIVE WIDEBAND RECEIVERS

#### Approved by:

Professor John D. Cressler, Advisor School of Electrical and Computer Engineering Georgia Institute of Technology

Professor John Papapolymerou School of Electrical and Computer Engineering Georgia Institute of Technology

Professor Saibal Mukhopadhyay School of Electrical and Computer Engineering Georgia Institute of Technology Professor Abhijeet Chatterjee School of Electrical and Computer Engineering Georgia Institute of Technology

Dr. Atri Dutta Mechanical and Aerospace Engineeering Princeton University

Date Approved: 17 June 2013

To,

my parents,

Kalpana and Ranajit.

### ACKNOWLEDGEMENTS

I would like to express my deepest gratitude to Prof. John D. Cressler for his guidance and support as my advisor. He is an excellent researcher, an outstanding teacher, and above all, a very nice human being. He has all the qualities of a great advisor and I am really lucky to have the opportunity to work under his guidance. I would like to thank him for all the hard work he puts in to make the students' lives easier. His passion for teaching and research has been and will always be a source of motivation for me.

I would like to thank Prof. John Papapolymerou, Prof. Saibal Mukhopadhyay, Prof. Abhijeet Chatterjee, and Dr. Atri Dutta for taking the time to serve in my dissertation committee and offer insights into my research.

I would also like to thank all of the members of the SiGe research team at Georgia Tech for their support and collaboration over the years. A special note of thanks goes out to the HEALICs team members, with whom I have spent countless hours doing measurements and discussing life. I would like to thank the GEDC staff; especially Lisa and Roosevelt for their friendship and support.

I would also like to acknowledge the fabrication support provided by Jazz, IBM, and IHP, without which this work would not have been possible.

Last, but not least, I want to thank my family and friends for their encouragement, support and love.

# TABLE OF CONTENTS

| DE            | DIC | ATIO   | <b>V</b>                                                       | iii       |

|---------------|-----|--------|----------------------------------------------------------------|-----------|

| $\mathbf{AC}$ | KNO | OWLE   | DGEMENTS                                                       | iv        |

| LIS           | т о | F TAE  | BLES                                                           | viii      |

| LIS           | т о | F FIG  | URES                                                           | ix        |

| SU            | MM  | ARY .  |                                                                | xv        |

| Ι             | INT | rodu   | UCTION                                                         | 1         |

|               | 1.1 | Origin | and History of the Problem                                     | 1         |

|               |     | 1.1.1  | Technology Scaling                                             | 1         |

|               |     | 1.1.2  | Process Variation and Impact on Yield                          | 2         |

|               | 1.2 | Conce  | pt of Self-healing Circuits                                    | 5         |

|               | 1.3 | A Brie | ef Introduction to SiGe HBTs                                   | 6         |

|               | 1.4 | Resear | rch Objectives                                                 | 9         |

| II            | WI  | DEBA   | ND LOW-NOISE AMPLIFIER                                         | 10        |

|               | 2.1 | Analys | sis of a Resistive-Feedback Amplifier with Reactive Matching . | 12        |

|               |     | 2.1.1  | Input Matching                                                 | 13        |

|               |     | 2.1.2  | Gain                                                           | 16        |

|               |     | 2.1.3  | Noise                                                          | 16        |

|               | 2.2 | Imple  | mentation                                                      | 18        |

|               | 2.3 | Measu  | rement Results                                                 | 19        |

|               | 2.4 | Summ   | ary                                                            | 22        |

| III           | AD  | APTIV  | VE IMAGE-REJECT MIXER                                          | <b>25</b> |

|               | 3.1 | Healin | g using External Sources                                       | 26        |

|               |     | 3.1.1  | System Architecture                                            | 26        |

|               |     | 3.1.2  | Performance Tuning                                             | 31        |

|               |     | 3.1.3  | Measurement results                                            | 33        |

|              |     | 3.1.4  | Automated healing in measurement                    | 36  |

|--------------|-----|--------|-----------------------------------------------------|-----|

|              | 3.2 | Integr | ation of signal sources and digital control on-chip | 43  |

|              | 3.3 | Monte  | e-carlo Based Verification of Healing               | 45  |

|              |     | 3.3.1  | Circuit improvements                                | 47  |

|              |     | 3.3.2  | Detailed descriptions of the healing algorithms     | 61  |

|              |     | 3.3.3  | Results                                             | 70  |

|              | 3.4 | Summ   | ary                                                 | 74  |

| IV           | LOV | W-LOS  | SS SWITCHES                                         | 77  |

|              | 4.1 | Low-lo | oss switch in bulk technology                       | 78  |

|              |     | 4.1.1  | Technology                                          | 79  |

|              |     | 4.1.2  | nMOS switch design                                  | 80  |

|              |     | 4.1.3  | Measured Results for nMOS device                    | 81  |

|              |     | 4.1.4  | SPDT Switch Design                                  | 83  |

|              |     | 4.1.5  | SPDT Measured Results                               | 83  |

|              |     | 4.1.6  | Phase Shifter design                                | 84  |

|              |     | 4.1.7  | Phase Shifter Measured Result                       | 85  |

|              |     | 4.1.8  | Benchmarking                                        | 86  |

|              | 4.2 | SOI sv | witch                                               | 88  |

|              |     | 4.2.1  | Switch design                                       | 88  |

|              |     | 4.2.2  | Measured data                                       | 91  |

|              | 4.3 | Summ   | ary                                                 | 93  |

| $\mathbf{V}$ | CO  | MPLE   | MENTARY SIGE OSCILLATOR                             | 96  |

|              | 5.1 | Techn  | ology Platform                                      | 98  |

|              | 5.2 | Circui | t Description                                       | 99  |

|              | 5.3 | Measu  | rement results                                      | 100 |

|              |     | 5.3.1  | Phase Noise Performance                             | 102 |

|              | F 1 | C      |                                                     | 104 |

| VI            | CONCLUSION   |                          |     |  |  |

|---------------|--------------|--------------------------|-----|--|--|

|               | 6.1          | Summary of Contributions | 106 |  |  |

|               | 6.2          | Future Work              | 107 |  |  |

| $\mathbf{RE}$ | FER          | ENCES                    | 109 |  |  |

| VI            | Γ <b>A</b> . |                          | 116 |  |  |

# LIST OF TABLES

| 1  | LNAs                                                                             | 22 |

|----|----------------------------------------------------------------------------------|----|

| 2  | Performance Summary and Comparison with other Published Image-Reject Mixers      | 36 |

| 3  | Values of control elements                                                       | 40 |

| 4  | Simulation results of the mixer at nominal settings in different process corners | 40 |

| 5  | Target Specifications                                                            | 40 |

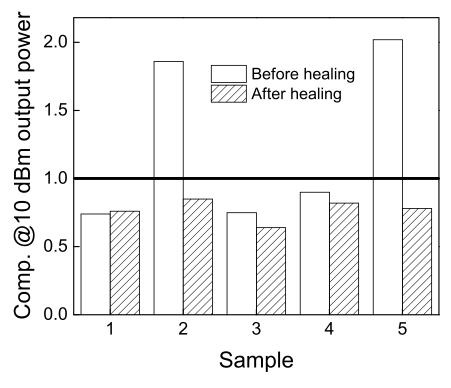

| 6  | Measured performance of the mixer before and after healing for 5 different dies  | 40 |

| 7  | Healing performance of the IR mixer with ALLs and DACs                           | 45 |

| 8  | Dependence matrix of tuning knobs and performance metrics                        | 62 |

| 9  | Comparison of SPDT switches                                                      | 87 |

| 10 | Comparison of phase shifters                                                     | 88 |

| 11 | Comparison of SPDT switches                                                      | 94 |

# LIST OF FIGURES

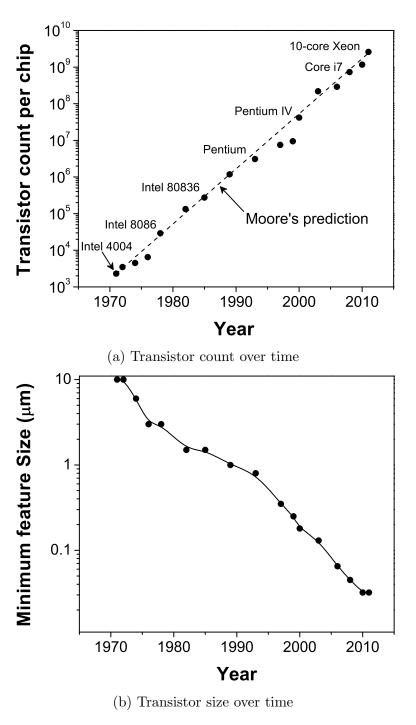

| 1  | Exponential change of integration complexity: (a) Transistor count of Intel microprocessors over time (b) Minimum transistor size of Intel                                                                        |    |

|----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

|    | microprocessors over time                                                                                                                                                                                         | 3  |

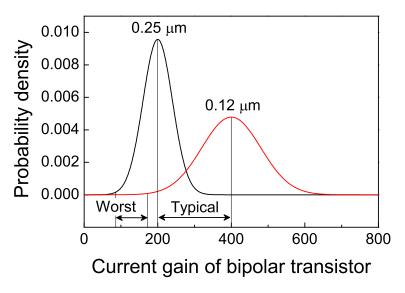

| 2  | Process variation increases with scaling down of feature size                                                                                                                                                     | 4  |

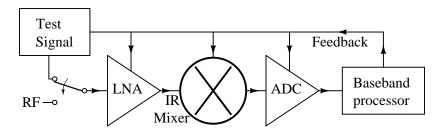

| 3  | Concept of a self-healing receiver system                                                                                                                                                                         | 6  |

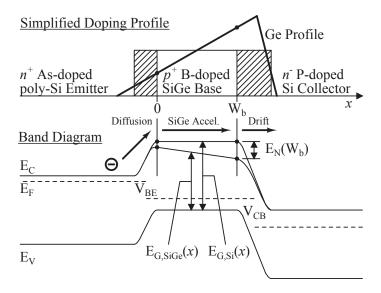

| 4  | A ramp germanium profile creates an electric field that accelerates minority carriers through the neutral base, improving base transit time and output impedance                                                  | 8  |

| 5  | A profile with large germanium content at $x=0$ reduces the potential barrier for minority carrier injection into the base, improving DC current gain and small signal transconductance for a fixed bias voltage. | 9  |

| 6  | Schematic of a generic shunt-shunt resistive-feedback LNA                                                                                                                                                         | 12 |

| 7  | Small-signal model of a resistive-feedback amplifier                                                                                                                                                              | 13 |

| 8  | Equivalent small-signal representation of input impedance: (a) without matching and (b) with $\pi$ -matching network. (c) Loci of $S_{11}$ with and without $\pi$ -matching network at the input                  | 14 |

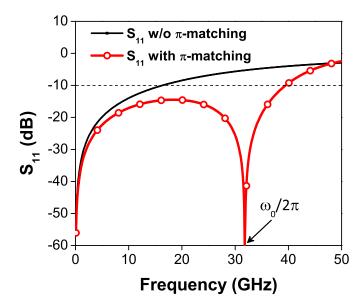

| 9  | $S_{11}$ with and without the $\pi$ -matching network at the input                                                                                                                                                | 15 |

| 10 | Small-signal model of the resistive-feedback amplifier for use in gain computation                                                                                                                                | 16 |

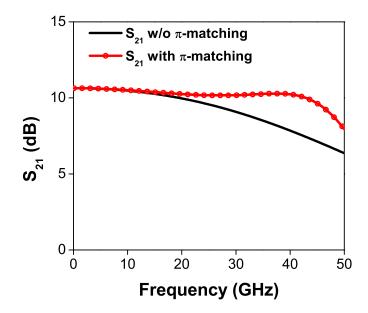

| 11 | Effect of input-matching network on $S_{21}$                                                                                                                                                                      | 17 |

| 12 | Small-signal model of a generic resistive-feedback amplifier including noise sources                                                                                                                              | 17 |

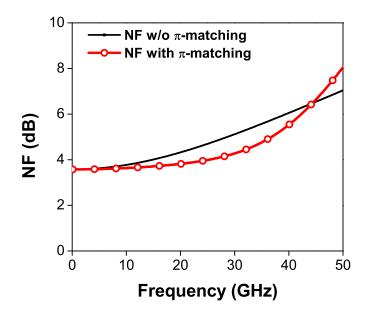

| 13 | Effect of input-matching network on noise figure.                                                                                                                                                                 | 18 |

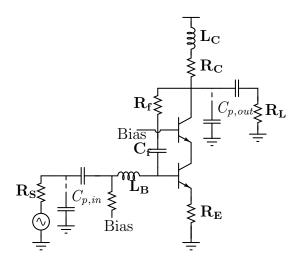

| 14 | Schematic of the resistive-feedback LNA with reactive components for improved matching                                                                                                                            | 19 |

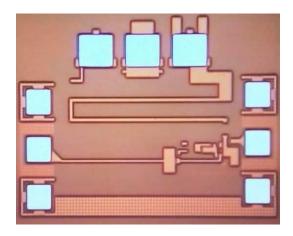

| 15 | Die microphotograph of the wideband SiGe LNA                                                                                                                                                                      | 20 |

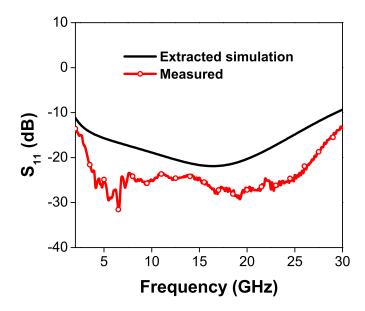

| 16 | Measured and extracted input return losses $(S_{11})$ of the wideband SiGe LNA                                                                                                                                    | 20 |

| 17 | Gain $(S_{21})$ vs. frequency of the wideband SiGe LNA: comparison of measured and parasitic-extracted simulation results                                                                                         | 21 |

| 18 | Output matching $(S_{22})$ across frequency of the wideband SiGe LNA: comparison of measured and parasitic-extracted simulation results                                                                           | 23 |

| 19 | Noise figure vs. frequency: comparison of measured and parasitic-<br>extracted simulation results                                                                                                                                                                                                                       | 23 |

|----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 20 | Output power vs. input power for fundamental and 3rd order components showing OIP3 and OP1dB                                                                                                                                                                                                                            | 24 |

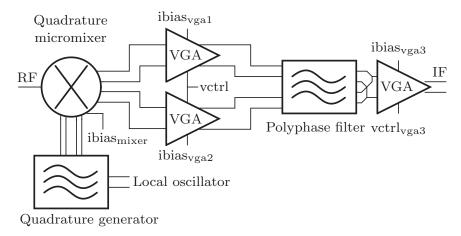

| 21 | Block diagram of the image-reject mixer. The voltage and current biases are used as control elements to tune different performance metrics.                                                                                                                                                                             | 26 |

| 22 | Schematic of the quadrature micromixer                                                                                                                                                                                                                                                                                  | 27 |

| 23 | Schematic of the multi-tanh VGA circuit with 'elastic' $g_m$                                                                                                                                                                                                                                                            | 27 |

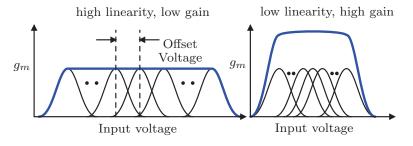

| 24 | 'Elastic transconductance' of the multi-tanh VGA. The bold curves show the overall transconductance $(G_m)$ , which is the superposition of the individual transconductances $(g_m)$ . By changing the offset voltage between the individual $g_m$ characteristics, linearity can be traded off for gain and vice-versa | 27 |

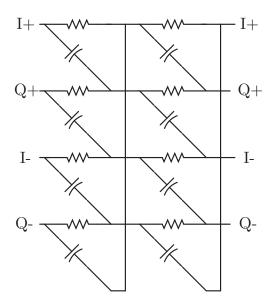

| 25 | 2-stage complex polyphase filter for image rejection                                                                                                                                                                                                                                                                    | 29 |

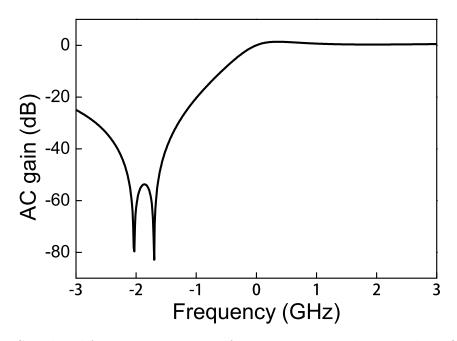

| 26 | Simulated frequency response of a two-stage complex polyphase filter. The filter pases through positive frequency components while canceling out the negative frequencies where the image is downconverted                                                                                                              | 30 |

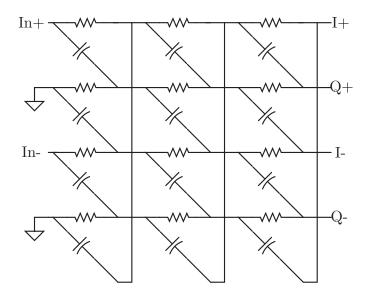

| 27 | 3-stage complex polyphase filter for quadrature LO generation                                                                                                                                                                                                                                                           | 30 |

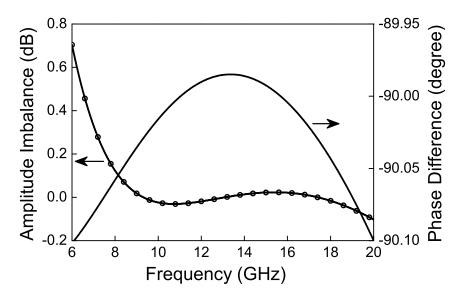

| 28 | Simulated amplitude and phase error of the quadrature generator based on a three-stage passive polyphase filter                                                                                                                                                                                                         | 31 |

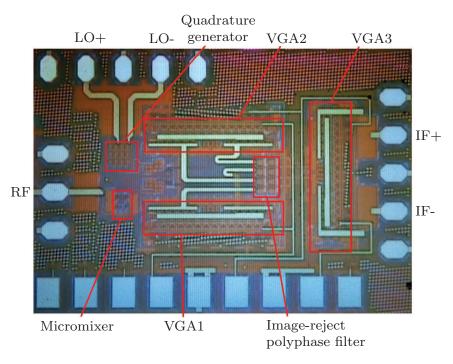

| 29 | Die photograph of the image-reject mixer. The mixer was fabricated in a 200-nm SiGe BiCMOS process. The chip die area is 1.6 mm x 1.0 mm.                                                                                                                                                                               | 33 |

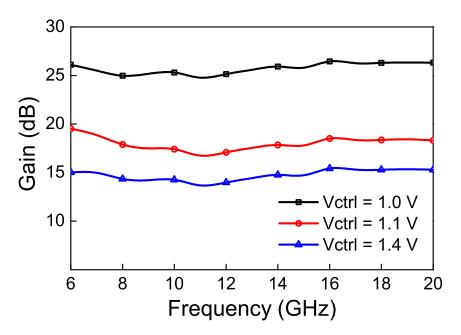

| 30 | Measured mixer gain across frequency for different VGA control voltages. The gain is quite flat across the entire frequency band and it can be varied by changing the control voltage of the VGAs                                                                                                                       | 34 |

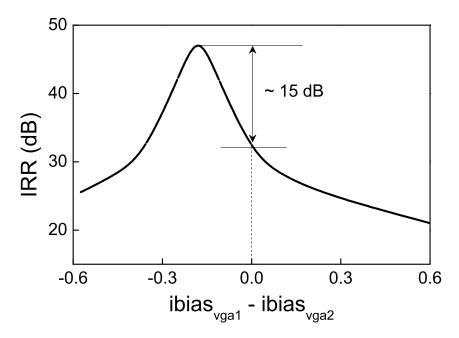

| 31 | Image rejection ratio (IRR) variation with VGA current biases in a typical case. An improvement of 15 dB was obtained by canceling the gain imbalances in the I and Q paths by introducing offset between the VGA current biases                                                                                        | 34 |

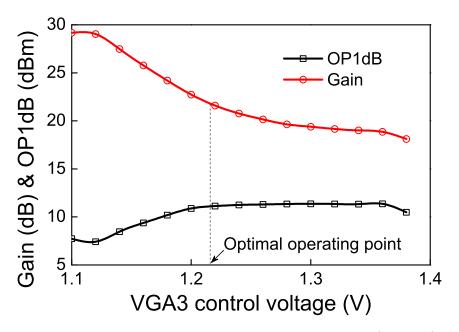

| 32 | Dependence of gain and 1-dB compression point (OP1dB) on control voltage of VGA3 ( $vctrl_{VGA3}$ )                                                                                                                                                                                                                     | 35 |

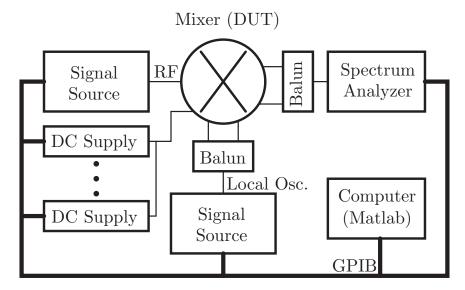

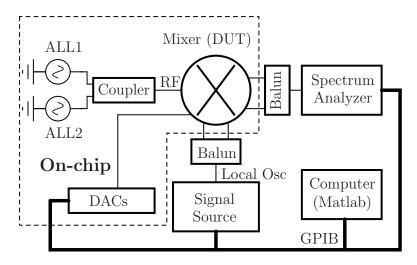

| 33 | Automated healing setup. All the instruments are connected using a GPIB interface. A Matlab program running on the computer iteratively measures performance and tunes bias values to adapt the performance of the mixer                                                                                                | 37 |

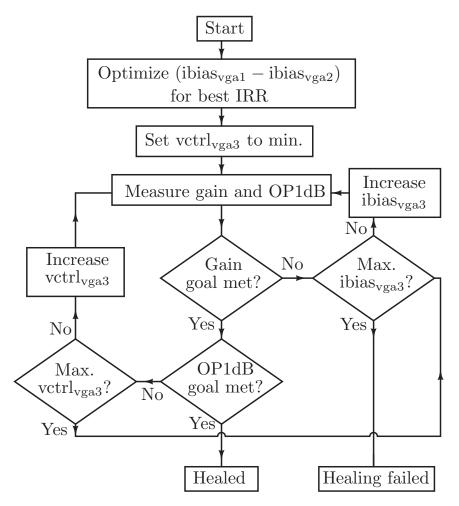

| 34 | Steps of the algorithm used in the automated healing procedure. IRR is healed first as it is independent of the rest of the parameters, and then the iterative loop measures gain and compression, and sets the biases accordingly | 38 |

|----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

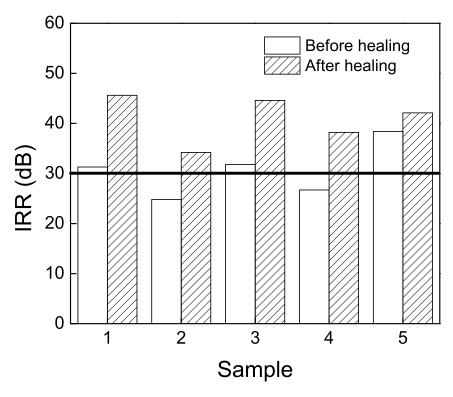

| 35 | Measured IRR of the mixer before and after healing for 5 different mixer die                                                                                                                                                       | 41 |

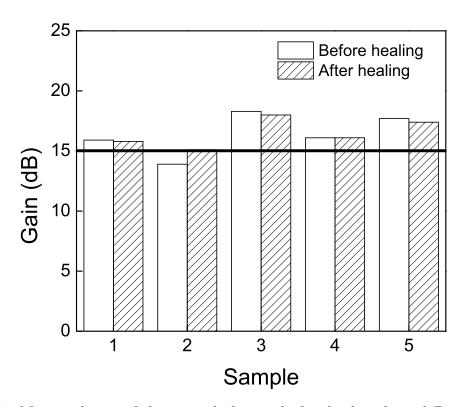

| 36 | Measured gain of the mixer before and after healing for 5 different mixer die                                                                                                                                                      | 42 |

| 37 | Measured OP1dB of the mixer before and after healing for 5 different mixer die                                                                                                                                                     | 42 |

| 38 | Healing setup of the image-reject mixer using ALLs and DACs                                                                                                                                                                        | 43 |

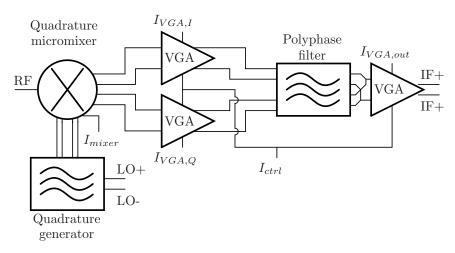

| 39 | Block diagram of the revised Image-reject mixer                                                                                                                                                                                    | 44 |

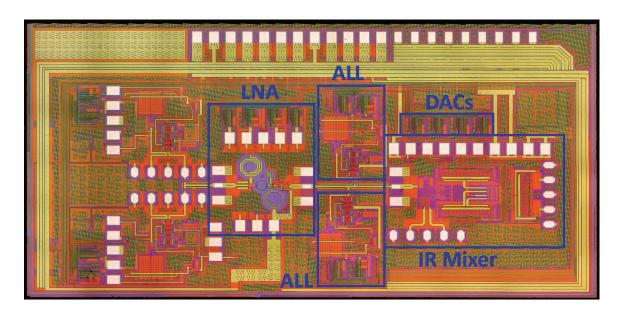

| 40 | Die photograph of the mixer with other components of the HEALICs receiver chain                                                                                                                                                    | 45 |

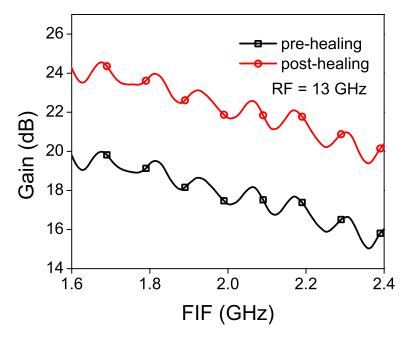

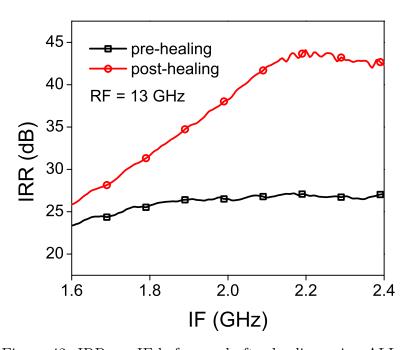

| 41 | Gain vs. IF before and after healing using ALLs                                                                                                                                                                                    | 46 |

| 42 | IRR vs. IF before and after healing using ALLs                                                                                                                                                                                     | 46 |

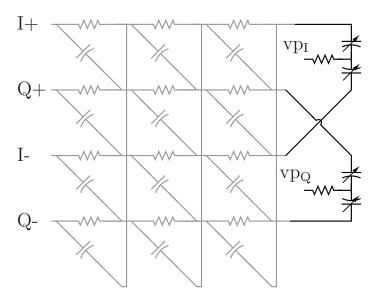

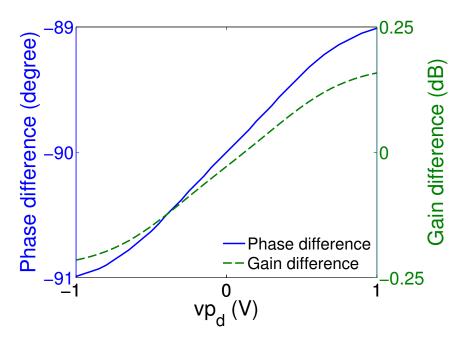

| 43 | Schematic of the quadrature LO generator with varactors at the output.                                                                                                                                                             | 48 |

| 44 | Phase tuning of I and Q LO signals using varactors: the difference between $vp_I$ and $vp_Q$ ( $vp_d$ ) controls the phase difference between I and Q signals                                                                      | 49 |

| 45 | Schematic of the LO limiting amplifier                                                                                                                                                                                             | 50 |

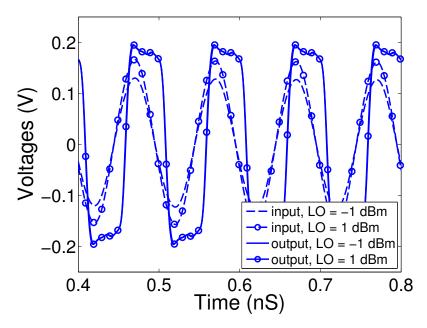

| 46 | Transient waveforms in and out of the LO limiting amplifier. The variaiton in input amplitude, within a certain range, does not affect the output amplitude                                                                        | 50 |

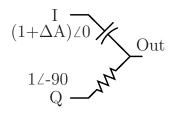

| 47 | Bulding block of the polyphase filter: one single RC network                                                                                                                                                                       | 52 |

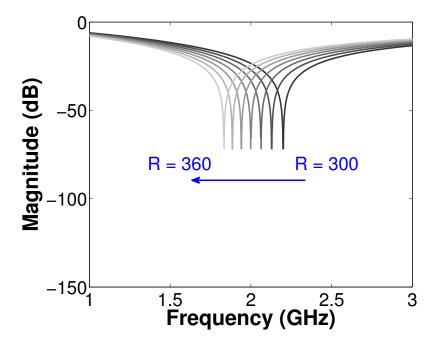

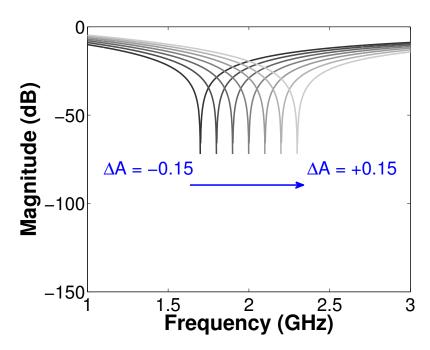

| 48 | Magnitude response of the RC-CR combination with changing resistor value, simulating the effect of process variation                                                                                                               | 52 |

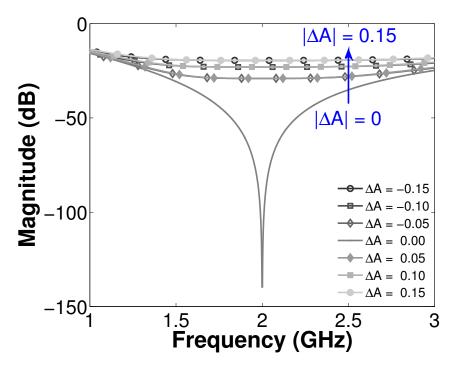

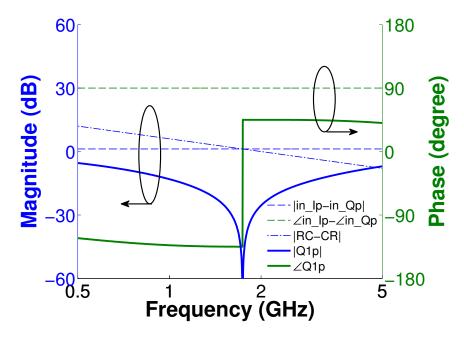

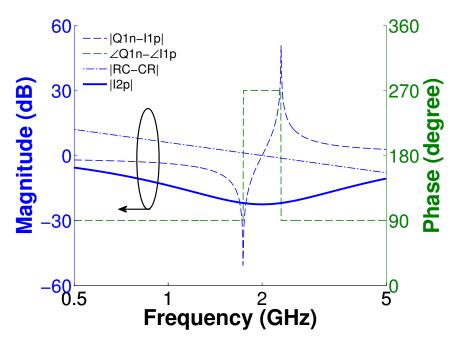

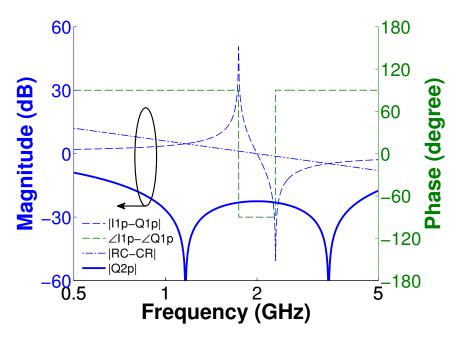

| 49 | Magnitude and phase response of an RC section with varying gain imbalance                                                                                                                                                          | 53 |

| 50 | Magnitude response of the RC-CR combination with changing gain imbalance at the input. The effect has the same signature as changing R or C values, and hence, can be used to tune out those effects                               | 54 |

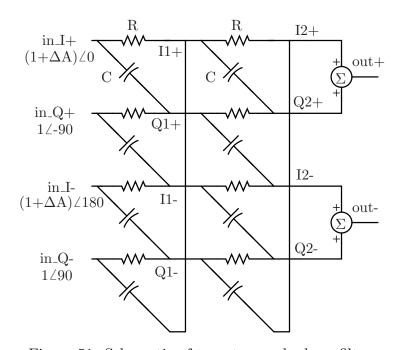

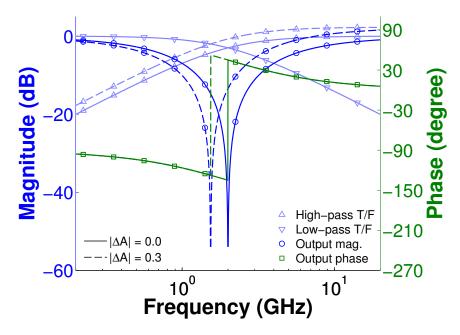

| 51 | Schematic of two-stage polyphase filter                                                                                                                                                                                            | 54 |

| 52 | Magnitude response of the two-stage polyphase filter with changing resistor value, simulating the effect of process variation                                                                                                                                                    | 55 |

|----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 53 | Magnitude response of the two-stage polyphase filter with changing gain imbalance at the input. It has a completely different signature as compared to that of varying R or C, and hence, it cannot use to compensate for drifting component values within the polyphase filter. | 56 |

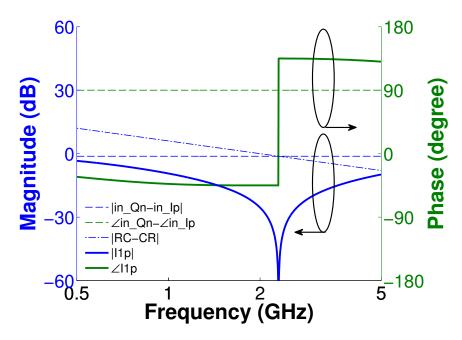

| 54 | Response of an CR branch to gain imbalance. schematic                                                                                                                                                                                                                            | 57 |

| 55 | Magnitude and phase response of an CR section with varying gain imbalance                                                                                                                                                                                                        | 57 |

| 56 | Magnitude and phase response of an CR section with varying gain imbalance                                                                                                                                                                                                        | 58 |

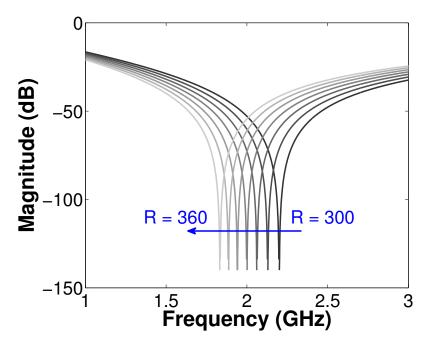

| 57 | Magnitude and phase response of an CR section with varying gain imbalance                                                                                                                                                                                                        | 58 |

| 58 | Magnitude and phase response of an CR section with varying gain imbalance                                                                                                                                                                                                        | 59 |

| 59 | Magnitude and phase response of an CR section with varying gain imbalance                                                                                                                                                                                                        | 60 |

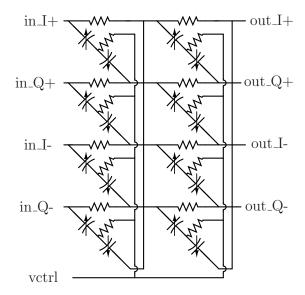

| 60 | Tunable polyphase filter                                                                                                                                                                                                                                                         | 61 |

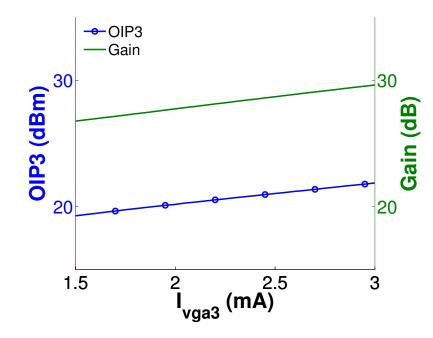

| 61 | Dependence of gain and OIP3 on $I_{VGA,out}$                                                                                                                                                                                                                                     | 64 |

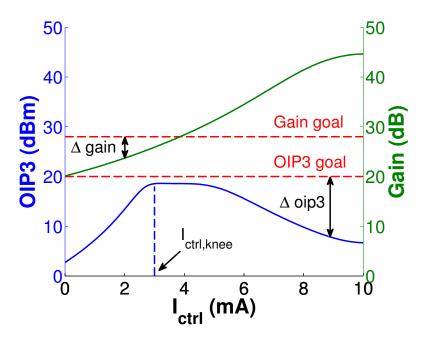

| 62 | Dependence of gain and OIP3 on $I_{ctrl}$                                                                                                                                                                                                                                        | 64 |

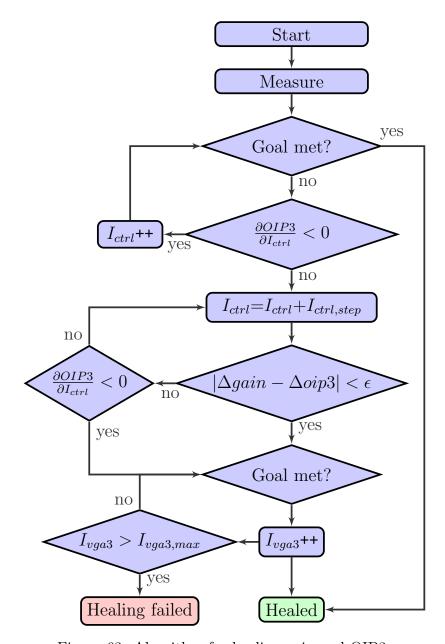

| 63 | Algorithm for healing gain and OIP3                                                                                                                                                                                                                                              | 66 |

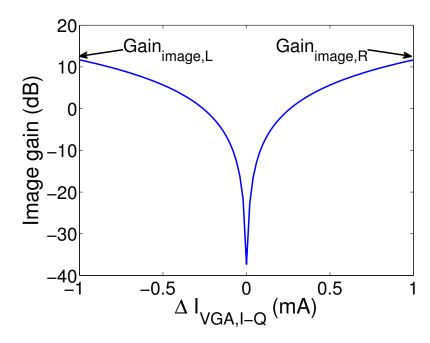

| 64 | Dependence of image gain on $I_{VGA,I} - I_{VGA,Q}$                                                                                                                                                                                                                              | 68 |

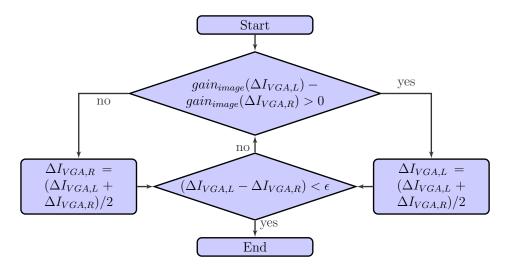

| 65 | Algorithm to find out optimum $\Delta I_{VGA}$ for gain compensation                                                                                                                                                                                                             | 68 |

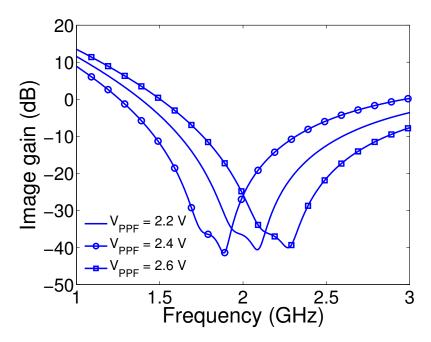

| 66 | Change in image gain frequency response with $V_{PPF}$                                                                                                                                                                                                                           | 69 |

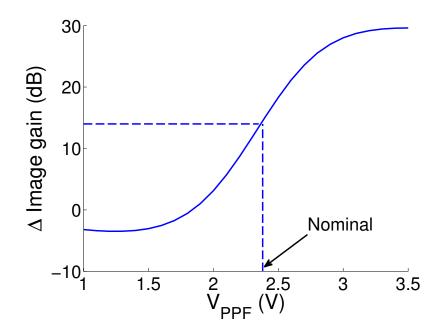

| 67 | Difference in image gain at upper and lower edge of the frequency band vs. $V_{PPF}$                                                                                                                                                                                             | 69 |

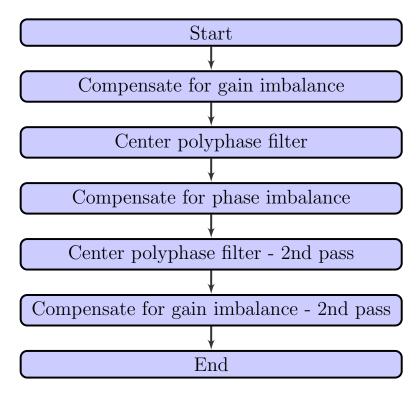

| 68 | Flow of IRR healing algorithm                                                                                                                                                                                                                                                    | 70 |

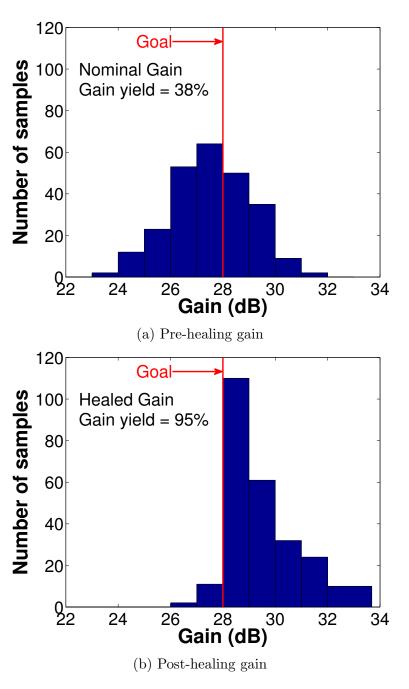

| 69 | Histogram of gain before and after healing for 250 monte-carlo runs                                                                                                                                                                                                              | 71 |

| 70 | Histogram of OIP3 before and after healing for 250 monte-carlo runs.                                                                                                                                                                                                             | 72 |

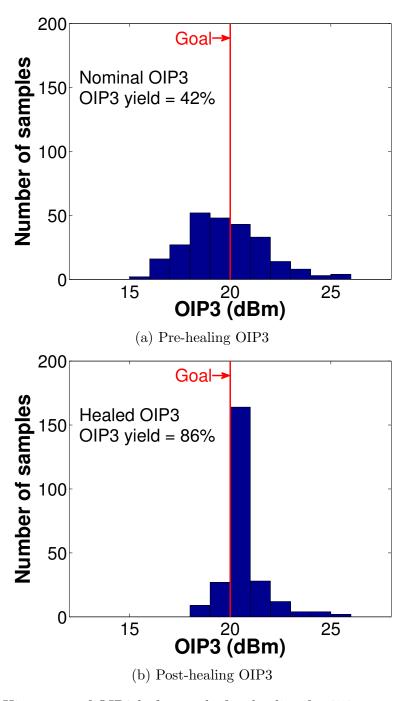

| 71 | Histogram of IRR before and after healing for $250$ monte-carlo runs                                                                                                                                                                                                             | 73 |

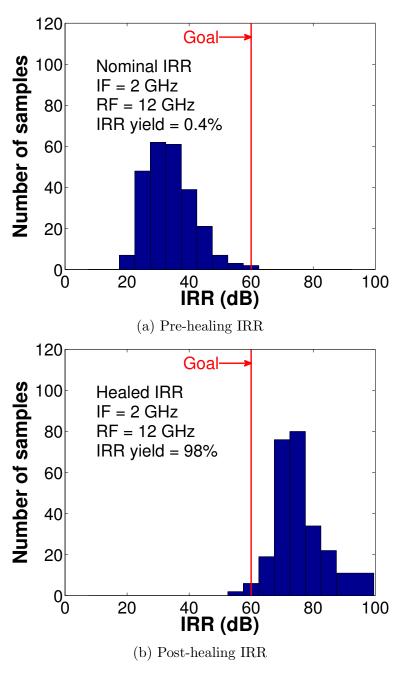

| 72 | IRR vs. IF before and after healing for 250 monte-carlo runs                                                                                                                                                                                                                     | 75 |

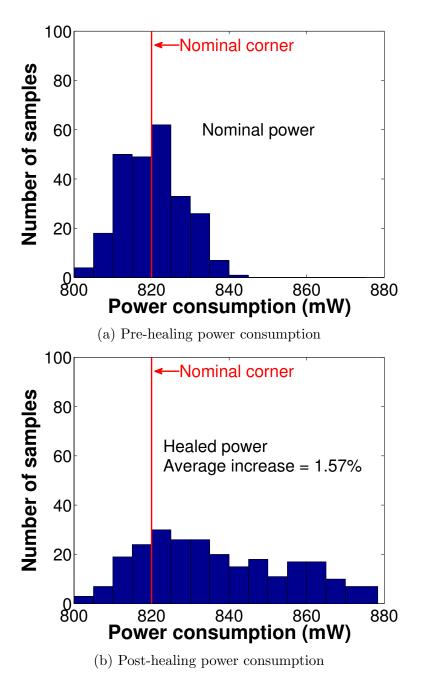

| 73 | Power consumption before and after healing for 250 monte-carlo runs.                                                                                                                                                                                                             | 76 |

| 74 | nMOS series-shunt SPDT switch topology                                                                                                                | 79  |

|----|-------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

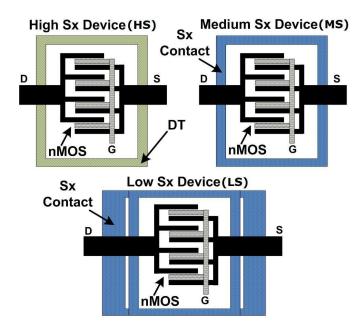

| 75 | Various layout configurations of the nMOS devices investigated                                                                                        | 81  |

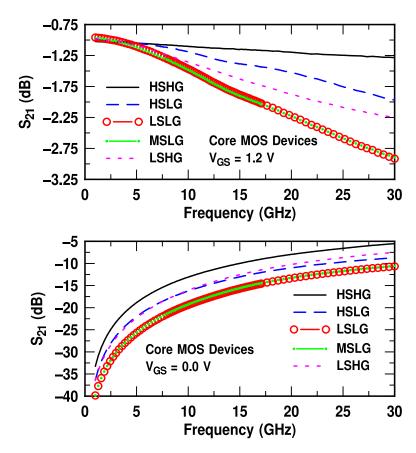

| 76 | Measured $S_{21}$ of various nMOS layouts for both on and off states                                                                                  | 82  |

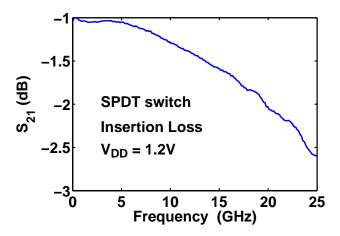

| 77 | Measured insertion loss of the SPDT switch                                                                                                            | 84  |

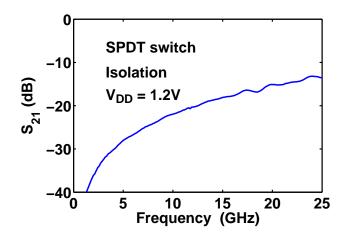

| 78 | Measured isolation of the SPDT switch                                                                                                                 | 84  |

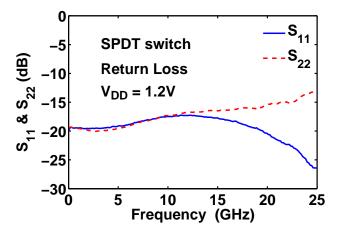

| 79 | $S_{11}$ and $S_{22}$ of the SPDT switch                                                                                                              | 85  |

| 80 | Die micrograph of the K-band phase shifter                                                                                                            | 85  |

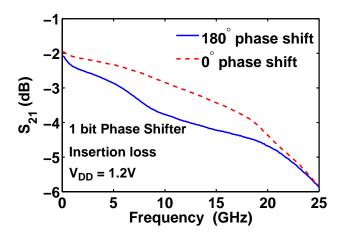

| 81 | Insertion loss of K-band phase shifter                                                                                                                | 86  |

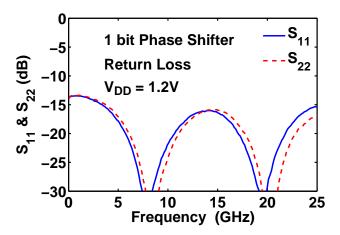

| 82 | $S_{11}$ and $S_{22}$ of the K-band phase shifter                                                                                                     | 86  |

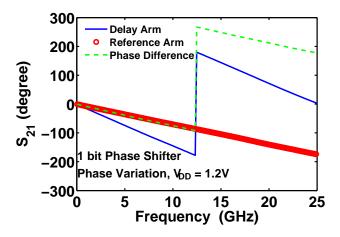

| 83 | Variation of phase with frequency                                                                                                                     | 87  |

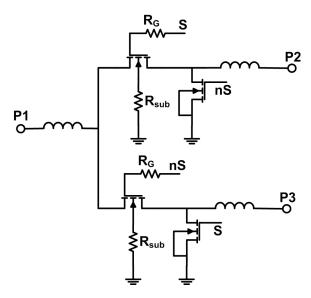

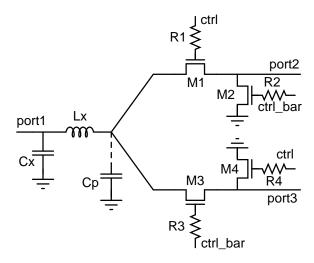

| 84 | Schematic of the SPDT RF switch                                                                                                                       | 89  |

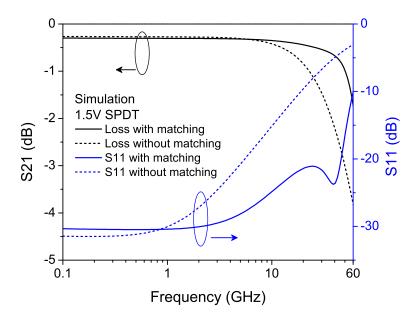

| 85 | Simulation results showing effects of matching network on insertion loss and matching                                                                 | 90  |

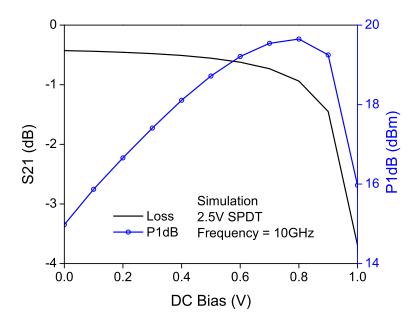

| 86 | Simulation results showing effects of DC bias variation on insertion and signal handling capacity (P1dB)                                              | 91  |

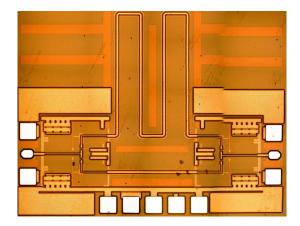

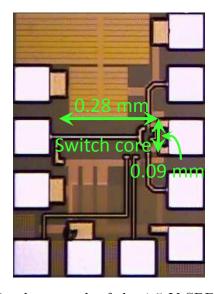

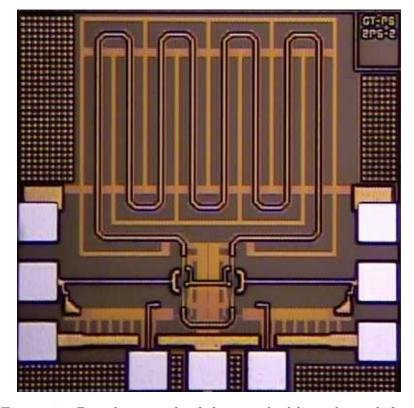

| 87 | Die photograph of the 1.5 V SPDT RF switch                                                                                                            | 91  |

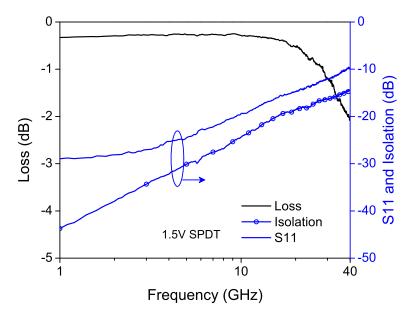

| 88 | Measured S-parameters of the 1.5 V SPDT RF switch                                                                                                     | 92  |

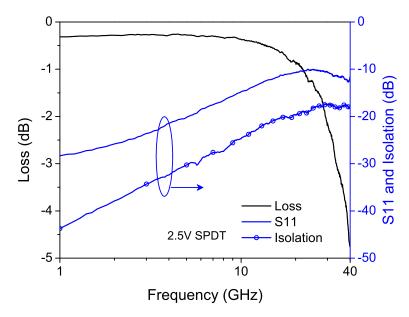

| 89 | Measured S-parameters of the 2.5 V SPDT RF switch                                                                                                     | 93  |

| 90 | Die photograph of the switched-line phase shifter                                                                                                     | 93  |

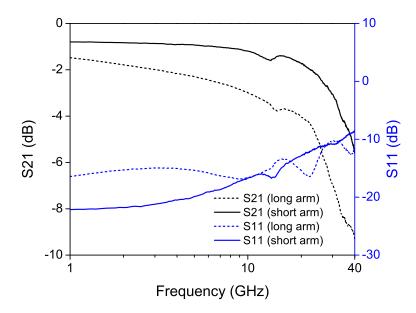

| 91 | Measured S-parameters of the one-bit switched-line 180° phase shifter using the 1.5 V switches. The phase shifter produces 180° phase shift at 20 GHz | 94  |

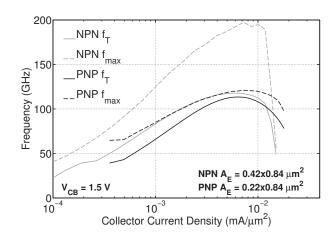

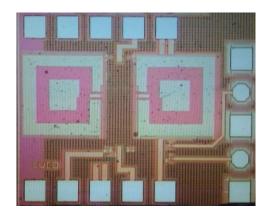

| 92 | AC characteristics of the $npn$ and $pnp$ high-speed complementary SiGe HBTs                                                                          | 97  |

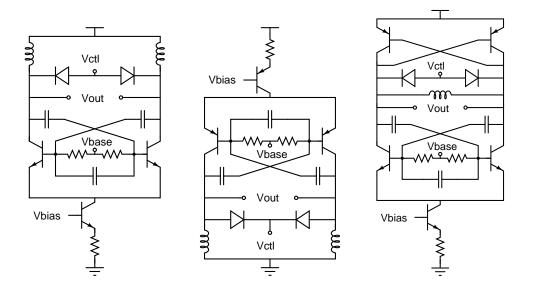

| 93 | Schematics of the VCOs (a) <i>npn</i> -only, (b) <i>pnp</i> -only and (c) complementary                                                               | 98  |

| 94 | Conceptual model of LC cross-coupled oscillators                                                                                                      | 99  |

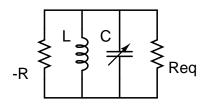

| 95 | Power characteristics of the complementary, $npn$ , and $pnp$ VCOs across bias current                                                                | 100 |

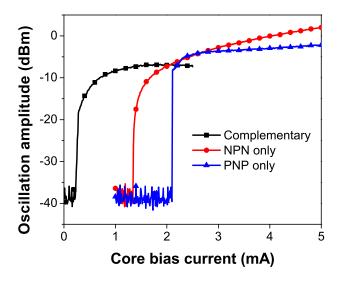

| 96 | Die photograph of the complementary SiGe VCO                                                                                                          | 101 |

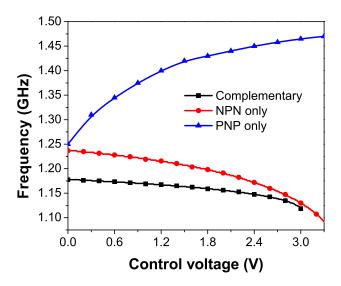

| 97 | Frequency characteristics of the complementary, $npn$ , and $pnp$ VCOs for different control voltages                                                 | 101 |

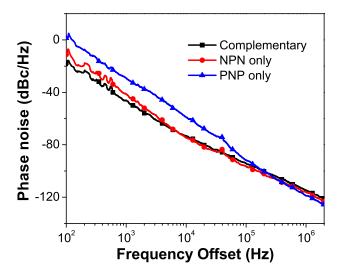

| 98 | Measured phase noise of the VCOs at constant control voltage $(V_{ctl} =$      |     |

|----|--------------------------------------------------------------------------------|-----|

|    | 0V). The complementary VCO, despite operating at much lower bias               |     |

|    | current (0.9 mA) as compared to the <i>npn</i> -only and <i>pnp</i> -only VCOs |     |

|    | (5 mA), has comparable phase noise in the $1/f^2$ region and performs          |     |

|    | better at close-in offsets                                                     | 103 |

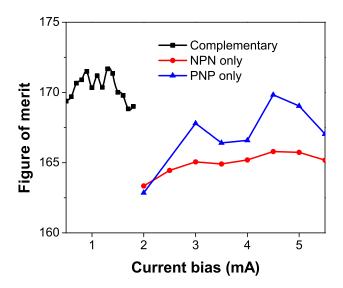

| 99 | Comparison of FoM (Eqn.17) of the VCOs based on phase noise at 1               |     |

|    | MHz offset. The complementary VCO outperforms both the <i>npn</i> -only        |     |

|    | and $pnp$ -only designs while operating at much lower power                    | 104 |

#### SUMMARY

The pursuit of dense monolithic integration and higher operating speed continues to push the integrated circuit (IC) fabrication technologies to their limits. Transistor dimensions are being scaled down with each passing generation of process technologies to improve performance and increase integration. But reducing transistor size, termed as technology scaling, is also associated with increased variability. In statistical terms, the increase in the mean performance is associated with an increase in the standard deviation. The increasing variation is having a negative impact on circuit yield in current IC technologies, and the problem is likely to become worse in the future. Circuit solutions that are more tolerant of the process-related variations are needed to fully utilize the benefits of technology scaling and improve yield. The primary goal of this research is to develop high-frequency circuits and systems that are capable of delivering consistent performance even under the threat of increasing process variation. These circuits can be used to build "self-healing" systems, which are able to detect process imperfections and compensate accordingly to deliver optimized performance. In addition to improving yield, such adaptive circuits and systems can provide more robust and efficient solutions for a wide range of applications under varying operational and environmental conditions.

Silicon-germanium (SiGe) BiCMOS technology is an ideal platform for highly integrated systems requiring both high-performance analog and radio-frequency (RF) circuits as well as large-scale digital functionality. For monolithic implementation of high-performance complex mixed-signal systems, SiGe BiCMOS offers capabilities not available in any other integrated-circuit platform. Thus, SiGe BiCMOS serves as an ideal platform for developing and demonstrating self-healing circuit solutions. This

research is focused on designing circuit components for a high-frequency wideband self-healing receiver in SiGe BiCMOS technology. The major contributions of this research are summarized as follows:

- 1. An adaptive wideband (6-20 GHz) image-reject mixer, suitable for use in a self-healing receiver, was designed. Automated simultaneous healing of multiple circuit parameters was demonstrated in measurement [1–3]. A monte-carlo simulation based methodology for verification of healing was developed. Circuits and algorithms were designed to achieve high image rejection ratio (IRR) over a wide bandwidth.

- 2. A wideband SiGe low-noise amplifier was designed. It was shown that the performance of the resistive feedback LNA can be enhanced by using small reactive elements with little area penalty [4].

- 3. Low-loss switches were implemented in bulk and silicon-on-insulator (SOI) technologies. The insertion loss of the bulk switches were reduced by using deep trench to isolated the bulk of the devices [5]. The SOI switches, to the best of the author's knowledge, feature lowest loss among all published wideband CMOS switches.

## CHAPTER I

## INTRODUCTION

## 1.1 Origin and History of the Problem

Microelectronics is undoubtedly at the forefront of technologies that have shaped our lives in the past few decades. We are now in the middle of a revolution that is making profound and pervasive changes to every sphere of human activity. Most visible changes have taken place in the fields of computing, communication, and consumer electronics. Cellular phones, personal computers, global positioning system (GPS), and internet are some of the many marvels that have become integral parts of our lives. It can be safely said that microelectronics has been the enabler for productivity and growth in virtually all areas of human activities. The revolution, which began with the invention of solid-state transistor by William Shockley in 1947, gained momentum rapidly when planar integrated circuit (IC) was fabricated for the first time by Jack Kilby in 1958. In the early years, the ICs had only a few transistors in them. Since that modest beginning, in a span of mere 50 years, we have now come to a point where billions of transistors are fabricated on ICs measuring less than a square centimeter. Over the years, electronic products have become smaller, cheaper, more powerful, and more reliable. One of the key factors, which made this revolution possible, is the reduction of transistor dimensions.

#### 1.1.1 Technology Scaling

A remarkable trend in the growth of the integrated circuits was first observed by Gordon Moore, one of the co-founders of Intel. In a short paper published in 1965, Moore outlined the trends of growing integration complexity, forming the basis of the legendary Moore's law. Moore pointed out that the number of integrated components

per chip, which minimizes the overall cost of the product, was doubling every year and predicted that this trend would continue in the foreseeable future. The time period for the "doubling of components" was later revised to be 18 months by Moore himself. Nevertheless, his prediction of this exponential growth has been valid for the last 50 years. Moore's law, which was an observation to begin with, subsequently became the trend-setter for increasing integration complexity and has been the basis for the sustained exponential growth in computing power, memory capacity, and the ubiquitous presence of cheap electronics all around us [6]. As an example demonstrating Moore's law, increasing complexity of Intel microprocessors is shown in Figure 1. The number of transistors per chip for Intel microprocessors is plotted in Figure 1a from the date of their introduction in 1971 to 2011. The most important factor behind this phenomenal growth is the reduction of the size of the transistors. The minimum feature size for the Intel microprocessors from 1971 to 2011 is plotted in Figure 1b. Not surprisingly, the rate of change is exponential in nature.

In addition to all the advantages related to Moore's law, a smaller transistor also results in higher intrinsic speed of operation. The current generation of processors has a minimum feature size of 32 nm, which is comparable to the size of viruses. As transistor size continues to approach atomic dimensions, the field of IC manufacturing is ripe with speculations regarding the future of Moore's law [6–8]. The end is inevitable. As Moore himself famously said [9], "No exponential is forever." The question is, what can we do to delay the inevitable?

#### 1.1.2 Process Variation and Impact on Yield

Process variation is the term used to describe the statistical variation in the attributes of the circuit components during fabrication. Transistors with smallest dimensions are most susceptible to process variation. The process variation is characterized in terms of "process corners", which usually represent three-sigma limits of the distribution,

Figure 1: Exponential change of integration complexity: (a) Transistor count of Intel microprocessors over time (b) Minimum transistor size of Intel microprocessors over time.

and the circuits are designed to be functional within the boundaries of the process corners.

As lithographic limits are being pushed to keep pace with Moore's law, process variations are steadily increasing (Figure 2). As shown in Figure 2, improvement in the worst-case performance is much smaller as compared to that of the nominal case. While relying on the worst-case models will result in over-design and waste of resources, using models based on nominal performance run the risk of taking a significant hit in terms of yield. Moreover, these process corners, although suitable for digital designs, fail to adequately represent effect of process variations on analog circuits. Various techniques are used at present to nullify effects of process variations. But there certainly is room for improvement, especially in the domain of high-frequency design. Post-fabrication trimming using fuses is good for one time adjustment and also occupies lots of area. Common-centroid layout, which is used to reduce mismatch, is difficult to implement at high frequencies due to added parasitic.

Figure 2: Process variation increases with scaling down of feature size.

One way to nip the problem in the bud is to improve process technologies to reduce process variation itself. Significant amount of effort is spent to achieve better control over the process of fabrication. But, despite best efforts, process variations have been increasing steadily. The other option is to design circuits that can adapt and function even when process variations are present. Modern microprocessors employ techniques to cope with the evils of process variation [10, 11]. To achieve similar goals for high-frequency systems, design approaches and circuit solutions need to be developed.

## 1.2 Concept of Self-healing Circuits

One emerging way of dealing with the problem of increasing process variation is to use "self-healing" circuits, which can detect, isolate, and fix its own flaws. The act of self-healing can be partitioned into three functions: sensing, processing, and actuating. Sensors are needed to detect and measure departure from the expected behavior, processing elements are needed to determine what is necessary to fix the problem, and actuators are needed to carry out the actions. Such circuits are partly inspired by biological systems that constantly heal themselves in the presence of random failures.

Ideas similar to self-healing have been tried in the domain of microprocessors [11,12] and memory design [13,14]. The field of high frequency circuits adds an extra layer of complexity to the problem due to increased sensitivity to parastic elements. The idea of self-healing radio-frequency (RF) circuits is being pursued actively at present. Increasing number of recent publications related to this topic [15–19] attests to the growing interest in the problem and the importance of it.

As an example, a block diagram of a self-healing receiver system is shown in Figure 3. The receiver chain consists of a low-noise amplifier (LNA), a mixer, and an analog-to-digital converter (ADC). The response of the system to a known test signal is analyzed by a baseband processor and corrective actions are taken if necessary.

This approach is quite similar to built-in-self-test (BIST) methodology, as far as sensing and processing of information are concerned. But the idea of self-healing also

has the added capability of fixing the problems. For an efficient implementation of this idea of self-healing, the individual circuit blocks need to be capable of adapting their performance in response to control signals, and the processor needs to be aware of the behavioral model of the circuit elements.

Figure 3: Concept of a self-healing receiver system.

## 1.3 A Brief Introduction to SiGe HBTs

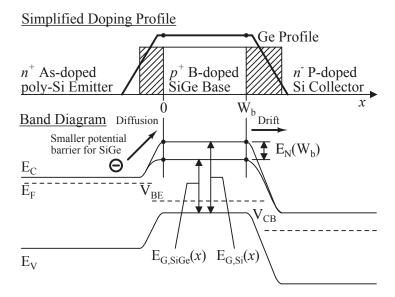

The heterojunction bipolar transistor (HBT) can be described as an enhanced version of the conventional bipolar junction transistor (BJT). To enhance desired performance aspects, the band diagrams of these devices are modified compared to the band diagram of a conventional BJT. In semiconductor materials, the bandgap can be adjusted by introducing an alloy of another material into a single crystalline growth. The technique of adjusting the bandgap, known as bandgap engineering, is used to produce the highest-performance transistors. A number of different materials are used to build these HBTs, e.g., Gallium Arsenide (GaAs), Indium Phosphide (InP), Gallium Nitride (GaN) etc. However, there is currently only one physically realizable siliconbased heterostructure that combines the performance of bandgap engineering with the processing advantages of silicon: the Silicon-Germanium (SiGe) HBT. Development of the SiGe HBT has spanned many decades. Although the original concept was first considered by William Shockley during development of bipolar device physics, it took over 30 years to produce a working prototype due to limitations in fabrication capability. An excellent history of SiGe process development is given in [20]. When germanium atoms are substituted for silicon atoms in the diamond-lattice crystalline structure, a narrowing of the bandgap occurs primarily through the valence band. The bandgap narrowing is a function of the amount of germanium in the alloy. A precisely controlled germanium profile, spanning the width of the base, results in controlled modulation of the device bandgap. There are multiple effects that can be achieved by altering the bandgap of a bipolar transistor. A linear-ramped germanium profile and the corresponding band diagram is shown in Figure 4. The start of the neutral base region is set as the origin, x = 0, while the other end of the neutral base is at x = Wb. The bandgap is the difference between the conduction and the valence bands, and is shown for both the Si BJT and SiGe HBT in the band diagram of Figure 4. The bandgap narrows as the germanium content increases across the width of the neutral base, producing the sloped conduction band seen in the SiGe band diagram. The sloped band diagram in the neutral base region corresponds to an electric field that pushes minority carriers through the neutral base according to traditional drift-carrier transport. This electric field has two important effects on static device characteristics. First, it reduces the base transit time of minority carriers, improving the speed of the device. The graded germanium profile also increases the output resistance of the HBT by impeding changes in the depletion region of the base-collector junction.

The germanium profile in the base can be changed to achieve different goals. In Figure 5, the added germanium reduces the bandgap uniformly across the neutral base. Since there is no electric field induced by the sloping bandgap, the transit time improvements are not present here. Instead, the bandgap narrowing reduces the potential barrier at x=0 in the emitter-base junction, allowing many more minority carriers to diffuse from the emitter into the base at a fixed bias voltage. This effect increases the DC current gain since there is not a significant increase in base recombination, and the base current remains nearly identical to that of a similar Si BJT. A hybrid of the box and linear-ramp profiles can also be used. These hybrids

Figure 4: A ramp germanium profile creates an electric field that accelerates minority carriers through the neutral base, improving base transit time and output impedance.

are referred to as trapezoidal profiles and often feature significant germanium content at x = 0 as well as a linear ramp across the neutral base.

Another important feature of the SiGe HBT devices is the exponential current relationship with the thermal voltage (kT). As temperature decreases, the circuit parameters increase proportionally. Leveraging this technique has produced record speeds in silicon-based circuits. With a wide number of profile combinations and a scarce amount of germanium available due to stability limits, germanium profile design is an application-dependent engineering problem with numerous trade-offs to consider. A snapshot of several state-of-the art SiGe processes from 2006 can be found in [20]. More details on SiGe HBT devices can be found in [20] and [21].

Yet another important advantage that SiGe HBT enjoys over other III-V technologies is its integration capability with complementary metal-oxide-semiconductor (CMOS) technology. At present, CMOS is the workhorse of the digital IC world. But CMOS alone is not sufficient to provide solutions for high-performance applications. SiGe HBTs fill that gap nicely, and can be easily integrated in the standard

Figure 5: A profile with large germanium content at x = 0 reduces the potential barrier for minority carrier injection into the base, improving DC current gain and small signal transconductance for a fixed bias voltage.

CMOS process flow at a minimal cost overhead. For monolithic implementation of high-performance complex mixed signal systems, SiGe BiCMOS offers capabilities that are not available in any other integrated-circuit platform.

## 1.4 Research Objectives

The purpose of this research is to develop high-frequency circuits and systems that are capable of delivering consistent performance even under the threat of increasing process variation in aggressively scaled fabrication technologies. The primary focus is on designing circuit components for a high-frequency, wideband, self-healing receiver in SiGe BiCMOS technology. The wideband nature of the circuits adds to the flexibility of the system, making it possible to handle multiple standards and frequency bands. A secondary goal of this research is to improve performance of these wideband circuits. Development of healing algorithms and demonstration of "self-healing" also naturally falls under the purview of this research.

## **CHAPTER II**

## WIDEBAND LOW-NOISE AMPLIFIER

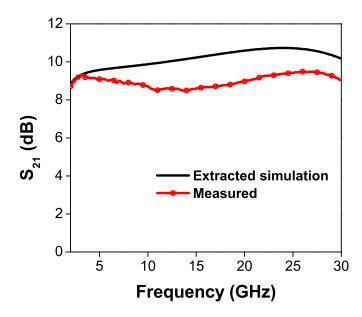

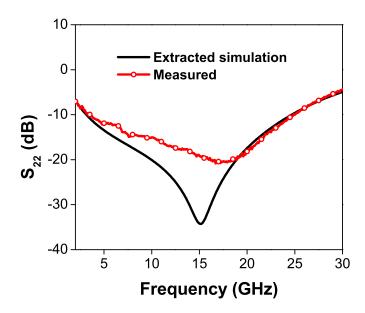

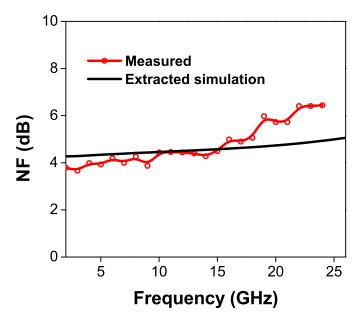

A wideband low noise amplifier (LNA) was designed and implemented in a 120-nm SiGe BiCMOS technology. Resistive shunt-shunt feedback is employed to achieve wideband gain and matching characteristics, and it is shown that addition of small reactive elements can extend the bandwidth of the amplifier significantly. Measured data for the LNA show 9.5 dB gain with less than 1.0 dB variation over a frequency range of 3-26 GHz. Input and output reflection coefficients ( $S_{11}$  and  $S_{22}$ ) are better than -10 dB over the entire bandwidth. The measured noise figure (NF) is less than 5 dB below 18 GHz and rises to only 6.5 dB at 24 GHz. In addition, the amplifier exhibits excellent linearity performance, with a input-referred third-order intercept point (IIP3) of 5.8 dBm and input-referred 1 dB compression point (P1dB) of -5.6 dBm. The SiGe amplifier occupies 0.48 mm<sup>2</sup> (including pads) and consumes 33 mW of power while operating on a 3.3 V supply.

Wideband low noise amplifiers are critical components of virtually all broadband communication systems. In recent years, allocation of the 3-10 GHz frequency band for ultra-wide band (UWB) applications has fueled tremendous interest in this domain [22] and resulted in a flurry of publications [23], [24], [25], [26]. Wideband LNAs also find extensive application in instrumentation, optical communication, and software defined radios. An amplifier with good matching and noise performance is essential to all such applications.

Known wideband amplifiers can be categorized into four different topologies. Narrow-band concepts can be extended for broadband applications by having higherorder matching networks at the input and output. But inclusion of a large number of inductances and capacitances becomes prohibitively costly in terms of chip area, and the inherent low quality-factor (Q) of such passive elements for monolithic implementation in silicon degrades the noise performance. Common-base or common-gate amplifiers provide inherent wideband characteristics but suffer from low gain and high noise figure. Distributed amplifiers, while being the best choice for extremely large bandwidth, suffer from large die area and high power consumption. Resistive-feedback LNAs, on the other hand, provide a compact solution with good wideband noise performance and low power consumption. Several implementations covering the 3-10 GHz UWB band can be readily found in the literature. Traditional inductor-less resistive-feedback LNAs provide a very compact solution, but at the same time limits the achievable maximum operating frequency. In the present paper, we investigate the limits of the resistive-feedback LNA topology and demonstrate how its operating bandwidth can be further extended by using small inductances, with very little area penalty.

There has been some discussion in the literature along similar lines in recent years [27], [28]. In [27], for instance, use of a  $\pi$ -matching network at the input has been shown to improve input matching. In this work, the effects of a matching network on the input matching, gain and noise are analyzed in the context of a SiGe amplifier. A design approach, that exploits the parasitic elements in the circuit to implement the matching network and improves performance, is presented. Theoretical analysis of the impact of reactive matching on resistive-feedback amplifier is presented in section 2.1. In section 2.2, the implementation details of the present LNA are discussed. Measurement results and a comparison with other published data are given in section 2.3, followed by a summary.

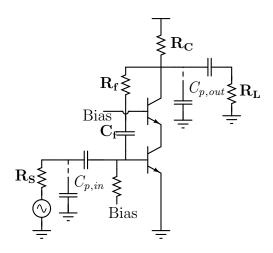

Figure 6: Schematic of a generic shunt-shunt resistive-feedback LNA.

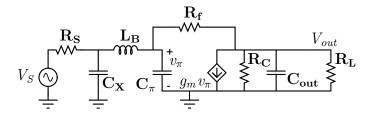

# 2.1 Analysis of a Resistive-Feedback Amplifier with Reactive Matching

Figure 6 shows a resistive shunt-shunt feedback amplifier in its standard form, with parasitic capacitances added to the input and the output nodes. A small-signal equivalent model is shown in Figure 7, in which the parasitic capacitances are absorbed into the input and output capacitances ( $C_{in}$  and  $C_{out}$ ). At low frequency, under the assumption that the device input impedance is much higher than  $R_f$ , straightforward analysis yields expressions for input and output resistances, which can be expressed as

$$R_{in} = \frac{R_f + R_L'}{1 + g_m R_L'} \tag{1}$$

and

$$R_{out} = R_C || (\frac{R_f + R_S}{1 + g_m R_S}), \tag{2}$$

where  $R'_L = R_C ||R_L$ . In the following analysis, we examine how the capacitances cause the impedances to depart from their ideal values and how this situation can be improved by designing a revised matching network. The effects of reactive matching on gain and noise is also considered.

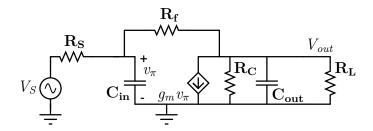

Figure 7: Small-signal model of a resistive-feedback amplifier.

### 2.1.1 Input Matching

The assumption of very high device input impedance breaks down at high frequencies. Device input capacitance, represented by  $C_{\pi}$  in the small-signal model, moves the input impedance  $(Z_{in})$  away from its ideal value. Any parasitic capacitance present at the input node, due to DC blocking capacitance or bondpads, adds to the effect and further deteriorates the input matching. The input impedance, including these described effects, can be expressed as

$$Z_{in} = R_{F,in} || \left(\frac{1}{j\omega C_{in}}\right), \tag{3}$$

where  $R_{F,in} = (R_f + R'_L)/(1 + g_m R'_L)$  and  $C_{in} = C_{\pi} + C_{p,in}$ . The small-signal equivalent circuit is shown in Figure 8.

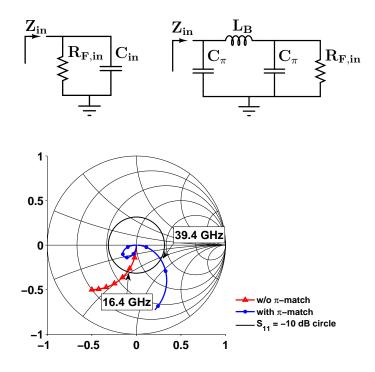

$R_{F,in}$  is often designed to be equal to  $R_S$ , which is usually 50  $\Omega$  for most RF systems. Under that assumption, we start from a perfect match at DC and the locus of the reflection coefficient moves along a constant conductance circle, as shown in Figure 8.

The condition of  $S_{11}$  being less than 10 dB can be taken as a reasonable measure for good input matching and expressed as

$$20.\log \left| \frac{1/R_S - 1/R_F - j\omega C_{in}}{1/R_S - 1/R_F + j\omega C_{in}} \right| < -10, \tag{4}$$

which can be simplified to

Figure 8: Equivalent small-signal representation of input impedance: (a) without matching and (b) with  $\pi$ -matching network. (c) Loci of  $S_{11}$  with and without  $\pi$ -matching network at the input.

$$\omega^2 < (-1 + 3.84/r - 1/r^2) \cdot \frac{1}{R_S C_{in}^2},$$

(5)

where  $r = R_F/R_S$ . From Equation (5), it can be easily found out that the input matching bandwidth is maximized for r = 0.72. But a smaller  $R_F$  would also mean a higher noise contribution from the feedback resistor and hence will degrade overall amplifier noise figure.

The input matching bandwidth can be extended if an inductor  $(L_B)$  is added at the base of the input device. Figure 8 shows the transformed equivalent circuit as far as the input impedance is concerned.  $L_B$  separates the device capacitance  $(C_{\pi})$ from the parasitic capacitances and forms a  $\pi$ -matching network. For the following analysis, it is assumed that the  $\pi$  network is symmetric. This can be achieved by adding capacitance to the input node if necessary. Figure 8 shows the locus of  $S_{11}$ on the Smith Chart and Figure 9 shows how the  $S_{11}$  magnitude compares to the

Figure 9:  $S_{11}$  with and without the  $\pi$ -matching network at the input.

standard resistive-feedback amplifier. In addition to DC, the  $\pi$ -matching network provides perfect matching at  $\omega_0/2\pi$ . The frequency  $\omega_0$  can be easily found by noting the frequency at which the reactive part of  $Z_{in}$  goes to zero and can be expressed as

$$\omega_0 = \sqrt{\frac{2}{L_B C_\pi} - \frac{1}{R_{F,in}^2 C_\pi^2}}. (6)$$

If  $\omega_0$  is not too far from DC,  $S_{11}$  stays below -10 dB for all intermediate frequencies and the matching bandwidth is thus greatly increased. In [27], it has been shown that a reasonable choice for  $\omega_0$  is

$$\omega_0 = \frac{1}{\sqrt{L_B C_\pi}},\tag{7}$$

and the resultant bandwidth is given by

$$f_{10dB} = \frac{1}{2\pi} \sqrt{\frac{\sqrt{10} + 3}{\sqrt{10} + 1}} \cdot \frac{1}{\sqrt{L_B C_\pi}}.$$

(8)

Figure 10: Small-signal model of the resistive-feedback amplifier for use in gain computation.

#### 2.1.2 Gain

The small-signal equivalent circuit for computation of the gain is shown in Figure 10. It can be easily seen that the input matching network forms a third-order low-pass filter and there is another pole at the output. An exact analytical expression for small-signal gain  $(A_V = V_{out}/V_S)$  is too cumbersome to provide much insight. Under the assumption of  $C_X = C_{\pi} = C$  and  $R_S = R_{F,in} = \sqrt{L_B/2C_{\pi}} = R$  (where  $R_{F,in} = (R_f + R_L')/(1 + g_m R_L')$ ), the small-signal gain can be expressed as

$$A_V = \frac{1/2}{s^3(\frac{LRC^2}{2}) + s^2(LC) + s(\frac{L}{2R} + RC)} \cdot \frac{-g_m(R_F||R_L')}{1 + s(R_F||R_L')C_{out}},$$

(9)

where  $R'_L = R_C || R_L$ .

The key difference between this result and a purely resistive-feedback amplifier lies in the input matching network. The device input capacitance  $(C_{\pi})$  is absorbed in the  $\pi$  section. A first-order pole at the input  $(1/(R_S||R_{F,in}||\frac{1}{j\omega C}))$  is replaced by a third-order low pass filter with a cut-off frequency  $(1/\sqrt{LC/2})$ , which is typically higher and thus improves overall frequency response. A comparison of the frequency response of  $S_{21}$  with and without the matching network is shown in Figure 11.

#### 2.1.3 Noise

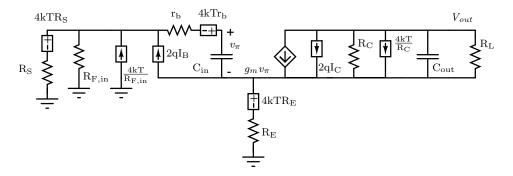

The small-signal model of the LNA including all significant sources of noise is shown in Figure 12. Noise contributions from  $R_E$  and  $r_b$  are included, although the effect of

Figure 11: Effect of input-matching network on  $S_{21}$ .

Figure 12: Small-signal model of a generic resistive-feedback amplifier including noise sources.

$r_b$  is excluded from impedance calculations to reduce complexity. Equivalent input referred noise can be expressed as

$$v_{ni}^{2}/\Delta f = 4kT(R_{S} + r_{b} + R_{E}) + \left(\frac{4kT}{R_{F,in}} + 2qI_{B}\right)$$

$$.(R_{S}||R_{F})^{2} + 2qI_{B}.R_{E}^{2}$$

$$+ \frac{4kT/R_{C} + 2qI_{C}}{g_{m}^{\prime 2}} \left| 1 + j\omega(R_{S}||R_{F,in})C_{\pi}^{\prime 2} \right|, \tag{10}$$

where  $g'_{m} = g_{m}/(1 + g_{m}R_{E})$  and  $C'_{\pi} = C_{\pi}/(1 + g_{m}R_{E})$ . Noise figure can be calculated as  $v_{ni}^{2}/(4kTR_{S})$ . It can be readily seen from (10) that low frequency noise

Figure 13: Effect of input-matching network on noise figure.

can be reduced by reducing  $R_E$  and increasing  $R_{F,in}$ , as expected.

With increasing frequency, collector current shot noise and load resistor thermal noise contributions increase, which is captured in the last term of Equation (10). This is due to the pole associated with the input node of the amplifier. Signals traveling through the pole get reduced in magnitude beyond the 3-dB cutoff frequency, but noise originating after the location of the pole  $(2qI_C \text{ and } 4kT/R_C)$  is not affected, hence degrading the signal-to-noise ratio (SNR).

As discussed above, inclusion of the  $\pi$  matching network moves the input pole to higher frequency and hence increases the frequency at which the noise figure rapidly increases. In other words, the  $\pi$ -matching networks helps to maintain a flat noise figure across frequency, as shown in Figure 13.

## 2.2 Implementation

An LNA demonstrating this design approach was implemented in a 120-nm SiGe BiCMOS process with 7 metal layers. The SiGe HBTs have a peak  $f_T$  of 200 GHz. The devices were biased well below their peak  $f_T$  current density to optimize noise

Figure 14: Schematic of the resistive-feedback LNA with reactive components for improved matching.

performance. The schematic is shown in Figure 14. An emitter degeneration resistor  $(R_E)$  was included to improve linearity. The effect of emitter degeneration can be easily included in the above analysis on matching performance by simply modifying the transconductance  $(g_m)$  and input capacitance of the device  $(C_\pi)$  by the degeneration factor  $(1/(1+g_mR_E))$ . Parasitic capacitances at the input node  $(C_{p,in})$ , due to the bondpad and decoupling capacitor) along with the base inductance  $(L_B)$  and the device input capacitance  $(C_\pi)$ , forms the input  $\pi$ -matching network. The implemented  $\pi$  network is not perfectly symmetric, but still results in a substantial performance improvement. A gain peaking inductor  $(L_C)$  was added to further boost the gain at high frequencies and flatten the gain response across frequency.

A die microphotograph of the LNA is shown in Figure 15. The die area including bondpads is 0.8  $\mu$ m x 0.6  $\mu$ m. This LNA is entirely monolithic and does not require any external bias-tee or RF-choke.

## 2.3 Measurement Results

On-wafer measurements were performed using a VNA for S-parameters and a spectrum analyzer for noise measurements. Measured S-parameters and comparison with

Figure 15: Die microphotograph of the wideband SiGe LNA.

Figure 16: Measured and extracted input return losses  $(S_{11})$  of the wideband SiGe LNA.

simulations are shown in Figure 16, Figure 17 and Figure 18. The measured gain  $(S_{21})$  is nominally 9 dB (Figure 17) and exhibits a very flat frequency response, with less than 1 dB variation over a frequency range of 2-30 GHz. Measured input reflection coefficient  $(S_{11})$  is less than -10 dB over 2-30 GHz. The effect of the input  $\pi$ -matching network can be clearly seen in Figure 16 as the dip in the  $S_{11}$  curve around 20 GHz.  $S_{22}$ , as shown in Figure 18, is better than -10 dB over 3-26 GHz. It should be noted that the low frequency limit of matching is imposed by the DC blocking networks at the input and the output and can be improved by increasing the size of the DC

Figure 17: Gain  $(S_{21})$  vs. frequency of the wideband SiGe LNA: comparison of measured and parasitic-extracted simulation results.

blocking capacitors, at the cost of increased die area and parasitic.

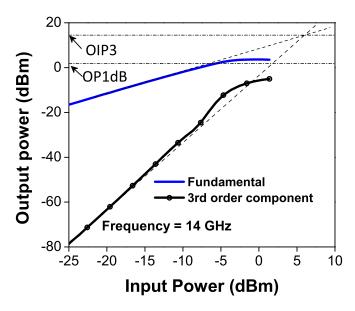

Simulated and measured noise figure are shown in Figure 19. The measured noise figure remains below 4.5 dB over 2-14 GHz. Beyond 18 GHz, the measured data did not match simulation very well, but the noise figure was still under 6.5 dB up to 24 GHz. Linearity, as shown in Figure 20, is excellent, with an output IP3 of 15 dBm and 1dB compression point of 1.85 dBm. Emitter degeneration was used to improve linearity, at the cost of increased noise figure. Noise performance of the LNA can be improved for a less stringent linearity requirement. The amplifier draws 10 mA from a 3.3 V supply.

Comparison with other published data are presented in Table 1. The SiGe LNA implemented in this work excels in terms of gain flatness over bandwidth of operation and linearity performance. The noise figure is slightly higher than some of the other designs, but that is due to its inherent trade-off with linearity. It should be noted that this LNA does not require any external component to function. In contrast, [27] requires an external RF choke and thus the present design enjoys an advantage in

Table 1: Performance summary and comparison with other published wideband LNAs

|           | BW<br>(GHz)  | $S_{21}$ (dB) | Gain<br>var.<br>(dB) | NF<br>(dB)<br>(3-10<br>GHz) | NF (dB)                    | IIP3<br>(dBm) | P1dB<br>(dBm) | Power (mW) | Die<br>Size<br>(mm²) | Technology               |

|-----------|--------------|---------------|----------------------|-----------------------------|----------------------------|---------------|---------------|------------|----------------------|--------------------------|

| This work | 3-26         | 9             | < 1                  | < 4.5                       | < 6.5                      | 5.8           | -5.6          | 33         | 0.48                 | 120-nm SiGe BiCMOS       |

| [28]      | 0.1-<br>14   | 10.9          | 3                    | $2.7-\ 3.5$                 | 2.7–3.7                    | -3.8          | _             | 14.4       | 0.031                | 130-nm<br>CMOS           |

| [29]      | 0.1-<br>20   | 11.2          | 3                    | _                           | 3.3–5.5                    | -2.5          | 1             | 20.4       | 0.35                 | 90-nm<br>CMOS            |

| [27]      | 1.6-<br>28   | 9.6           | 2.2                  | $2.92-\ 3.23$               | 2.92-4.4                   | 4             | -9            | 21.6       | 0.139                | 90-nm<br>CMOS            |

| [30]      | 1.2-<br>11.9 | 8.73          | 1.94                 | $4.5-\ 5.1$                 | _                          | -6.2          | -             | 20         | 0.59                 | 180-nm<br>CMOS           |

| [31]      | 0-<br>22.1   | 9.2           | 3                    | _                           | 4.3–6.6<br>(0.5-15<br>GHz) | -2.67         |               | 8.4        | 0.131                | 90-nm<br>CMOS            |

| [32]      | 1-25         | 11.5          | 3                    | _                           | 3.5-4.5                    | 15.5          | 4.5           | 900        | 1.44                 | 200-nm<br>GaN<br>HEMT    |

| [25]      | 3-10         | 20            | 1                    | 3.05–<br>4.5                | _                          | -11.7         | _             | 42.5       | 0.52                 | 200-nm<br>SiGe<br>BiCMOS |

| [33]      | 3-20         | 19.1          | 5                    | _                           | 4.2–5.2<br>(8-18<br>GHz)   | -6            | _             | 116        | 0.09                 | 180-nm<br>SiGe           |

terms of die area, noise figure and gain. It can be inferred that overall performance of this wideband SiGe LNA is competitive with other state-of-the-art designs, in CMOS or III-V platforms, some of which are implemented in more aggressive technology nodes.

# 2.4 Summary

Analysis and design of a wideband SiGe low-noise amplifier (LNA) was presented. It was shown that by adding small inductors into the scheme of resistive-feedback amplifier design, matching can be greatly improved. The effects of a  $\pi$ -matching network at the input of the LNA on matching, gain, and noise performance were

Figure 18: Output matching  $(S_{22})$  across frequency of the wideband SiGe LNA: comparison of measured and parasitic-extracted simulation results.

Figure 19: Noise figure vs. frequency: comparison of measured and parasitic-extracted simulation results.

analyzed theoretically. The design approach of combining reactive matching with resistive feedback improves performance as compared to a traditional shunt-shunt resistive-feedback amplifier, at the cost of slightly increased die area.

Figure 20: Output power vs. input power for fundamental and 3rd order components showing OIP3 and OP1dB.

#### CHAPTER III

### ADAPTIVE IMAGE-REJECT MIXER

A wideband (6-20 GHz) SiGe adaptive image-reject mixer with an intermediate-frequency (IF) around 1.8 GHz was designed and fabricated in a 200-nm SiGe BiC-MOS process with a peak  $f_T$  of 150 GHz. The mixer can be automatically healed to deliver consistent performance by nullifying the effects of process variations, environmental changes, and aging. The mixer can also be adapted to different specifications.

The image-rejection ratio (IRR) of quadrature-downconversion based mixer architectures may degrade significantly in the presence of scaling-induced process variations [34]. Complex image-reject architectures are used to reduce sensitivity to process variation at the cost of increased die area and power consumption. Even with the use of complicated architectures, IRR degradation due to mismatch remain a problem [35]. The designed image-reject (IR) mixer corrects for amplitude imbalances in the I and Q paths and consistently delivers high IRR. In addition to that, other key mixer parameters, such as conversion gain and linearity, can also be tuned to meet particular performance requirements.

The self-healing mixer, in its envisioned final form, should be a monolithic entity which can heal itself without any external intervention. In section 3.1, the design of the mixer and results of the healing experiment with external signal sources are described. In the next step, the mixer was integrated with on-chip amplitude locked loops (ALL) and DACs. The ALLs provide test signal sources and the DACs enable digital control. The detailed description and results are in section 3.2. In the final part (section 3.3), a monte-carlo simulation based method to verify effectiveness of healing is described.

Figure 21: Block diagram of the image-reject mixer. The voltage and current biases are used as control elements to tune different performance metrics.

## 3.1 Healing using External Sources

#### 3.1.1 System Architecture

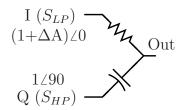

A block diagram of the IR mixer is shown in Figure 21. The mixer consists of a quadrature-downconversion stage, two variable gain amplifiers (VGAs) in the in-phase and quadrature (I and Q) paths, a two-stage polyphase filter for image rejection, a three-stage polyphase filter for quadrature signal generation, and another VGA at the output. The overall mixer can be described as a variation of the Hartley architecture using passive RC polyphase filters to provide the required phase shift and subsequent summation for image rejection [36].

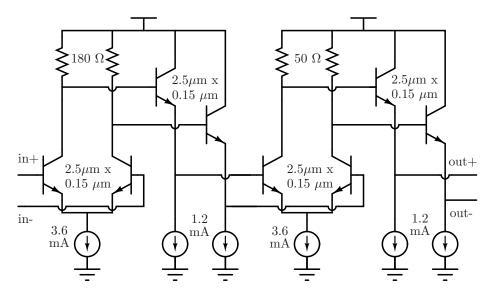

#### 3.1.1.1 Quadrature Mixer

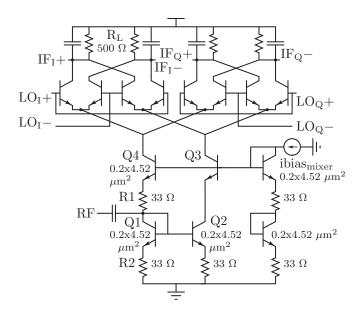

Quadrature down-conversion is accomplished by a micromixer (Fig. 22), which was chosen for its superior linearity and inherent wideband input matching capability [37]. The input is matched to  $50 \Omega$  using a parallel combination of resistor R1 in series with the  $1/g_m$  impedance of the Q1 and the impedance looking into diode-connected Q4, which is degenerated by the resistor R2. The class-AB input stage consisting of Q2-Q4 provides excellent linearity, even under large signal condition. Individual currents out of the transistors Q2 and Q4 are nonlinear, but their combination remain linear [37] for

Figure 22: Schematic of the quadrature micromixer.

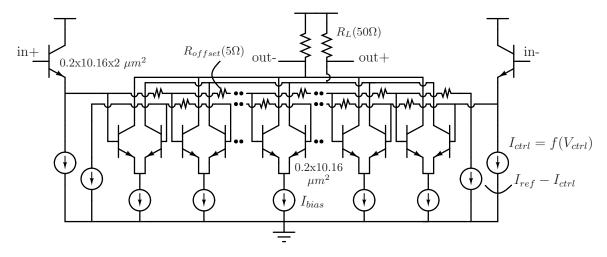

Figure 23: Schematic of the multi-tanh VGA circuit with 'elastic'  $g_m$ .

Figure 24: 'Elastic transconductance' of the multi-tanh VGA. The bold curves show the overall transconductance  $(G_m)$ , which is the superposition of the individual transconductances  $(g_m)$ . By changing the offset voltage between the individual  $g_m$  characteristics, linearity can be traded off for gain and vice-versa.

a wide range of input signal amplitude. Transistor Q3 is added to improve symmetry and balance. The input RF stage is shared between the I and Q paths. Common input transistors have an important advantage from a noise perspective. Noise generated by these transistors in the image frequency band are correlated in the I and Q paths and are canceled along with the image at the IF output. The resulting noise figure can be about 3 dB lower compared to the case when the noise is not correlated.

The wide bandwidth of the mixer can be attributed to two things:

- The down-converter (micromixer) does not use any resonant LC circuit.

- The input matching is implemented by means of a resistance in series with 1/gm of the HBTs.

This wideband nature is a typical characteristic of micromixers that do not use inductors, and comes at the cost of a relatively high noise figure. Small devices (Q1-Q4 in Fig. 22) were used to reduce the device capacitances and extend bandwidth. The use of small devices with high base resistance also adds to the noise figure of the mixer.

#### 3.1.1.2 VGA

The VGAs in the I and Q paths serve the dual purpose of increasing the overall gain and canceling out I-Q imbalances by introducing gain offset. A multi-tanh, 'elastic'  $g_m$  based topology [38,39] was chosen because of the flexibility it offers in terms of controlling gain and linearity. Each VGA consists of 13 differential pairs arranged in parallel (Fig. 23), with two emitter-followers driving their inputs. The overall transconductance  $(G_m)$ , which results from the superposition of individual  $g_m$ 's of the differential pairs, is linear over a wider range of input voltage swing. Voltage offsets between individual  $g_m$ 's is the voltage drop across  $R_{offset}$ . These offsets can be varied continuously by changing a control voltage  $(V_{ctrl})$  and thus changing shape of  $G_m$  (Fig. 24).  $R_{offset}$  and the bias current were chosen to allow offset variation from 0 to 50 mV, which corresponds to high gain and high linearity modes, respectively.

Figure 25: 2-stage complex polyphase filter for image rejection.

Changing the control voltage allows a direct trade-off between gain and input P1dB. The VGA's gain can also be varied by changing the tail current of the differential pairs independent of the control voltage.

The VGA at the output acts as a buffer between the image reject polyphase filter and output load. The linearity of this VGA dictates the overall linearity of the complete system. In addition, it also provides an additional degree of freedom for controlling the mixer gain. The load resistance of the VGAs were chosen to be 50  $\Omega$  so that the output is matched to differential 100 ohm load.

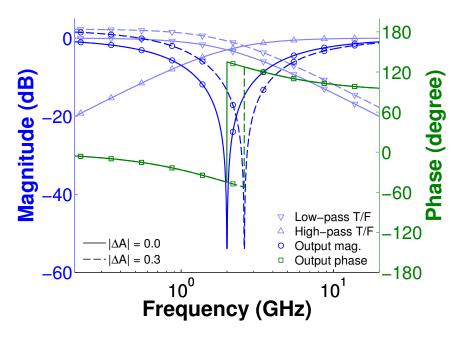

To avoid unwanted oscillations due to capacitive loading of the emitter-followers, a shunt R-C network ( $R_S$ - $C_S$  in Fig. 23) was added to the input. The pole frequency was chosen such that it provides high impedance at the intended operating frequency, and thus does not have significant impact on normal operation. At higher frequencies, however, the shunt resistance compensates for any negative resistance seen at the base, thereby stabilizing the circuit.