# A SYSTEM DESIGN APPROACH TO NEUROMORPHIC CLASSIFIERS

A Thesis Presented to The Academic Faculty

by

Shubha Ramakrishnan

In Partial Fulfillment

of the Requirements for the Degree

Doctor of Philosophy in the

School of Electrical and Computer Engineering

Georgia Institute of Technology May 2013

# A SYSTEM DESIGN APPROACH TO NEUROMORPHIC CLASSIFIERS

#### Approved by:

Professor Jennifer Hasler, Advisor School of Electrical and Computer Engineering Georgia Institute of Technology

Professor David Anderson School of Electrical and Computer Engineering Georgia Institute of Technology

Professor Sung-kyu Lim School of Electrical and Computer Engineering Georgia Institute of Technology Professor Robert Butera School of Electrical and Computer Engineering Georgia Institute of Technology

Professor Eugenio Culurciello School of Biomedical Engineering Purdue University

Date Approved: Jan 2013

#### ACKNOWLEDGEMENTS

I thank my advisor, Jennifer Hasler, for all her support, encouragement, and mentorship. I am deeply grateful to her for introducing me to several exciting areas of research, as well as allowing me freedom to pursue some of my own interests.

I thank my committee members, for the time they have taken to serve on my committee and for their feedback. I am especially thankful to David Anderson for his insight and guidance on noise-suppression and auditory processing.

I met several bright and wonderful people at the ICELAB, whom I enjoyed working with and who taught me a lot. I thank all the members of ICELAB for their help and camaraderie.

I thank my parents for their unconditional love, support, encouragement, and patience. I am grateful to my sister Prabha, for all the phone counseling. I am thankful to my parents-in-law for all their support.

My journey would have been impossible without my husband Rishi, who was with me every step of the way and also made it enjoyable.

# TABLE OF CONTENTS

| AC            | KN(               | VLEDGEMENTS iii                             |

|---------------|-------------------|---------------------------------------------|

| LIS           | т о               | TABLES vii                                  |

| LIS           | T O               | FIGURES                                     |

| $\mathbf{SU}$ | MM.               | RY                                          |

| Ι             | NE                | ROMORPHIC DESIGN FOR ENGINEERING 1          |

|               | 1.1               | Analog Signal Processing                    |

|               | 1.2               | Neuromorphic Engineering                    |

| II            |                   | CH PROCESSING ON A RECONFIGURABLE ANALOG    |

|               | $\mathbf{PL}^{A}$ | FORM                                        |

|               | 2.1               | peech Enhancement                           |

|               |                   | .1.1 Known signal quality                   |

|               |                   | .1.2 Unknown signal quality                 |

|               | 2.2               | Reconfigurable Analog Hardware              |

|               | 2.3               | ystem Components                            |

|               |                   | .3.1 Band Pass filter                       |

|               |                   | .3.2 Envelope Detector                      |

|               |                   | .3.3 Multiplier                             |

|               | 2.4               | ingle Channel System Results                |

|               | 2.5               | Multi-Channel System Results and Discussion |

|               |                   | .5.1 Power consumption                      |

|               | 2.6               | Conclusions                                 |

| III           | TH                | VMM AND WTA AS AN ANALOG CLASSIFIER 32      |

|               | 3.1               | mplementation and Efficiency Overview       |

|               | 3.2               | Hardware: FPAA Implementation               |

|               | 3.3               | Vinner Take All                             |

|               |                   | .3.1 WTA dynamics                           |

|              |     | 3.3.2   | Multiple Winners                                                | 42         |

|--------------|-----|---------|-----------------------------------------------------------------|------------|

|              | 3.4 | Compa   | act VMM Implementations                                         | 43         |

|              | 3.5 | Capab   | oility of VMM+WTA Classifiers                                   | 46         |

|              |     | 3.5.1   | Linear Classifiers                                              | 47         |

|              |     | 3.5.2   | Multi-class Classifiers                                         | 49         |

|              |     | 3.5.3   | Non-linear classifiers                                          | 51         |

|              | 3.6 | System  | n performance characterization                                  | 54         |

|              |     | 3.6.1   | Mismatch compensation                                           | 54         |

|              |     | 3.6.2   | Speed, Power and Efficiency                                     | 55         |

|              |     | 3.6.3   | Temperature Effects                                             | 58         |

|              | 3.7 | Conclu  | asions                                                          | 59         |

| IV           |     |         | IGURABLE NEURON ARRAY WITH PLASTIC SYNA<br>OGRAMMABLE DENDRITES | PSES<br>61 |

|              | 4.1 | A Neu   | romorphic FPGA                                                  | 62         |

|              |     | 4.1.1   | Chip Architecture                                               | 64         |

|              |     | 4.1.2   | Global Interconnect                                             | 65         |

|              | 4.2 | Silicon | Neuron Model                                                    | 65         |

|              |     | 4.2.1   | Silicon Synapses                                                | 66         |

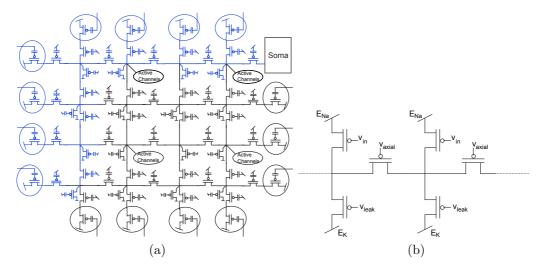

|              |     | 4.2.2   | Dendritic modeling                                              | 68         |

|              |     | 4.2.3   | Neuron Soma                                                     | 69         |

|              |     | 4.2.4   | AER                                                             | 70         |

|              | 4.3 | Dendr   | itic computation                                                | 72         |

|              | 4.4 | Conclu  | asions                                                          | 74         |

| $\mathbf{V}$ |     |         | G GATE SYNAPSES WITH SPIKE TIME DEPEN-<br>ASTICITY              | 76         |

|              | 5.1 | Basics  | of Transistor Learning Synapses                                 | 78         |

|              |     | 5.1.1   | Feed Forward Synapse Computation                                | 79         |

|              |     | 5.1.2   | Synaptic Weight Updates                                         | 82         |

|              | 5.2 | Learni  | ng Algorithm                                                    | 84         |

|               |      | 5.2.1   | LTP Learning Algorithm                        | 84  |

|---------------|------|---------|-----------------------------------------------|-----|

|               |      | 5.2.2   | LTD Learning Algorithm                        | 85  |

|               |      | 5.2.3   | STDP Learning Algorithm                       | 87  |

|               | 5.3  | Mathe   | matical Model                                 | 88  |

|               |      | 5.3.1   | LTP model                                     | 90  |

|               |      | 5.3.2   | LTD model                                     | 90  |

|               |      | 5.3.3   | STDP model                                    | 92  |

|               | 5.4  | Measu   | rements from Spike Based Learning Experiments | 92  |

|               |      | 5.4.1   | STDP Learning Experiments                     | 94  |

|               | 5.5  | Conclu  | ision                                         | 95  |

| VI            | SYS  | STEM    | IMPLEMENTATION                                | 97  |

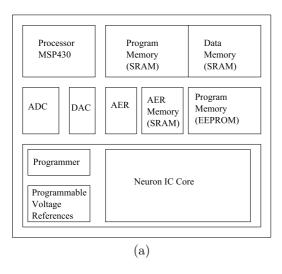

|               | 6.1  | RASP    | 3.0N                                          | 97  |

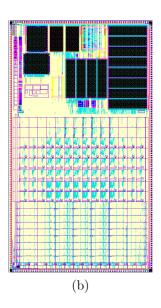

|               |      | 6.1.1   | Neuron RASP Core                              | 99  |

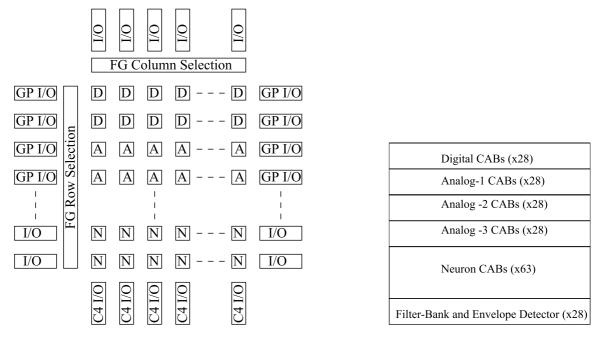

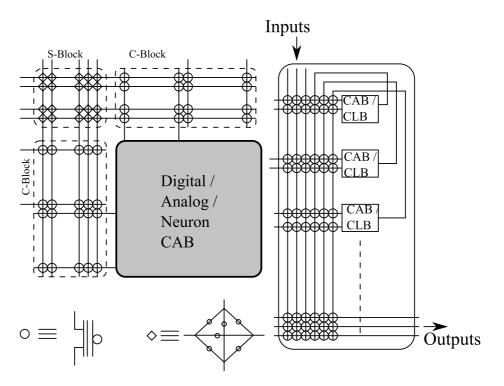

|               |      | 6.1.2   | Neuron Tile                                   | 101 |

| VII           | [CO] | NCLUS   | SION                                          | 107 |

|               | 7.1  | List of | Contributions                                 | 108 |

| $\mathbf{AP}$ | PEN  | IDIX A  | A — A COMPACT VMM                             | 110 |

|               |      |         |                                               | 113 |

|               | D 4  |         |                                               | 110 |

|               |      |         |                                               |     |

# LIST OF TABLES

| 1 | Subjective evaluation of noise suppression algorithm on speech samples |    |

|---|------------------------------------------------------------------------|----|

|   | with added pink noise                                                  | 22 |

| 2 | Power consumption of individual blocks for a 4-channel system          | 23 |

| 3 | Key parameters of the Neuron2 Chip                                     | 66 |

# LIST OF FIGURES

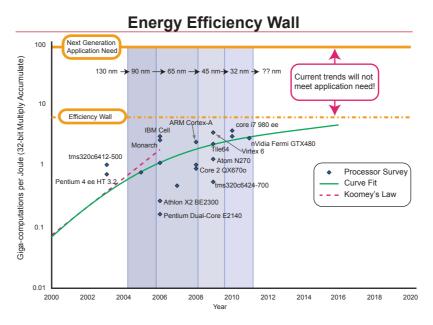

| 1  | Efficiency Wall for Digital Processors                                                   | 2  |

|----|------------------------------------------------------------------------------------------|----|

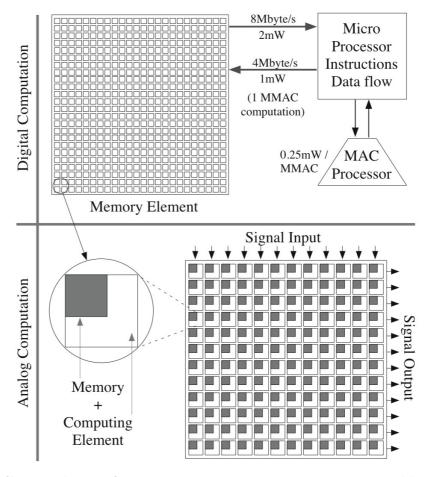

| 2  | Comparison of memory access costs                                                        | 3  |

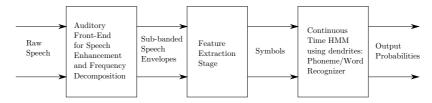

| 3  | System flow for building neuromorphic classifiers                                        | 5  |

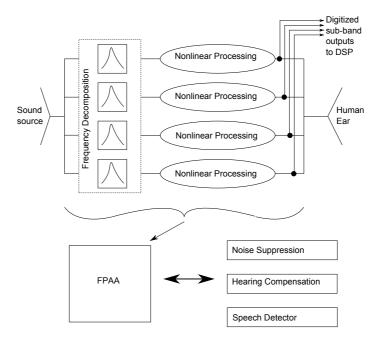

| 4  | High level overview of auditory processing on a reconfigurable platform.                 | 8  |

| 5  | System overview and MATLAB simulation results                                            | 9  |

| 6  | Overview of RASP 2.8a chip                                                               | 11 |

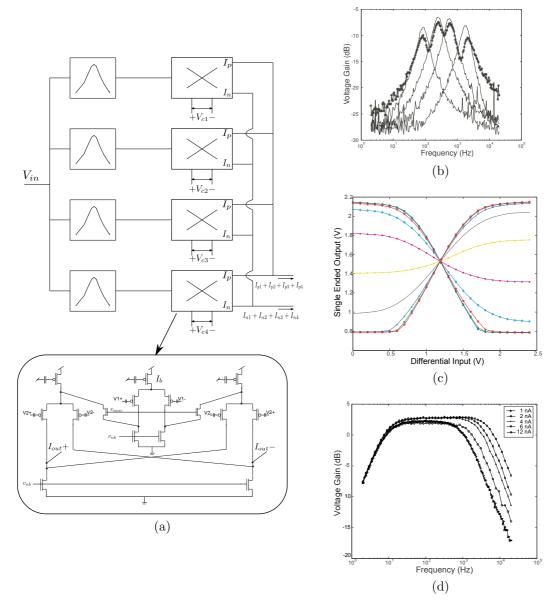

| 7  | Programmable Band Pass Filter                                                            | 15 |

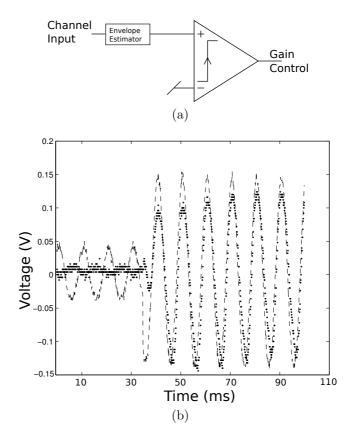

| 8  | Envelope detector: circuit diagram and measurements                                      | 17 |

| 9  | Signal Multiplier: Circuit diagram, DC and transient measurements and frequency analysis | 25 |

| 10 | Single Channel results for envelope thresholding system                                  | 26 |

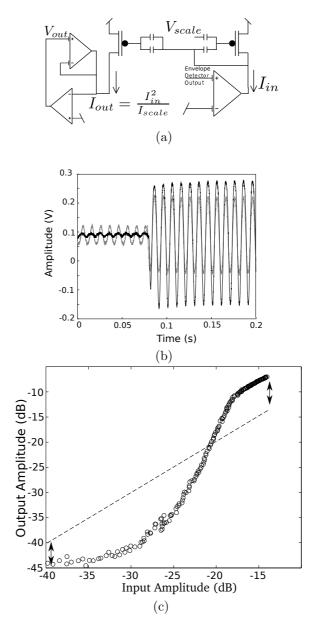

| 11 | Squaring Non-linearity for dynamic range expansion                                       | 27 |

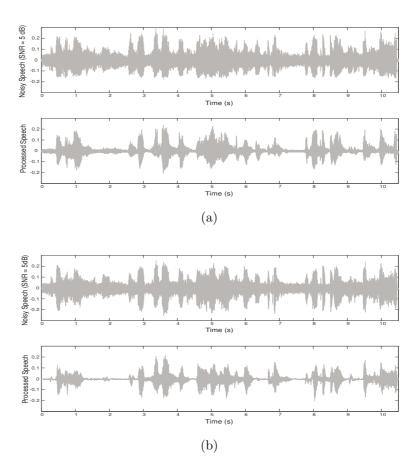

| 12 | Multi-channel System Results                                                             | 28 |

| 13 | SNR Estimation System: block diagram and measured results                                | 29 |

| 14 | Characterization of the translinear product-reciprocal circuit                           | 30 |

| 15 | Effect of limited channels on performance                                                | 30 |

| 16 | Spectrogram of noisy and processed speech                                                | 31 |

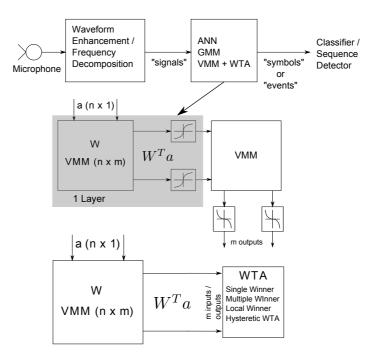

| 17 | Application of VMM+WTA classifiers in an Analog Speech Recognizer.                       | 33 |

| 18 | RASP 2.9v IC overview: specialized infrastructure for building large VMMs                | 35 |

| 19 | Schematic of winner-take-all structures and its input-output characteristics             | 37 |

| 20 | System Block diagram of VMM+WTA classifiers                                              | 38 |

| 21 | Measured dynamic response of WTA to input current step                                   | 39 |

| 22 | k-winner-take-all                                                                        | 40 |

| 23 | 1x2 VMM characterization                                                                 | 43 |

| 24 | Equivalence between VMM topologies                                                       | 45 |

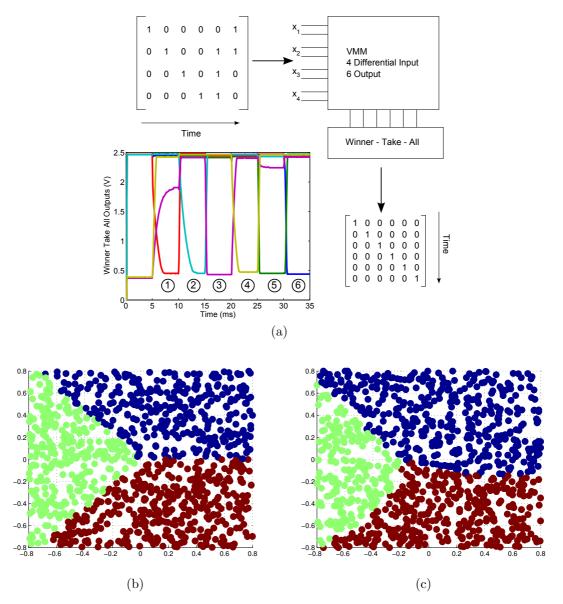

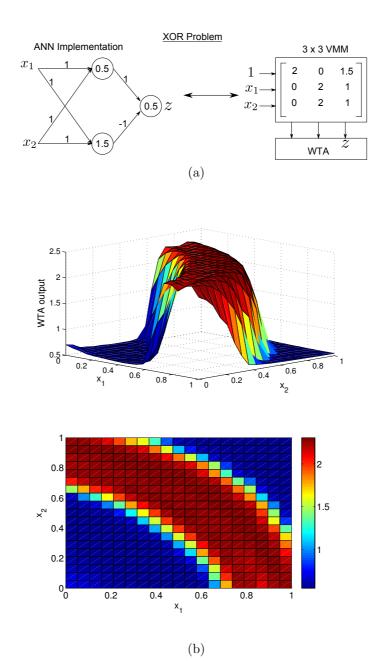

| 25 | Implementation of linear classifiers using VMM+WTA                                       | 48 |

| 26 | Multi-dimensional classifiers                                  | 49  |

|----|----------------------------------------------------------------|-----|

| 27 | Implementation of nonlinear classifiers using VMM+WTA          | 52  |

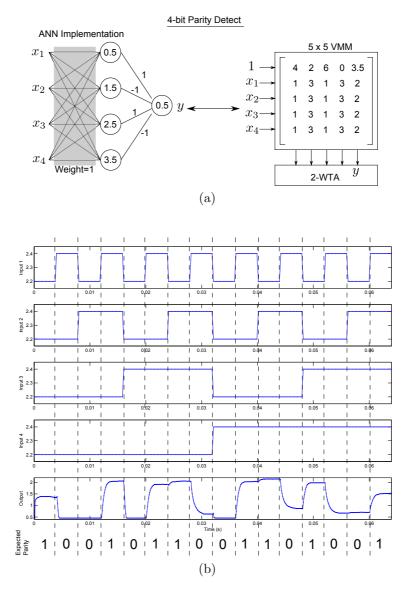

| 28 | Implementation of the four-bit parity problem using VMM+WTA $$ | 53  |

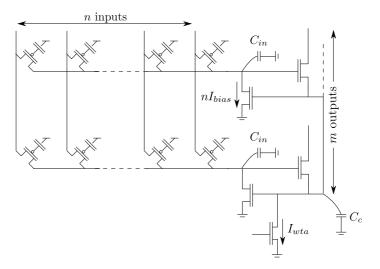

| 29 | Schematic of VMM+WTA circuit: Speed, Power and Efficiency      | 56  |

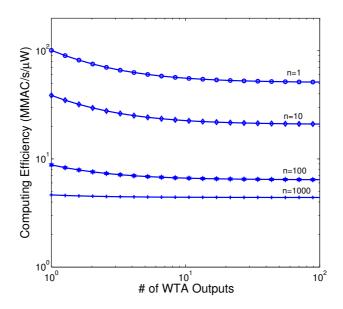

| 30 | Computing Efficiency vs classifier size                        | 56  |

| 31 | Temperature dependence of VMM+WTA classifier                   | 59  |

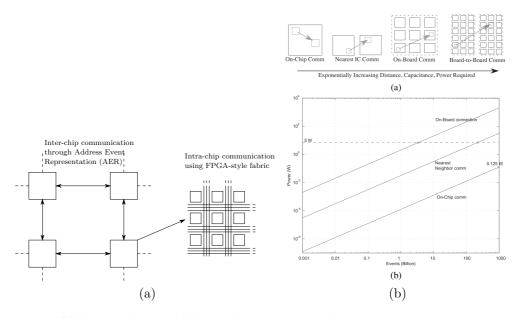

| 32 | Scaling arguments affecting chip design philosophy             | 63  |

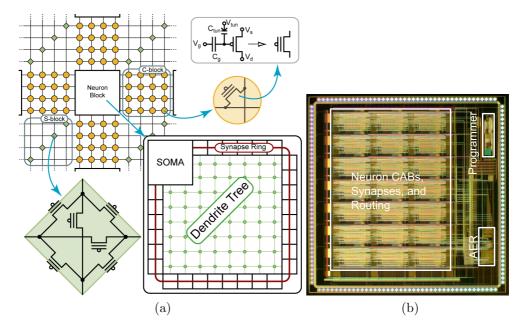

| 33 | Neuron chip architecture                                       | 64  |

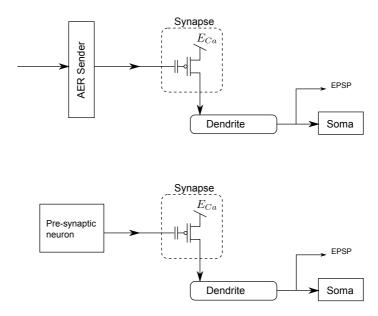

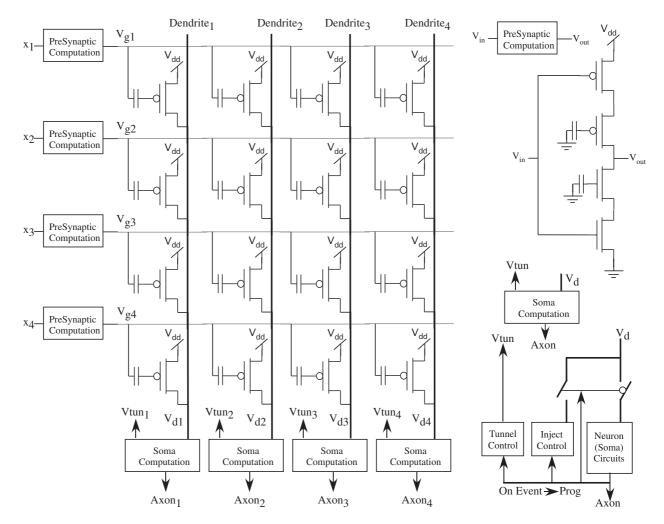

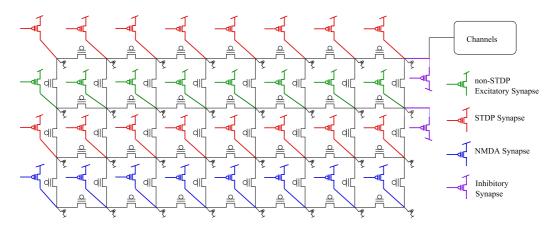

| 34 | Synaptic Inputs                                                | 67  |

| 35 | EPSP and Action Potential                                      | 68  |

| 36 | Programmable dendritic structure in the Neuron2 chip           | 69  |

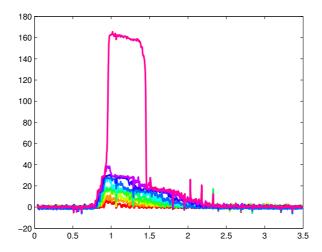

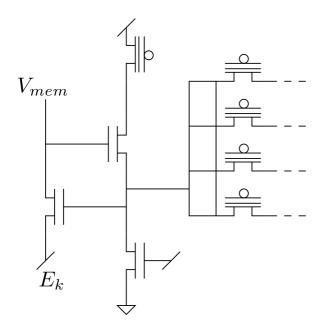

| 37 | Summation of synaptic inputs on the dendrite                   | 70  |

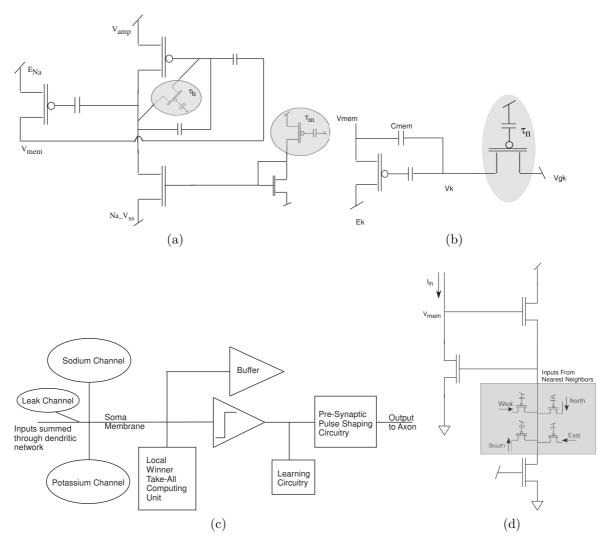

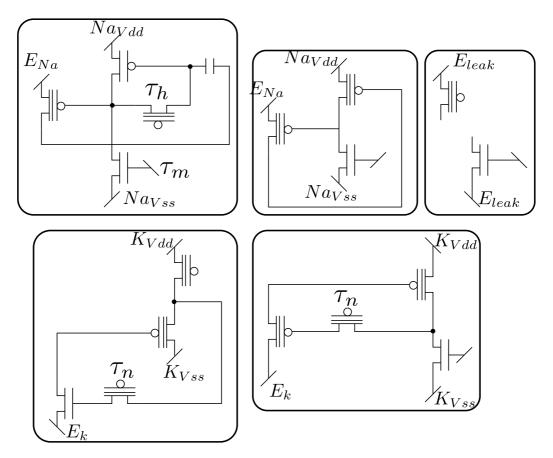

| 38 | Detailed diagram of the configurable soma                      | 71  |

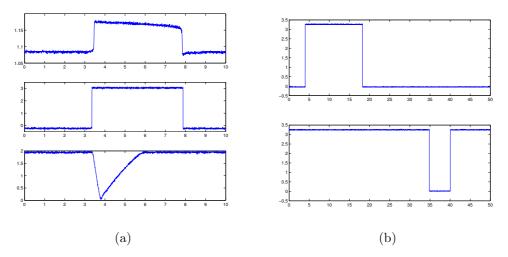

| 39 | Timing waveforms generated as a result of a neuron spike       | 72  |

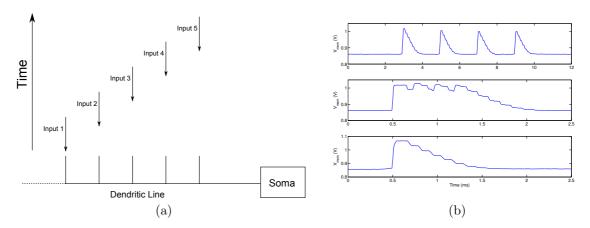

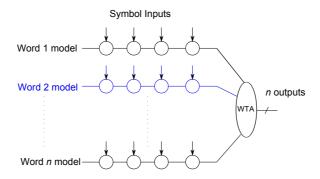

| 40 | Word Detector                                                  | 73  |

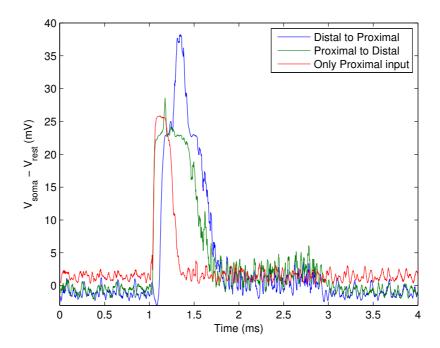

| 41 | Directional Selectivity in the dendrite                        | 74  |

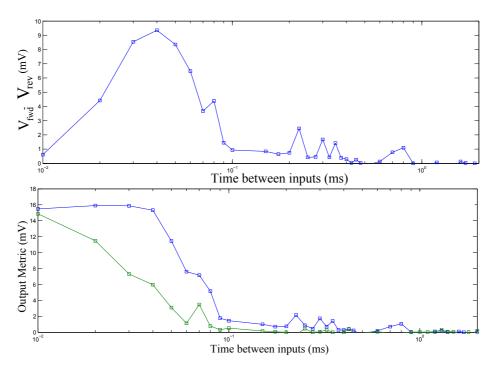

| 42 | Sensitivity of dendrite line to delays between inputs          | 75  |

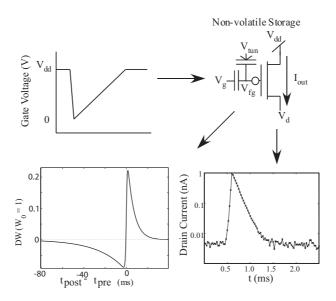

| 43 | Single Transistor Learning Synapse                             | 77  |

| 44 | EPSC before and after learning                                 | 78  |

| 45 | Array for Learning Synapses.                                   | 81  |

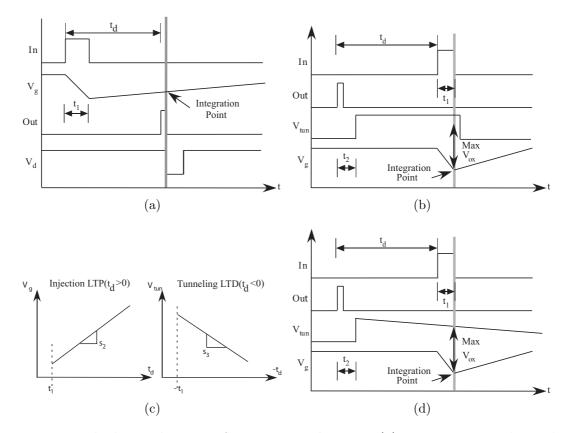

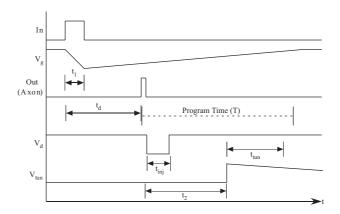

| 46 | Timing Diagram for LTP and LTD                                 | 83  |

| 47 | Timing of the Programming algorithm for the STDP learning rule | 85  |

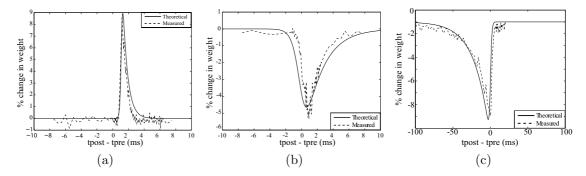

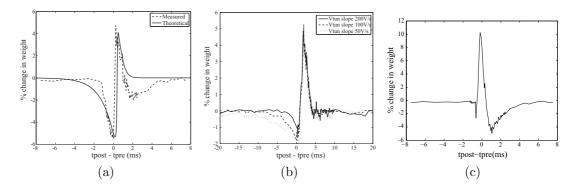

| 48 | Learning Experiments: LTP and LTD                              | 91  |

| 49 | Learning Experiments: STDP                                     | 93  |

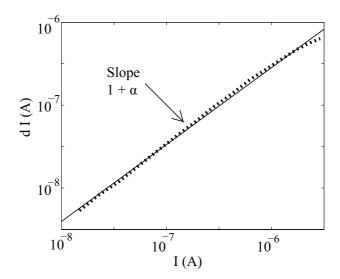

| 50 | Injection Characterization                                     | 96  |

| 51 | A block diagram of the RASP 3.0N IC and its layout             | 97  |

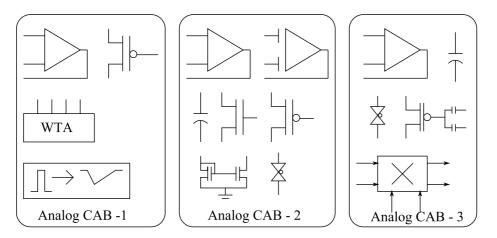

| 52 | CABs in the Neuron RASP IC Core                                | 98  |

| 53 | Tiles in the RASP 3.0N IC                                      | 100 |

| 54 | Components of the Analog CABs                                  | 101 |

| 55 | The Neuron CAB in the RASP 3.0N IC | 102 |

|----|------------------------------------|-----|

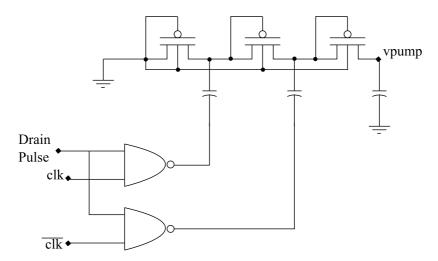

| 56 | Schematic of the charge pump       | 103 |

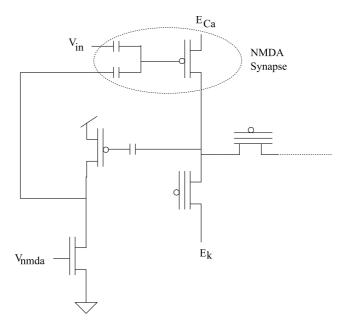

| 57 | Schematic of the NMDA Synapse      | 104 |

| 58 | Channels in the Soma block         | 105 |

| 59 | Modified WTA block                 | 106 |

#### **SUMMARY**

In our attempts to make our devices smarter, smaller, and increase battery lives, we need to consider alternative strategies to mainstream approaches to problem solving - namely analog and neuromorphic solutions for signal processing. Contrary to expectations from Moore's Law predicting an efficiency increase with technology node scaling, the efficiencies of modern digital processors have asymptotically approached 10 Giga Computations per Joule. It is clear that the next generation application need demands a much higher computing efficiency than is possible with following current trends. We need to investigate other techniques to increase computing efficiencies. The two strategies that we deal with in this research are analog and neuromorphic engineering. Carver Mead's hypothesis states that computation using the inherent physics of the device is 1000X more efficient than digital. It has already been shown that for certain functions such as Matrix Multiplication, Frequency decomposition, Analog FFT, Adaptive filtering, Winner Take All, analog is more efficient than digital processing. However, for analog signal processing to be a serious contender to digital techniques, it is essential that the hardware is programmable. Custom analog IC fabrication, although more efficient, is very expensive. Custom analog is also inflexible, making it difficult to make modifications to the processing algorithm or use it for slightly different applications.

Neuromorphic engineering deals with the design of systems that are either inspired by neuro-biological functions or replicate them. However, for real impact, it is essential to demonstrate significant advantages to main stream approaches in engineering applications by introducing a new paradigm of computing, new algorithms for information processing ultimately leading to more intelligent systems. This research deals with developing emulation tools in silicon that enable investigation of neural computing principles and their pertinence to information processing in engineering applications.

Ultimately, this work aims to develop a neuromorphic system design flow for implementing speech classifier solutions, thereby demonstrating significant computational efficiency advantages over other existing implementations. This work uses low-power analog solutions for frequency analysis and feature extraction, and a neuromorphic approach to classification tasks. In doing so, this work also aspires to posit the significance of dendrites in neural computation.

## CHAPTER I

#### NEUROMORPHIC DESIGN FOR ENGINEERING

A large portion of the research in electrical and computer engineering today is directed towards efficient computing to make smart and low power devices. In our attempts to make our devices smarter, smaller, and increase battery lives, we need to consider alternative strategies to mainstream approaches to problem solving - namely analog and neuromorphic solutions for signal processing. The reason for alternate approaches is due to the barrier to computing efficiency observed in today's digital computers. Marr et al published a survey of digital processors currently in the market by plotting their technology node and their computing efficiency [69]. These were inmarket ICs and contrary to expectations from Moore's Law predicting an efficiency increase with technology node scaling, the efficiencies asymptotically approached 10 Giga Computations per Joule. The unit of computation here was considered to be a Million Multiply Accumulate (MMAC) operations, which is a fair metric for comparing DSPs, microprocessors as well as analog processors. We prefer to use the metric of MMAC for computation as opposed to Operations (Ops), since the MMAC actually defines a computation, while an Op could well be a no-Op. The survey from [69] is plotted in Fig. 1. A possible cause for the efficiency wall is the sub-threshold mismatch in devices that worsens as the technology scales. Designers have to spend more power and area compensating for the mismatch. It is clear that the next generation application need for smart devices demands a much higher computing efficiency than is possible with following current trends. We need to investigate other techniques to increase computing efficiencies. The two strategies that we deal with in this research are analog and neuromorphic engineering.

Figure 1: Efficiency Wall for Digital Processors: A barrier to the observed computing efficiency at 10 Giga Computations / Joule is plotted. Technology node scaling does not change the barrier. Sub-threshold mismatch is hypothesized as a reason for this efficiency barrier.

# 1.1 Analog Signal Processing

Carver Mead's hypothesis states that computation using the inherent physics of the device is 1000X more efficient than digital [72]. It has already been shown that for certain functions such as Matrix Multiplication, Frequency decomposition, Analog FFT, Adaptive filtering, Winner Take All, analog is more efficient than digital processing [17, 31]. However, for analog signal processing to be a serious contender to digital techniques, it is essential that the hardware is programmable. Custom analog IC fabrication, although more efficient, is very expensive. Custom analog is also inflexible, making it difficult to make modifications to the processing algorithm or use it for slightly different applications.

Programmable analog processing in the case of a multiplier is more efficient due to the computing element also having memory, as shown in Fig. 2. The local weight storage obviates the need for memory access, as in the case of a digital computing flow, thereby reducing power consumed during computation. Programmable analog also

Figure 2: Comparison of memory access costs: In programmable analog, the computing and storage elements are located close to each other, while in digital they are separated. The cost of computing includes access to the memory.

has the great advantage of canceling mismatch effects using floating-gates. Hence, during the course of this work, we explore programmable analog strategies for signal processing.

# 1.2 Neuromorphic Engineering

Neuromorphic engineering deals with the design of systems that are either inspired by neuro-biological functions or replicate them. The goal of neuromorphic engineering may be developing system emulation tools for neuroscientists for investigative purposes with a significant improvement over fully digital solutions in terms of computing efficiency and size. Systems that closely model biology, with power supplies similar to biology can be used for neural interfacing and stimulation in medical applications. Other goals include high-level modeling of signal processing pathways based on the structure of biological systems for improving performance/efficiency and detailed modeling of neural networks to exploit low-level processing for engineering applications.

In the two decades of its existence, progress has been made in bringing the fundamental principles of neuromorphic engineering to fruition in products like touch-pads and imagers, system designs such as silicon retina/imager, silicon cochlea. However, for greater impact, it is essential to demonstrate significant advantages to main stream approaches in engineering applications by introducing a new paradigm of computing, new algorithms for information processing ultimately leading to more intelligent systems. This research deals with developing emulation tools in silicon that enable investigation of neural computing principles and their pertinence to information processing in engineering applications.

Humans perform much better than current systems at speech recognition tasks. Low-power real-time compact implementations have several wide ranging applications such as in aids for the hearing impaired, search of speech databases, and enhancing human computer interactions. However, the best existing speech recognizers perform poorly on unconstrained speech, and do better with specific talkers when ample training data is available. Among the popular speech recognition algorithms in use today is one that uses Hidden Markov Model (HMM) techniques, but is also the most computationally challenging. However, it consistently performs better than other classifier architectures in speech recognition tasks which make it an attractive option to pursue. The high computation and memory requirements of the algorithm mandate massively parallel designs for real-time, large-vocabulary speech recognizers which raises the barrier for hardware implementation using conventional digital hardware approaches.

Figure 3: System flow for building neuromorphic classifiers.

This work aims to develop a neuromorphic system design flow for implementing HMM-based speech classifier solutions, thereby demonstrating significant computational efficiency advantages over other existing implementations. This work uses low-power analog solutions for frequency analysis and feature extraction, and a neuromorphic approach to classification tasks. In doing so, this work also aspires to posit the significance of dendrites in neural computation, which is often ignored by a significant portion of the neuroscience community.

The system shown in Fig. 3, includes a sensory front-end built based on high-level biological modeling of the cochlea to enhance speech and extract sub-band signal energies. These inputs are transformed into "symbols" or "parts of speech" representation using a weighted summation, after which the probability that a "symbol" is detected is estimated. These input probabilities are supplied to a continuous-time HMM, which computes the output probabilities for phonemes/words.

This document is organized as follows. In Chapter 2, we describe architectures for audio classification front-ends on a reconfigurable analog platform. Real-time implementation of audio processing algorithms involving discrete-time signals tend to be power-intensive. We present an alternate continuous-time system implementation of a noise-suppression algorithm on our reconfigurable chip, while detailing the design considerations. We also describe a framework which enables implementations of other speech processing algorithms, classifier front-ends and hearing aids.

In Chapter 3, a novel classifier structure is presented as a general-purpose, low-power, compact, programmable classifier architecture that is capable of greater computation than a 1-layer neural network, and equivalent to a 2-layer perceptron. The classifier generates event outputs and is suitable for integration with event-driven systems. The main sources of mismatch, temperature dependence and methods for compensation are discussed. We present measured data from simple linear and non-linear classifier structures and analyze the power and computing efficiency for scaled structures.

In Chapter 4, a novel neuromorphic chip that models neurons for efficient computation is discussed. Traditional architectures of neuron array chips consist of large scale systems that are interfaced with AER for implementing intra- or inter-chip connectivity. We present a chip that uses AER for inter-chip communication but uses fast, reconfigurable FPGA-style routing with local memory for intra-chip connectivity. We model neurons with biologically realistic channel models, synapses and dendrites. This chip is suitable for small-scale network simulations and can also be used for sequence detection, utilizing directional selectivity properties of dendrites, ultimately for use in word recognition.

In Chapter 5, we describe a single transistor floating gate synapse device that can be used to store a weight in a non-volatile manner, compute a biological EPSP, and demonstrate biological learning rules such as LTP, LTD and STDP. We also describe a highly scalable architecture of a matrix of synapses to implement the described learning rules. Parameters for weight update in the  $0.35\mu$ m process have been extracted and can be used to predict the change in weight based on time difference between pre- and post-synaptic spike times.

Finally, in Chapter 6, we describe a new IC that integrates all the elements required for building low power, efficient neuromorphic classifiers. We list the choices made in the design process and describe the functional blocks.

## CHAPTER II

# SPEECH PROCESSING ON A RECONFIGURABLE ANALOG PLATFORM

We present a reconfigurable analog chip that can be used as a front-end for audio processing and signal enhancement. The possible benefits of analog in terms of power dissipation per unit computation has long been hypothesized by Mead in [72]. A careful study of the same done in [92] showed that for a particular system, analog processing would be better than digital if the desired signal to noise ratio (SNR) was below a certain value. Since then, there have been several custom analog implementations of various signal processing blocks exploiting this feature [19, 20, 57, 80, 95]. The popularity of analog processing, however has remained far lesser than digital owing to difficulty in design and fixed functionality. However, recent developments in field programmable analog arrays (FPAAs), the analog equivalent of FPGAs, shows great promise in allowing the end user to easily utilize the power of analog processing. The scope of such a structure in performing signal processing was discussed earlier in [108]. FPAAs offer the advantage of rapid prototyping and programmability, allowing the user to implement a wide variety of circuits, unlike expensive custom analog IC fabrication. In this work, we use the FPAA to implement a few signal processing algorithms that are useful in audio processing. We introduce the reader to the trade-offs in implementing a few algorithms on a reconfigurable platform and demonstrate a few examples of noise suppression algorithms based on a physiological model of hearing that use non-linear filtering in different sub-bands. The motivation and approach to audio processing adopted in this work, shown in Fig. 4 is closely

Figure 4: **High level overview:** We envision a range of biologically inspired signal processing algorithms, that fit into the pathway between speech production (source) and perception (human ear). These algorithms are implemented by non-linear processing of sub-banded speech signals for applications such as noise suppression or hearing compensation, by proper choice of the non-linearity. In addition, the outputs of the non-linear processor can be taken at each sub-band, for speech detection instead of recombining to generate a perceptible signal for the human ear.

related to the model for the human auditory system [62]. The frequency decomposition performed by the basilar membrane is modeled using a bank of parallel bandpass filters, with exponentially spaced center frequencies. The inner and outer hair cells, which detect the sound intensity and provide non-linear amplification respectively, are modeled by the non-linear signal processing block. Using this general framework, a variety of non-linear processing can result in applications ranging from noise suppression systems, speech activity detectors, speech classifiers and hearing aid blocks. The signal is recombined post-processing and converted back into an audio signal, or digitized before recombination, providing sub-banded input for further DSP. This structure is amenable to easy implementation on the FPAA, making it an attractive platform for comparing various analog signal processing (ASP) algorithms for audio applications. This chapter is organized as follows: Section II examines a few gain

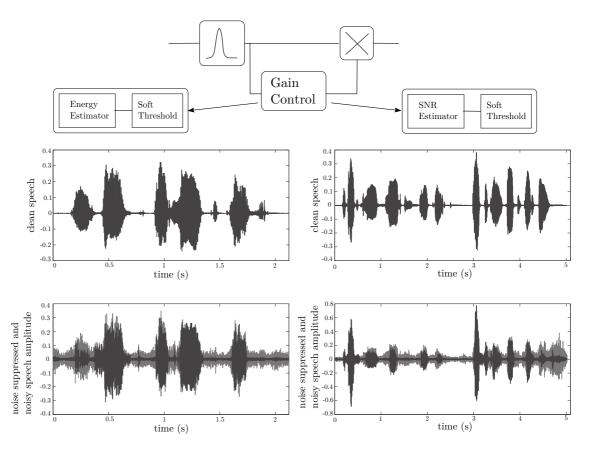

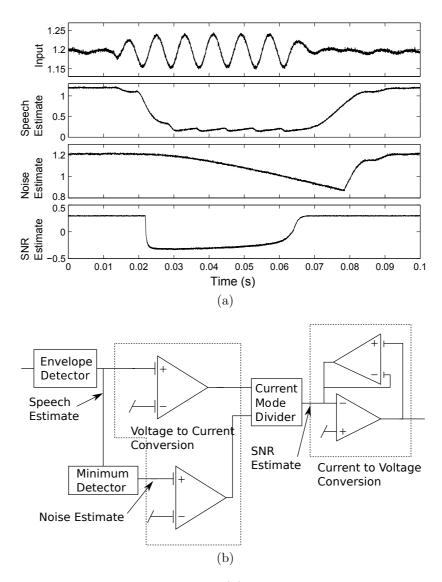

Figure 5: **System Overview:** Top level signal flow consists of frequency decomposition of incoming speech signal into exponentially spaced sub-bands. The non-linear processing consists of signal energy detector and a gain control block which modulates the gain applied to a signal-signal multiplier block. The outputs from the multipliers are then recombined to produce the processed output. For a non-linear processing block consisting of a speech envelope detector and a thresholding block, results from a MATLAB simulation showing clean, noisy(gray) speech with 5 dB SNR and processed speech. MATLAB simulation results for a processing block consisting of an SNR estimator and a threshold block are also shown.

control topologies and their applicability to noise suppression algorithms. Section III provides a short review of the reconfigurable hardware that is being used. Section IV and V discuss circuits and measurement results of individual blocks used in our algorithm and measurement results from a single channel implementing a processing algorithm respectively. In Section VI we present measured results for a few system implementations of noise suppression.

# 2.1 Speech Enhancement

Today, most efforts in audio signal enhancement have been concentrated in processing the digitized signal with Wiener filtering, spectral subtraction and other techniques [58,90]. We consider an approach in which the signal is "enhanced" prior to/instead of digitizing, using the non-linear signal processing blocks available in the FPAA, to propose a solution for speech enhancement. Our solution follows the algorithm previously described in [3, 21], suitable for implementation using analog VLSI. A noisy audio signal x(t) can be represented as

$$x(t) = s(t) + n(t) \tag{1}$$

where s(t) is the signal and n(t) is the noise. We assume the noise is stationary over a longer period of time relative to the speech signal, resulting in a separation of timescales in s(t) and n(t). We estimate the noise  $\hat{n}(t)$ , from x(t) and then modulate the gain of the signal in the following stage. When  $x(t) > \hat{n}(t)$ , our audio signal dominates our noise estimate. Hence, we apply a large gain to the signal, to emphasize speech portions of the signal. When  $x(t) \approx \hat{n}(t)$ , the audio signal is mostly noise and we reduce the signal gain, so that the noisy portions may be suppressed.

Fig. 5 depicts the approach taken in this research for noise suppression. The noisy audio signal is sub-banded using a second-order bandpass filter. We represent an acoustic signal as a sum of band-limited signals; each sub-band representation is further decomposed into a product of an envelope (which carries the instantaneous loudness information) and a rapidly oscillating signal (carrier) of nearly constant power. This signal representation can be applied to auditory analysis by making the signal sub-bands roughly equal in bandwidth to the critical bands in the ear. In particular, the acoustic signal s(t) can be expressed as

$$s(t) = \sum_{i} e_i(t)v_i(t) \tag{2}$$

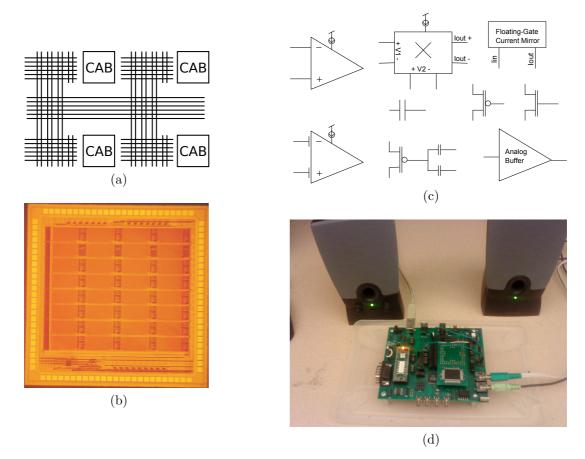

Figure 6: Overview of RASP 2.8a chip: (a) This FPAA consists of computational analog blocks(CABs) embedded in a routing fabric made up of programmable switches. (b) A die photo of the device fabricated in a  $0.35\mu m$  CMOS process. (c) The CAB consists of commonly used analog functional blocks such as OTAs, signal-signal multipliers, transistors, MITEs and capacitors. (d) Our test infrastructure includes a PCB that uses USB for power and communication. The board consists of a micro-controller, DACs, ADCs for programming and testing. The board also has audio ports and amplifiers that can be used to drive speakers.

where  $v_i(t)$  is the speech excitation (high frequency) and  $e_i(t)$  is the speech envelope (low frequency) in the  $i^{th}$  channel. The band-limited signal envelope is estimated using an envelope detector, followed by a gain control block which modulates the gain of the signal provided by a signal-by-signal multiplier.

#### 2.1.1 Known signal quality

The gain control block can be simplified with a priori knowledge of the incoming speech signal quality. For signals with reasonably high SNR, we can assume that

when the sub-banded noisy speech envelope falls below a certain value, there is no actual speech signal and it is mostly noise. A soft thresholding function applied to the envelope estimate then results in attenuation of all signals with an envelope below a certain value and a gain applied to all signals above the threshold. Fig. 5 shows the results from a MATLAB simulation for such a block. This technique results in loss of stand-alone soft sounds in the speech. Furthermore, this algorithm is limited in the sense that it performs poorly on inputs with low SNR.

#### 2.1.2 Unknown signal quality

This method does not make assumptions about the input SNR, but assumes that the temporal characteristics of background noise and speech signal are different [22]. Using that information, we can arrive at a noise estimate based on the noisy input speech. Dividing the noisy speech envelope by the noise estimate gives us a measure of the "instantaneous SNR". A soft thresholding function is now applied to the instantaneous SNR estimate, to emphasize portions of the input with moderate SNR and attenuate portions with low SNR. Fig. 5 plots the simulated results for such an algorithm. This method performed better in retaining soft sounds, unless the masking noise was present in the same band as the soft sound. We also expect that this technique performs better with low SNR inputs. Simulations indicate that a soft-thresholding function is essential to avoid artifacts of processing such as harsh clipping sounds generated due to the switching of the gain-control block output. In this work, we do not consider the non-linearities generated due to soft-thresholding.

# 2.2 Reconfigurable Analog Hardware

The chip used in our implementation has been described previously [6]. Nevertheless, we briefly describe it here for the sake of completeness. The Rasp 2.8a has 32 Computational Analog Blocks (CABs) embedded in programmable routing fabric, as shown in Fig. 6a. The CABs consist of commonly used analog circuit components such

as Operational Transconductance Amplifiers (OTA), signal multipliers, floating capacitors, voltage buffers, multiple-input floating-gate (FG) transistors, transmission gates and transistor arrays. Some of the OTAs have FG inputs to the differential pair (FGOTA) due to the presence of capacitive dividers for increasing input linear range. All of the OTAs, buffers and multipliers are biased using precisely programmable FG transistors giving the user the flexibility to make trade-offs between bandwidth and power consumption. The range of the FG programming is 6 pA to 20  $\mu$ A, with an accuracy of 9.5 floating-point bits [6]. FGs demonstrate excellent charge retention properties, with a charge loss of < 1% over a period of 10 years [104]. The interconnection between the various CAB components is made using the routing fabric which are of various types, allowing the user to select global routing lines for connecting blocks that are spaced far apart, local lines for connecting blocks within the same CAB and nearest neighbor lines, allowing connection between neighboring CABs. These offer flexibility to the user to choose a routing scheme which minimizes parasitic load capacitance for sensitive analog nodes (by choosing local or nearest neighbor lines) or a low resistance path for signals that travel long distances (by choosing global routing lines). Another advantage of this chip is that the interconnect switches are also FG transistors that can be programmed in an analog fashion and not just as ON/OFF switches [107]. Hence these can also be used as circuit elements, increasing the number of computational elements per unit area of the chip. The maximum signal bandwidth through the switch matrix is 57 MHz and the highest achievable filter bandwidth is 5 MHz, which makes it suitable for implementing audio processing algorithms. The test platform for using the FPAA is powered on USB which doubles up as a communication interface. It also has two sound ports for input and output stereo sounds, seen in Fig. 6d. The user can specify the desired signal processing function from a high level interface in SIMULINK, a software product by Mathworks.

An intermediate processing software is used which first converts the SIMULINK description to a SPICE netlist, which is then converted into target switch addresses on the chip [5], [82].

# 2.3 System Components

In this section, we discuss the various components used in the signal flow and present measured results from characterizing each individual block.

#### 2.3.1 Band Pass filter

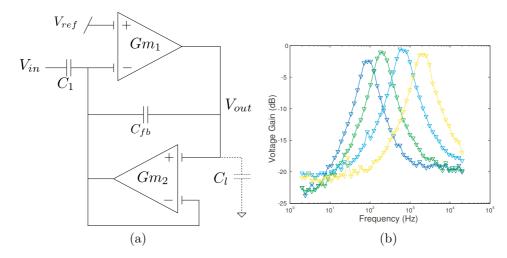

The first stage of the signal processing chain involves frequency decomposition. We use a bank of second-order bandpass filters that have exponentially spaced center frequencies. The basilar membrane can be modeled as a bank of bandpass filters with a 20 dB/decade roll off on the low frequency side, and a steeper roll off on the high frequency side. In practice, a filter with 20 dB/decade roll off is sufficient to separate the signal into bands. In a hearing aid model, we would choose the bandwidth of each filter to equal the bandwidth of the corresponding critical band in the cochlear model. The OTAs and FGOTAs in our chip enable implementation of Gm-C filters with tunable frequency responses. Their bias currents are set by FG devices which can be precisely programmed. The general expression for the subthreshold transconductance of the OTA used is

$$Gm = \kappa I_b / 2 * U_T \tag{3}$$

where  $I_b$  is the bias current,  $\kappa$  is the subthreshold slope of the transistors making up the differential input pair of the OTA and  $U_T$  is the thermal voltage. Fig. 7a depicts the schematic of a second-order bandpass filter compiled on the RASP2.8a, which is an OTA-based implementation of the circuit described in [103]. We use OTAs with FG differential inputs in this structure to improve the input linear range of the

Figure 7: Band Pass Filter: (a) Schematic of the second order bandpass filter used for frequency decomposition. (b) Measured results from a bank of 4 bandpass filters with exponentially spaced center frequencies. The mismatch in the passband gain is due to the parasitic load capacitance  $C_L$ .

system. The transfer function of the filter is given by

$$\frac{V_o(s)}{V_i(s)} = \frac{\frac{C_1}{C_{FB}} s \frac{\tau}{Q} (s\tau_z - 1)}{s^2 \tau^2 + s \frac{\tau}{Q} + 1}$$

(4)

where  $\tau = \sqrt{\frac{C_1 C_{FB}}{Gm_1 Gm_2}}$  is the filter time constant,  $Q = \sqrt{\frac{C_1}{C_{FB}} \frac{Gm_2}{Gm_1}}$  is the quality factor, and  $\tau_z = \frac{C_{FB}}{Gm_1}$ .  $Gm_1$  and  $Gm_2$  are the subthreshold transconductances of the forward and reverse amplifiers respectively. Intuitively, the filter is a second order section where the bias current of the forward amplifier sets the high-frequency cutoff and the bias current of the feedback amplifier sets the lower cutoff frequency. The midband gain is set by the ratio of the two capacitors. The additional filter zero can be placed at frequencies outside the speech band, thereby relying on low-pass filtering by the signal multiplier and the human ear itself to minimize its effects. The same filter structure is used but the bias currents are varied to get different center frequencies. Since the center frequency is given by  $f_c = \frac{1}{2*\pi} \sqrt{\frac{Gm_1 Gm_2}{C_1 C_{FB}}}$  and  $Gm \propto I_b$ , the higher frequency channels dissipate more power than the lower frequency channels. Fig. 7b shows the measured frequency response of a bank of four filters compiled on our chip. The variability in gain is seen due to parasitic capacitance  $C_L$  at the output

node causing additional loading. The mid-band gain including the effect of parasitic loading at the output is given by

$$A_v = -\frac{C_1}{C_{FB}} \frac{1}{1 + \frac{Gm_2}{Gm_1} \frac{C_L}{C_{FB}}} \tag{5}$$

The effect of the parasitic capacitance can be lowered by increasing  $C_{FB}$ , but to maintain the same filter Q and center frequency,  $C_1$ ,  $Gm_1$  and  $Gm_2$  will also have to be proportionally increased. Making a sensible routing choice for the output node helps in reducing the variability in gain. Since this node is sensitive to parasitic capacitance, it is preferable to use local or nearest-neighbor routing lines for making connections. Also, a voltage buffer is used at the output of the filter to prevent loading due to the following block.

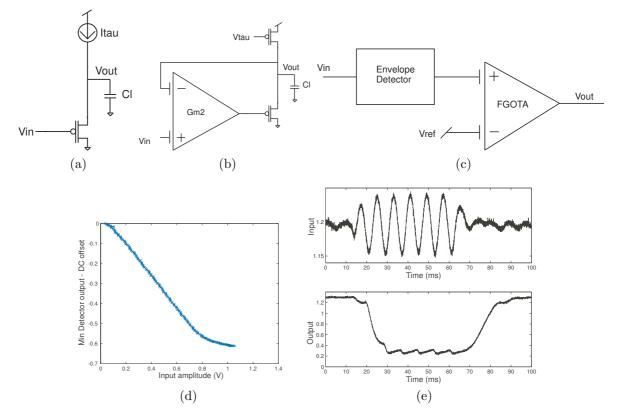

#### 2.3.2 Envelope Detector

To extract the envelope we take advantage of the non-linear behavior exhibited by a simple source follower. A pFET based source follower shown in Fig. 8a actually acts as a minimum detector.  $V_{out}$  quickly follows  $V_{in}$  with a gain of  $\kappa$  when the input decreases, but charges up at a rate  $\frac{I_{\tau}}{C_L}$ , where  $C_L$  is the capacitance at the output node. An nFET based source follower functions as a maximum-detector and can be used to extract the positive envelope of the signal. Using an OTA based peak detector, shown in Fig. 8b instead of a regular capacitively loaded source follower makes the circuit more sensitive to small changes in input. The gain now becomes  $\frac{\kappa A}{(1+\kappa A)}$  where A is the open loop gain of the amplifier. The attack time constant of the minimum detector is also decreased by a factor of  $(1 + \kappa A)$ , allowing a faster response. Kirchoff's current law at the output node can be written as,

$$C_L \frac{dV_{out}}{dt} = I_o e^{(\kappa V_{in} - V_{out})/U_T} - I_\tau \tag{6}$$

We assume sub- $V_T$  saturation operation for the input device and the transistor implementing the current source. Removing DC bias from (6) by using  $I_o e^{(\kappa V_{in} - V_{out})/U_T} =$

Figure 8: **Envelope Detector:** (a) and (b) Schematics of minimum detector circuits implemented on our chip. (c) Minimum detector followed by a FGOTA, providing a gain of about 5. (d) Measured transfer curve of the minimum detector showing output voltage versus input amplitude. (e) Transient output of the amplified envelope detector.

$I_{\tau}$ , we get

$$C_L \frac{dv_{out}}{dt} = I_\tau [e^{(\kappa v_{in} - v_{out})/U_T} - 1]$$

(7)

Using normalized variables  $x = \frac{\kappa v_{in}}{U_T}$ ,  $y = \frac{v_{out}}{U_T}$ , and  $\tau = \frac{C_L U_T}{I_\tau}$ , the dynamics of the output voltage for the pFET based source follower can be written in normalized form as

$$\tau \frac{dy}{dt} = e^{x-y} - 1 \tag{8}$$

where  $I_{\tau}$  is the quiescent bias current flowing through the circuit, set by  $V_{\tau}$ . x and y refer to the normalized input and output voltages. For an OTA based minimum-detector, the dynamics remain the same, but  $\tau = \frac{C_L U_T}{I_b(1+\kappa A)}$ , resulting in a faster response time. The transfer function of the minimum detector is plotted in Fig. 8d.

The "attack" and "release" parameters of the envelope detector can be modified by changing the bias current. For the  $i^{th}$  channel, we choose the bias current for the peak detector such that the rate of decay of its output  $I_b/C_L$  does not cause a significant change in output voltage in a time period corresponding to the lowest frequency signal in that band. Choosing a very small bias current will cause the envelope detector to miss portions of the envelope, especially in the higher frequency signals within the  $i^{th}$  band. A higher than optimum bias current choice will result in capturing the excitation signal in addition to the envelope itself, which is not desirable. Thus, the bias current for the lower frequency bands is lower than that of the higher frequency bands. While in this implementation this parameter is set using a DAC voltage  $V_{\tau}$ , it can be replaced with a FG switch element in the routing fabric, thereby storing the parameter  $V_{\tau}$  on-chip. The measured results from the minimumdetect block are plotted in Fig. 8e. For an increased gain from the envelope detector, we use an open loop FGOTA to further amplify the signal, shown in Fig. 8c.

## 2.3.3 Multiplier

A fully differential signal by signal multiply block present in the RASP 2.8a is used to control the gain for each individual channel in the system. The multiplier is the well known gilbert cell structure, shown in Fig. 9a [28]. Stacking of multiple differential pairs leads to voltage head-room issues in the traditional Gilbert cell. In our structure, we avoid this by folding signal currents. The cascode biases are generated using [73].  $V_1$  and  $V_2$  are the two differential inputs to the multiplier. The multiplier block produces differential output currents which can be converted to single ended voltage using a FG current mirror. Fig. 9c plots the measured output voltage against the differential input voltage  $V_1$  for several fixed values of  $V_2$ .

The frequency response of the multiplier block is shown in Fig. 9d. The bandwidth of the multiplier can be increased by programming a larger bias current. In the figure,

$I_b$  refers to the current in the bias generation circuits. All the inputs to the multiplier are FG transistors, which allow for precise offset cancellation. Since the outputs of the multiplier blocks are differential currents, signals from multiple channels can be added by tying the output nodes together. The summed current is then converted into voltage using a single FG current mirror. The FG transistors at the multiplier inputs and in the current mirror enable offset cancellation due to mismatch. Fig. 9a shows a piece of our system with 4 sub-banded channels and 4 gain stages provided by the gilbert multiplier. Fig. 9b plots the sum of the 4 channels at the output. In this case, there is a gain of 0.5 for each channel in the multiplier. The signal attenuation in the highest-frequency channel is higher than other channels since the bandwidth of the compiled system was around 2 KHz.

# $\it 2.4$ Single Channel System Results

We now proceed to discuss single band systems that include blocks described in the previous section. The non-linear signal processing block in Fig. 5 can be implemented in a variety of ways to produce processed speech for different applications. For noise suppression of signals with  $SNR \geq 10 dB$ , we apply a soft threshold to the sub-banded signal envelope to determine the gain for that channel, shown in Fig. 10a. The soft-threshold block is implemented using a comparator with very low gain. This is realized using an FGOTA programmed to a bias current of 1nA. Fig. 10b shows the transient results for such a system for a single tone input.

A system that expands the dynamic range of the input signal can result in noise suppression [79]. One way to achieve this is by ensuring a power law relationship with an exponent > 1 between the input and output. The non-linear function can be implemented in current mode employing the trans-linear principle using MITE transistors [74]. The voltage output from the envelope detector is converted to current using an FGOTA block which has a linear range of about 600mV. Fig. 11a depicts a

circuit with a squaring non-linearity.  $I_{scale}$  is set by the reference voltage  $V_{scale}$ . The output of the squaring circuit is converted back to voltage using a trans-impedance amplifier. Fig. 11c plots the relation between input and output amplitudes and shows a 12 dB improvement in dynamic range. The transient response of the system for a single tone input is plotted in Fig. 11b.

While an expansive non-linearity can be used for noise-suppression, a compressive non-linearity can be used in hearing aid applications [15]. Hearing loss is characterized by loss of inner hair cells that impair the ability to discern low intensity sounds. To compensate for the hearing loss, hearing aids typically compress the dynamic range by implementing a power law relationship with an exponent < 1. The squaring circuit can be easily converted into a square root circuit, by changing the configuration of the capacitors on the MITE transistors. While we do not show results from a speech processing system for hearing aid applications, we believe that the FPAA would be a good tool for prototyping algorithms.

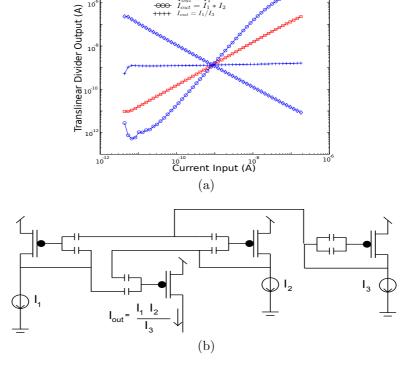

While the circuits described previously may be suitable for enhancement of speech signals with moderately high SNR, they do not perform well for inputs with SNR  $\leq 10$  dB. In these cases, it is preferable to estimate the noise portion of the speech input before further processing. To do a real-time estimation of the noise floor, we detect the minimum of the noisy sub-band envelope [70]. The integration time constant of the minimum detector is chosen to be slower than the envelope detector for that channel. Essentially, our noise floor estimate is the minimum of the envelope signal in a time window that is set by the bias current of the minimum detector. We choose this time window to be large enough that the speech signal in that band is too fast to cause a significant change in the noise estimate. We rely on a separation of timescales in the noise signal and speech signal within a particular band. The voltage output from the envelope estimator and the noise estimator are then converted into currents, as shown in Fig. 13b. The MITE transistors can be configured to do current mode

multiplication and division using the circuit shown in Fig. 14b [74]. The output of the divider circuit is plotted in Fig. 14a. The relevant signals in the SNR estimator circuit is shown in Fig. 13a. In this case, we choose to use a minimum detector as the first envelope estimator and a slow maximum detector on the envelope to arrive at the noise estimate. Since the current to voltage converter provides an inversion, the divider voltage output is low for high SNR estimates and high for low SNR. The divider output is now thresholded using a comparator to produce the control voltage for the multiplier.

# 2.5 Multi-Channel System Results and Discussion

A four channel noise suppression system was implemented on the Rasp 2.8a chip. The maximum number of channels that can be implemented on this chip is 8, limited by the number of gilbert multiplier blocks. For the multi-band system, the time constants for the envelope detector and noise estimator blocks were set independently using on-board DACs. The envelope detector for the lowest frequency channel is tuned to have the highest time constant.

Transient output waveforms from the envelope-threshold and SNR estimator systems are plotted in Fig. 12. We used speech samples from the NOIZEUS database, which provides acoustically recombined noisy speech samples with fixed SNR [43]. Noisy speech with 0 dB and 5 dB SNR was played and the output from our system was recorded. Both systems resulted in substantial reduction of background noise present between speech. In the envelope-threshold system, the intelligibility of the output suffered, since this system resulted in harsher clipping sounds, cutting out soft sounds in the speech itself.

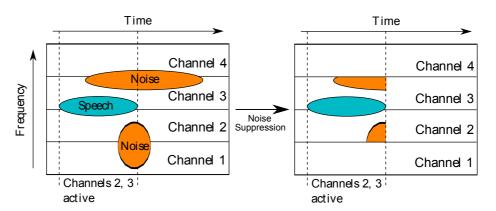

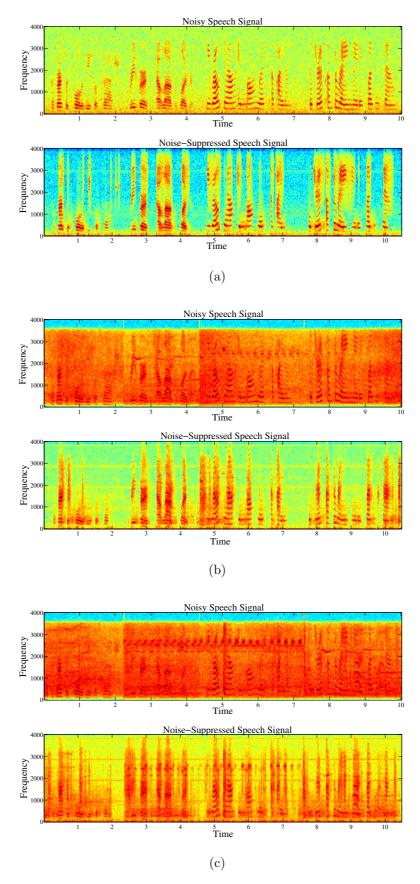

The SNR estimator system performed better with overall processed speech quality. Listening tests on the processed speech revealed that the system effectively reduced noise in between speech portions, but failed to do so during the speech. This behavior is expected and is illustrated by Fig. 15. Channels 2 and 3 are active when speech is detected and the SNR is high enough. However, this allows the noise present in these channels to also leak through to the output. Increasing the number of bands will increase the ability of the system to resolve speech and noise into multiple bands, thereby allowing it to suppress the noise better. We conducted blind subjective hearing tests on a group of graduate students, the results of which are tabulated in 1. The students were asked to compare the noisy and processed speech on the background noise level and intelligibility and mark the sample that had lower noise and higher intelligibility. The percentages of people who preferred the processed speech in these metrics is presented in Table 1. A majority of students felt that the processed speech was more noise-suppressed than the original speech. However, the quality of our output rated lower than the original speech, which we attribute to the hardware limitation of 4 bands in the system. The spectrogram of the processed speech for selected inputs is plotted in Fig. 16, and shows that our system suppresses noise considerably for moderately low input SNR.

Table 1: Subjective evaluation of noise suppression algorithm on speech samples with added pink noise

| SNR  | Subjective (%): Noise | Subjective (%): Intelligibility |

|------|-----------------------|---------------------------------|

|      | level                 |                                 |

| 0.7  | 100                   | 35                              |

| 2.6  | 100                   | 40                              |

| 4.5  | 100                   | 40                              |

| 5.5  | 90                    | 0                               |

| 10.6 | 90                    | 0                               |

| 13   | 80                    | 5                               |

#### 2.5.1 Power consumption

Increasing the number of bands allows separation of the speech and noise activity, resulting in better noise suppression, but will also increase the power consumption.

The power consumed in individual blocks is listed in Table 2. The total power consumption for the 4 channel system, without including the FG programming circuitry and the amplifiers to drive the audio ports is  $128.03\mu W$ . A significant portion of this power is consumed in the buffers, that are necessary for driving sensitive analog signals over routing lines with large parasitic capacitance. The projected power consumption for a 32 channel system is 1.02mW. The power consumption of all blocks except the bandpass filter can be linearly scaled. The filter power consumption is dependent on its center frequency, but since it is a small fraction of the total power, we assume it to be constant.

Table 2: Power consumption of individual blocks for a 4-channel system.

| Functional Block         | Power consumption |

|--------------------------|-------------------|

| Bandpass filter          | $0.4\mu W$        |

| Noise estimator          | $3.84\mu W$       |

| Speech estimator         | $4.03\mu W$       |

| Multiplier               | $5.52\mu W$       |

| Divider and gain control | $27.84 \mu W$     |

| Buffers                  | $86.4\mu W$       |

| Total                    | $128.03 \mu W$    |

#### 2.6 Conclusions

Our work describes how the reconfigurable chip (FPAA) described in [6], can be used for implementing signal processing algorithms, specifically for audio applications. The framework developed in this research also supports other applications such as voice-activity detection, hearing compensation, and classifier front-ends. The FPAA provides the user the flexibility in implementing circuits for analog signal processing while avoiding the costs of custom analog IC fabrication. Significant effort is spent in custom IC design to overcome mismatch effects. In our implementation, circuit parameters are set using FG biases that can be precisely programmed, enabling compensation of offsets due to component mismatch. This feature is exploited in

tuning the multiplier, bandpass filter and SNR estimator blocks. In the current implementation, the programmable biases show a temperature dependence. However, techniques for temperature compensation can be applied, where the gate coupling voltage to all FG transistors is supplied from a bootstrap reference. This ensures that the bias current (in weak inversion) is independent of temperature. One approach to noise suppression discussed in this work was previously published in [22]. However, we provide measured data for the first time from an integrated system compiled on a single reconfigurable chip. We also discuss three different approaches to noise suppression where we use implementations for the system components based on the blocks present in the FPAA, while describing trade-offs in performance. We acknowledge that there are better noise suppression algorithms in the literature, and the goal of this research is not to develop the best noise suppression system. We hope this chip makes analog signal processing more accessible to a wide audience.

Figure 9: **Signal Multiplier:** (a) Feedforward system with four channels and four multipliers. The multipliers have current outputs that allow channel summing by tying together the outputs of individual channels. The multiplier has programmable bias current, and FG fully-differential inputs that allow offset cancellation. (b) Frequency response of the feedforward system, with summed responses from all four channels. The lines and dots denote the individual channels and the summed response, respectively. The gain of the fourth channel is lower than that of the other channels since the bandwidth of the system has been programmed to be lower than the center frequency of the fourth channel. (c) Multiplier DC response:  $V_{out}$  versus  $V_1$  for different  $V_2$ . The current output of the multiplier is converted into voltage using a current mirror fashioned out of transistors in the CABs. (d) The frequency response of the multiplier. The corner frequency can be tuned by programming a higher bias current.

Figure 10: Single Channel results for envelope thresholding system: (a) Channel gain is determined by thresholding the envelope estimate. (b) Transient results for single tone inputs (Dashed trace is the input and Dotted trace is the output).

Figure 11: **Squaring Non-linearity:** (a) Schematic of squaring block implemented with MITE elements in the FPAA. (b) Transfer function of single channel system implementing the squaring non-linearity, resulting in an expansion of the dynamic range. (c) Transient response of system for a single tone input(gray trace). Large input amplitudes are amplified while smaller inputs are attenuated.

Figure 12: **Multi-channel System Results:** Comparison of noisy and processed speech for 5dB input SNR in the (a) Envelope thresholding system, (b) SNR estimation system.

Figure 13: **SNR Estimation System:** (a) The input and control voltages generated in the SNR estimation system. (b) System block diagram: The SNR estimate is computed by using the speech estimate and the noise estimate. The speech estimate is approximately equal to the envelope while the noise estimate is equal to the slow average of the minimum of the envelope. The current mode divider requires the conversion of the estimates from voltage to current domain. This is achieved using FGOTA blocks. The divider output is converted back into voltage using a transimpedance amplifier.

Figure 14: **SNR Estimation System:** (a) Characterization of the trans-linear multiplier/divider circuit with the relation  $I_{out} = I_1 * I_2/I_3$ . The slope when  $I_1$  and  $I_2$  are swept together is double that of when  $I_1$  is swept alone. When  $I_3$  is swept with  $I_1$  and  $I_2$  kept constant, the slope is -1. (b) Implementation of the current mode multiplier/divider circuit on the FPAA using MITE transistor elements.

Figure 15: **Effect of limited channels on performance:** The gain control system is active when speech activity is detected, transmitting the entire channel for that duration. Any noise present in the active channel in that duration is also transmitted to the output.

Figure 16: **Spectrogram of noisy and processed speech:** Comparison of noisy and processed speech for (a) Speech with 34 dded pink noise, at 13 dB SNR, (b) with street noise at 5dB SNR, and (c) with added pink noise, at 0 dB SNR

## CHAPTER III

#### THE VMM AND WTA AS AN ANALOG CLASSIFIER

In embedded systems that receive sensory inputs, process and classify them to make decisions, it is essential to take a low-power approach for enabling such structures in robots and other mobile platforms. Classifiers are typically used in the information refinement stage and it is often essential that besides being low power, they also produce very few events. Events are generated when a certain class has been detected, triggering further circuitry dependent on this decision. Energy efficiency is a key concern in information processing in low-power smart sensors and mobile devices [69]. A typical information processing chain usually involves a refinement stage that reduces the processing load on the following stages.

In highly integrated systems, an increased number of events often leads to increased power consumption, which is required to transmit events over interconnects between blocks that have significant capacitances. This strategy of minimizing the number of events is observed in biology, where the nervous system processes several sensory inputs and refines the information before transmitting them along large distances. The high power efficiency of the nervous system observed in biological organisms, is achieved by maintaining a low rate of spiking in the neurons, which is on average 100 Hz or less [71].

There are advantages to using Analog Signal Processing (ASP), as opposed to digital, for classification tasks that do not require high precision [94]. In the past, significant effort in hardware classifiers has been through the rise of the Artificial Neural Network (ANN) community since the 1980s, which solidified a framework of neural models that resulted in a variety of techniques to solve problems in many

Figure 17: Application in Analog Speech Recognizer Chain: The speech input undergoes frequency decomposition or enhancement resulting in sub-band signals. These signals undergo first-level information refinement in the feature detection stage, resulting in a sparse "symbols" or "event" representation. The following stage detects sequences of symbols/events to identify words or syllables. The feature detect stage maybe implemented as an Artificial Neural network, Gaussian Mixture model (GMM) or a VMM+WTA classifier. A typical 2-layer NN has synaptic inputs represented by the VMM and the sigmoid modeling the soma of a point-neuron. Alternatively, we can have synaptic computation followed by a competitive network modeled by the WTA. We investigate computational advantages to using the VMM+WTA over the ANN/GMM approach.

applications. Many of these techniques are considered standard and taught in most universities. The NN approach has its early roots in the perceptron [91] and adaptive filter models [110] that then extend to multi-level network models, Hopfield models as well as other related computational approaches.

In the simplest approach, we have inputs being multiplied by a weight vector, added together at the soma compartment, where a linear or nonlinear function is applied before we receive the output. ANN approaches include having continuous valued (e.g. tanh) functions that approximate the spike frequency versus current

input (f-I) characteristic of neurons with an analog voltage, or spiking (integrateand-fire neurons, rate-encoded neurons), feedforward or feedback stages.

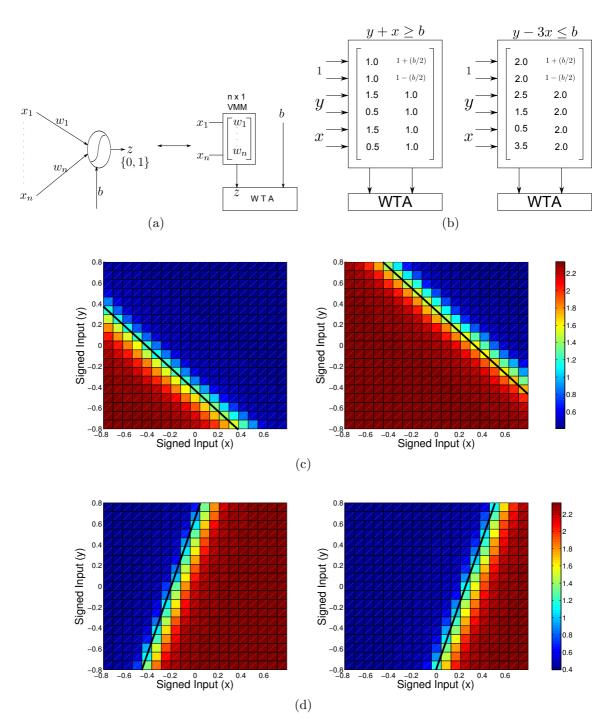

In this research, we consider an analog classifier consisting of a Vector-Matrix Multiply (VMM) terminated with a Winner-Take-All (WTA), shown in Fig. 17, that is versatile and has more computing power than a 1-layer NN. The VMM block performs a multiply operation between a vector and a matrix of weights, resulting in a vector and forms a core component of many signal processing algorithms. The VMM+WTA, which we use as the base classifier, compares favorably against the 1-layer NN in terms of the number of components as well. We show a direct translation of a 1-layer NN to a VMM+WTA, where the WTA acts as a current comparator. In a different formulation, the WTA can perform an analog max function, selecting the largest (or smallest) of its inputs. With minor modifications, the WTA can be designed to allow multiple winners, local winners or exhibit hysteresis [46, 56, 75], leading to classifiers that allow multiple winners with spatial responses which can be useful in image processing, or exhibit hysteresis which makes the classifier immune to noisy inputs.

We see this structure being used in an analog speech recognizer as shown in Fig. 17. The speech input undergoes frequency-decomposition or signal-enhancement in the front-end, resulting in input features such as sub-band energies. These signal inputs are transformed into symbols or events with ANN, GMM or VMM+WTA in the first stage of information refinement. This can be followed by higher level refinement or by a sequencing block to detect syllables or words.

This chapter is organized as follows. We briefly discuss the computational efficiency and circuit complexity comparisons of VMM+WTA versus NN implementations in Sec. 3.1. In Sec. 3.2, we describe the hardware platform used for implementing our classifiers. Next, in Sec. 3.3, we discuss the WTA circuit, its dynamics, and modifications made to obtain a multiple-winner WTA. In Sec. 3.4, we describe

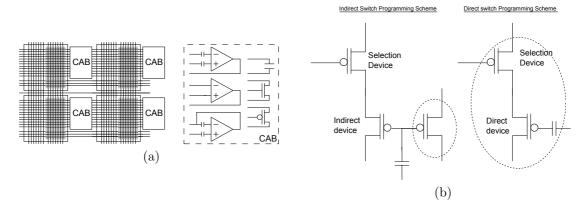

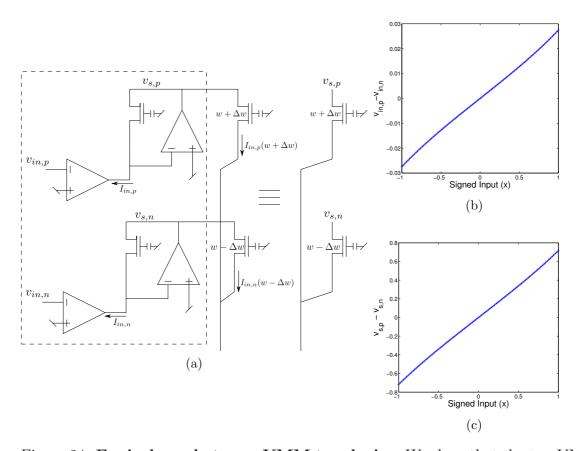

Figure 18: Field Programmable Analog Array (FPAA): The FPAA used in this work consists of 78 Computational Analog Blocks (CABs) embedded in reprogrammable routing enabled by floating-gate switches [98]. Each CAB consists of capacitors, transistors and Operational Transconductance Amplifiers (OTAs) that have programmable bias currents. Some OTAs have floating-gate inputs that allow cancellation of input offsets. The routing elements may be of the two types shown in (b). Switch programming schemes: The device(s) within the dashed circle appear in the signal path while other devices are used for programming and selection. The indirect programming scheme minimizes parasitic in the signal path by using a separate device that shares the floating gate with the actual device. The selection device is required for isolation. The indirect scheme can result in inaccuracies due to mismatch between programmed device and actual device, but can be characterized. The direct scheme, where the programmed device and actual device are the same, requires no additional characterization. However, there is an extra selection device in the signal path which reduces switch conductance at low voltages.

our VMM implementation, which is more compact and has lower noise and power than the previously described VMMs. In Sec. 3.5, we present measured results from classifier circuits that integrate the VMM and WTA to yield linear, multi-class and nonlinear classifier systems. Finally, we discuss mismatch, computing efficiency, and temperature effects in Sec. 3.6.

# 3.1 Implementation and Efficiency Overview

A 1-layer neural network requires the computation of a Vector-Matrix Multiply (VMM) + neuron. The addition of various weighted inputs is achieved through Kirchoff's Current Law (KCL) at the soma node, adding all currents. We define synaptic computation as the multiplication of inputs with synaptic weights, and neuron computation

as a non-linear threshold function. Assuming we have n synapses per neuron and m neurons, we expect a complexity of m \* n for synaptic computation. The computation at the neuron is governed by the choice of complexity in the model. A simple neuron model (tanh(.)) would require 4 MAC (Multiply ACcumulate) per neuron computation, as seen from a Taylor series expansion with 4 terms.

$$tanh(x) \approx x - \frac{x^3}{x} + \frac{x^5}{5} - \frac{x^7}{7}$$

$$\approx x(1 - \frac{x^2}{3}(1 - \frac{3}{5}x^2(1 - \frac{5}{7}x^2))) \tag{9}$$

Usually, for moderate size of n, the synaptic computation dominates the neuron computation.

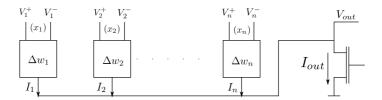

The VMM+WTA classifier topology has the advantage of being highly dense and low power. Each multiply is performed by one single transistor that stores the weight as well, and each WTA unit has only 2 transistors, providing very high circuit density. Custom analog VMMs have been shown to be 1000X more power efficient than commercial digital implementations [97]. The non-volatile weights for the multiplier can be programmed allowing flexibility. The transistors performing multiplication are biased in deep sub-threshold regime of operation, resulting in high computing efficiency. We combine these advantages of VMMs with the reconfigurability offered by FPAA platforms to develop simple classifier structures. VMMs on FPAA with high power efficiency have already been demonstrated in core signal processing applications viz. Image transforms and OFDM receivers [17, 106]. In this chapter, we discuss the computing power of the VMM+WTA classifier, and show that we can implement any 2-layer perceptron with modifications to the WTA.

# 3.2 Hardware: FPAA Implementation

The hardware platform used for implementing the classifier is among the family of Field Programmable Analog Array (FPAA) chips, specifically geared towards building large VMMs. A detailed description of this chip and its features can be found in

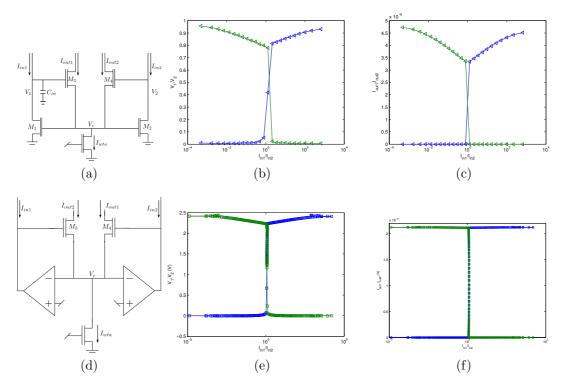

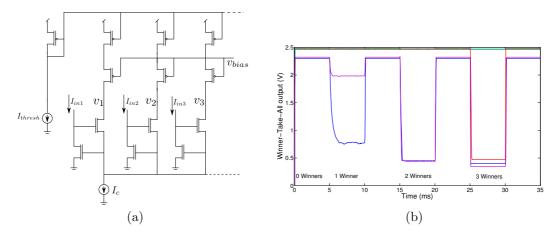

Figure 19: Schematic of winner-take-all structures and its input-output characteristics: (a) Circuit diagram of current-mode Winner-take-all structure from [56]. (b) Voltage outputs on the winner-take-all input nodes for a differential input current. (c) Current output of the winner-take-all for a differential input current. (d) Circuit diagram of the modified winner-take-all using OTAs. (e) Voltage outputs on the winner-take-all input nodes. (f) Current outputs from the winner-take-all.

[98]. However, for the sake of completeness, we provide a short discussion on the architecture of this chip.

FPAAs have the general structure of Computational Analog Blocks (CAB) with routing infrastructure to make re-programmable connections between the components. The CAB consists of circuit blocks commonly used in analog design, as shown in Fig. 18. The re-programmability is enabled using floating-gate transistors that can be programmed ON or OFF by operations known as injection and tunneling respectively, similar to programming EEPROMs. The programming infrastructure that includes selecting specific switches and injecting them is integrated on-chip, as discussed in [6].

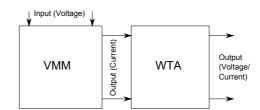

The chip that is used in this work, follows a similar architecture to |6| with some key differences, which are leveraged for building classifier structures. To build large VMMs, we require a large number of floating-gate switches that can be programmed accurately. The switch used for programmable connectivity uses the indirect programming structure, shown in Fig. 18b, that was developed to minimize parasitic resistance on the switch by using a separate device that shared the gate. This other device required extra devices for ensuring isolation during injection. In building VMMs, we require precise control over the weights programmed on the transistors, but this structure also suffers from mismatch issues that involve lengthy characterization process. In the FPAA used in this work, a portion of the routing switches are directly programmed switches, where the actual device used in the circuit is programmed. This removes any errors due to mismatch, but these switches are poorer than the indirectly programmed switch, since they contain an extra device in the signal path that is needed during program time for isolation purposes. The two programming schemes are shown in Fig. 18b. A detailed discussion on direct and indirectly programmed switches can be found in [30]. The components in the FPAA that are available for building classifiers are shown in Fig. 18. A high-level system overview of the VMM+WTA circuit is shown in Fig. 20. The inputs to the classifier are voltages, while the outputs from the VMM are uni-directional currents. The WTA may produce voltage or current outputs.

Figure 20: **High level System Flow:** The VMM takes voltage inputs and has uni-directional current output. The WTA may generate voltage or current outputs.

## 3.3 Winner Take All

WTA networks of neurons was an early area where VLSI and neuroscience positively interacted with each other, providing a unique and efficient means of computation. The WTA module is used for modeling competition in neural networks, specifically in representing the mechanism of attention [51]. A WTA network consists of multiple (m) somas that all connect (through excitatory synaptic connections) onto a single neuron that provides inhibitory feedback to all the original somas. The net effect is that we have an adaptive threshold, which can be global or local, that is the largest of some function on the inputs. Whether these somas are continuous valued or spiking representations is dependent on the design and computing environment.

In spiking representations, the WTA models the inhibiting effect exerted by neurons over the firing rate of competing neurons in a network. The neuron that starts to fire earliest, inhibits its neighbors before they can fire through inhibitory synaptic connections. This mechanism is critical to reducing firing rates in biological networks, which in turn translates to a fewer number of events and therefore, lower overall power dissipation. The classic circuit implementation by Lazzaro et al [56] was based on

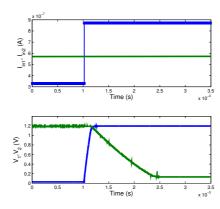

Figure 21: Measured dynamic response of WTA to input current step: The winning node settles faster than losers. The dynamics of the winning node are governed by a diode time constant (small). In this measurement, the WTA nodes see a large pin capacitance of  $\approx 10 \text{pF}$ .

Figure 22: **k-winner-take-all:**(a) The traditional WTA can be modified to a k-WTA with a current threshold at each output, realized using a cascoded pFET. The current flowing through the winning branch is constrained, allowing other inputs to the WTA to win. The voltage outputs from the WTA are inverted and a node wins when its output is below mid-rail. (b) Choice of current threshold determines the number of winners: winner-take-all with 0, 1, 2 and 3 winners.

continuous valued elements, that utilized transistor device physics to build an efficient circuit. Later, others built multiple spike-based representations to complete the connection between the analog VLSI approach and biological computation [45]. Several modifications to this circuit exist, that allow local winners, hysteresis behavior that stabilize the outputs, temporary winners that fatigue after a period of winning and allow other inputs to win and multiple winners [46,55,109]. In this chapter, we discuss the computational advantages offered by WTAs in classifier architectures.

The CAB components in the FPAA support several WTA implementations, but we first implement the classic WTA composed of discrete transistors shown in Fig. 19a. The two possible outputs from the WTA circuit are the voltages at the input nodes  $(V_1, V_2)$ , or output currents in each branch  $(I_{out1}, I_{out2})$ . The measured DC characteristics are plotted in Fig. 19b and Fig. 19c. The WTA biases itself depending on the input currents. The small-signal gain for the WTA shown in Fig. 19a is  $\frac{U_T}{\kappa I}$  where I is the DC input current,  $U_T$  is the thermal voltage and  $\kappa$  is the inverse of the sub-threshold slope.