# FABRICATION TECHNOLOGY AND DESIGN FOR CMUTS ON CMOS FOR IVUS CATHETERS

A Dissertation Presented to The Academic Faculty

by

Jaime S. Zahorian

In Partial Fulfillment

of the Requirements for the Degree

Doctor of Philosophy in the

School of Electrical and Computer Engineering

Georgia Institute of Technology MAY 2013

Copyright © Jaime Zahorian 2013

# FABRICATION TECHNOLOGY AND DESIGN FOR CMUTS ON CMOS FOR IVUS CATHETERS

## Approved by:

Dr. F. Levent Degertekin, Advisor School of Mechanical Engineering Georgia Institute of Technology

Dr. A. Bruno Frazier School of Electrical and Computer Engineering Georgia Institute of Technology

Dr. Oliver Brand School of Electrical and Computer Engineering Georgia Institute of Technology Dr. Thomas Michaels School of Electrical and Computer Engineering Georgia Institute of Technology

Dr. Peter Hesketh School of Mechanical Engineering Georgia Institute of Technology

Date Approved: December 5, 2012

#### **ACKNOWLEDGEMENTS**

First, I wish to thank my advisor Dr. Levent Degertekin for his consistent support, guidance, and positive attitude. I am especially grateful for his approachability and open door policy which significantly enhanced the research environment. I would also like to thank my committee members Dr. Albert Frazier, Dr. Oliver Brand, Dr. Thomas Michaels, and Dr. Peter Hesketh for taking the time and effort to serve on my defense committee. Additionally, I would like to thank Dr. Mustafa Karaman, Dr. Stephane Carlier, and Dr. Marvin Doyley for their guidance and support to many aspects of this work.

This work was made possible through the financial support of the National Institute of Health, Boston Scientific Corporation, and the National Science Foundation.

The work presented in this dissertation is the result of years of collaborative team work between many multi-disciplinary groups and would not have otherwise been possible. For their work with fabrication, simulation, testing, electronics design, I would like the thank specific members of Dr. Degertekin's group, Dr. Rasim Guldiken, Dr. Gokce Gurun, Dr. Coskun Tekes, Dr. Shakeel Qureshi, Sarp Satir, Michael Hochman, and Toby Xu. For their work with integration technology, flex tape and through silicon vias, I would like to thank Jutta Müntjes and James Yang respectively.

I owe special thanks to the clean room staff of the MiRC for their processing support and endless efforts to keep equipment in excellent operating conditions. In dealing with equipment issues I would like to thank Gary Spinner, Tran-Vinh Nguyen, Charlie Suh, Eric Woods, and William Kimes. For their support with processing issues, I would like to thank Dr. Mikkel Thomas and Janet Cobb-Sullivan.

# TABLE OF CONTENTS

| Page                                                          |

|---------------------------------------------------------------|

| ACKNOWLEDGEMENTSiv                                            |

| LIST OF TABLESx                                               |

| LIST OF FIGURESxi                                             |

| LIST OF ABBREVIATIONS xxiv                                    |

| SUMMARYxxvi                                                   |

| CHAPTER 1 INTRODUCTION AND BACKGROUND1                        |

| 1.1. Motivation                                               |

| 1.2. IVUS Catheters                                           |

| 1.3. Angioplasty and Stent Placement                          |

| 1.4. Chronic Total Occlusions6                                |

| 1.5. Heart Valve Replacement                                  |

| 1.6. Catheter Constraints9                                    |

| CHAPTER 2 CMUTs: BASIC MODEL, DESIGN CRITERIA AND FABRICATION |

| BACKGROUND WITH INTEGRATED ELECTRONICS11                      |

| 2.1. Introduction to CMUTs                                    |

| 2.1.1. CMUT Operation                                         |

| 2.1.2. Static Parallel Plate CMUT Analysis                    |

| 2.1.3. Small Signal AC Mason Equivalent Circuit Model15       |

| 2.1.4. CMUTs in Comparison to Piezoelectric Transducers       |

| 2.2 CMUT-Electronics Integration 20                           |

| 2.2.1.     | CMUT-in-CMOS                                                | 20 |

|------------|-------------------------------------------------------------|----|

| 2.2.2.     | Interleaved CMUT-CMOS                                       | 21 |

| 2.2.3.     | Flip Chip Bonding                                           | 21 |

| 2.2.4.     | CMUT-on-CMOS                                                | 22 |

| 2.3. Arra  | y Design Requirements                                       | 24 |

| 2.3.1.     | FL-IVUS Dual-Ring Array                                     | 24 |

| 2.3.2.     | SL-IVUS Annular Ring Arrays                                 | 27 |

| 2.4. Sum   | mary                                                        | 31 |

| CHAPTER 3  | OPTIMIZED CMUT FABRICATION AND MONOLITHIC CMOS              |    |

| INTEGRATIO | ON                                                          | 33 |

| 3.1. Moti  | vation for Fabrication for Optimized CMUT Tx-Rx Performance | 34 |

| 3.2. Robi  | ust CMUT Layout Design Considerations                       | 37 |

| 3.3. Elect | trode Optimization with Copper Sacrificial Layer            | 42 |

| 3.4. CMU   | JTs on CMOS Fabrication                                     | 47 |

| 3.4.1.     | CMUT-on-CMOS Integration                                    | 48 |

| 3.4.2.     | CMOS Wafer Substrate                                        | 49 |

| 3.4.3.     | Polishing                                                   | 51 |

| 3.4.4.     | CMUT-on-CMOS Via Interconnect                               | 53 |

| 3.4.5.     | CMUT-on-CMOS Design and Processing Considerations           | 56 |

| 3.5. Cath  | eter Interconnect Development                               | 57 |

| 3.5.1.     | Flex Tape Integration                                       | 59 |

| 3.5.2.     | Through Silicon Via Approach                                | 63 |

| 3.6 Sum    | mary                                                        | 66 |

| CHAPTER 4 IMPROVED CMUT MODELING68                                   |

|----------------------------------------------------------------------|

| 4.1. CMUT Design Space68                                             |

| 4.2. Fabricated CMUT Geometry and Array Option Examples              |

| 4.3. Finite Difference Boundary Element Modeling                     |

| 4.3.1. Acoustic Response                                             |

| 4.3.2. Limitations of The Thin Plate Approximation                   |

| 4.3.3. Static FEA for K Matrix Evaluation                            |

| 4.3.4. FEA K Matrix Validation                                       |

| 4.3.5. Computation Time Reduction                                    |

| 4.3.6. Large Signal Expansion                                        |

| 4.3.7. CMUT and Array Optimization Algorithm90                       |

| 4.4. Summary91                                                       |

| CHAPTER 5 FORWARD-LOOKING DUAL-RING ARRAY93                          |

| 5.1. Physical Depiction of an Ideal FL-DRA Catheter Implementation93 |

| 5.2. FL-DRA Specifications95                                         |

| 5.3. Initial DRA Fabrication with External CMOS                      |

| 5.4. DRA integration with CMOS                                       |

| 5.4.1. Electrical Characterization                                   |

| 5.4.2. Acoustic Characterization                                     |

| 5.5. CMUT-on-CMOS Imaging with Integrated Pulsers                    |

| 5.6. Fabrication Optimization of DRA Elements                        |

| 5.7. Summary                                                         |

| CHAPTER 6 ANNULAR CMUT ARRAYS FOR SL-IVUS119                         |

| 6.1. Phy  | vsical Description of a Side-Looking Annular Ring Array   | 120 |

|-----------|-----------------------------------------------------------|-----|

| 6.2. Anı  | nular Array Specifications                                | 121 |

| 6.3. Fab  | ricated Annular Arrays                                    | 125 |

| 6.3.1.    | Initial Annular Array                                     | 125 |

| 6.3.2.    | Second Generation Annular Array                           | 126 |

| 6.3.3.    | Third Generation Annular Array                            | 127 |

| 6.3.4.    | Initial Annular Array Testing in Water                    | 128 |

| 6.3.5.    | Initial Annular Array Imaging                             | 132 |

| 6.4. Fin  | ite Element Analysis for Crosstalk Evaluation             | 134 |

| 6.5. Box  | undary Element Method Simulation                          | 138 |

| 6.5.1.    | Annular Array Design 1                                    | 138 |

| 6.5.2.    | Annular Array Design 2                                    | 140 |

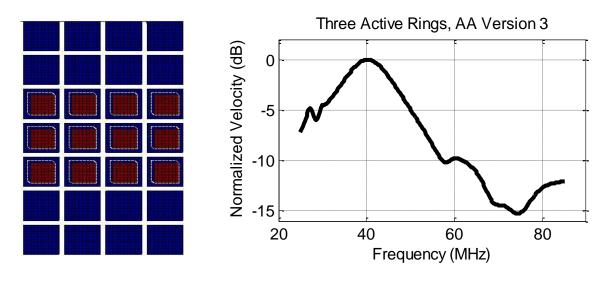

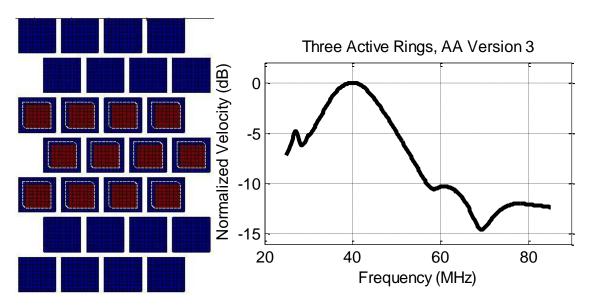

| 6.5.3.    | Annular Array Design 3                                    | 142 |

| 6.6. Tes  | ting of the Second and Third Generation of Annular Arrays | 144 |

| 6.7. Sun  | nmary                                                     | 147 |

| CHAPTER 7 | CONCLUSIONS AND FUTURE WORK                               | 149 |

| 7.1. Cor  | nclusions                                                 | 149 |

| 7.2. Cor  | ntributions                                               | 149 |

| 7.2.1.    | CMUT-CMOS Integration Processing                          | 149 |

| 7.2.2.    | Optimization of CMUT Processing                           | 151 |

| 7.2.3.    | Improved Modeling                                         | 152 |

| 7.2.4.    | Forward-Looking Dual-Ring Array                           | 153 |

| 725       | Side-Looking Annular-Ring Array                           | 154 |

| 7.3. Future | e Work                                      | 155 |

|-------------|---------------------------------------------|-----|

| APPENDIX A  | LOW TEMPERATURE CMUT FABRICATION            | 157 |

| APPENDIX B  | COPPER SACRIFICIAL CMUT FABRICATION         | 161 |

| APPENDIX C  | ANSYS SAMPLE CODE                           | 170 |

| APPENDIX D  | COMSOL SAMPLE CODE FOR K MATRIX CALCULATION | 181 |

| REFERENCES  | <b>.</b>                                    | 185 |

# LIST OF TABLES

|                                                                   | Page |

|-------------------------------------------------------------------|------|

| Table 1. CMUT-CMOS Integration Comparison                         | 24   |

| Table 2. Typical dimensions for a 10 MHz membrane.                | 35   |

| Table 3. Design Parameters for Optimization                       | 37   |

| Table 4. Etch rates for Cr, Al, Cu                                | 43   |

| Table 5. Material Properties of Cr, Al, Cu, Si                    | 44   |

| Table 6. Array Element Connection Capacitance Comparison          | 48   |

| Table 7. RIE Parameters for Via Interconnect                      | 54   |

| Table 8. Shipley 1827 Processing                                  | 57   |

| Table 9. CMUT design matrix with example geometric cross-sections | 70   |

| Table 10. Simulation material properties                          | 81   |

| Table 11. Mass loaded geometry dimensions                         | 84   |

| Table 12. FL-DRA parameters                                       | 95   |

| Table 13. Tissue properties                                       | 97   |

| Table 14. DRA Dimension for CMOS Integration                      | 102  |

| Table 15. Layers and Collapse Voltages for DRA Test Arrays        | 112  |

| Table 16. Receive Sensitivity at 15 MHz for DRA Test Arrays       | 112  |

| Table 17. First Generation Annular Array Areas                    | 126  |

| Table 18. Second Generation Annular Array Areas                   | 127  |

| Table 19. Third Generation Annular Array Areas                    | 128  |

# LIST OF FIGURES

| Page                                                                                         |

|----------------------------------------------------------------------------------------------|

| Figure 1. Sample angiograms from a fluoroscopic procedure showing the blood flow             |

| through the vessels (left) and a clogged coronary artery (right) [5, 6]                      |

| Figure 2. Examples of single-element and multi-element transducer configurations with        |

| imaging planes shown on the right [9]                                                        |

| Figure 3. IVUS cross-sectional images of a normal vessel (left) and with calcification       |

| (right) [15]                                                                                 |

| Figure 4. A pictorial diagram of the angioplasty procedure (left) and the stent placement    |

| procedure (right) [17]                                                                       |

| Figure 5. CTO imaging demonstrating the two imaging scenarios. The catheter                  |

| approaches the CTO through the blood (left) and the catheter is pushing through the          |

| occlusion (right) [18].                                                                      |

| Figure 6. Hard plaque (left) and soft plaque (right) [18]                                    |

| Figure 7. A TAVI procedure is shown placing a prosthetic aortic valve through the use of     |

| a catheter inserted through the groin area (left) and a prosthetic heart valve based on an   |

| expandable stent mesh (right) [19, 20]                                                       |

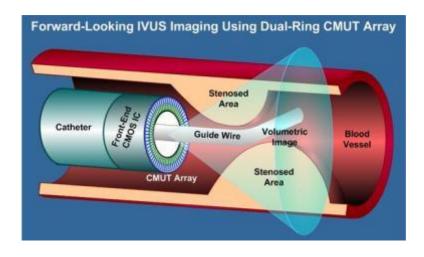

| Figure 8. A depiction of a forward-looking ultrasonic catheter with guide wire 10            |

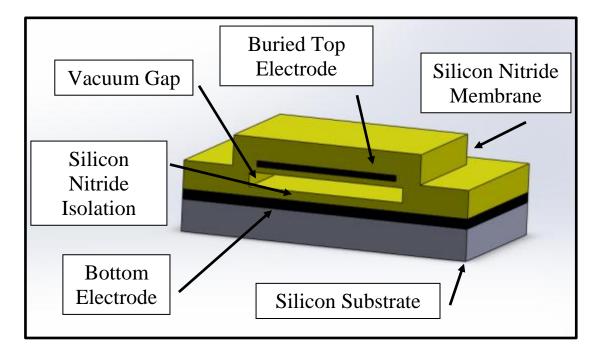

| Figure 9. Cross-sectional image of a CMUT, primarily made from silicon nitride 12            |

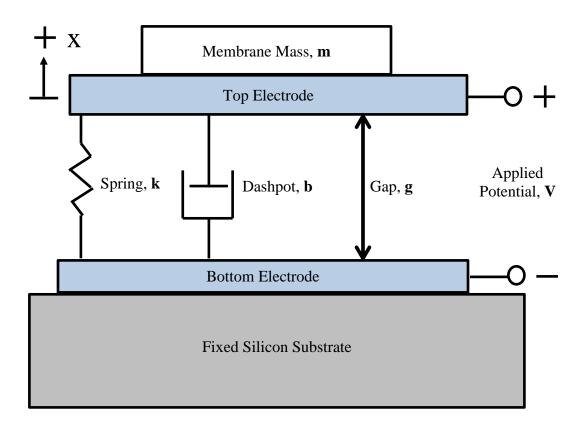

| Figure 10. An illustration of a parallel plate CMUT model of the first-order                 |

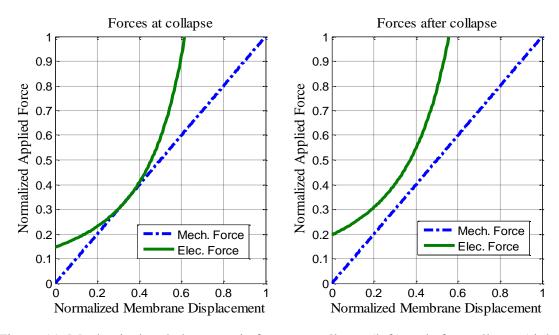

| Figure 11. Mechanical and electrostatic forces at collapse (left) and after collapse (right) |

| for a parallel plate actuator with $k=1\ kN/m$ and $g_0=0.1\ \mu m$ [24]                     |

| Figure 12. Mason equivalent circuit.                                                         |

| Figure 13. Mechanical mesh impedance analysis of a simple parallel plate CMUT with a         |

|----------------------------------------------------------------------------------------------|

| spring constant, K, and mass, m, in comparison to water                                      |

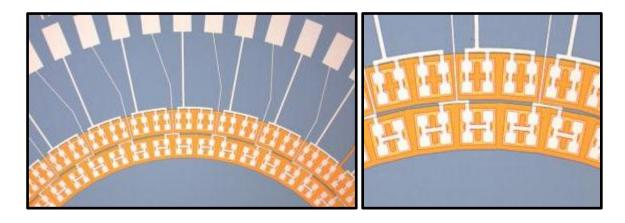

| Figure 14. Fabricated CMUT arrays with a single-ring of elements, 1.2 mm outer               |

| diameter (left) [37] and dual-ring of elements, 0.8 mm outer diameter (right)                |

| Figure 15. A single CMUT element, center, with surrounding CMOS electronics [40] 21          |

| Figure 16. Schematic of a 2D CMUT array bonded to electronics through flip chip              |

| bonding methods [49].                                                                        |

| Figure 17. A simplified depiction of a CMUT on a CMOS substrate connected to an              |

| amplifier                                                                                    |

| Figure 18. A single ring PZT based forward looking array [51]                                |

| Figure 19. A fabricated single-ring CMUT array (left) and a diagram of a catheter with a     |

| single-ring array for forward-looking imaging with guide wire (right)                        |

| Figure 20. A fabricated dual-ring CMUT design with separate Tx and Rx bias capabilites       |

| (left) and flow chart for Tx-Rx integration with electronics (right)                         |

| Figure 21. A depiction of a single element annular array with a geometric focus [65] 28      |

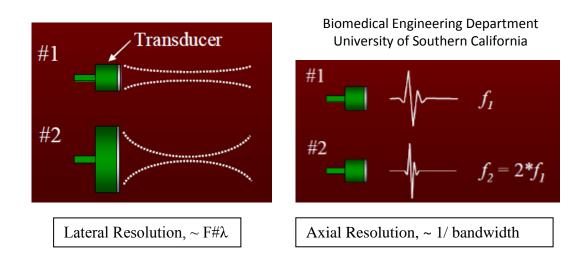

| Figure 22. An illustration of lateral resolution (left) and axial resolution (right) [66] 28 |

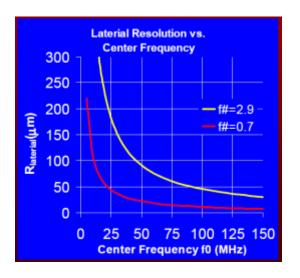

| Figure 23. Graphs of: lateral resolution versus center frequency (left) and axial resolution |

| versus bandwidth (right) [66]                                                                |

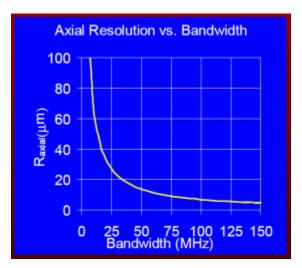

| Figure 24. A depiction of an annular array (left) and illustration showing relative pulse    |

| delays for focusing (right) [65]                                                             |

| Figure 25. An eight element PZT annular array with surface wire bonding [77]                 |

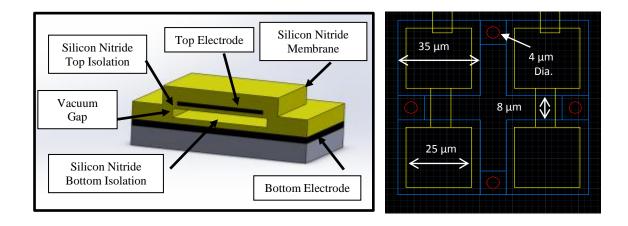

| Figure 26. CMUT cross-section showing the silicon nitride top and bottom isolation as        |

|----------------------------------------------------------------------------------------------|

| well as top and bottom electrodes (left). A sample 10 MHz dual-ring array element with       |

| four individual membranes electrically linked (right)                                        |

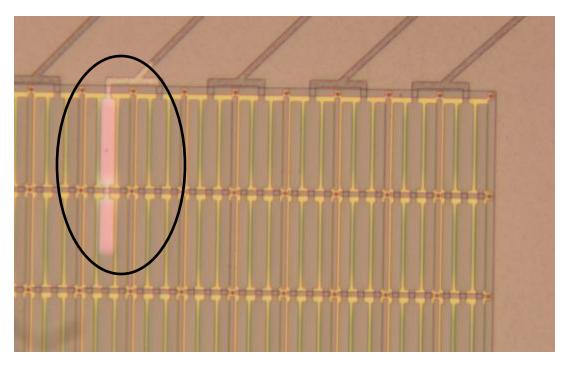

| Figure 27. The top center electrode has been etched by the sacrificial etchant through the   |

| silicon nitride during the release process                                                   |

| Figure 28. The start of the sacrificial release with acceptable alignment on the left and    |

| misalignment on the right                                                                    |

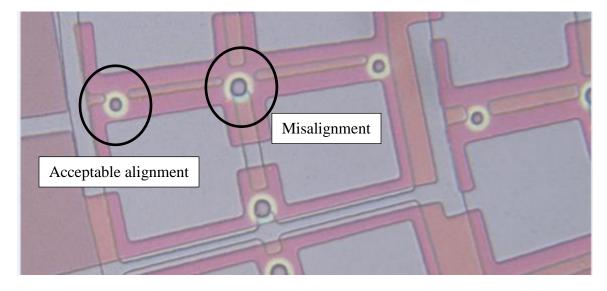

| Figure 29. Sacrificial layer and etch directions. Previous sacrificial layout and release    |

| etch holes (a) and modified layout (b) to reduce overall time required for release 41        |

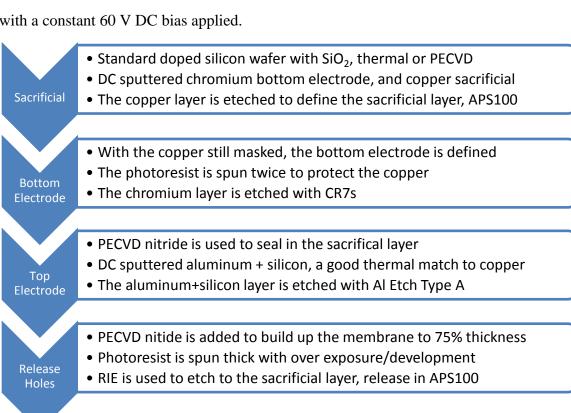

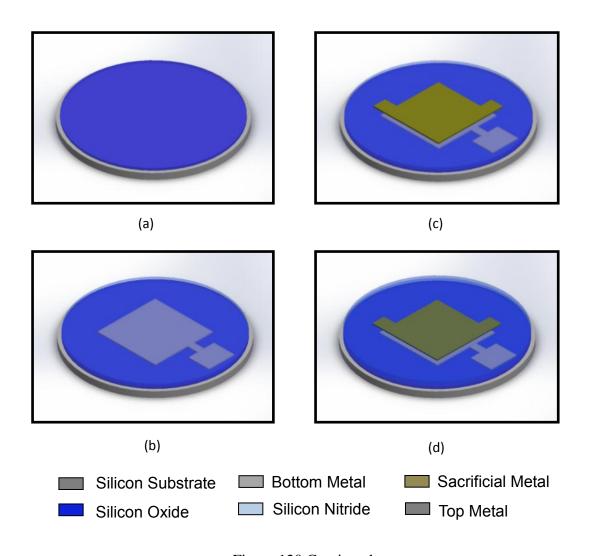

| Figure 30. Modified process flow using the copper sacrificial layer                          |

| Figure 31. The chromium bottom electrode and copper sacrificial layer are shown where        |

| the bottom electrode has been enlarged by $\sim 3~\mu m$ radially to protect the sacrificial |

| copper during the wet etch definition                                                        |

| Figure 32. Aluminum top electrode definition shows no delamination and the patterning        |

| is shown to not affect the sacrificial layer                                                 |

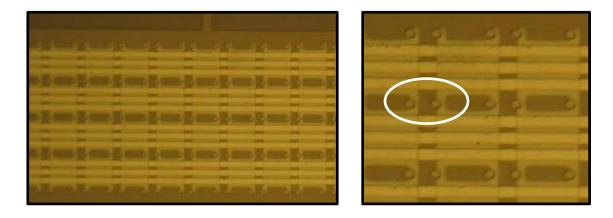

| Figure 33. A functional released CMUT linear array employing a dual top electrode is         |

| shown with sacrificial release hole etch locations misaligned in the horizontal direction    |

| by~ 2 μm without detrimental effect                                                          |

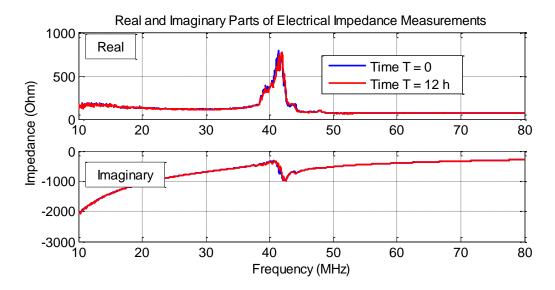

| Figure 34. Real and imaginary impedance measurements of a 40 MHz CMUT array in air           |

| with a 60 V DC bias over time show no deviation in magnitude or resonance indicating         |

| minimal charging effects                                                                     |

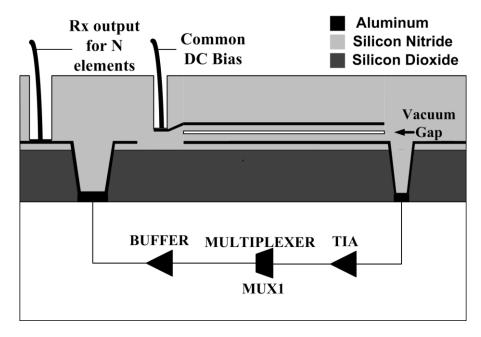

| Figure 35. Cross-section schematic of the CMUT on CMOS membrane and the critical             |

| metal interconnections made to CMOS electronics. Receive elements are connected and          |

| divided between multiplexers for receiver output signals and all receive elements are              |

|----------------------------------------------------------------------------------------------------|

| connected to a common DC bias. Dual ring arrays use four multiplexers, MUX1-4, to                  |

| route one output from a group of 8 or 16 receive channels for parallel output 49                   |

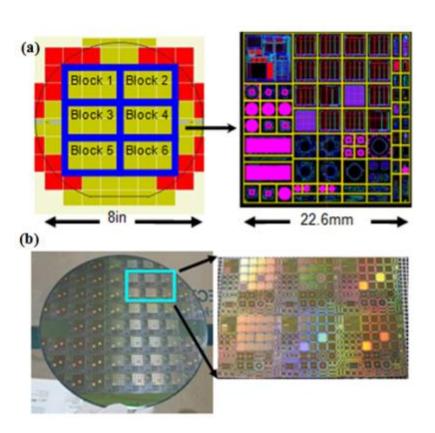

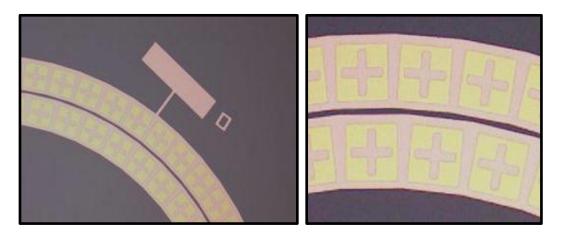

| Figure 36. The repeated squares and block dicing lines are shown on the left with a                |

| magnified view of an individual square with die on the right, (a). The custom 200 mm               |

| CMOS wafer is shown on the left with a diced block on the right, (b)                               |

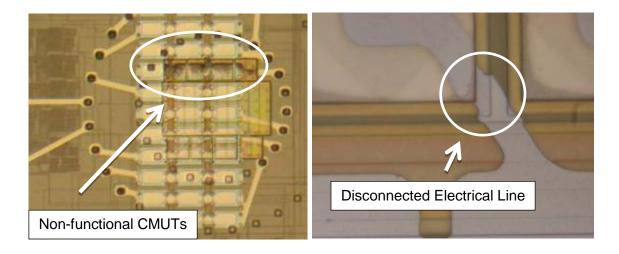

| Figure 37. Topography of the CMOS electronics. CMUTs fabricated with non-functional                |

| elements on the left and a failed electrical connection on the right                               |

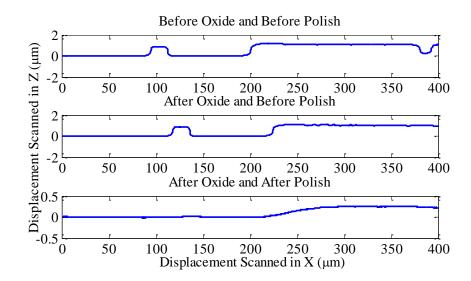

| Figure 38. Profilometer scans of the same region shown, (from top to bottom): (a) the              |

| initial topography, (b) after 3 $\mu m$ of PECVD silicon dioxide passivation, (c) after 3 h of     |

| polishing                                                                                          |

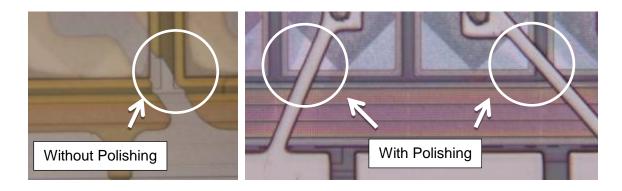

| Figure 39. Similar electronics without polishing (left) and with polishing (right). The            |

| discontinuity of the connection line has been mitigated through the addition of silicon            |

| oxide and subsequent polishing. 52                                                                 |

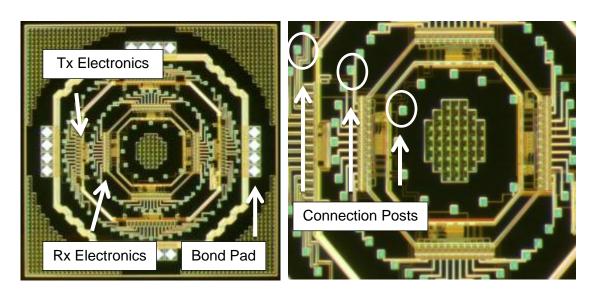

| Figure 40. CMOS electronics block for a DRA with Tx and Rx electronics. Bond pads on               |

| the outer ring for power, signal, and clock connections                                            |

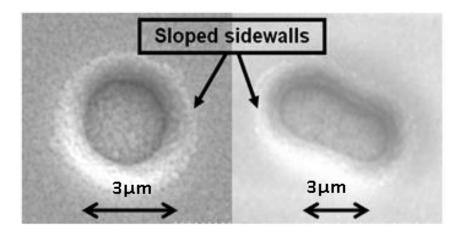

| Figure 41. Test connection vias through $\sim 3~\mu m$ of silicon oxide using a 5 $\mu m$ circular |

| mask feature. 55                                                                                   |

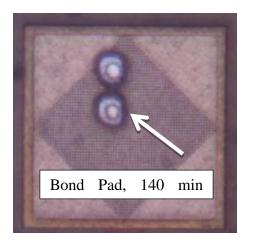

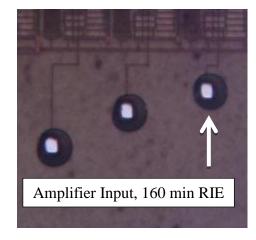

| Figure 42. Etched vias over a bond pad location with 140 min of RIE with visible sloped            |

| side wall (left) and a via with slight over etching at 160 min at an amplifier input location      |

| (right)                                                                                            |

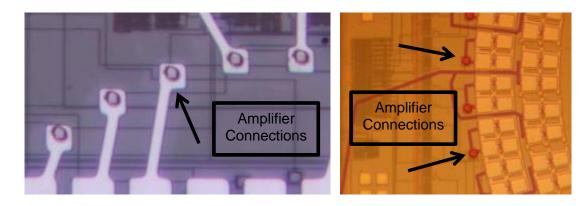

| Figure 43. Metal connection to amplifier connections on the CMOS electronics through               |

| the use of a connection via                                                                        |

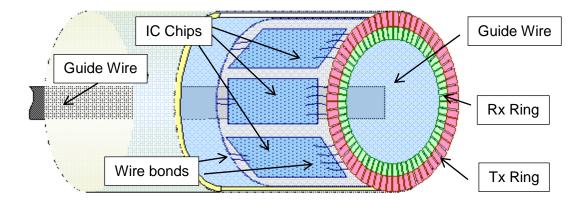

| Figure 44. Diagram of FL DRA arrays wire bonded to IC chips and additional signal           |

|---------------------------------------------------------------------------------------------|

| lines                                                                                       |

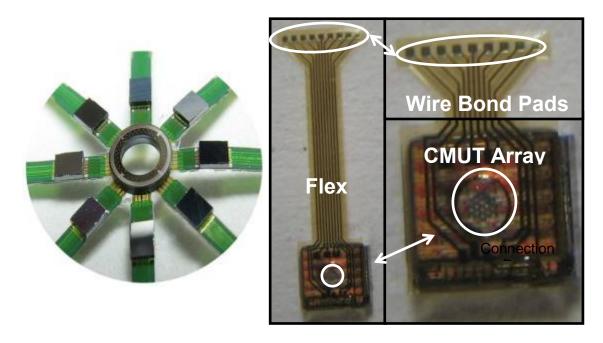

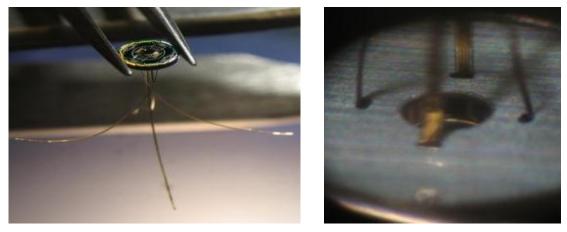

| Figure 45. Flexible interconnect technology showing a CMUT ring array integrated with       |

| electronics via TSV and flexible circuitry [50] (left) and a test CMUT array connected to   |

| flexible circuitry via top side bond pads (right)                                           |

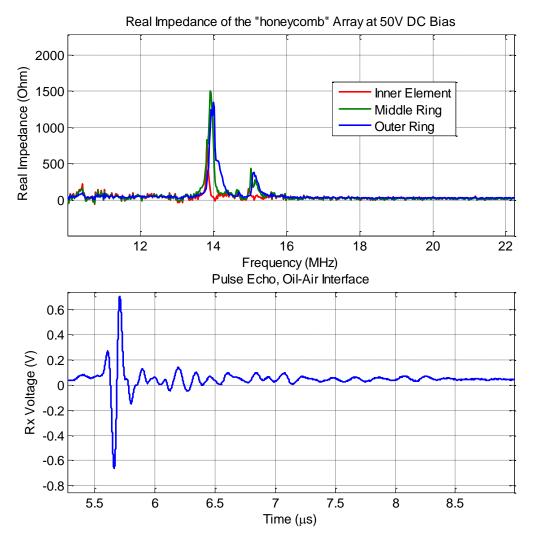

| Figure 46. The resonances in air for the three elements of the "honeycomb" type CMUT        |

| array with the flexible circuit attached are shown indicating functional devices (top). A   |

| pulse echo from an oil-air interface from the same array with the flexible circuit          |

| connected (bottom). 61                                                                      |

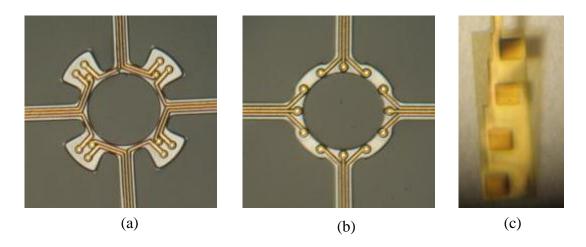

| Figure 47. Two flexible tape rings designed for front side connection to FL-DRA CMOS        |

| electronics, (a) and (b) with bond pads for wire bonding (c)                                |

| Figure 48. Doughnut shaped CMUT array with flex tape connections to the front of the        |

| array and passed through the silicon to the back side for connection to electrical lines 62 |

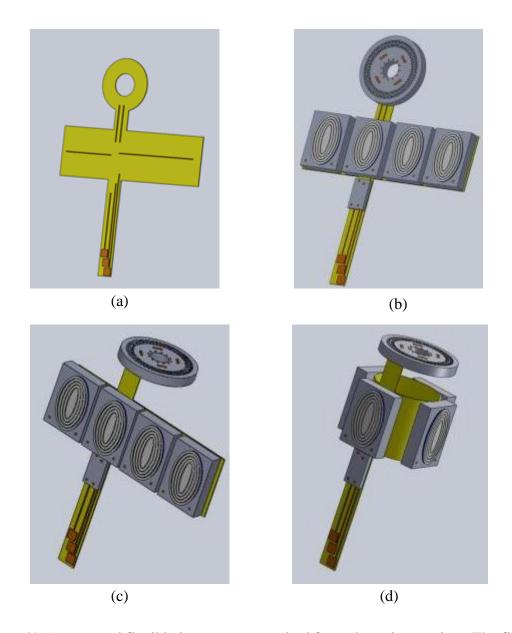

| Figure 49. A proposed flexible interconnect method for catheter integration. The flexible   |

| tape in (a) is designed for forward looking and side looking arrays. Five CMUT arrays       |

| and one CMOS switch circuit attached to the flex tape (b) with a fold (c) and wrap (d). 63  |

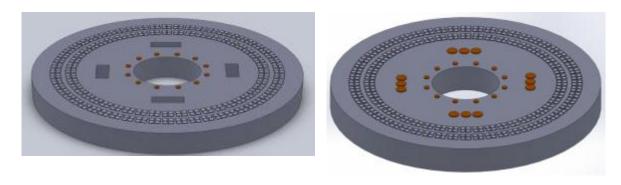

| Figure 50. Depictions of DRA's with openings for flex tape (left) and with copper TSV's     |

| at the same locations (right)                                                               |

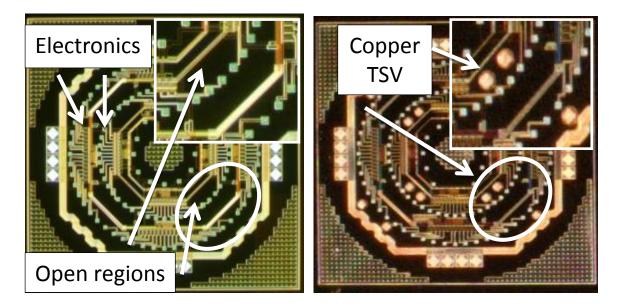

| Figure 51. Second generation DRA CMOS electronics with both Tx and Rx capibilities          |

| and open regions for through wafer etching. 65                                              |

| Figure 52. An AutoCAD drawing with via interconnection layer and top electrode metal        |

| layer used for connections between electronics and TSVs for back side connection (left)     |

| and fabricated array (right).                                                               |

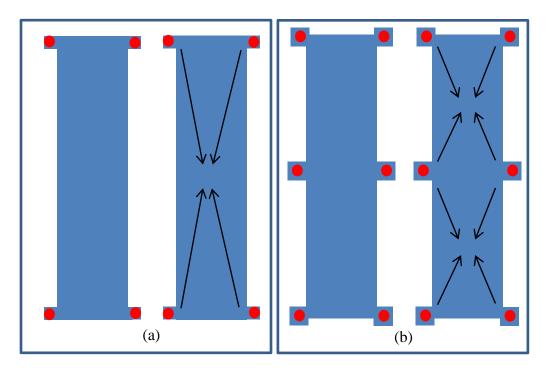

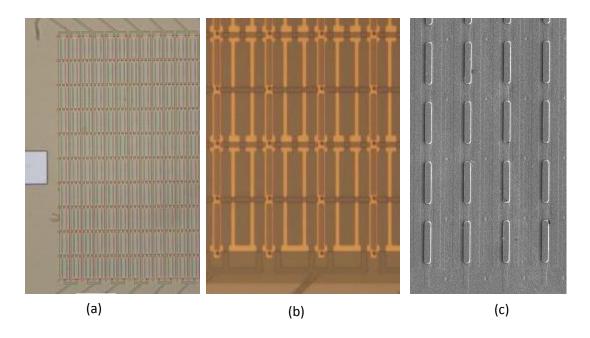

| Figure 53. Dual electrode linear array with two rows connected in parallel, (a),              |

|-----------------------------------------------------------------------------------------------|

| individual membranes with side electrodes 10 $\mu m$ and center electrode 15 $\mu m,$ (b) and |

| SEM view with additional mass loading (c).                                                    |

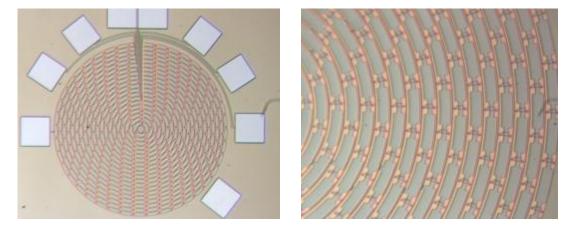

| Figure 54. Dual ring array with separate Tx and Rx rings. The transmitter inner ring is       |

| shown with experimental electrode configurations                                              |

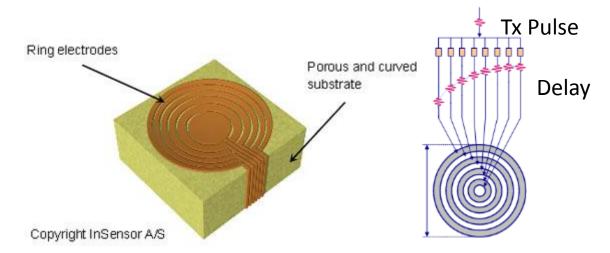

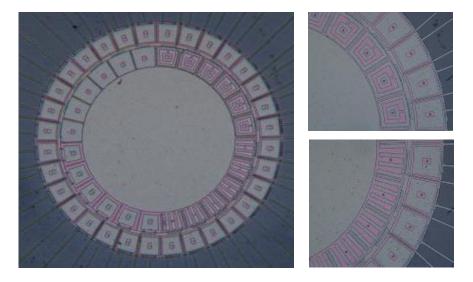

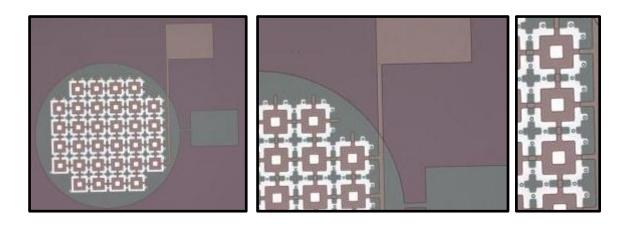

| Figure 55. Annular ring array with eight electrically linked rings (left). Individual curved  |

| membranes that make up the 21 rings of the eight element annular array (right)                |

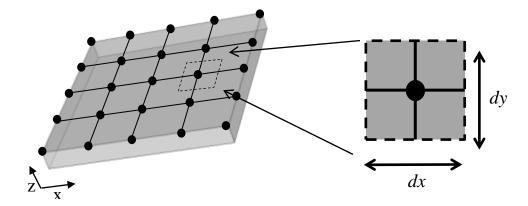

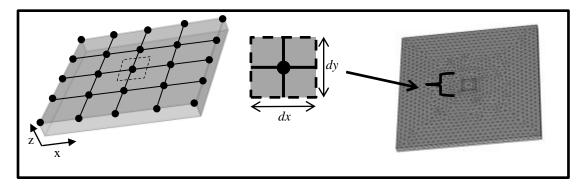

| Figure 56. A CMUT membrane divided into a 5 x 5 matrix of nodes, N=25, with                   |

| corresponding areas $dx \times dy$                                                            |

| Figure 57. CMUT membrane used for the finite difference calculation (left) and the            |

| CMUT membrane used for FEA stiffness calculations (right)                                     |

| Figure 58. CMUT nodal spacing and a meshed membrane in COMSOL used for K matrix               |

| calculations. 80                                                                              |

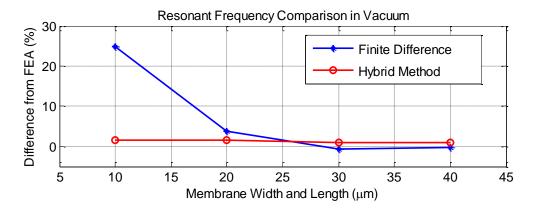

| Figure 59. A comparison of a square membrane in vacuum. The finite difference and             |

| hybrid methods are compared to FEA                                                            |

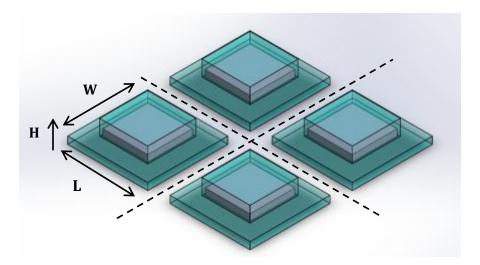

| Figure 60. Mass loaded CMUTs with aluminum electrodes. Dashed lines indicate                  |

| symmetry for the 2 x 2 array simulated using FEA                                              |

| Figure 61. FEA simulation of a single mass-loaded membrane compared to simulation             |

| using the hybrid method (top). A 2 x2 array of mass-loaded membranes (bottom) 84              |

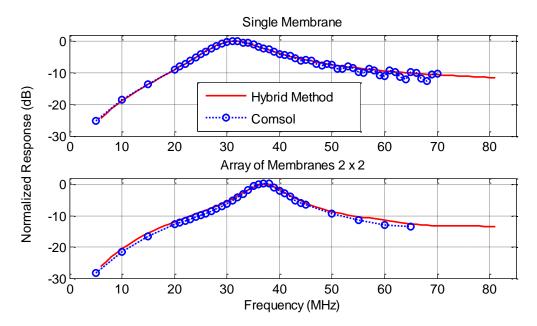

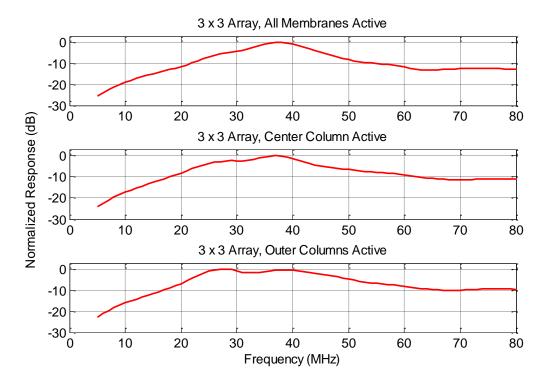

| Figure 62. Simulations of a 3 x 3 matrix of mass-loaded membranes with all membranes          |

| active, top, center column active, middle, and outer two columns active bottom. All three     |

| cases show distinct frequency responses.                                                      |

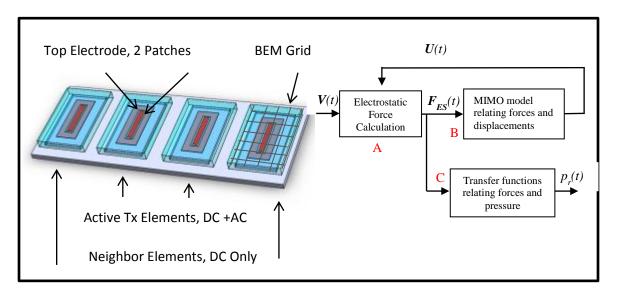

| Figure 63. An array of four CMUT membranes each with two electrostatic patches where     |

|------------------------------------------------------------------------------------------|

| the center two CMUTs are actuated with both a DC and AC signal for the Tx mode of        |

| operation. The outer two CMUTs are subject to only a DC bias as in the Rx mode. The      |

| right most CMUT is shown with an example BEM grid. A block diagram describing the        |

| transient model with arbitrary voltage input and pressure output                         |

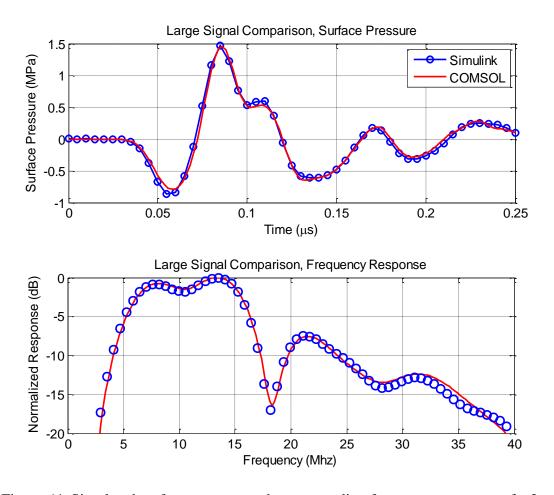

| Figure 64. Simulated surface pressure and corresponding frequency response, of a 2 x 2   |

| array of CMUT membranes for a high amplitude, short pulse resulting in full gap swing.   |

|                                                                                          |

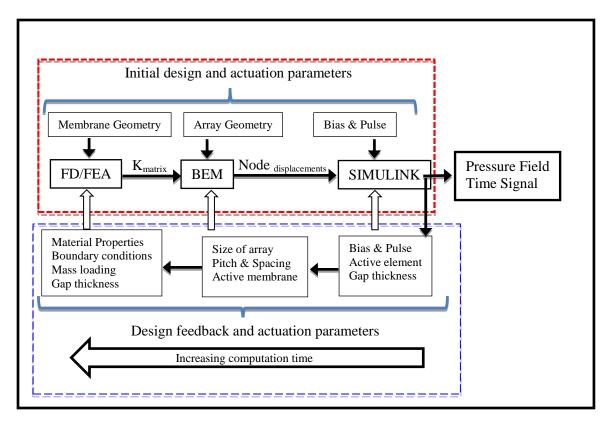

| Figure 65. A block diagram describing the modeling process and design feedback           |

| parameters that can be modified at each stage of the modeling                            |

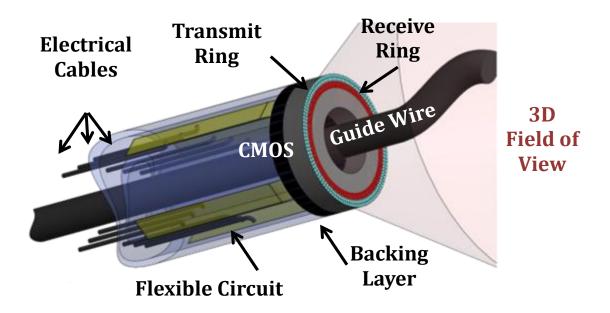

| Figure 66. A depiction of a dual-ring CMUT array with backside flexible circuit          |

| interconnect technology. The doughnut CMOS with monolithically integrated CMUTs          |

| allows for the passage of the central guide wire                                         |

| Figure 67. CTO imaging demonstrating the two imaging scenarios. The catheter             |

| approaches the CTO through the blood (left) and the catheter is pushing through the      |

| occlusion (right) [18].                                                                  |

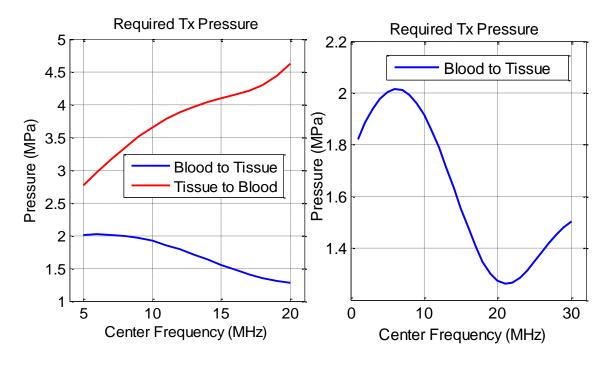

| Figure 68. Required transmit pressure for a fixed bandwidth of 10 MHz at a distance of 1 |

| cm as a function of the center frequency for 30 dB SNR                                   |

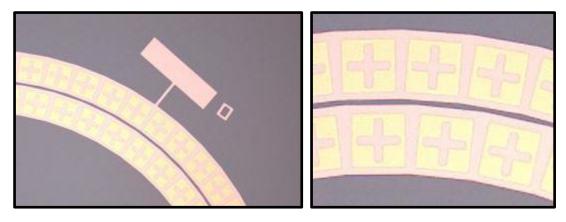

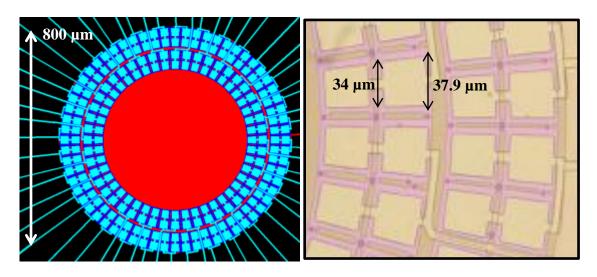

| Figure 69. An AutoCAD drawing of a dual-ring array (left) and close up view of           |

| fabricated CMUT membranes (right)                                                        |

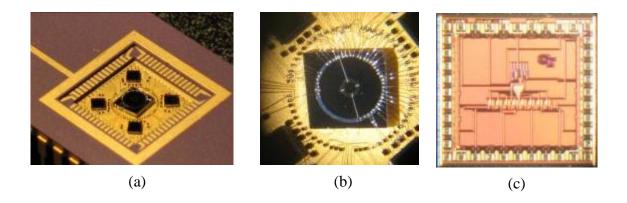

| Figure 70. A dual-ring array in a 64 pin DIP surrounded by 4 custom IC chips (a), Close  |

| up view of the array and fan out chin (h) Magnified view of the custom IC chin (c) 99    |

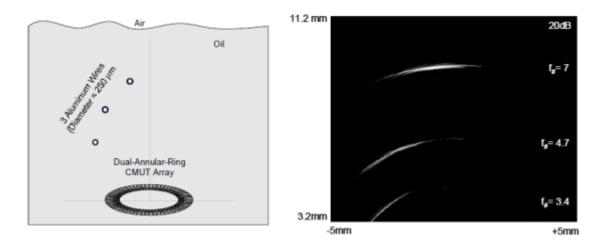

| Figure 71. A depiction of a 3 wire target above the CMUT array (left) and cross-sectional |

|-------------------------------------------------------------------------------------------|

| image with 20 dB dynamic range (right)                                                    |

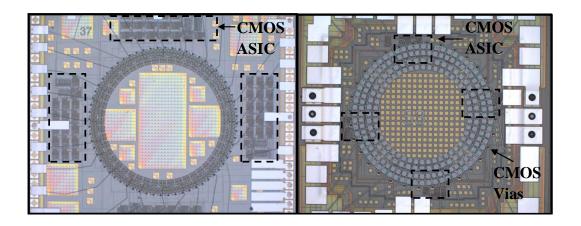

| Figure 72.A fully fabricated CMUT on CMOS dual ring array with a 1.6 mm diameter          |

| array (left) and a 840 µm diameter array fabricated directly on top of the CMOS ASIC      |

| for FL-IVUS application (right)                                                           |

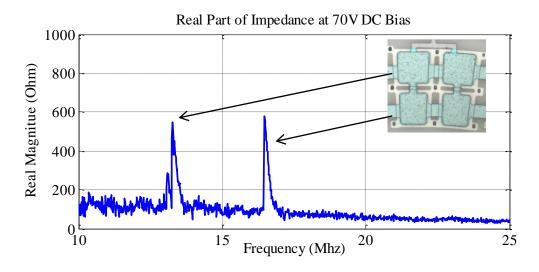

| Figure 73.Agilent network analyzer measurement of real electrical impedance of            |

| fabricated CMUT on CMOS device showing 2 distinct resonant peaks due to membrane          |

| geometry differences. The peaks of this transmitter are measured at 13.3 MHz and 16.5     |

| MHz                                                                                       |

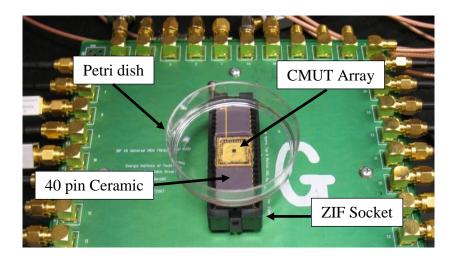

| Figure 74. Experimental set up of wire-bonded 1.6 mm dual-ring CMUT array in a            |

| ceramic package combined with a modified Petri dish. The custom PCB board interfaces      |

| the ceramic package to external pulsers, FPGA board, high voltage bias lines, and signal  |

| output line to the digitizer card via SMA connections                                     |

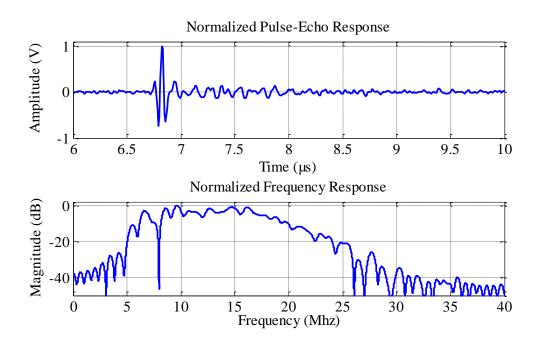

| Figure 75. Pulse-echo response from a single pair of transmit and receive elements,       |

| showing functioning CMUT on CMOS array element, top. Frequency response from a            |

| dual ring array element in water shows that the CMUT on CMOS fabrication was              |

| successful and frequency response has enough bandwidth for imaging capabilities,          |

| bottom                                                                                    |

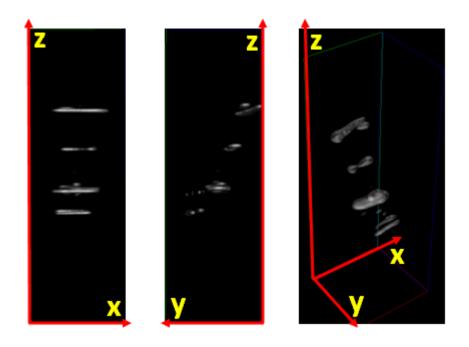

| Figure 76. Side, front, and isometric views of a volume 2 mm x 2 mm x 6 mm of a 4 wire    |

| target, 15 dB dynamic range                                                               |

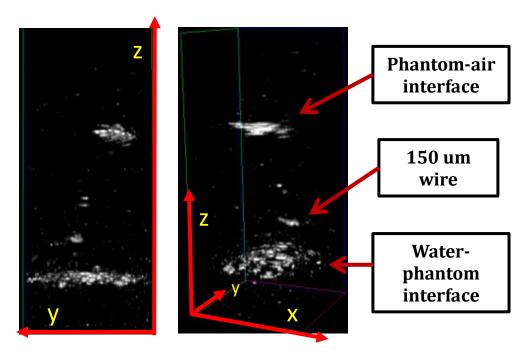

| Figure 77. Tissue-like phantom with scattering and embedded wire target of a 4 mm x 4     |

| mm x 9 mm volume, front and isometric view with 15 dB dynamic range,                      |

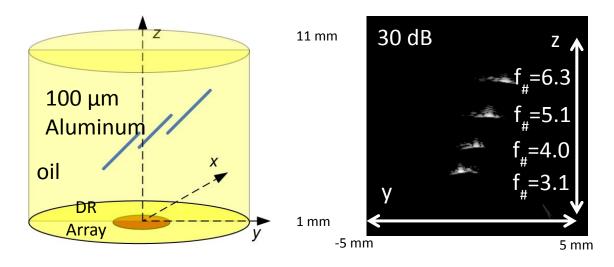

| Figure 78. A depiction of a wire target in oil (left) and cross-section of a reconstructed             |

|--------------------------------------------------------------------------------------------------------|

| volume with 30 dB SNR (right)                                                                          |

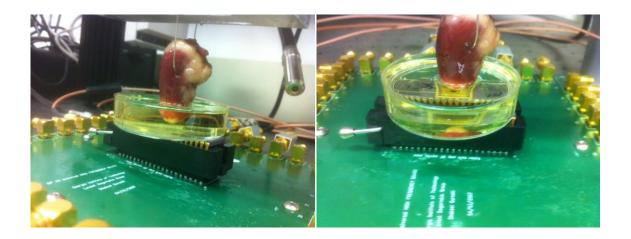

| Figure 79. A chicken heart suspended 2.5 mm above a CMUT-on-CMOS array in oil. 110                     |

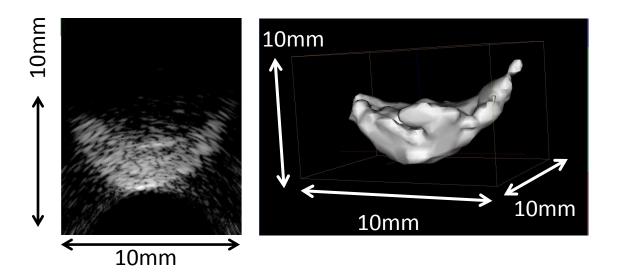

| Figure 80. A cross-sectional view and isometric 3D image of a chicken heart using GE                   |

| Microview with a 40 dB dynamic range                                                                   |

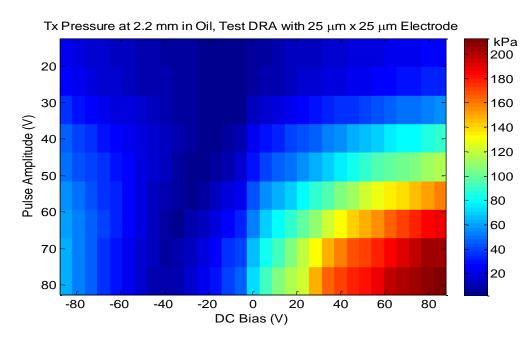

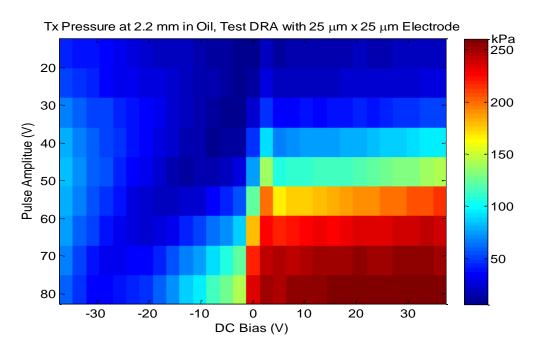

| Figure 81. Transmit pressure for the chromium CMUT with 100 nm gap 114                                 |

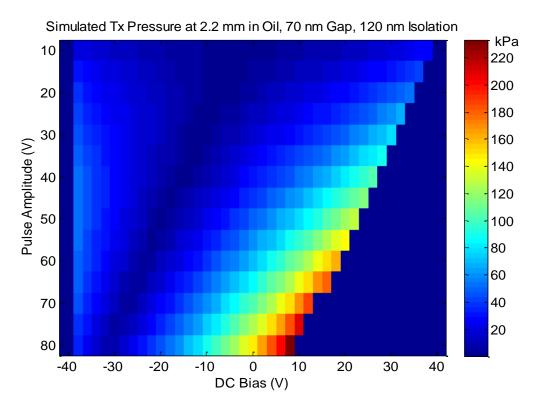

| Figure 82. Transmit pressure for the copper CMUT with 70 nm gap                                        |

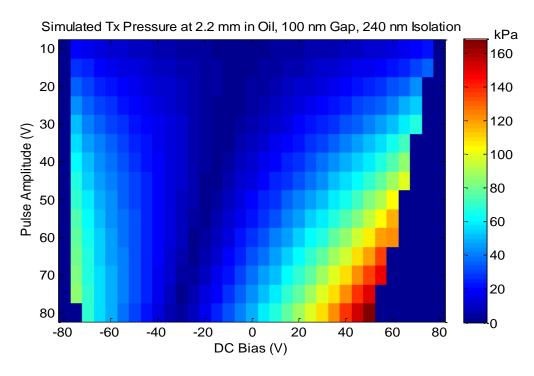

| Figure 83. Simulated transmit pressure for the CMUT with 100 nm gap and 240 nm of                      |

| silicon nitride isolation                                                                              |

| Figure 84. Simulated transmit pressure for the CMUT with 70 nm gap and 120 nm of                       |

| silicon nitride isolation                                                                              |

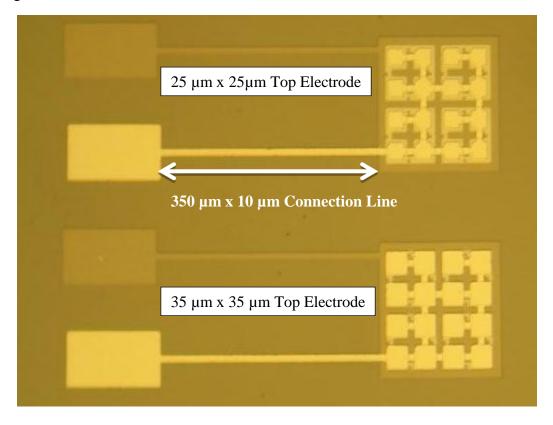

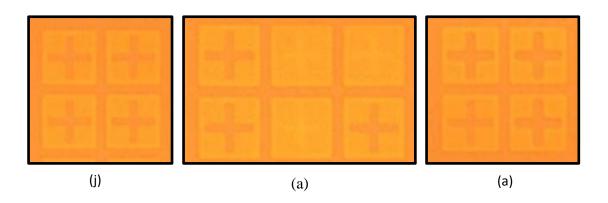

| Figure 85. Sample DRA test elements using 35 $\mu$ m x 35 $\mu$ m membranes in a 4 x 4                 |

| configuration with bond pads for electrical connection. Two options include 25 $\mu m \; x \; 25$      |

| $\mu m$ top electrode coverage (top) and full electrode 35 $\mu m$ x 35 $\mu m$ coverage (bottom). 117 |

| Figure 86. An annular array on the side of an IVUS catheter wire bonded to associated                  |

| electronics which is rotated to generated a 2D cross-sectional image                                   |

| Figure 87. Four annular array devices placed on the outside of a catheter and wire bonded              |

| to electronics (left) and four annular arrays integrated with custom electronics to                    |

| eliminate wire bonding (right)                                                                         |

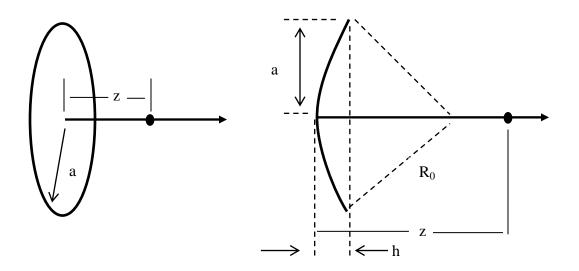

| Figure 88. Circular piston (left) and circular piston with fixed curvature (right) 122                 |

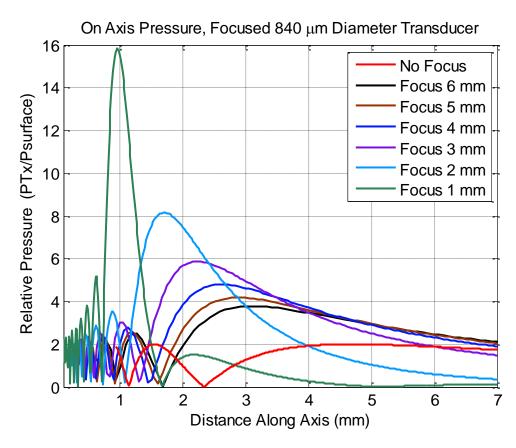

| Figure 89. On axis pressure for a piston transducer without focus and with focusing from               |

| 6 mm to 1 mm                                                                                           |

| Figure 90. Simulated 2D PSFs for different probe types for an image depth of 3.36 mm.      |

|--------------------------------------------------------------------------------------------|

| The transducer with imaging plane is shown (top) cross-section at f/2 and f/4 (middle)     |

| and surface cross section at f/2 (bottom) [110]                                            |

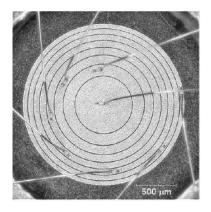

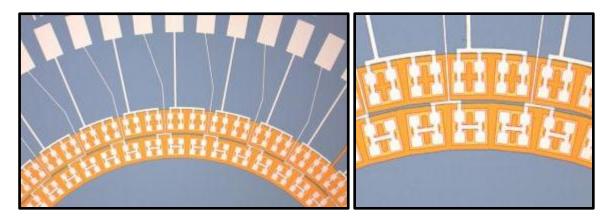

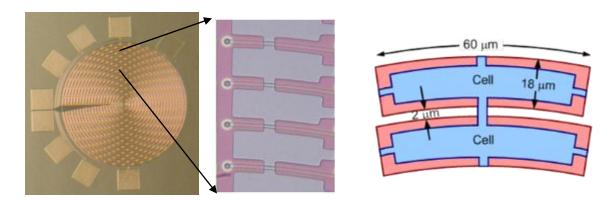

| Figure 91. Fabricated 8 element CMUT annular array (left) with membrane dimensions         |

| (right)                                                                                    |

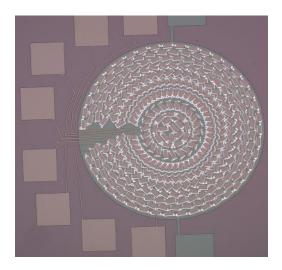

| Figure 92. Second generation of annual array with equal area elements along with varied    |

| periodicity in the radial direction. 127                                                   |

| Figure 93. A third generation annular array with square membranes for reduced acoustic     |

| cross talk                                                                                 |

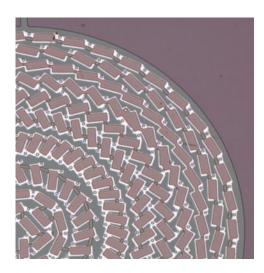

| Figure 94. The test setup used for annual array evaluation in a water bath using a         |

| hydrophone with xyz stage                                                                  |

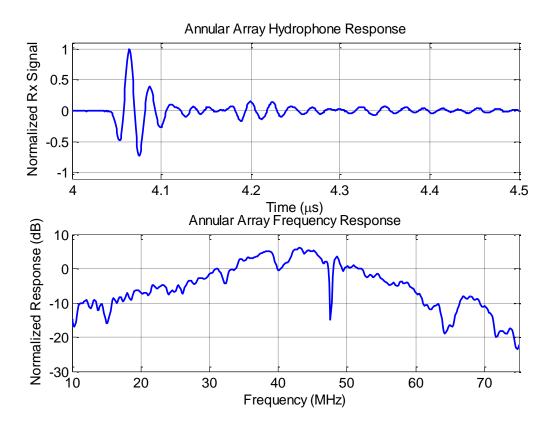

| Figure 95. A sample time domain normalized receive signal from the center annular array    |

| element with corresponding frequency response                                              |

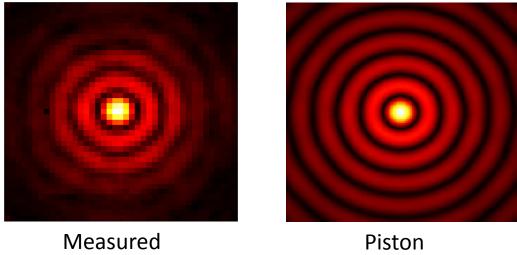

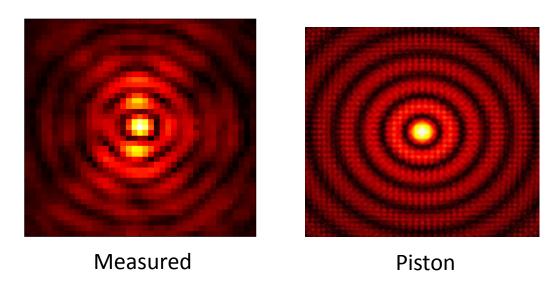

| Figure 96. Radiation pattern from the 4th element filtered at 38MHz, measured versus       |

| piston approximation                                                                       |

| Figure 97. Radiation pattern from the 6th element filtered at 32 MHz, measured versus      |

| piston approximation                                                                       |

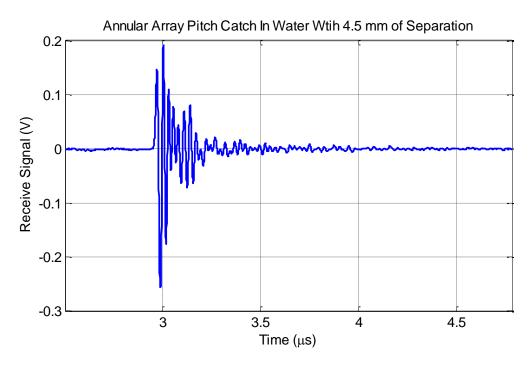

| Figure 98. Initial annular array pitch catch experiment in water                           |

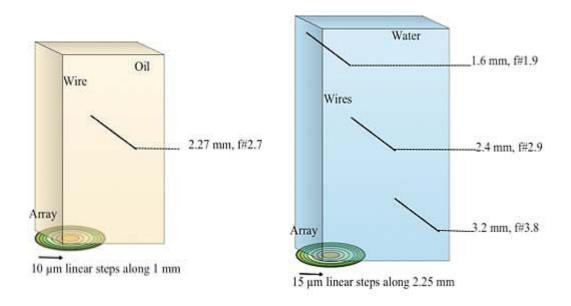

| Figure 99. Experimental setups used for evaluation of the 20 MHz array (left) and 50       |

| MHz array (right) [110]                                                                    |

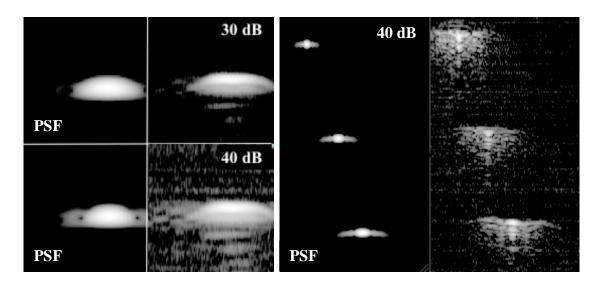

| Figure 100. Imaging results are compared to the theoretical point spread functions for the |

| 20 MHz experiment (left) and 50 MHz experiment (right) [110]                               |

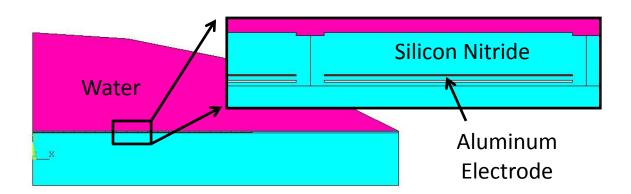

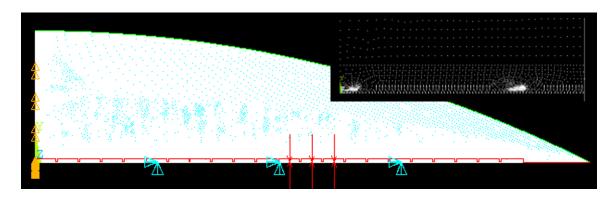

| Figure 101. Annular array geometry modeled in ANSYS                                        |

| Figure 102. Annular array geometry meshed with boundary conditions shown as triangles     |

|-------------------------------------------------------------------------------------------|

| and loads as arrows. 136                                                                  |

| Figure 103. Finite element analysis shows the frequency response of a CMUT element,       |

| 5 <sup>th</sup> ring, and crosstalk to neighboring elements                               |

| Figure 104. Surface displacement at 25 MHz with the 5 <sup>th</sup> element active        |

| Figure 105. Annular array with varied periodicity in the two directions 90 degrees apart. |

|                                                                                           |

| Figure 106. Measured radiation pattern versus a single FEA simulation versus the          |

| expanded FEA simulation                                                                   |

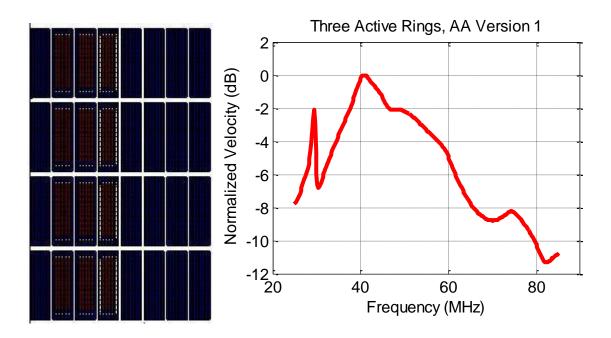

| Figure 107. Annular array version 1 simulation with 3 active rings in a 4 by 8 membrane   |

| simulation                                                                                |

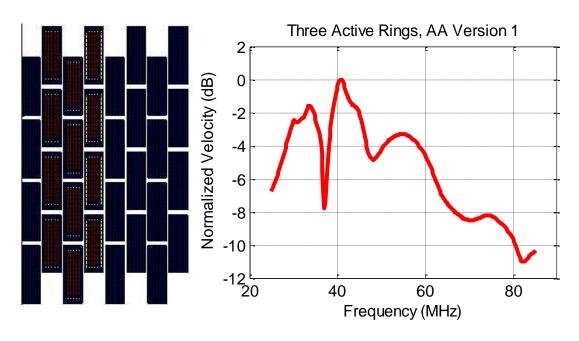

| Figure 108. Annular array version 1 simulation with 3 active rings in a 4 by 8 membrane   |

| simulation offset to simulate the alternate radial periodicity                            |

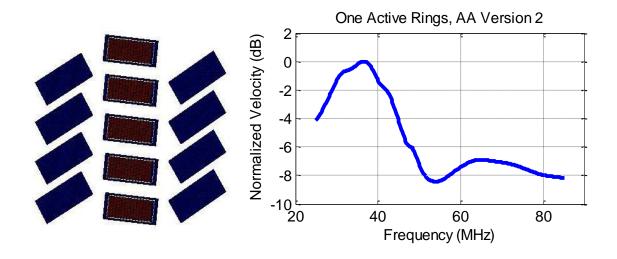

| Figure 109. Annular array version 2 simulation with 1 active ring to simulate the third   |

| element                                                                                   |

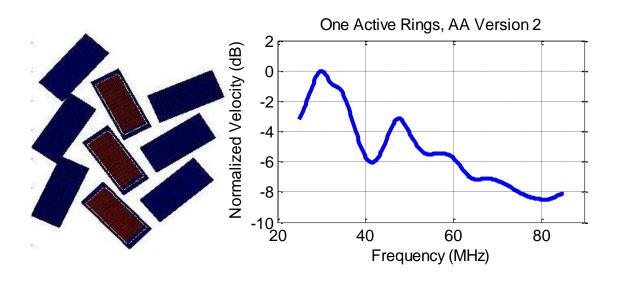

| Figure 110. Annular array version 2 simulation with 1 active ring to simulate the fifth   |

| element                                                                                   |

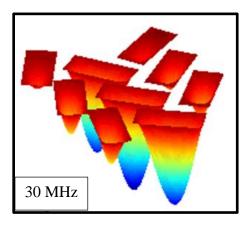

| Figure 111. Mode shapes at 30 MHz and 41 MHz for the array configuration shown in         |

| the figure above                                                                          |

| Figure 112. Annular array version 3 simulation with 1 active ring from three rows         |

| combined                                                                                  |

| Figure 113. Annular array version 3 simulation with 1 active ring from three shifted rows |

| combined 143                                                                              |

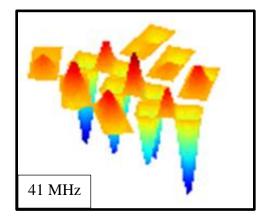

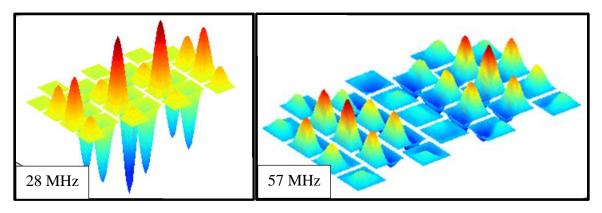

| Figure 114. Mode shapes at 28 MHz and 57 MHz for the array configuration shown in             |

|-----------------------------------------------------------------------------------------------|

| the figure above                                                                              |

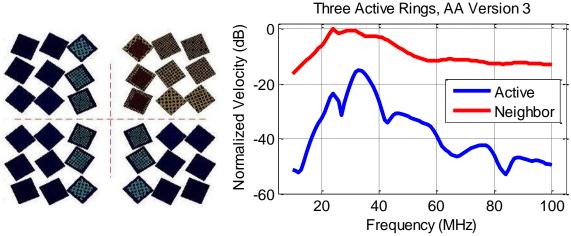

| Figure 115. Annular array version 3 simulation with membrane rotation to remove               |

| periodicity                                                                                   |

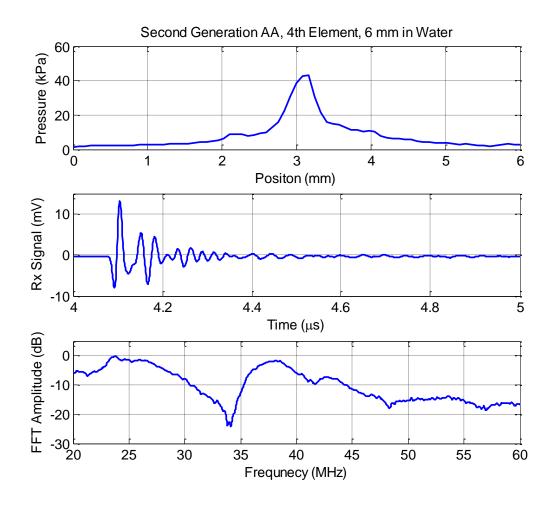

| Figure 116. Annular Array, second generation radiation pattern at 6 mm, received              |

| hydrophone signal, and FFT of the time domain signal                                          |

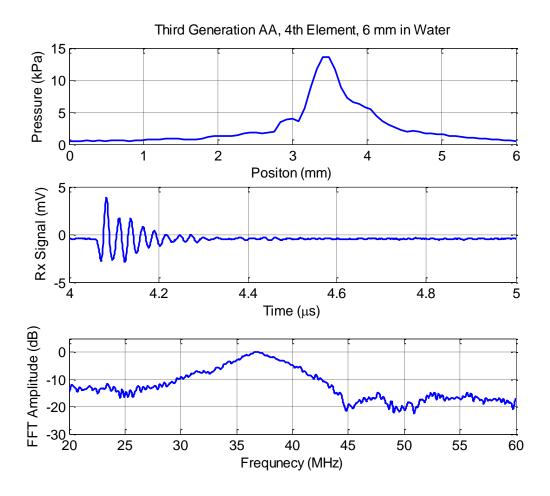

| Figure 117. Annular Array, third generation radiation pattern at 6 mm, received               |

| hydrophone signal, and FFT of the time domain signal                                          |

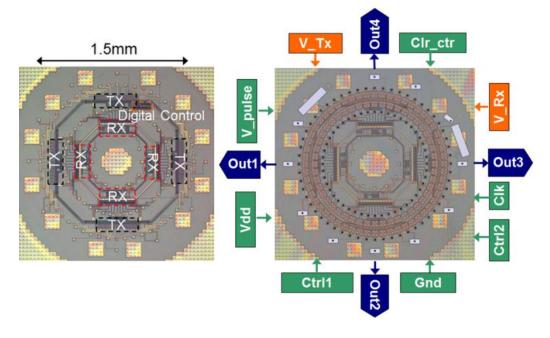

| Figure 118. CMOS electronics for a 1.4 mm diameter FL-IVUS array (left) and the same          |

| silicon array with CMUTs fabricated above electronics with 13 electrical connections          |

| (right)                                                                                       |

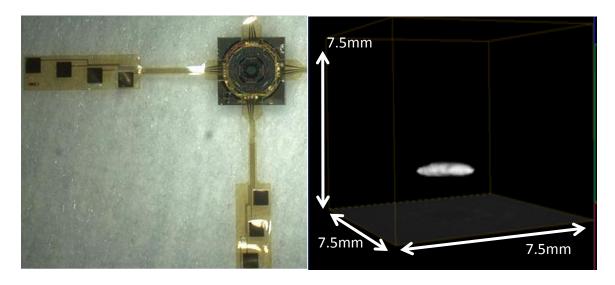

| Figure 119. Flex tape integrated via top side connection (left) and reconstructed image of    |

| a 0.5 mm wire target 3.5 mm above the array with a 40 dB dynamic range (right) 151            |

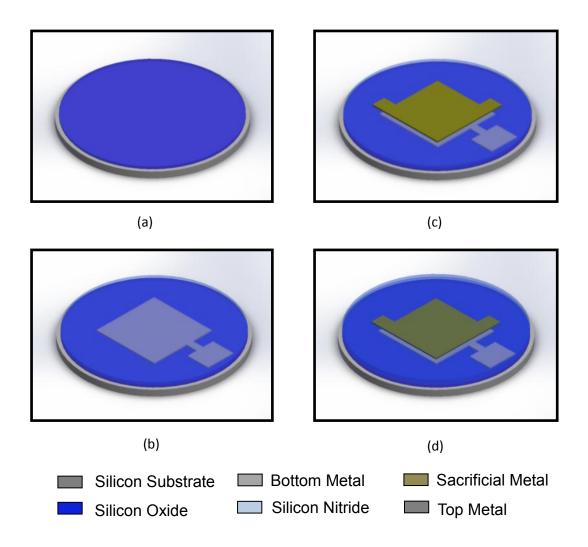

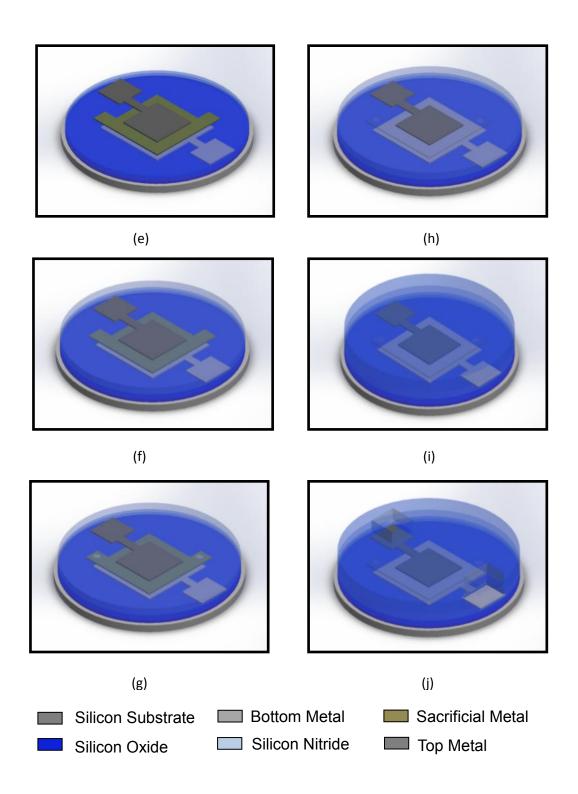

| Figure 120. CMUT fabrication process steps. 158                                               |

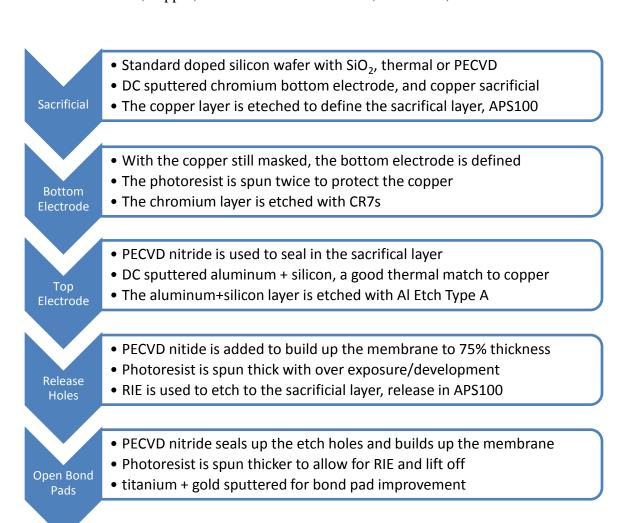

| Figure 121. Process flow for the use of copper as a sacrificial layer                         |

| Figure 122. The sacrificial layer in (a) is properly etched with clean, sharp definition. The |

| sacrificial layer in the center of (b) shows failed sacrificial etching from the formation of |

| bubbles on the surface. The sacrificial layer on the right side of (c) shows over etching     |

| from excessive sloshing                                                                       |

| Figure 123.The chromium bottom electrode is larger than the sacrificial copper as a           |

| protection measure against the CR7S. For this device, the distance in the radial direction    |

| from the sacrificial layer to the bottom electrode is approximately 7 um                      |

#### LIST OF ABBREVIATIONS

- 1. ASIC Application-specific integrated circuit

- 2. BEM Boundary element method

- 3. CMOS Complementary metal oxide semiconductor

- 4. CMUT Capacitive micromachined ultrasonic transducer

- 5. CTO Chronic total occlusion

- 6. DEMUX Demultiplexer

- 7. DOF Depth of field

- 8. DRA Dual ring array

- 9. FEA Finite element analysis

- 10. FL Forward looking

- 11. FPGA Field-programmable gate array

- 12. ICE Intracardiac echocardiography

- 13. IVUS Intravascular ultrasound

- 14. LPCVD Low pressure chemical vapor depostion

- 15. MIMO Multiple-input multiple-output

- 16. MISO Multiple-input single-output

- 17. MUX Multiplexer

- 18. NDE Non-destructive evaluation

- 19. PCB Printed circuit board

- 20. PECVD Plasma enhanced chemical vapor deposition

- 21. PZT Lead zirconate titanate

- 22. SL Side looking

- 23. SMA SubMiniature version A (connector)

- 24. SNR Signal-to-noise ratio

- 25. TAVI Transcatheter aortic valve implantation

- 26. TIA Transimpedance amplifier

- 27. TSMC Taiwan Semiconductor Manufacturing Company Limited

- 28. TSV Through silicon via

- 29. RIE Reactive ion etching

- 30. Rx Receive

- 31. Tx Transmit

#### **SUMMARY**

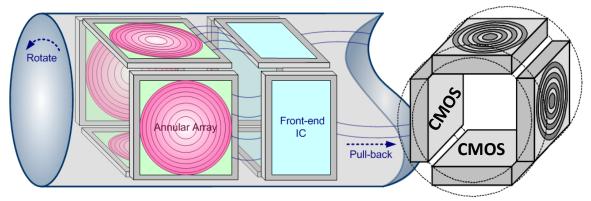

The objective of this research is to develop novel capacitive micromachined ultrasonic transducer (CMUT) arrays for intravascular ultrasonic (IVUS) imaging along with the fabrication processes to allow for monolithic integration of CMUTs with custom CMOS electronics for improved performance. The IVUS imaging arrays include dual-ring arrays for forward-looking volumetric imaging in coronary arteries and annular-ring arrays with dynamic focusing capabilities for side-looking cross sectional imaging applications. Both are capable of integration into an IVUS catheter 1-2 mm in diameter.

The research aim of monolithic integration of CMUTs with custom CMOS electronics has been realized mainly through the use of sloped sidewall vias less than 5 µm in diameter, with only one additional masking layer as compared to regular CMUT fabrication. Fabrication of CMUTs has been accomplished with a copper sacrificial layer reducing isolation layers by 50%.

Modeling techniques for computational efficient analysis of CMUT arrays were developed for arbitrary geometries and further expanded for use with larger signal analysis.

Dual-ring CMUT arrays for forward-looking volumetric imaging have been fabricated with diameters of less than 2 mm with center frequencies at 10 MHz and 20 MHz, respectively, for an imaging range from 1 mm to 1 cm. These arrays, successfully integrated with custom CMOS electronics, have generated 3D volumetric images with only 13 cables necessary. Performance from optimized fabrication has reduced the bias required for a dual-ring array element from 80 V to 42 V and in conjunction with a full electrode transmit array, it was shown that the SNR can be improved by 14 dB. Simulations were shown to be in agreement with experimental characterization indicated transmit surface pressure in excess of 8 MPa.

For side-looking IVUS, three versions of annular CMUT arrays with dynamic focusing capabilities have been fabricated for imaging 1 mm to 6 mm in tissue. These arrays are 840  $\mu$ m in diameter membranes linked to form 8 ring elements with areas that deviate by less than 25 %. Through modeling and simulation undesirable acoustic cross between ring elements was reduced from -13 dB to -22 dB.

#### **CHAPTER 1**

#### INTRODUCTION AND BACKGROUND

#### 1.1. Motivation

Heart disease in its various forms is the leading cause of death in developed countries, and as such, the diagnosis and treatment with non-invasive techniques is of particular interest [1]. Based on 2007 mortality statistics in the United States, 2200 people die each day from cardiovascular disease claiming more lives than cancer, chronic lower respiratory disease, and all accidents combined [2].

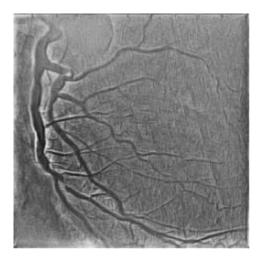

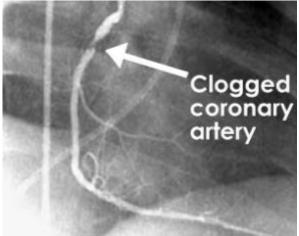

Angiography remains a standard medical imaging technique for the diagnosis of heart disease through where an X-ray absorbing contrast agent is inserted into the blood vessel while X-ray imaging techniques such as fluoroscopy are used to evaluate the flow of blood [3, 4]. Figure 1 shows two example angiograms with normal blood flow on the left and a clogged coronary artery indicated in the image on the right [5, 6]. While this method accurately shows the flow inside of the vessel, it fails to show any information about the arterial wall itself, and it subjects the patients to potentially harmful radiation [7].

To assist in the diagnosis and treatment of heart disease where the angiogram is unclear, specialized catheters with ultrasonic imaging capabilities were developed with the ability to provide a cross-sectional image equating to a plane perpendicular to the catheter tip [3, 8]. The following summarizes current intravascular ultrasound (IVUS) technology, discusses common medical interventions assisted by IVUS and identifies physical catheter constraints.

Figure 1. Sample angiograms from a fluoroscopic procedure showing the blood flow through the vessels (left) and a clogged coronary artery (right) [5, 6].

#### 1.2. IVUS Catheters

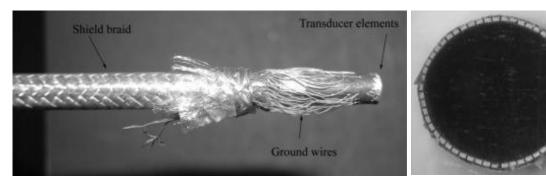

Since their first appearance in the late 1990's, piezoelectric based IVUS has become an accepted tool for coronary and vascular imaging to assist in the diagnosis and treatment of heart disease with a single mechanically scanned transducer or a multi-element electronically steerable assembly as shown in Figure 2 [9]. To date, all commercially available ultrasonic imaging catheters are based upon piezoelectric transducer technology with fabrication techniques that typically require thinning of a piezoelectric substrate and subsequent dicing. The shapes and sizes producible are limited by the capabilities of the dicing and handling. The ability to process and handle smaller piezoelectric samples is a major avenue of current research including such process as thin film deposition and laser dicing [10, 11].

Figure 2. Examples of single-element and multi-element transducer configurations with imaging planes shown on the right [9].

Catheters are available in a variety of sizes from 3 French to 15 French which corresponds to diameters of one to five mm respectively with a central guide wire on many of the designs. The smaller sized catheters, on the order of 1-2 mm in diameter, are used for IVUS while larger catheters on the order of 3-5 mm are useful for intracardiac echocardiography, ICE. As such, piezoelectric transducer fabrication is better suited for larger transducers or transducer arrays, and it is not ideal for small scale transducer elements required for IVUS applications. The standard frequency range of operation varies from 5 MHz up to 45 MHz depending upon the application and imaging resolution desired. Additional research includes higher frequency transducers beyond 45 MHz for harmonic imaging modalities and/or increased resolution [12-14].

Standard IVUS catheters can be divided into two main categories depending upon whether they utilize a single-element or multi-element array as shown in Figure 2. The single-element catheter is relatively simple in design requiring minimal electronics integration, but it requires 360 degree mechanical rotation to form an image. Conversely,

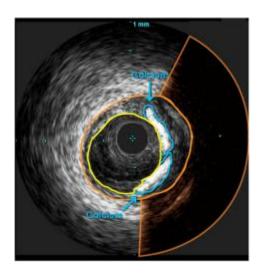

the multi-element catheters, which can have up to 64 elements wrapped around the catheter, require complex electronics but don't necessarily require constant rotation. By retracting the catheter at a known rate, the tissue can be imaged in a 3D manner through the acquisition of multiple cross-sectional images. Sample cross-sectional images are shown in Figure 3 and show a normal vessel, left, and a vessel with plaque and calcification, right [15]. Although current commercial IVUS catheters are predominantly side-looking with the inability to image directly in front of the catheter, Volcano has introduced a "forward-looking" catheter with RF ablation capabilities. This catheter requires rotation and only produces an image over a conical surface but not a full 3D volumetric image in front of the catheter and it doesn't appear to be for sale as of August 2012 [16].

Figure 3. IVUS cross-sectional images of a normal vessel (left) and with calcification (right) [15].

### 1.3. Angioplasty and Stent Placement

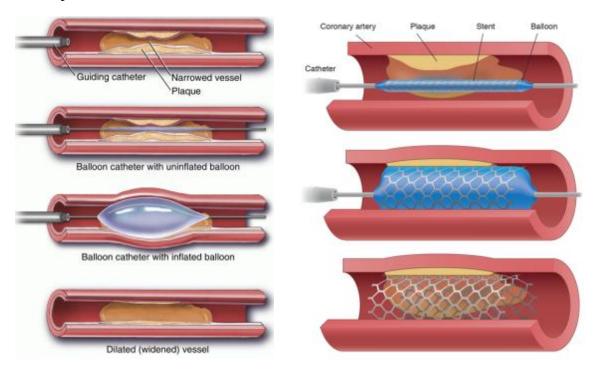

IVUS procedures of particular interest for the treatment of heart disease requiring accurate non-destructive evaluation (NDE) of the vascular system include, but are not limited to, angioplasty and stent placement. Angioplasty is a procedure to unblock or

expand occluded arteries where an inflatable balloon on the end of a catheter is used to compress the plaque buildup through repeated inflation and deflation, Figure 4-left [17]. Following the angioplasty, and depending upon the situation, a stent can be permanently placed and expanded to support the arterial wall helping it to remain open for a longer period of time, Figure 4-right. This stent, which is commonly a wire mesh, can also be coated with medicines to prevent the artery from becoming clogged. Currently, accurate stent placement is difficult, with the stent often being completely misplaced altogether. There is also a desire for high-resolution imaging capable of evaluating how the stent is interacting with the surround tissue just after placement, and for reevaluation after an extended period of time.

Figure 4. A pictorial diagram of the angioplasty procedure (left) and the stent placement procedure (right) [17].

Because of the limited imaging capabilities of current IVUS catheters, namely the imaging plane perpendicular to the catheter axis, physicians and other clinical personnel often have difficulty guiding the catheter through the many vascular branches before it is retracted for 3D imaging. These procedures would directly benefit from the inclusion of

forward-looking capabilities on the catheter to evaluate the effectiveness of the vessel dilation and proper stent placement and expansion.

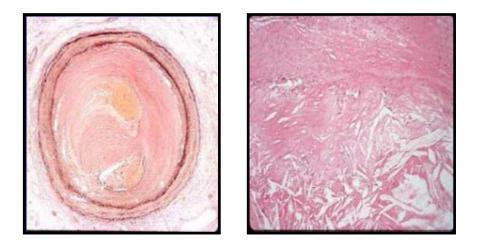

#### 1.4. Chronic Total Occlusions

Complications also arise with chronic total occlusions (CTOs), defined as when the artery has been completely blocked for more than 30 days. Blood flow from stenosed vessels can be decreased to such an extent as to be clinically significant. In Figure 5 the vessel is completely occluded, and the guide wire is used to push through the plaque. This situation occurs in approximately 30% of patients suffering from coronary disease [3, 18]. Occluding plaque can be divided into two categories based on the physical properties, hard and soft, Figure 6. The hard plaque is fibrocalcific, more than 50% collagen and calcium while the soft plaque is cholesterol, macrophages, and loose fibrous tissue. Treatment options include medication, ~22%, surgery, ~31%, and angioplasty ~47% [18]. Unfortunately, angioplasty for these patients is more resource intensive in terms of device utilization, catheter lab time, and fluoroscopy exposure which also leads to greater exposure to radiation. For these situations, advancing catheters are unable to image in front of them, and in more severe situations, the catheter can rupture the vessel wall while attempting to pass an occlusion as the guide wire progresses as depicted in Figure 5-right. For this scenario, the forward-looking IVUS catheter would be beneficial to evaluate the blockage and reduce procedure time along with associated catheter lab resources.

Figure 5. CTO imaging demonstrating the two imaging scenarios. The catheter approaches the CTO through the blood (left) and the catheter is pushing through the occlusion (right) [18].

Figure 6. Hard plaque (left) and soft plaque (right) [18].

### 1.5. Heart Valve Replacement

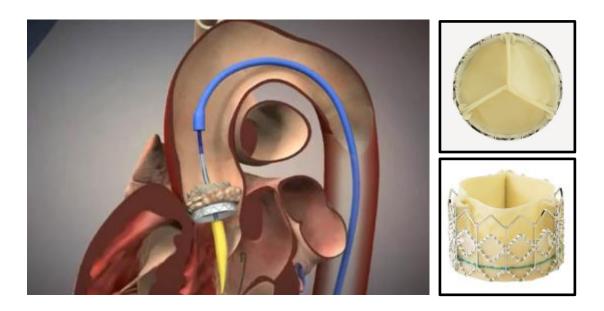

Heart surgery is routinely performed to repair or replace diseased heart valves through open heart surgery or less invasive procedures with a catheter inserted through a smaller incision. Recent developments have focused on the use of intracardiac echocardiography (ICE) catheters to replace heart valves without the need for invasive open heart surgery. The transcatheter aortic valve implantation (TAVI) depicted in

Figure 7 uses a catheter inserted in the groin area to deploy a prosthetic heart valve [19, 20]. The valve shown is comprised of three bovine pericardial tissue leaflets integrated with stainless steel expandable stent which remains compressed until it reaches the aortic valve. A balloon on the catheter is used to expand the valve within the current diseased valve to act as a direct replacement. Candidates for these percutaneous procedures include patients deemed to be inoperable as defined as a patient who faces more than a 50% risk of death following the standard surgical procedure. Patients in this category include those of advanced age or previous heart surgery. The TAVI and other procedures requiring soft tissue imaging of the heart benefit from forward-looking improved imaging capabilities for accurate valve deployment/evaluation or other repair procedure.

Figure 7. A TAVI procedure is shown placing a prosthetic aortic valve through the use of a catheter inserted through the groin area (left) and a prosthetic heart valve based on an expandable stent mesh (right) [19, 20].

#### 1.6. Catheter Constraints

Intravascular catheters, by their very nature, have certain limitations as they are inserted into the human body. They are inserted and guided through the vascular system around corners and through various branches. The whole assembly including tip with transducers and associated electronics must be flexible enough to reach the affected area. The number of cables for powering electronics and signal transmission are limited, on the order of 25 cables/mm², which translates to ~ 20 cables for a 3 French/1mm diameter catheter based on Tyco Electronics 48 AWG coax cable documentation [21]. Additionally, within the body, there are voltage limitations to prevent accidental shocking of the patient, which can lead to fibrillation and other complications.

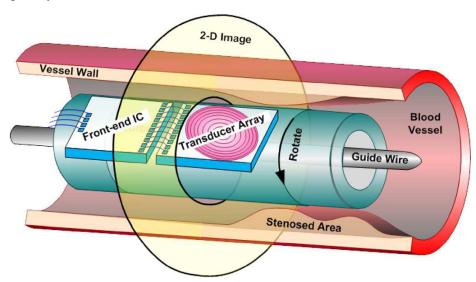

With these constraints in mind, the transducer arrays for forward-looking IVUS and ICE capabilities need to be small in diameter to fit on the tip of the catheter while incorporating a center hole for a guide wire as shown in Figure 8. The element sizes for the ring array also need to be small in the radial and lateral dimensions to reduce side lobes which adversely affect imaging performance. To generate the volumetric image with sufficient SNR, the array area would also completely cover the doughnut shape tip real-estate. Therefore with a larger number of small transducer elements there is an inherent desire for direct electronics integration at the tip for signal amplification and to multiplex the output as constrained by the limited cable count.

The capacitive micromachined ultrasonic transducer (CMUT) has been introduced to address the limitations of piezoelectric transducer technology, namely the difficulty in fabrication of small, thin elements and the ability to integrate with electronics [22]. The following chapter will introduce the CMUT technology that will be investigated for use in developing ring arrays for real-time volumetric imaging capable of integration on the tips of IVUS catheters similar to the depiction of Figure 8.

Figure 8. A depiction of a forward-looking ultrasonic catheter with guide wire.

## **CHAPTER 2**

# CMUTs: BASIC MODEL, DESIGN CRITERIA AND FABRICATION BACKGROUND WITH INTEGRATED ELECTRONICS

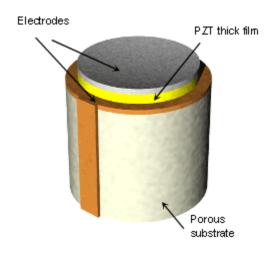

Although theorized in the late 1800's it wasn't until the 1990's that it was possible to micromachine CMUTs capable of competing with piezoelectric transducers in terms of performance [22]. These CMUTs offer an attractive alternative to the piezoelectric transducers, (mostly lead zirconium titanate PZT based), technology, especially while attempting to fabricate and integrate both forward-looking (FL) and side-looking (SL) arrays into a single IVUS catheter. This chapter will introduce the basics of CMUTs as well as the specific design requirements for FL and SL arrays with improved performance as compared to the currently available commercial IVUS catheters.

#### 2.1. Introduction to CMUTs

## 2.1.1. CMUT Operation

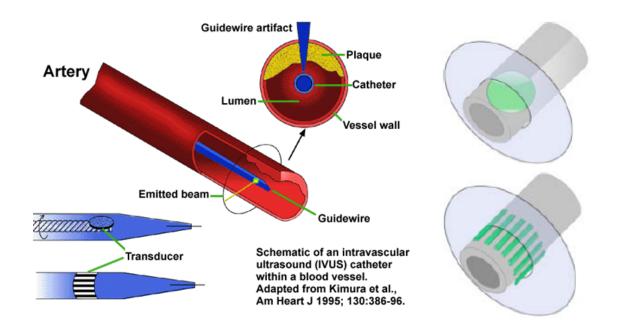

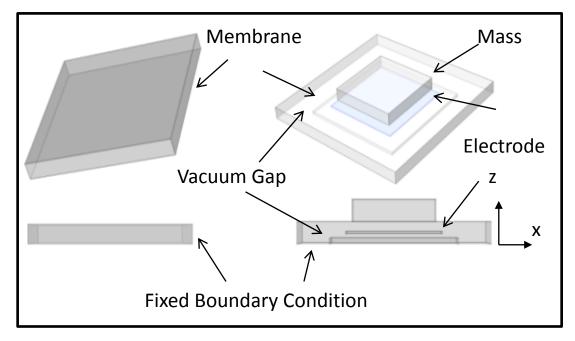

In its most basic form, a CMUT is comprised of two electrodes with a vacuum gap between. One electrode is fixed, the bottom electrode, and the other electrode is buried inside or affixed to a top, movable membrane. Figure 9 shows a cross-sectional diagram of such a CMUT with silicon nitride as the membrane material and buried top electrode above a vacuum gap. Appendix A describes the standard CMUT fabrication used for this research. A DC bias is applied to provide charge to the top electrode which in turn deflects the membrane closer to the bottom electrode setting up an electric field in the GV/m range. Additionally, this increases the linearity of the response. This is similar to the standard capacitive electret type microphones which utilizes a permanently trapped

charge in a material such as Teflon<sup>TM</sup> as opposed to an external DC bias [23]. In the transmit mode of operation, an AC signal is also applied to induce membrane motion which couples to the surrounding fluid generating the ultrasound for imaging. In the receive mode of operation, incoming ultrasonic waves impinge upon the membrane causing it to deflect which in turn changes the capacitance of the transducer generating a detectible current.

Figure 9. Cross-sectional image of a CMUT, primarily made from silicon nitride.

## 2.1.2. Static Parallel Plate CMUT Analysis

A CMUT has a compliant membrane typically with an electrode gap separation much smaller than the lateral dimensions, aspect ratios >> 100. Neglecting the deflected membrane shape, a simple parallel plate actuator can be used to develop analytical models to better understand the operation of a CMUT. Figure 10 shows a first order model with a spring-mass-dashpot mechanical system with an applied potential between the top and bottom electrodes. For a static analysis, the mass associated with membrane

and the force from the dashpot can be ignored, and the force balance between the membrane stiffness, k, and the electrostatic force can be evaluated.

Figure 10. An illustration of a parallel plate CMUT model of the first-order.

The mechanical force from the spring can be described by equation (1) where k is the spring constant associated with the membrane stiffness,  $g_0$  is the initial gap, and g is the instantaneous gap. The electrostatic force is given by equation (2) where A is the electrode surface area,  $\varepsilon_0$  is the permittivity of the space between the electrodes, and  $V_0$  is the applied potential. When the mechanical force and electrostatic force are in equilibrium, the net force on the membrane is zero. By mathematically setting the electrostatic force equal to the mechanical force it can be shown that after a certain potential,  $V_0 = V_{collapse}$ , the electrostatic force will always be greater than the mechanical force, equation (3) leading to a condition where the membrane will completely deflect

leading to a collapsed condition. By plugging equation (3) into the force balance, the membrane displacement at collapse,  $x_{collapse}$ , can be simplified and is found to be 1/3 of the original gap, equation (4). Figure 11 shows the static mechanical and electrostatic forces as a function of the normalized membrane displacements at collapse and after collapse. It can be seen that as the collapse is approached, the static equilibrium occurs at 1/3 of the gap, whereas the electrostatic force is always greater than the mechanical force after collapse [24].

$$F_{\rm S} = k(g_0 - g) \tag{1}$$

$$F_{es} = -\frac{\varepsilon_0 A V_0^2}{2g^2} \tag{2}$$

$$V_{collapse} = \sqrt{\frac{8kg_0^3}{27\varepsilon_0 A}} \tag{3}$$

$$x_{collapse} = \frac{g_0}{3} \tag{4}$$

Figure 11. Mechanical and electrostatic forces at collapse (left) and after collapse (right) for a parallel plate actuator with k = 1 kN/m and  $g_0 = 0.1$  µm [24].

# 2.1.3. <u>Small Signal AC Mason Equivalent Circuit Model</u>

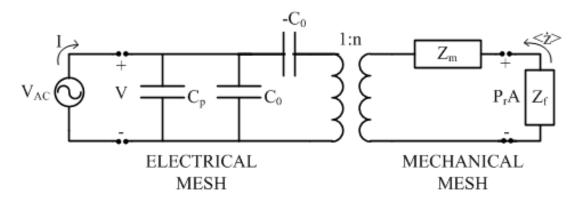

The CMUT is a reciprocal transducer converting electrical energy into mechanical in the transmit (Tx) mode of operation and mechanical to electrical in the receive (Rx) mode of operation. The Mason Equivalent circuit can be used to investigate CMUT operation in fluid assuming linear, small-signal analysis with parallel plate operation [25]. The deformed membrane profile is again neglected for the parallel plate, and it is assumed that the dynamic voltage and displacements are much smaller than their associated static components. Figure 12 shows the circuit with an electrical mesh consisting of an AC signal with parasitic capacitor,  $C_p$ , and membrane capacitance with DC bias,  $C_0$ . The mechanical mesh includes complex impedances for the membrane and fluid,  $Z_m$  and  $Z_f$ , respectively. The two meshes are connected via a transformer with ratio 1:n, where the current in the electrical domain is equivalent to the velocity in the mechanical domain. Through algebraic manipulation and circuit analysis, it can be

shown that the transformer ratio, n, is inversely proportional to the square of the effective gap of the CMUT, equation (5). In this equation  $\varepsilon_r$  is the relative permittivity of the isolation material between the electrodes, 6.7 for silicon nitride, and  $t_{nit}$  is the thickness of the isolation [26]. As the DC bias is increased, the gap is reduced up to the point of collapse, 1/3 of the equivalent gap, to yield the greatest transformer ratio. It can be shown that at collapse, the transformer ratio is only dependent up on the initial gap, equation (6). Therefore one would like to fabricate CMUTs with the smallest possible gap for highest Rx mode sensitivity. A more complete derivation and evaluation of the Mason equivalent circuit can be found in [24, 27].

Figure 12. Mason equivalent circuit.

$$n = \frac{F_{es,AC}}{V_{AC}} = -\frac{\varepsilon_0 A}{\left(g + \frac{t_{nit}}{\varepsilon_r}\right)} \frac{V_{DC}}{\left(g + \frac{t_{nit}}{\varepsilon_r}\right)} = C_0 E$$

(5)

$$n_{collapse} = \sqrt{\frac{3kA\varepsilon_0}{2g_0}} \tag{6}$$

# 2.1.4. CMUTs in Comparison to Piezoelectric Transducers

Two distinct advantages are easily identifiable when comparing CMUTs to their piezoelectric counterparts within the context of catheter integration. For IVUS imaging arrays, dicing of the brittle piezoelectric materials as the element sizes drop below 200 µm is expensive and difficult, a significant drawback. Alternatively, CMUT technology is based on micromachining principles which allow for batch fabrication of transducer arrays of arbitrary shapes and sizes well below 20 µm. The bulk fabrication and ability to define curved, micron scale, features are a significant advantage when working with circular arrays for catheters. The processes used in the fabrication are well defined and characterized having been originally developed for the semiconductor industry.

Secondly, the fabrication processes involved with CMUTs are compatible with CMOS technology. This key feature allows for the transducer-electronics necessary to achieve compact assemblies with reduced cable counts as well as improved SNR associated with the direct connection of CMUT elements to amplifier electronics with details to be further discussed in the following sections.

To determine the resonant frequency, the standard piezoelectric transducer element is thinned to an appropriate thickness, with additional matching layers as the impedance of the transducer material can be significantly greater than that of water. In the case of lead titanate, PbTiO3, the impedance is 36 MRayls, 24 times that of water, 1.5 MRayls [28]. These matching layers are difficult to realize and reduce the bandwidth which is detrimental to the axial resolution. In terms of performance, previously fabricated CMUTs show greater fractional bandwidth than comparable PZTs [27, 29-32]. The impedance of a CMUT is lower than that of water leading to an over-damped system. This in turn leads to the larger bandwidth and improved transmission into water [33].

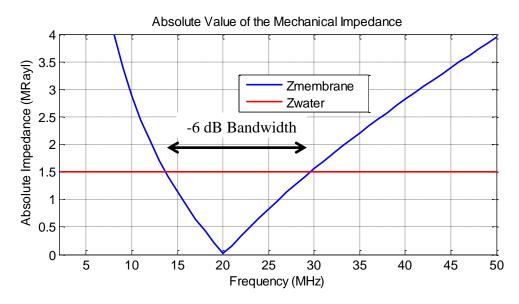

To illustrate, the mechanical mesh in Figure 12 can be evaluated for a simplified CMUT. In this case the impedance of the membrane is modeled as a simple spring and

mass system to produce  $Z_m(f)$  which is equivalent to a band pass filter from a series capacitor and inductor with a resonance is set to 20 MHz which is shown when  $|Z_m| = 0$  in Figure 13. Assuming the CMUT membrane surface is larger in comparison to the wavelength, the impedance of the fluid is assumed to be real and  $Z_f = \rho_0 c_0 = 1.5 \, Mrayls$  for the case of water [34]. The -6 dB pressure bandwidth is calculated from the crossing of  $Z_m(f)$  with  $Z_f$  which is approximately 14 MHz to 29 MHz as shown in Figure 13 for a 70% fractional bandwidth (FBW).

Figure 13. Mechanical mesh impedance analysis of a simple parallel plate CMUT with a spring constant, K, and mass, m, in comparison to water.

Unfortunately, CMUTs suffer in the performance area when evaluating the peak output pressure as compared to their piezoelectric counterparts. For the CMUT, the maximum membrane displacement is physically limited to the fabricated vacuum gap, and the peak pressure is proportional to the displacement. For a simplified piston type transducer with uniform harmonic surface displacement in fluid, the surface pressure can be described by  $P_{surface} = \rho c \pi f u$  where  $\rho$  is the density and c is the speed of sound in fluid, u is the piston displacement, and f is the frequency of operation. From this basic

analysis, is can be observed that the surface pressure is proportional to the frequency of operation, and the transmit pressure for CMUTs designed for low frequency applications, ~ 10 MHz, require 4 x the displacement of a 40 MHz transducer for the same desired output pressure. Certain techniques to improve the pressure in the Tx mode have been shown to be effective through geometric and biasing optimization [27, 31, 35, 36].

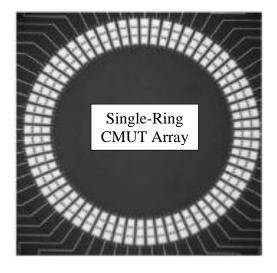

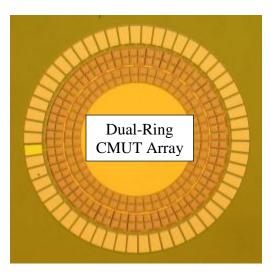

However in general, from the basic analysis, the optimization of the CMUT for receive operation is based on reduction of the vacuum gap, but this reduction reduces the transmit pressure capability. As such, for the ring array design for forward looking applications, it has been proposed that that the single ring can be divided into two separate rings, one for transmit and one for receive as shown in Figure 14. This allows for separate optimization of the Tx/Rx CMUT elements and additionally allows for electrical separation when integrated with electronics.

Although the models used for comparison purposes are simple, ignoring many realistic factors, it provides initial insight. Therefore, a better model is needed to predict the behavior of both Tx and Rx elements.

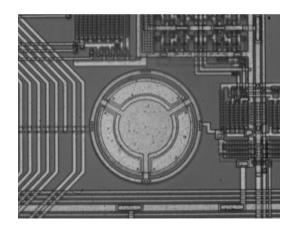

Figure 14. Fabricated CMUT arrays with a single-ring of elements, 1.2 mm outer diameter (left) [37] and dual-ring of elements, 0.8 mm outer diameter (right).

# 2.2. CMUT-Electronics Integration

One of the primary benefits of CMUT technology is the promise of simplified integration with CMOS electronics for improved performance and real estate optimization [38, 39]. By connecting the CMUTs directly to the CMOS electronics, the parasitic capacitance can be significantly reduced to improve the overall SNR, and with front end multiplexing electronics, the number of cables necessary to connect the front end of the catheter to the backside imaging system can be significantly reduced. Further, real estate optimization is extremely important when dealing with forward-looking arrays found on the tip of a catheter. Arrays for side-looking capabilities are not as constrained since they can utilize the lateral dimension, but still require electronics integration for SNR improvement. Multiple integration methods have been proposed and implement with varied strengths and weakness. The following sections describe previous work along with the method of integration developed as part of this dissertation.

### 2.2.1. CMUT-in-CMOS

Processing of the CMUTs can be simultaneously accomplished with the fabrication of electronics utilizing reliable and well-established CMOS processing techniques [40]. Due to the parallel processing, the overall fabrication time and processing costs are reduced. However, the design space for the CMUTs suffers from the limited CMOS fabrication options in terms of material types, material properties, and layer thicknesses. Total device area also increases as the electronics and CMUTs must be positioned side-by-side. Therefore, this is not an ideal scheme for FL-IVUS applications where available space is limited. Figure 15 shows a single CMUT membrane fabricated during the CMOS processing with associated electronics above and to the right [40].

Figure 15. A single CMUT element, center, with surrounding CMOS electronics [40].

### 2.2.2. Interleaved CMUT-CMOS

To improve upon the CMUT design space, it is possible to interrupt the electronics fabrication for outside processing [41, 42]. This method has been utilized to generate smaller gap heights as compared to the aforementioned CMUT-in-CMOS processing. This technique increases cost and fabrication complexity and may experience resistance from commercial CMOS foundries due to contamination concerns. In addition, even though CMUT performance can be improved, this process is still similar to the standard CMUT-in-CMOS technique outlined above, in which available area is not optimally utilized.

## 2.2.3. Flip Chip Bonding

To improve on the utilization of available device area, and to allow for better optimization of CMUT material properties, separately fabricated CMOS and CMUT chips can be electrically connected through flip chip bonding [43-48]. In this case, the CMUTs are not limited to low temperature, CMOS-compatible fabrication processes, nor are they limited to the materials and layer thicknesses designated by standardized foundry processes. However, this interconnect method requires a number of additional fabrication steps that include deep reactive ion etching, conformal metal and dielectric

depositions, backside patterning, and the final wafer bonding step [49]. Furthermore, the packaging techniques associated with this technology are complex in nature adding to the overall cost. This technique is attractive for larger CMUT arrays [50], but may not be ideal for FL-IVUS applications as the minimum solder bump pitch approaches the CMUT element pitch. Figure 16 shows a schematic of a 2D CMUT array which is flip chip bonded to a front-end IC for 3D volumetric imaging [49].

Figure 16. Schematic of a 2D CMUT array bonded to electronics through flip chip bonding methods [49].

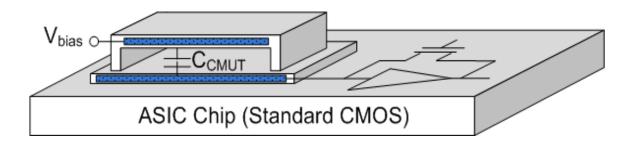

### 2.2.4. CMUT-on-CMOS

To address the real-estate optimization and vacuum gap fabrication flexibility for forward-looking array optimization, a CMUT-on-CMOS process, has been pursued as an integration scheme where the CMUTs are directly fabricated above associated electronics as depicted in

Figure 17. This interconnect approach minimizes parasitic capacitances associated with connection lines while introducing only one additional masking step as will be described in CHAPTER 3. Total occupied area is minimized as the CMUTs can be located over CMOS metal layers, similar to the flip-chip bonding method, but without the complexity and spacing requirements associated with solder bump technology. In addition, the

CMUTs are not constrained by the CMOS processing steps, so it is possible to optimize material properties and produce thinner vacuum gaps for low voltage operation and increased electromechanical coupling efficiency. A drawback to this method is that fabrication is limited to processes under 400 °C so as not to damage the CMOS. However, it has been shown that the performance of CMUTs fabricated with such low temperature PECVD silicon nitride and oxide are not significantly affected.

The main design trade-offs associated with the different CMOS integration approaches is summarized in Table 1. Again, for the design constraints associated with FL-IVUS, this CMUT-on-CMOS fabrication was developed as a good compromise with advantages in optimal space utilization, minimal parasitic capacitances, and relative ease of fabrication and final assembly. Details of this fabrication will be discussed in CHAPTER 3.

Figure 17. A simplified depiction of a CMUT on a CMOS substrate connected to an amplifier.

Table 1. CMUT-CMOS Integration Comparison

|                                       | CMUT-in-CMOS | Interleaved | Flip Chip | CMUT-on-CMOS |

|---------------------------------------|--------------|-------------|-----------|--------------|

| Number of Processing<br>Steps         | +            | +           | •         | -            |

| Active CMUT Area Optimization         | -            | -           | +         | +            |

| Processing<br>Temperature             | n/a          | -           | +         | -            |

| Gap Height Control                    | -            | +           | +         | +            |

| CMUT to CMOS<br>Interconnect Assembly | +            | +           | -         | +            |

| Foundry Compatibility                 | +            | -           | n/a       | n/a          |

# 2.3. Array Design Requirements

The objective of this research is to improve upon the imaging capabilities of IVUS catheters through the use of novel CMUT arrays integrated with CMOS electronics. These CMUT-on-CMOS arrays can be divided into two distinct categories based on the imaging direction, forward-looking and side looking. The requirements for each are unique in terms of operational frequency, array design, electronics, and SNR. A preliminary breakdown of the design objectives will be discussed in this section.

## 2.3.1. FL-IVUS Dual-Ring Array

Forward-looking arrays for generating 3-D forward-looking volumetric images can also be utilized for Doppler blood flow imaging through the investigation of the frequency shift in the received signal as a further assessment tool. In the context of IVUS catheters, the available transducer space is limited to a doughnut shaped region as the guide wire passes through the center, as previously introduced. With such a limited

surface area to work with, fabrication with piezoelectric based transducers becomes increasingly difficult and hence is an ideal candidate for the CMUT-on-CMOS technology.

An experimental forward-looking PZT array for 3-D imaging can be seen in Figure 18 where a rectangular PZT slab was diced and wrapped around a catheter tube with a final outer diameter of 4.3 mm, 13 French [51]. Although too large for many IVUS applications, this is an excellent example of a single-ring array using PZT technology for volumetric imaging.

Duke University 2009 55 Element, 4.6MHz 20% -6dB BW

Figure 18. A single ring PZT based forward looking array [51].

Single-ring CMUT arrays have been previously fabricated as shown in Figure 19-left [37, 52, 53]. These designs work well with the doughnut shaped real estate available, but just as in the PZT array in Figure 18, each element is used for both Tx and Rx operations. For the CMUT, this means that the DC bias used is the same for both Tx and Rx operation and requires protection circuitry for the electronics integration. This additional circuitry increases the complexity of the electronics and the noise in the system. Figure 19-right shows a previously proposed integration scheme where the

CMUT array on the front of the catheter is connected to associated electronics on the sides via wire bonding.

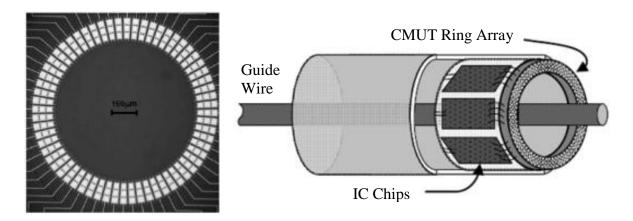

Figure 19. A fabricated single-ring CMUT array (left) and a diagram of a catheter with a single-ring array for forward-looking imaging with guide wire (right).

Dual-ring CMUT arrays have also been fabricated, Figure 20, to improve upon the single-ring CMUT design [29, 54]. With two rings of CMUTs, the Tx and Rx elements can be separated and optimized independently. For example, the vacuum gaps for the Rx elements can be minimized to increase the transformer ratio and increased for the Tx elements as necessary to allow for sufficient membrane displacement and corresponding Tx pressure. With this dual-ring design, there is a small loss in resolution from the reduced inside diameter, but with separate Tx-Rx elements, protection circuitry is no longer required which also reduces the associated noise from such circuitry. This in turn allows for easier CMOS integration as the Rx elements can be directly connected to amplifiers and Tx elements can be directly connected to pulser circuitry.

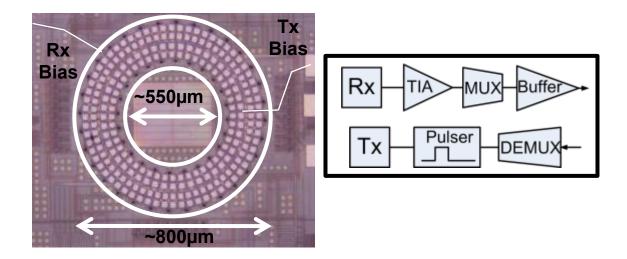

Figure 20. A fabricated dual-ring CMUT design with separate Tx and Rx bias capabilites (left) and flow chart for Tx-Rx integration with electronics (right).

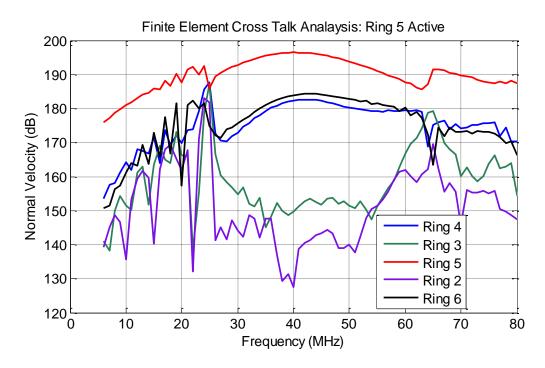

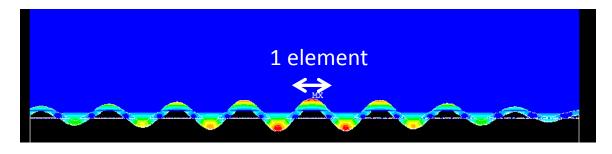

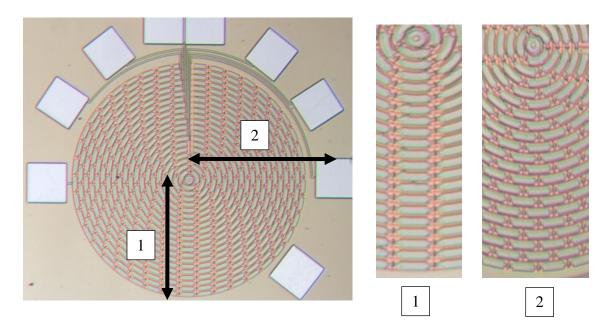

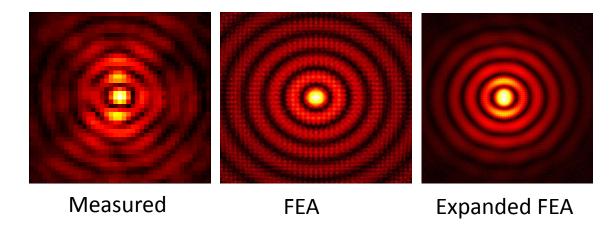

# 2.3.2. <u>SL-IVUS Annular Ring Arrays</u>