# **Polymer Ferroelectric Memory for Flexible Electronics**

Dissertation by

Mohd Adnan Khan

In Partial Fulfillment of the Requirements

For the Degree of

**Doctor of Philosophy**

King Abdullah University of Science and Technology

Thuwal, Kingdom of Saudi Arabia

November, 2013

The dissertation of Mohd Adnan Khan is approved by the examination committee.

| Boon Ooi              |           |      |

|-----------------------|-----------|------|

| Committee Member      | Signature | Date |

| Aram Amassian         |           |      |

| Committee Member      | Signature | Date |

| Pierre M. Beaujuge    |           |      |

| Committee Member      | Signature | Date |

| Udo Schwingenschloegl |           |      |

| Committee Member      | Signature | Date |

| Husam Alshareef       |           |      |

| Committee Chair       | Signature | Date |

© November-2013

Mohd Adnan Khan

All Rights Reserved

#### **ABSTRACT**

### Polymer Ferroelectric memory for Flexible Electronics

#### Mohd Adnan Khan

With the projected growth of the flexible and plastic electronics industry, there is renewed interest in the research community to develop high performance all-polymeric memory which will be an essential component of any electronic circuit. Some of the efforts in polymer memories are based on different mechanisms such as filamentary conduction, charge trapping effects, dipole alignment, and reduction-oxidation to name a few. Among these the leading candidate are those based on the mechanism of ferroelectricity. Polymer ferroelectric memory can be used in niche applications like smart cards, RFID tags, sensors etc. This dissertation will focus on novel material and device engineering to fabricate high performance low temperature polymeric ferroelectric memory for flexible electronics. We address and find solutions to some fundamental problems affecting all polymer ferroelectric memory like high coercive fields, fatigue and thermal stability issues, poor breakdown strength and poor p-type hole mobilities. Some of the strategies adopted in this dissertation are: Use of different flexible substrates, electrode engineering to improve charge injection and fatigue properties of ferroelectric polymers, large area ink jet printing of ferroelectric memory devices, use of polymer blends to improve insulating properties of ferroelectric polymers and use of oxide semiconductors to fabricate high mobility p-type ferroelectric memory. During the course of this dissertation we have fabricated: the first all-polymer ferroelectric capacitors with solvent modified highly conducting polymeric poly(3,4-ethylenedioxythiophene)-poly(styrenesulfonate) [PEDOT:PSS] electrodes on plastic substrates with performance as good as devices with metallic Platinum-Gold electrodes on silicon substrates; the first all-polymer high performance ferroelectric memory on banknotes for security applications; novel ferroelectric capacitors based on blends of ferroelectric poly(vinylidene fluoride trifluoroethylene) [P(VDF-TrFE)] and highly insulating dielectric poly(p-phenylene oxide) [PPO] with drastically improved fatigue and thermal stability; novel all-polymer ferroelectric diodes based on blends of ferroelectric [P(VDF-TrFE)] and n-type semiconducting [6,6]-phenyl-C61-butyric acid methyl ester [PCBM] with resistive switching properties and the first hybrid p-type ferroelectric memory with transparent tin monoxide [SnO] on plastic substrates with record mobilities.

#### **ACKNOWLEDGEMENTS**

I would like to take this opportunity to express sincere appreciation to all the people who have supported me through the entire PhD study.

Firstly I would like to dedicate this dissertation to my father, Shamsuddin Khan who has been a pillar of strength for me over the years with all his love, support, encouragement and advice. Also would like to thank my entire family for their patience, love and prayers during my tough times. Also a special thanks to my beautiful and loving wife for her patience and understanding of my second love i.e. my PhD research.

Most importantly I want to express gratitude to my advisor Prof. Husam Alshareef for his support of my PhD study, for his patience, motivation, enthusiasm, and immense knowledge. He has been an advisor, friend and a mentor to me who never put pressure on me during the entire PhD. I could not have imagined having a better advisor and mentor and can only say "Thank You". Next I would like to thank my post-doc, friend and therapist Dr. Unnat Bhansali for teaching me everything I know now. Thank you for making this PhD so much fun and your support and advice during the frustrating times. I would also like to thank all my professors, committee members and research scientists at KAUST for their technical help and advice. A special thanks also goes to Dr. Ihab Odeh and Mahmoud Almadhoun at SABIC-CRI for their support and advice. Last but not least my appreciation also goes to all my colleagues and friends for making my time at "King Abdullah University of Science and Technology" a great experience.

### TABLE OF CONTENTS

| ABSTRACT                                                                                                    | 4   |

|-------------------------------------------------------------------------------------------------------------|-----|

| ACKNOWLEDGEMENTS                                                                                            | 6   |

| LIST OF ABBREVIATIONS                                                                                       | 8   |

| LIST OF ILLUSTRATIONS                                                                                       | 9   |

| LIST OF TABLES                                                                                              | 17  |

| INTRODUCTION                                                                                                | 18  |

| Fabrication and Characterization of All Polymer Flexible and Transparent Ferroelectric Capacitors           | 53  |

| Series Resistance Effects of High Performance Polymer Ferroelectric Capacitors                              | 65  |

| Large Area Ink-Jet Printed All Polymer Ferroelectric Memory                                                 | 81  |

| Characterization of Current Transport in Polymer Ferroelectric Devices                                      | 95  |

| Electrodes Engineering to Fabricate Fatigue Free Polymeric Ferroelectric Memory                             | 110 |

| High Performance Non-Volatile Ferroelectric Memory on Banknotes                                             | 123 |

| All Polymer Memory Based on Phase Separated Ferroelectric-Fullerene Blends with Resistiv Switching Behavior |     |

| High Performance Ferroelectric Memory Based on Phase Separated PPO Blends                                   | 163 |

| High Performance Low Temperature Flexible Single and Dual Gate Hybrid p-type Ferroelect<br>Memory           |     |

| Summary of Dissertation                                                                                     | 212 |

| LIST OF PUBLICATIONS                                                                                        | 215 |

| LIST OF PATENTS                                                                                             | 216 |

#### LIST OF ABBREVIATIONS

### (Entries are listed alphabetically)

AFM Atomic Force Microscopy

DMSO Dimethyl sulfoxide

DMF Dimethyl Formamide

DFT Density Functional theory

FeFET Ferroelectric field effect transistor

IC Integrated circuit

MEK Methyl-Ethyl-Ketone

PPO poly(p-phenylene oxide)

PVDF poly(vinylidene difluoride)

P(VDF-TrFE) poly[(vinylidene-difluoride-trifluoroethylene]

PEDOT:PSS poly (3,4-ethylenedioxythiophene)-poly(styrenesulfonate)

RFID Radio Frequency Identification

SEM Scanning Electron Microscopy

TEM Transmission Electron Microscopy

TFT Thin film transistor

WORM Write Once Read many

XRD X-ray diffraction

# LIST OF ILLUSTRATIONS

| Figure. 1.1. (a) Projected growth for flexible electronics market. (b) Projected market share of different technologies in flexible electronics by 2020. [1]                                                                                                                                                                                        |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Figure. 1.2 (a) Roll to roll processing on plastic substrates (b) Large area printed, flexible polymeric circuits for RFID application [2]                                                                                                                                                                                                          |

| Figure. 1.3 Classification of different types of memory [2]                                                                                                                                                                                                                                                                                         |

| Figure. 1.4 (a) Polarization loop in a normal dielectric (b) Polarization (Hysteresis) loop in a ferroelectric dielectric [5]                                                                                                                                                                                                                       |

| Figure. 1.5 (a) Chemical Structure of PVDF monomer (b) Molecular configuration in PVDF (Fluorine atoms in Red and Hydrogen in Yellow and Carbon in Blue) [4]                                                                                                                                                                                        |

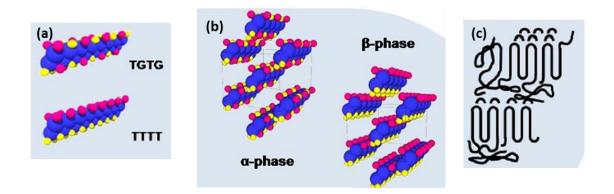

| Figure. 1.6 (a) Conformation like TFTG and TTTT in ferroelectric polymers. (b) Different packing modes leads to different crystalline structures like the $\alpha$ and $\beta$ phase (c) Typical nature of a semicrystalline polymer with crystalline and amorphous regions. (Fluorine atoms in Red and Hydrogen in Yellow and Carbon in Blue) [4]. |

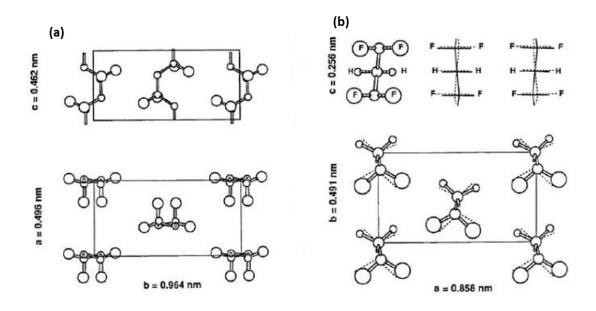

| Figure. 1.7 (a) $\alpha$ phase of PVDF (b) $\beta$ phase of PVDF. [5]                                                                                                                                                                                                                                                                               |

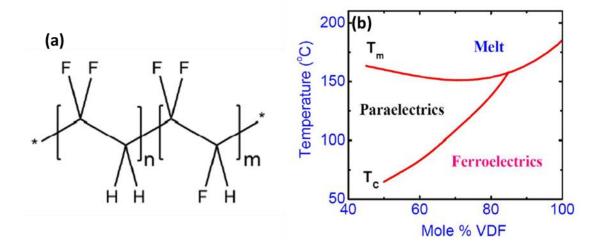

| Figure. 1.8 (a) Chemical structure of P(VDF-TrFE) (b) Phase diagram of P(VDF-TrFE) [6]29                                                                                                                                                                                                                                                            |

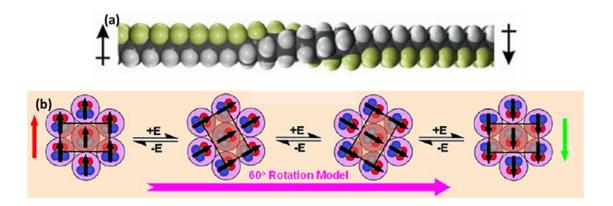

| Figure. 1.9 (a) Illustration of the dipole switching in PVDF. (b) Dipole switching of fluorine-hydrogen dipoles based on 60° rotation model [2, 3]                                                                                                                                                                                                  |

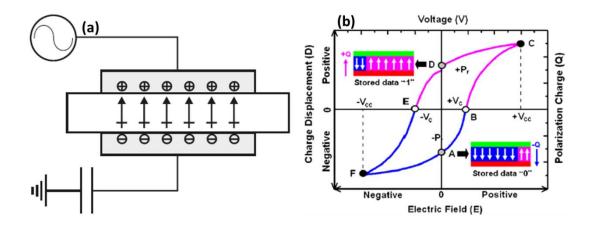

| Figure. 1.10 (a) Sawyer-Tower circuit to measure polarization hysteresis in a ferroelectric capacitor (b) Polarization or Charge displacement versus Electric field curved for a typica ferroelectric capacitor [2,7].                                                                                                                              |

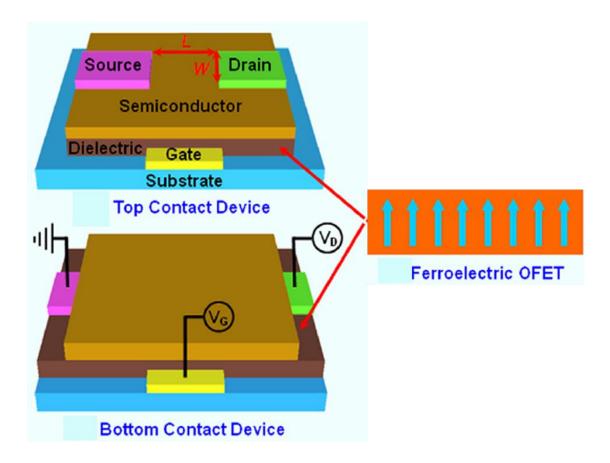

| Figure. 1.11. OTFT in top and bottom contact configuration. If a ferroelectric polymer is used as the gate dielectric then it becomes a Ferroelectric Field Effect Transistor (FeFET) [2]36                                                                                                                                                         |

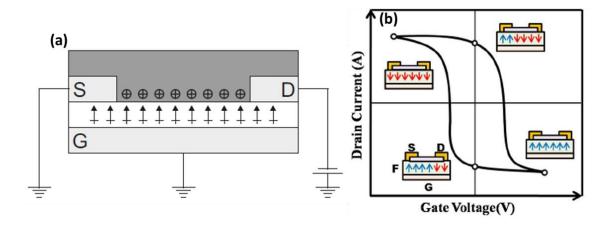

| Figure. 1.12 (a) Layout of typical thin film transistor showing source, drain and gate contacts. (b) $I_d$ - $V_g$ characteristics of a FeFET                                                                                                                                                                                                       |

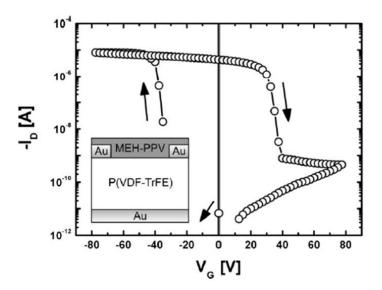

| Figure. 1.13 (a) Transfer curve ( $I_d$ - $V_G$ ) of the first FeFET with a polymeric semiconductor (MEH-                                                                                                                                                                                                                                           |

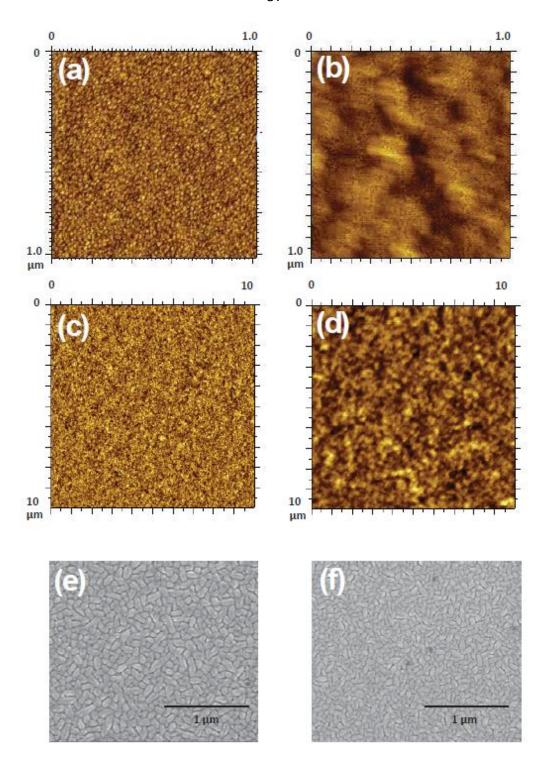

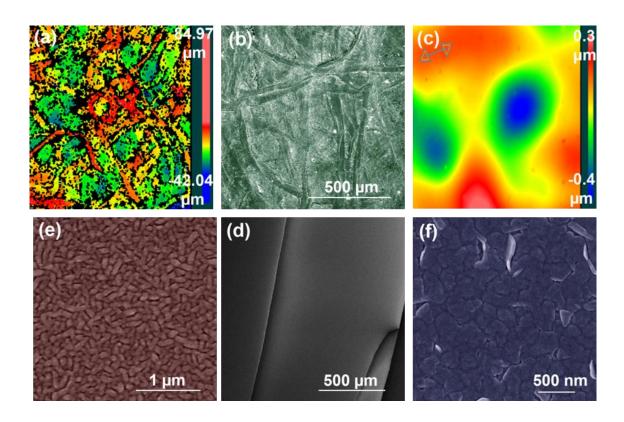

| Figure. 2.1 AFM topography images of (a) Pt surface (b) PEDOT:PSS surface (c) P(VDF-TrFE) grown on Pt surface (d) P(VDF-TrFE) grown on PEDOT:PSS surface. SEM images of (e) P(VDF-TrFE) grown on Pt surface (f) P(VDF-TrFE) grown on PEDOT:PSS surface                                                                                                                                                                                                                                                                                                               |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

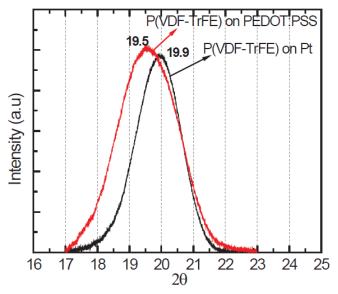

| Figure. 2.2 Grazing Incidence XRD spectra of P(VDF-TrFE) films on Pt and PEDOT:PSS electrodes.                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

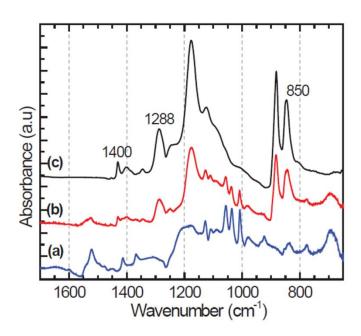

| Figure. 2.3 p polarized FT-IR spectra of (a) spin coated PEDOT:PSS b) P(VDF-TrFE) film (~110±10 nm) on PEDOT:PSS and (c) P(VDF-TrFE) film on a Pt substrate                                                                                                                                                                                                                                                                                                                                                                                                          |

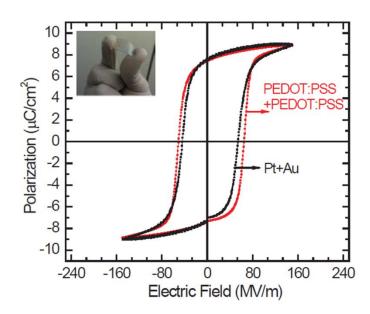

| Figure. 2.4 Hysteresis loops at a frequency of 1 Hz and Electric Field of 150 MV/m from devices with Platinum/Gold electrodes and with PEDOT:PSS top and bottom electrodes                                                                                                                                                                                                                                                                                                                                                                                           |

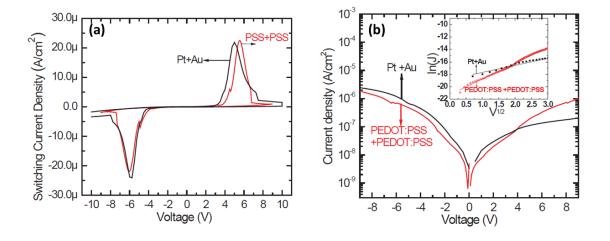

| Figure. 2.5 (a) Switching current response from devices with Platinum/ Gold electrodes and with PEDOT:PSS top and bottom electrodes (b) I-V characteristics of devices with Platinum/Gold electrodes and PEDOT:PSS electrodes. The inset shows a plot of Current density versus Voltage <sup>0.5</sup> measured at room temperature                                                                                                                                                                                                                                  |

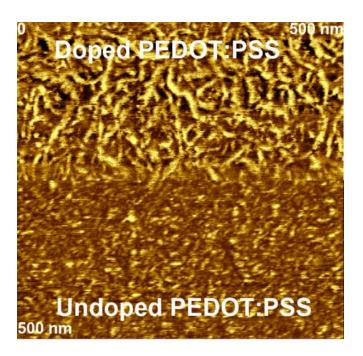

| Figure. 3.1 AFM phase image of a 0.5 x 0.5 $\mu m^2$ area with top half showing morphology of doped PEDOT:PSS and bottom half of undoped PEDOT:PSS film                                                                                                                                                                                                                                                                                                                                                                                                              |

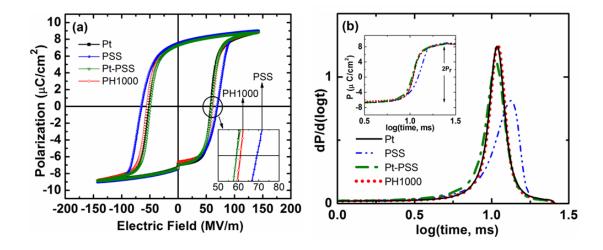

| Figure. 3.2 (a) Polarization (P) vs Electric Field (E) hysteresis loop measurements at a frequency of 10 Hz. Inset shows a magnified image of coercive fields for devices with different bottom electrodes i.e. (b) Switching characteristics for ferroelectric capacitors at 120 MV/m, with peak of dP/d(log t) vs. log t representing respective switching times. Inset shows a switching event with sharp increase in polarization at corresponding switching times                                                                                               |

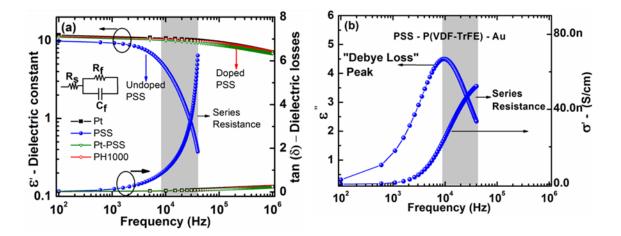

| Figure. 3.3 (a) Dielectric spectroscopy study with dielectric constant (left axis) and dielectric losses (right axis) for all the devices studied. Equivalent circuit model is represented in the inset where $R_s$ is series resistance from electrodes, $R_f$ and $C_f$ is resistance and capacitance of dielectric film, respectively. (b) Imaginary part of the complex permittivity ( $\epsilon$ ") (left axis) indicating a "debye-loss" peak at ~ 7 kHz and conductivity ( $\sigma$ ') (right axis) of the ferroelectric co-polymer with increasing frequency |

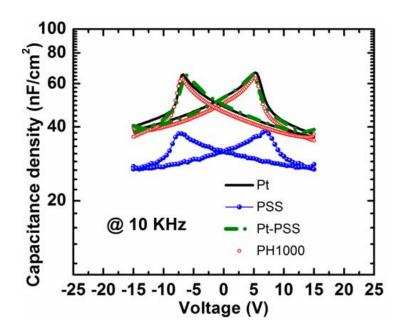

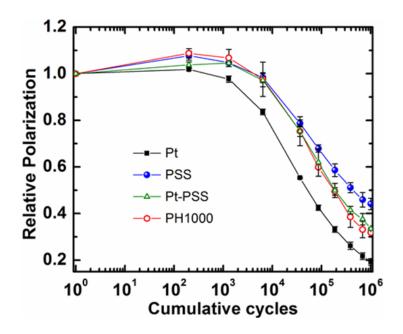

| Figure. 3.4 Capacitance density plotted as a function of voltage from -15 to +15 V for different electrodes. The C-V ("butterfly") curves were measured at 10 kHz                                                                                                                                                                                                                                                                                                                                                                                                    |

| Figure. 3.5 Electrical fatigue properties showing relative polarization of P(VDF-TrFE) films stressed at 80 MV/m and a frequency of 100 Hz. The PUND measurements were done at saturation fields of 125 MV/m                                                                                                                                                                                                                                                                                                                                                         |

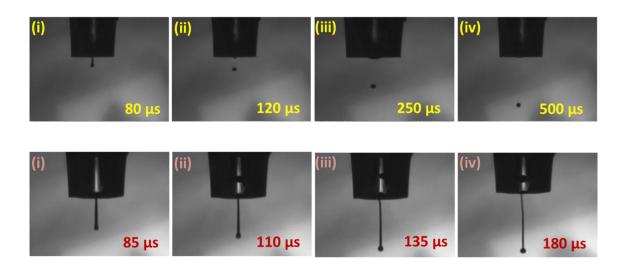

| Figure. 4.1 Stroboscopic in-flight images of: PEDOT:PSS single-drop formation and release (top) and tail elongation of P(VDF-TrFE) and no break-off even after 180 μs85                                                                                                                                                                                                                                                                                                                                                                                                    |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

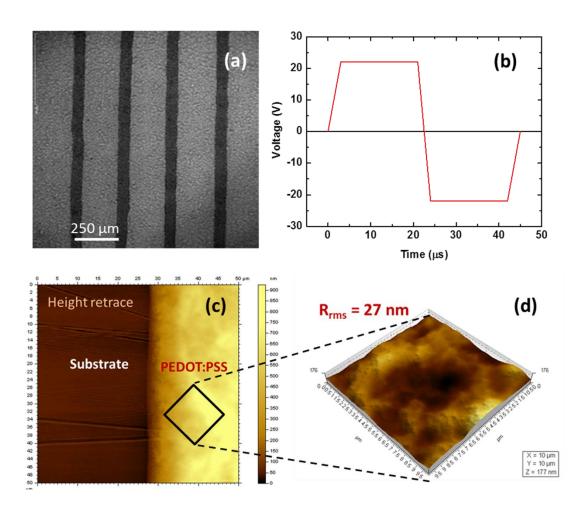

| Figure. 4.2 (a) An optical microscope image of the printed PEDOT:PSS lines on plastic substrate. The pitch spacing is set at 250 $\mu$ m. (b) A typical voltage pulse applied to the piezoelectric print head for stable ejection of PEDOT:PSS ink. (c) Height retrace AFM image showing the PEDOT:PSS line edge and (d) surface morphology of printed PEDOT:PSS features showing a roughness ( $R_{rms}$ ) $\sim$ 27 nm. The scan area is 10 $\mu$ m x 10 $\mu$ m.                                                                                                        |

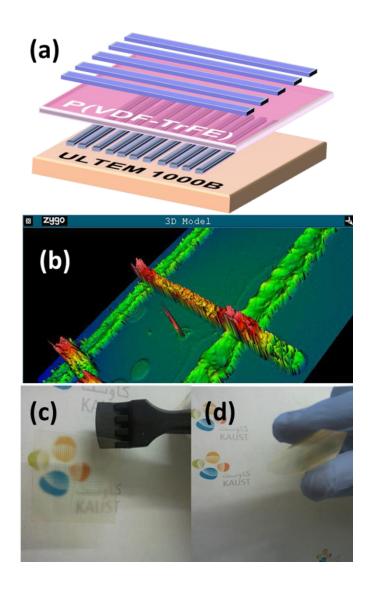

| Figure. 4.3 (a) Schematic of the device structure showing a transparent substrate, orthogonal lines of inkjet-printed PEDOT:PSS and a spin-cast P(VDF-TrFE) layer, (b) a white light interferometry image of the device showing the concave profile of the inkjet-printed PEDOT:PSS lines. Photographs of the actual device on ULTEM 1000B where the transparency and flexibility can be discerned in (c) and (d), respectively.                                                                                                                                           |

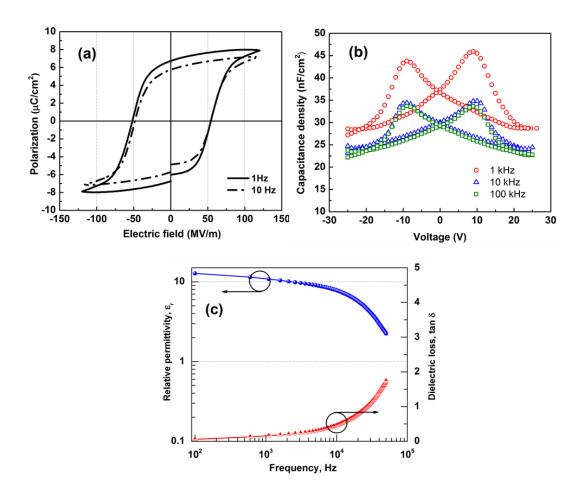

| Figure. 4.4 (a) Hysteresis loops of ferroelectric capacitors measured at 1 Hz and 10 Hz under an electric field of 120 MV/m (b) Capacitance - Voltage curves measured for frequencies upto 100 kHz and (c) dielectric constant (left axis) and dielectric losses (right axis) measured at room temperature from 100 Hz to 50 kHz.                                                                                                                                                                                                                                          |

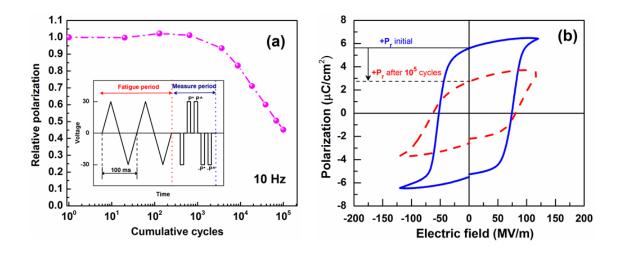

| Figure. 4.5 (a) Normalized fatigue behavior for inkjet-printed PEDOT:PSS electrode capacitors showing dP (= $P^*$ – $P^*$ ) vs. frequency, where $P^*$ is the (remanent + non-remanent polarization) and $P^*$ is the non-remanent polarization from a PUND measurement. The devices were stressed at a switching frequency of 10 Hz and 120 MV/m. Inset shows the voltage profile and the measurement protocol used for this study and (b) a comparison of hysteresis curves before and after electrical fatigue, indicating that $P_r$ drops to 45% of the initial value |

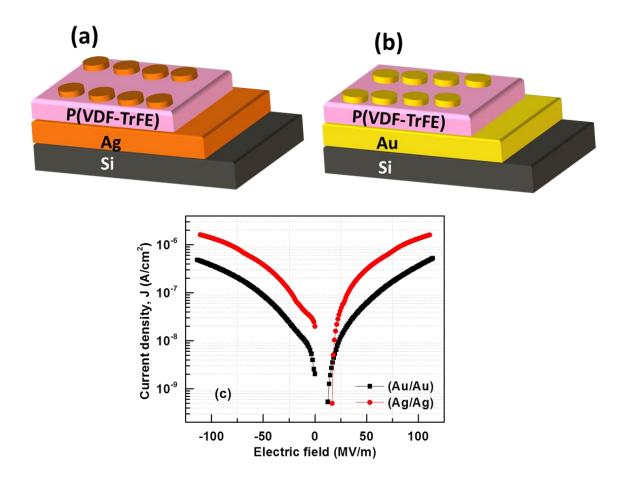

| Figure. 5.1 A schematic of devices with symmetric electrodes, (a) Ag and (b) Au, as top and bottom metal contacts to P(VDF-TrFE) used for this study and (c) J-E curves for metal-ferroelectric-metal structures with Ag and Au top/bottom electrodes                                                                                                                                                                                                                                                                                                                      |

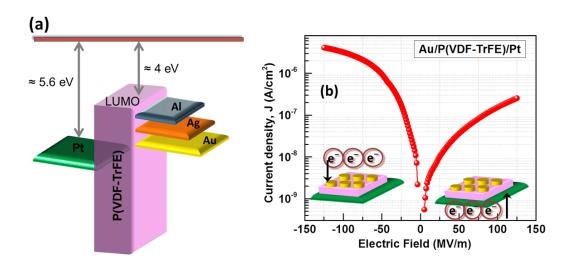

| Figure. 5.2 (a) Proposed band diagram with the P(VDF-TrFE) energy levels and the work functions of metals used in this study w.r.t. vacuum. (b) Typical J-E plot of a Au/P(VDF-TrFE)/Pt device showing higher leakage when injecting electrons from Au (negative bias) compared to Pt (positive bias). The insets show the direction of electron injection corresponding to the polarity.                                                                                                                                                                                  |

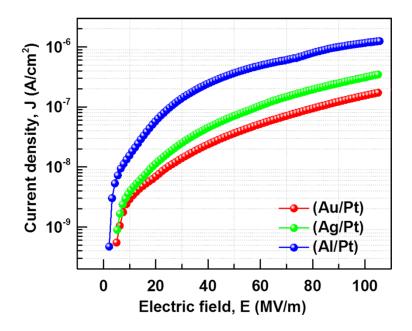

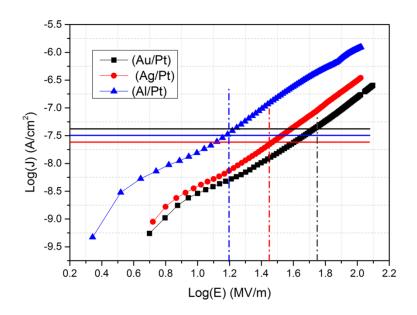

| Figure. 5.3 J-E plots for asymmetric devices showing highest leakage current for Al/(P(VDF)-TrFF)/Pt compared to Ag/(P(VDF)-TrFF)/Pt and Au/(P(VDF)-TrFF)/Pt                                                                                                                                                                                                                                                                                                                                                                                                               |

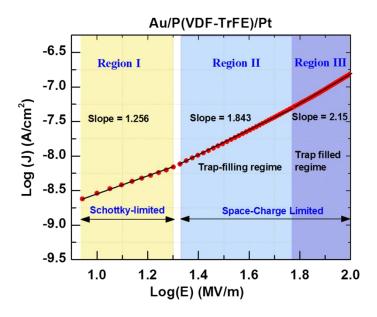

| Figure. 5.4 A log-log plot of the J-E curve for Au/(P(VDF)-TrFE)/Pt device. Three regions with distinct slopes indicating different transport mechanisms are depicted. The slope values are calculated from a linear fit to the J-E curve and the adjusted R2 values are $> 0.993$ 102                                                                                                                                                            |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

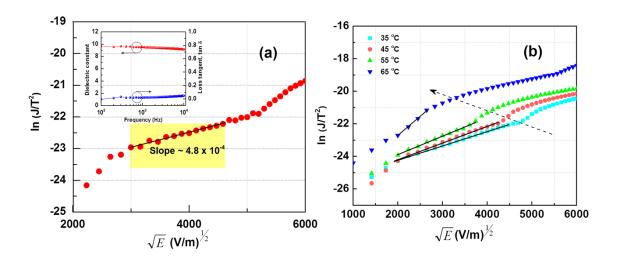

| Figure. 5.5 (a) A plot of In J/T <sup>2</sup> vs. VE for a Au/(P(VDF)-TrFE)/Pt device measured at room temperature. Inset shows the measured experimental relative permittivity and dielectric losses as a function of frequency. (b) Temperature dependent current-voltage dependence of Au/P(VDF-TrFE)/Pt device from T=25 - 65 °C. The direction of the arrow indicates a reducing electric field for the onset of the SCLC transport behavior |

| Figure. 5.6 Log (J) vs. Log (E) plots for Au/P(VDF-TrFE)/Pt, Ag/(P(VDF-TrFE)/Pt and Al/(P(VDF-TrFE)/Pt devices. The field values at which the slope of the J-E curve is $\geq$ 2 are marked as x-axis intercepts and the current density $\approx 3\times10^{-8}$ A/cm <sup>2</sup> , indicating bulk-limited SCLC transport 106                                                                                                                  |

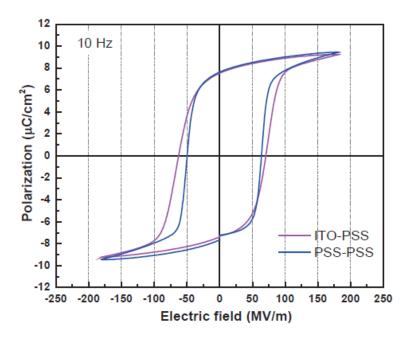

| Figure. 6.1 Polarization-Electric field (P-E) hysteresis curves measured at ± 15V and 10 Hz. The device structures are PEN/ITO/P(VDF-TrFE)/PEDOT:PSS and PEN/PEDOT:PSS/P(VDF-TrFE)/PEDOT:PSS                                                                                                                                                                                                                                                      |

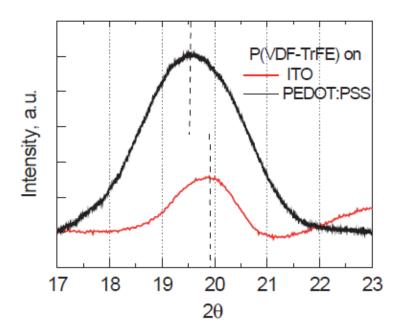

| Figure. 6.2 Grazing Incidence X Ray Diffraction spectra for 100 nm P(VDF-TrFE) films grown on ITO and PEDOT:PSS. The incidence angle was set at 0.5°                                                                                                                                                                                                                                                                                              |

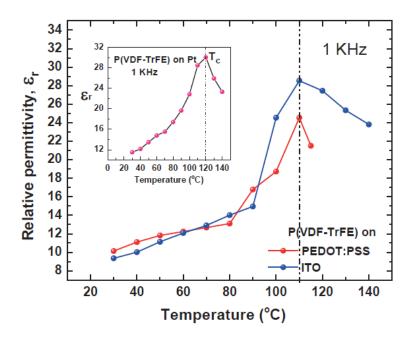

| Figure. 6.3 Temperature characteristics of dielectric constant of P(VDF-TrFE) films on ITO and PEDOT:PSS measured at 1 KHz. Inset shows a higher Curie transition (T <sub>c</sub> ) temperature of P(VDF-TrFE) on Pt                                                                                                                                                                                                                              |

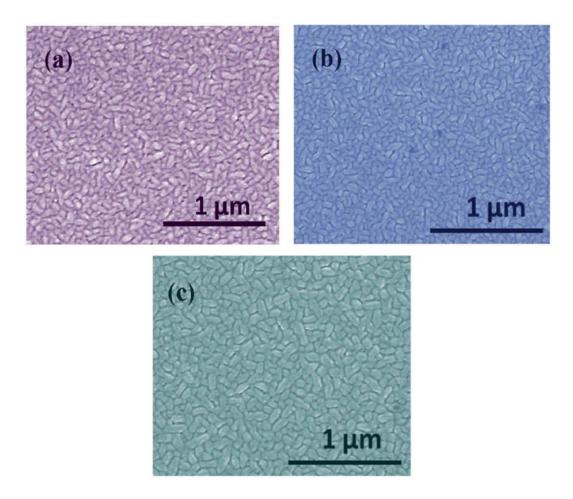

| Figure. 6.4 SEM images of P(VDF-TrFE) grown on (a) ITO, (b) PEDOT:PSS and (c) Pt substrate 116                                                                                                                                                                                                                                                                                                                                                    |

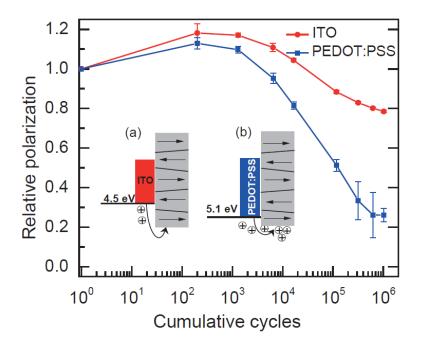

| Figure. 6.5 Normalized fatigue behavior for ITO and PEDOT:PSS bottom electrode capacitors showing dP (=P*- P^) vs. frequency, where P* is the (remanent + non-remanent polarization) and P^ is the non-remanent polarization from a PUND measurement. The devices were stressed at a switching frequency of 100 Hz. Insets (a) and (b) illustrate the charge injection mechanism in oxide and polymer electrodes                                  |

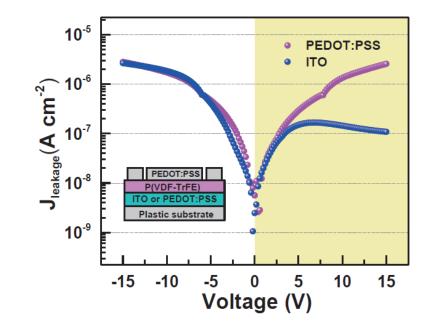

| Figure. 6.6 A comparison of J-V (leakage current density vs. voltage) characteristics of ferroelectric capacitors; ITO/P(VDF-TrFE)/PEDOT:PSS and PEDOT:PSS/P(VDF-TrFE)/PEDOT:PSS. The bottom electrode was swept from -15 V to +15 V while the top electrode was at 0 V. Inset shows the device cross-section on a plastic substrate                                                                                                              |

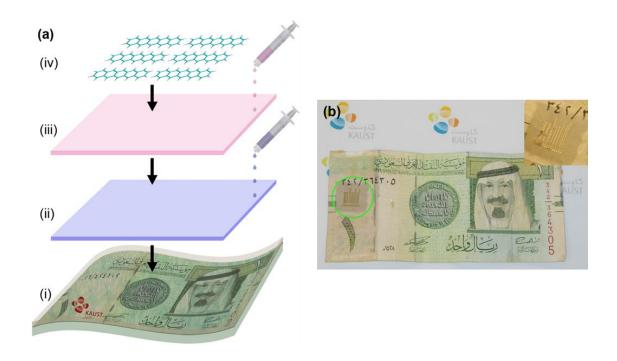

| Figure. 7.1 (a) Fabrication of polymer ferroelectric memory devices on banknotes :(i) PDMS coated banknote (ii) spin-coating PEDOT:PSS bottom electrodes (iii) spin-coating P(VDF-TrFE)                                                                                                                                                                                                                                                           |

ferrolectric layer ~ 140 nm (iv) thermally evaporated pentacene thin film (~60 nm) and (b)

Photograph of a 1-Saudi Riyal note covered with arrays of polymer ferroelectric memory

| devices                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Figure. 7.2 3D surface profiles of untreated and PDMS coated banknote (a & c) and their corresponding SEM images (b & d). Top view SEM images of P(VDF-TrFE) grains grown or PEDOT:PSS electrodes (e) and pentacene grains grown on P(VDF-TrFE) (f). 10 μm x 10 μm 3-E AFM images of P(VDF-TrFE)grown on PEDOT:PSS and Pt (g) and (h), respectively                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

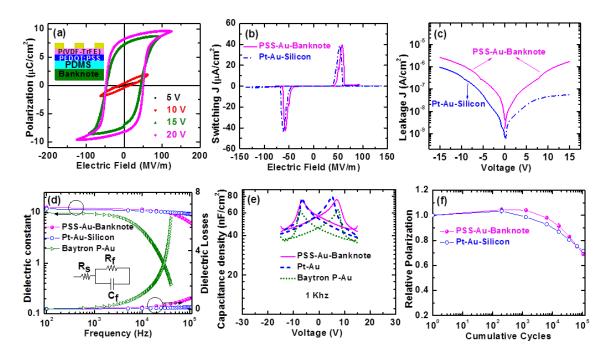

| Figure. 7.3 (a) Hysteresis curves measured at different fields at 1 Hz for devices on banknotes Inset shows the device cross-section. (b) Switching current density versus electric field for devices on banknotes and Pt coated silicon substrates (c) J-V curves showing leakage current measured from –15 to +15 V. (d) Dielectric spectroscopy study with dielectric constant (left axis and dielectric losses (right axis) for poorly conducting PEDOT:PSS (Baytron P), highly conducting PEDOT: PSS (PSS) and Pt electrodes. Equivalent circuit model is represented in the inset where R is series resistance from electrodes, R <sub>f</sub> and C <sub>f</sub> is resistance and capacitance of the film respectively. (e) Capacitance –Voltage (Buttefly loops) at 1 KHz and reverse voltage sweep from –15 to +15 V. (f) Fatigue performance of capacitors at 100 Hz and stressed at 15 V for 100,000 cycles. |

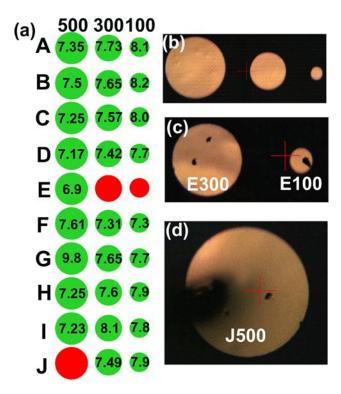

| Figure. 7.4 (a) Schematic of device layout on banknotes with different diameters of 500, 300 and 100 μm (left to right). (b) Optical microscope images of working devices. (c) and (d) defects and irregularities in non-functional devices E300, E100 and J500                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

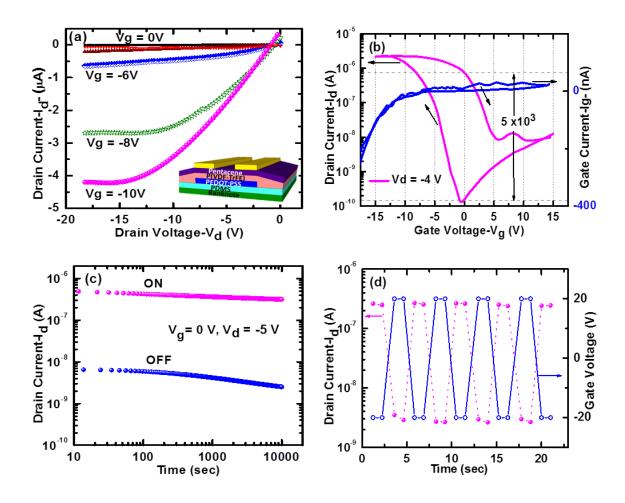

| Figure. 7.5 (a) Source-drain ( $I_d$ - $V_d$ ) characteristics of a p-channel transistor on banknote with W/I ratio = 1000/60. Inset shows the device cross section. (b) Transfer characteristics ( $I_d$ - $V_g$ ) [left axis] and gate current ( $I_g$ - $V_g$ ) [right axis] of FeFETs on banknote measured at $V_d$ = -4V. (c Retention characteristics of FeFETs measured at $V_g$ = 0 V and $V_d$ = -5 V. A 3 sec. gate voltage pulse of -20 V and +20 V was applied to turn the transistor ON or OFF before the test. (d) Dynamic retention (Id versus time) plot obtained using a pulse width of 1 sec at $V_d$ = -5 V 136                                                                                                                                                                                                                                                                                       |

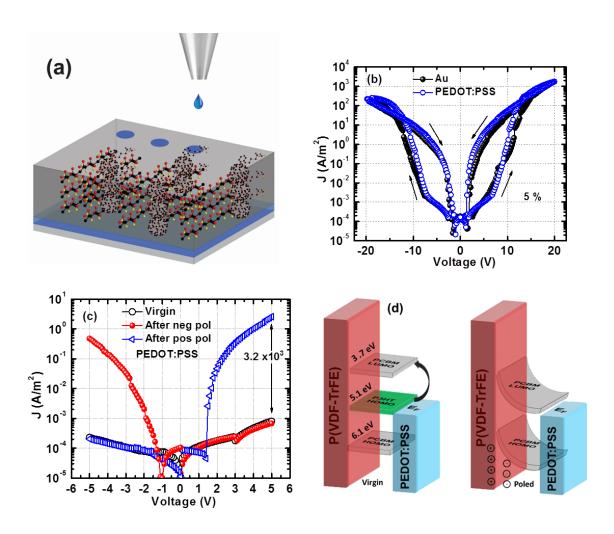

| Figure. 8.1 (a) Schematic 3-D cross section of all polymer memory devices with phase separated network of P(VDF-TrFE) and PCBM polymers. PEDOT:PSS was ink-jet printed as the top electrode. (b) Current density (J) –Voltage (V) sweeps of P(VDF-TrFE)-PCBM blend (95:5) devices with Au and PEDOT:PSS electrodes showing resistive memory behavior. (c) J-V memory performance of virgin polymer P(VDF-TrFE)-PCBM blends (95:5) and after positive and negative poling. (d) Band diagram at the interface between PCBM phase and bottom PEDOT:PSS electrode for virgin and poled devices.                                                                                                                                                                                                                                                                                                                              |

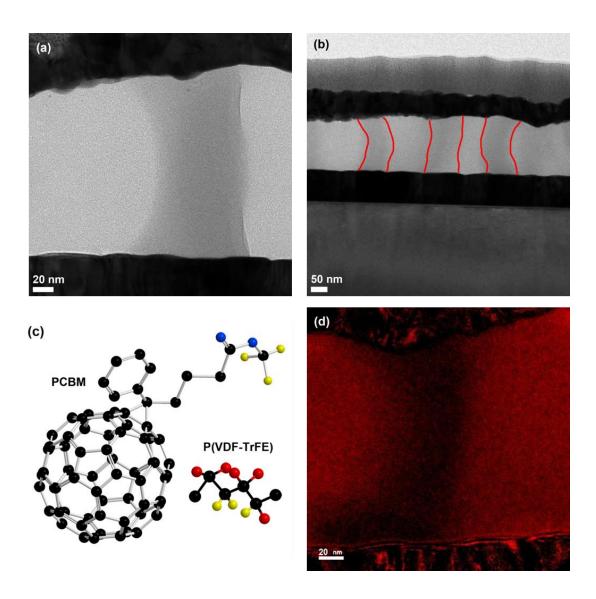

| Figure. 8.2 (a) Cross section TEM showing nano-scale phase separated PCBM continuous                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

between the gold electrodes (b) Cross section TEM showing multiple phase-separated PCBM columns throughout the thin film with an average domain width of  $\sim$  80 nm. The red lines are a

| visual aid for delineation of the PCBM phase in the PVDF TrFE matrix. (c) Molecular structures of semiconducting PCBM (left) and ferroelectric P(VDF-TrFE) (right). (d) X-ray elemental mapping of the polymer blend film using EFTEM showing the fluorine (red) in the P(VDF-TrFE) phase 153                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

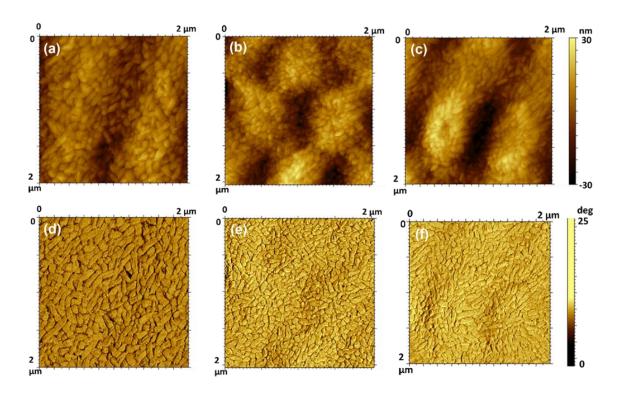

| Figure. 8.3 AFM images showing topography (a,b,c) and phase (d,e,f) images of a blend with 0 wt %. 5 wt % and 10 wt% PCBM respectively. Surface roughness ( $R_{rms}$ ) $^{\sim}$ 6.9, 7.94 and 11.5 nm for 0, 5 and 10 wt% PCBM films                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

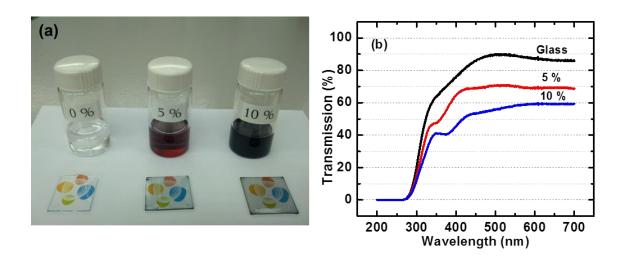

| Figure. 8.4 (a) Photographs of the all-polymer transparent non-volatile resistive memory fabricated on glass substrates. The corresponding solutions with 0 wt%, 5 wt% and 10 wt% PCBM (Left to Right) showing a homogenous solution. (b) UV-Vis transmission spectra for devices with 5 wt% and 10 wt% PCBM blend films                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

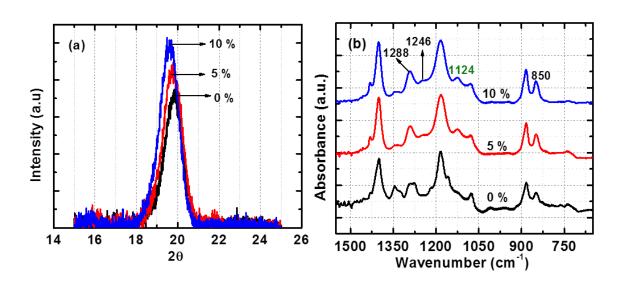

| Figure. 8.5 (a) Grazing incidence XRD spectra for pure ferroelectric P(VDF-TrFE) and blend films with 5 wt% and 10 wt% PCBM. (b) FT-IR spectra of pure ferroelectric P(VDF-TrFE) and 5 wt% and 10 wt% PCBM blend thin flms                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

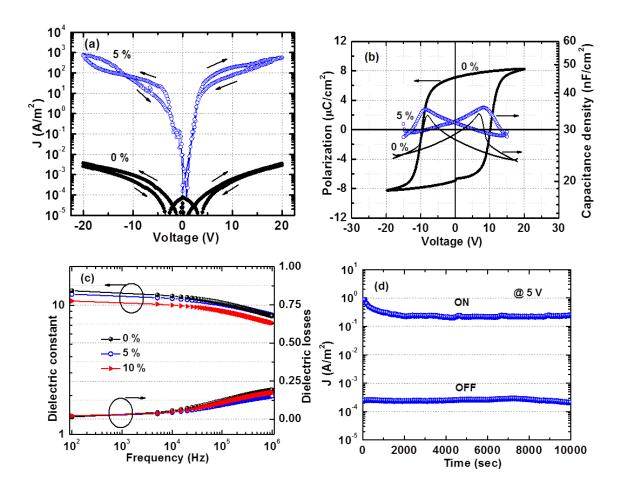

| Figure. 8.6 (a) Current density (J)- Voltage (V) characteristics of 200 nm pure P(VDF-TrFE) films showing no current hysteresis. Un-annealed 5 wt % polymer blend films show an increase in current by 5 orders but no memory behavior. (b) Polarization-Voltage Hysteresis curve for 200 nm pure ferroelectric films at 10 Hz (Left Axis). Small signal Capacitance –Voltage (Butterfly loops) at (100 mV,1 MHz) for pure P(VDF-TrFE) films and blends with 5 wt% PCBM (Right axis) (c) Dielectric spectroscopy study with dielectric constant (left axis) and dielectric losses (right axis) for pure ferroelectric P(VDF-TrFE) (0 wt% PCBM) and polymer blend films with 5 wt% and 10 wt% PCBM content. (d) Retention characteristics of non-volatile resistive memory with 5 wt% PCBM measured at $V = +5 V$ showing an ON/OFF ratio of $\sim 10^3$ . A voltage pulse of $+20 V$ and $-20 V$ was applied to turn the device ON or OFF, respectively before the test |

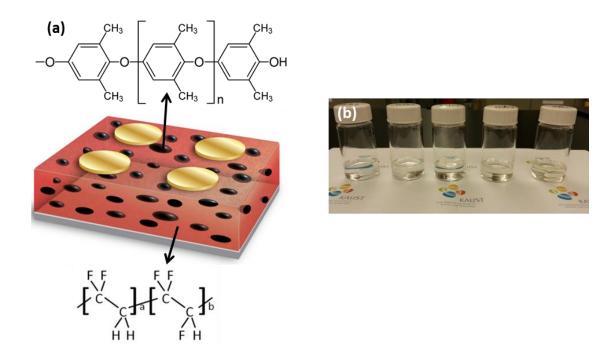

| Figure. 9.1 (a) Schematic 3-D cross section of ferroelectric capacitors with phase seperated blends of P(VDF-TrFE)-PPO sandwiched between Pt and Au electrodes. The morphology consists of phase separated nanospheres of amorphous PPO, surrounded by P(VDF-TrFE) matrix. (b Solutions with 0 wt%, 2 wt%, 4 wt %, 6 wt % and 8 wt% PPO (Left to Right) showing clear homogenous and stable solutions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

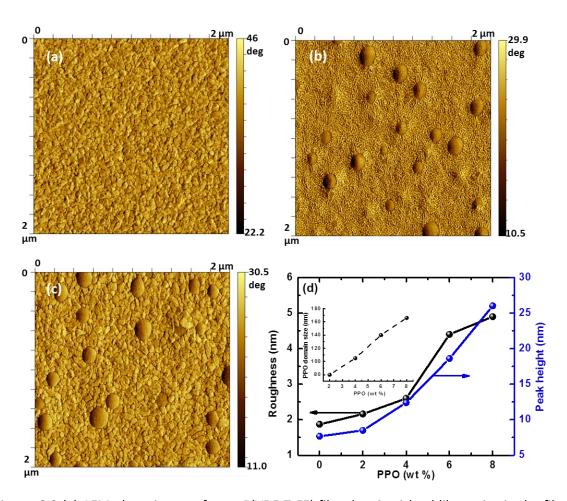

| Figure. 9.2 (a) AFM phase image of pure P(VDF-TrFE) film showing island like grains in the film (b) AFM phase image of as spun blend films with 6 wt % PPO without annealing. (c) AFM phase image of blend films with 6 wt % PPO after annealing at 135 °C, with increase in grain size o P(VDF-TrFE). (d) R <sub>rms</sub> (Left) and peak height (Right) of blend films as a function of PPO loading The inset shows average size of the PPO nanospheres as calculated from the AFM phase images                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| ±/\(                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

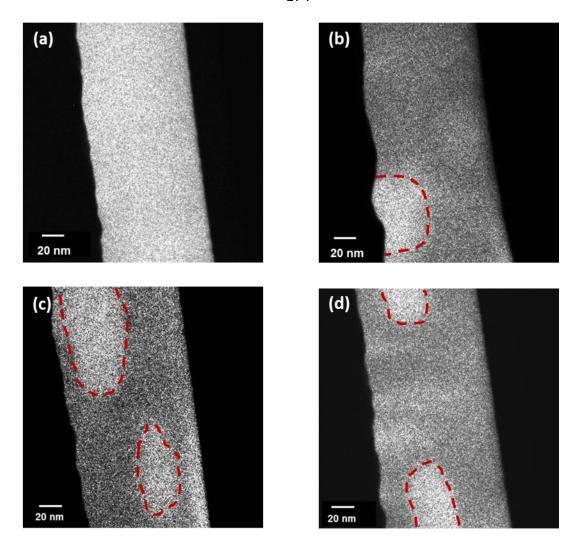

| Figure. 9.3 Cross section TEM images of pure P(VDF-TrFE) films (a) and blend films with 6 wt % PPO (b,c,d)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

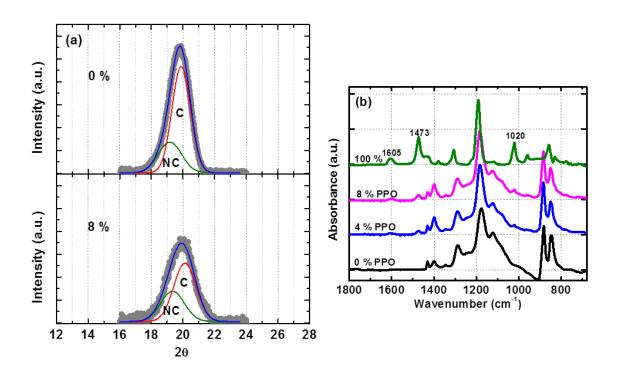

| Figure. 9.4 (a) Grazing incidence XRD spectra for pure ferroelectric P(VDF-TrFE) films and blend films with 8 wt% PPO. (b) FT-IR spectra of pure ferroelectric P(VDF-TrFE) thin film, pure PPO thin film and blend films with 4 wt% and 8 wt% PPO                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

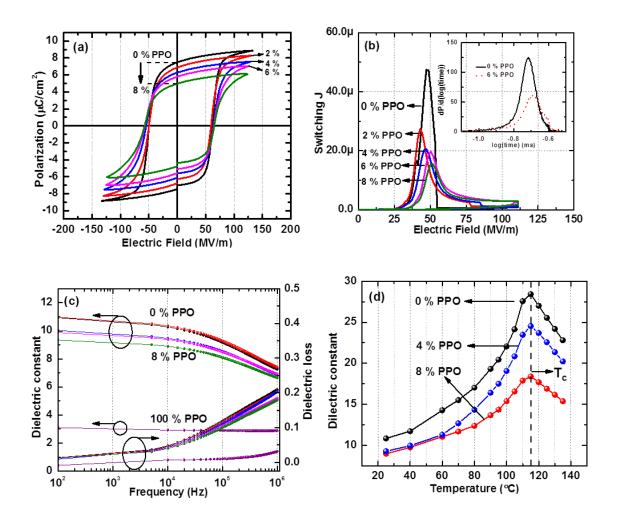

| Figure. 9.5 (a) Polarization-Electric Field hysteresis loop measurements for blend films at 10 Hz as a function of amount of PPO. (b) Switching current response from blend films with 0 to 8 wt % PPO and with Platinum/ Gold electrodes. The inset shows switching characteristics for blend film at 125 MV/m, with peak of dP/d(log(t)) vs. log(t) representing respective switching times. (c) Dielectric spectroscopy study with dielectric constant (left axis) and dielectric losses (right axis) for blend films with 0 to 8 wt % PPO and pure PPO films. (d) Temperature dependence of dielectric permittivity for devices with 0, 4 and 8 wt % PPO at 1 KHz                                                                                   |

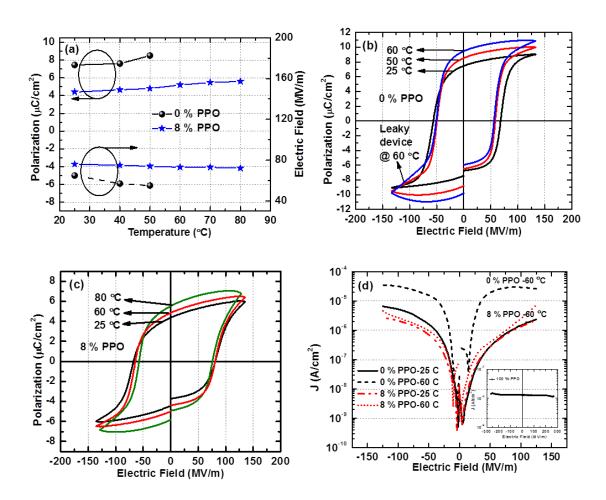

| Figure. 9.6 (a) $P_r$ and $E_c$ as a function of temperature for pure P(VDF-TrFE) films and blend films with 8 wt % PPO. (b) P-EF hysteresis loop measurements for pure P(VDF-TrFE) films at 10 Hz as a function of T. (c) P-EF hysteresis loop measurements for blend films with 8 wt % PPO at 10 Hz as a function of T (d) Current density-Electric Field measurements of blend films (0, 8 wt % PPO) at 0 °C and 60 °C. The inset shows the leakage J of pure PPO device with Pt-Au electrodes 182                                                                                                                                                                                                                                                   |

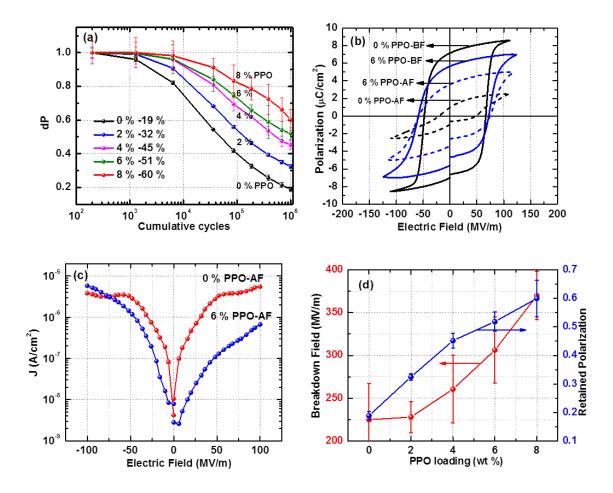

| Figure. 9.7 (a) Electrical fatigue properties showing relative polarization of blend films with 0 to 8 wt % PPO. The films were stressed at 100 MV/m and a frequency of 100 Hz and the PUND measurements were done at saturation fields of 125 MV/m and 100 Hz. (b) Polarization-Electric Field hysteresis loop measurements for pure P(VDF-TrFE) films and 6 wt % PPO films before (BF) and after fatigue (AF), characterized also at 100 Hz. (c) Current density-Electric Field measurements of pure P(VDF-TrFE) films and 6 wt % PPO films after fatigue upto 106 cycles at 100 Hz (d) Dielectric breakdown strength (Left) and Fatigue or polarization retention after 10 <sup>6</sup> cycles (Right) as a function of amount of PPO in blend films |

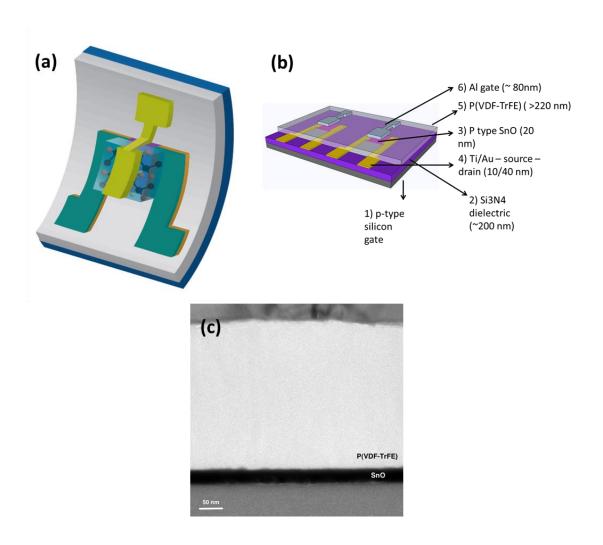

| Figure. 10.1 (a) Top gate SnO-P(VDF-TrFE) FeFET on polyimide (b) Dual gate FeFET's with $Si_3N_4$ and p-type Silicon as bottom dielectric and gate. (c) TEM image of the SnO/P(VDF-TrFE) interface                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

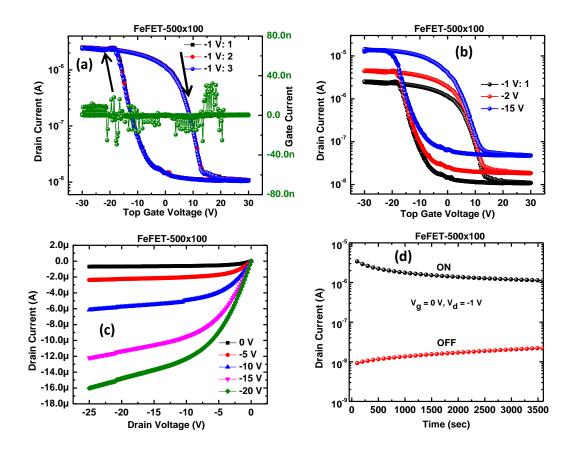

| Figure. 10.2 SnO/P(VDF-TrFE) FeFET characteristics on polyimide. (a) Transfer characteristics at $V_{DS}$ =-1V (Linear) and gate leakage current (Right Axis) (b) Transfer characteristics at different $V_{DS}$ = -1 V (Linear) to -15 V (Saturation) (c) Output characteristics from $V_{GS}$ =0 V to -20 V at -5V steps (c) Retention Characteristics. The ON/OFF states were produced at gate voltages of -30/+30 V with a 1 sec pulse and the retention was measured at zero gate bias condition 201                                                                                                                                                                                                                                               |

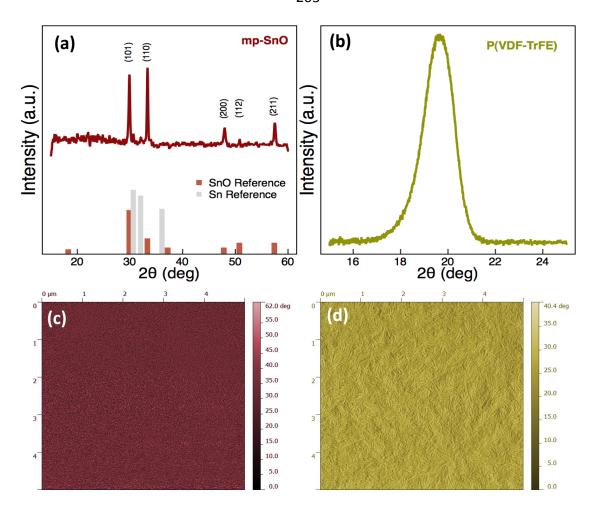

| Figure. | 10.3            | Materials    | characte   | rization.  | (a) XRD   | pattern   | of SnO   | thin f  | ilms.  | The line | es at the |

|---------|-----------------|--------------|------------|------------|-----------|-----------|----------|---------|--------|----------|-----------|

| botton  | n shov          | v the diffra | ction patt | erns of te | etragona  | l SnO (JC | PDS car  | d No. 0 | 6-039  | 5) and t | etragonal |

| Sn (JCF | DS ca           | rd No. 04-   | 0673); (b) | GIXRD p    | attern c  | f P(VDF-  | TrFE) la | yer (c) | AFM i  | mage o   | f the SnO |

| surface | e; (d) <i>A</i> | AFM image    | of the P(\ | /DF-TrFE)  | surface   | morpho    | logy     |         |        |          | 203       |

|         |                 |              |            |            |           |           |          |         |        |          |           |

| Eiguro  | 10 /            | Dual Gato    | EoEET cha  | ractoristi | cc (a) Di | ual gato  | EaEET tr | ancfor  | curvac | in Lino  | ar rogimo |

# LIST OF TABLES

| Table 3.1. Conductivities of different PEDOT: PSS grades, characterized u  | sing a four probe  |

|----------------------------------------------------------------------------|--------------------|

| measurement system. Clevios PH500 and PH1000 were doped with 4 % [         | Dimethyl Sulfoxide |

| (DMSO). All films were spun at 1500 rpm for 30 seconds                     | 70                 |

|                                                                            |                    |

| Table 10.1. Important parameters for our dual gate FeFET's as a function o | f different bottom |

| gate bias.                                                                 | 208                |

# **CHAPTER 1**

# **INTRODUCTION**

### 1. Motivation and Background

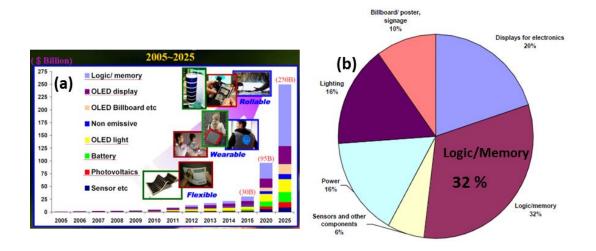

Flexible electronics has made remarkable progress during the last 15 years, especially in the field of organic/polymer thin film transistors (OTFTs), organic light emitting diodes (OLEDs), polymer memory, and sensors. The large-area, flexible electronics market is currently a 2 billion US \$ market and expected to grow to about US \$250 Billion by 2025 (Fig. 1.1(a)) [1]. An essential part of most flexible electronic circuits is a non-volatile memory that can be used to store and retrieve information when required. In fact logic/memory is expected to be the leading technology in flexible electronics, capturing 32 % of the market share (Fig. 1.1(b)) [1].

Figure. 1.1. (a) Projected growth for flexible electronics market. (b) Projected market share of different technologies in flexible electronics by 2020. [1]

Traditional memory circuits based on silicon are difficult to integrate with plastic substrates due to the high processing temperature for silicon and its poor flexibility. Polymeric memories are a promising alternative due to their simple device structure, low temperature processability, low cost, large information storage capacity and multilayer stacking possibility [2]. Polymeric materials possess unique advantages, like good mechanical strength, high flexibility and most importantly ease of processability. A variety of deposition techniques such as spin-coating, spray-coating, dip-coating, roller-coating and ink-jet printing can be used to deposit polymers on a variety of substrates (plastics, silicon wafers, paper, glass etc.) for large scale low cost fabrication of memory devices (Fig. 1.2(a) and (b)).

Figure. 1.2 (a) Roll to roll processing on plastic substrates (b) Large area printed, flexible polymeric circuits for RFID application [2].

One of the major markets that one can think for the use of polymer memory would be low cost mass data storage. In this market, it would have to compete with

Flash memory (a multi-billion dollar market) by lowering the fabrication costs [3]. Integrated memory circuits (IC's) for niche applications would be another potential market for polymer memory. A popular example is the RFID tag (radio-frequency identification) [3]. These tags are small ICs that communicate data stored in its memory via radio. The RFID tags can potentially replace bar codes. RFID tags fabricated by using silicon, cost around \$ 0.35 per tag. Thus to compete in this market the cost price of the RFID tags must be only a few cents [3]. This might not be possible using RFID tags fabricated with silicon, but may be possible by using polymeric/organic materials that are cheaper to synthesize, can be solution processed and deposited over large areas using different techniques.

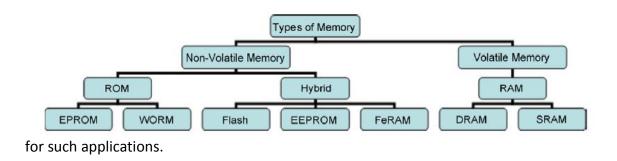

Many efforts are ongoing towards the fabrication of a fully polymer based nonvolatile-rewritable electronic memory device that can be used for a wide range of applications. Generally, electronic memories can be categorized into: Volatile and Nonvolatile memories (Fig. 1.3) [2]. Volatile memory loses the stored information as soon as it loses its power. They require a continuous power source so they don't lose the stored data. On the other hand non-volatile memory will retain the stored information or data even when it loses its power supply. Among volatile memories, DRAM (random access memory) is the most popular and is mainly used for computers/laptops today. It stores each bit i.e. "1" or "0" in a separate capacitor, but is volatile as the stored charge leaks away with time. Thus it loses its data when the power supply is turned off. Volatile memories such as these are unsuitable for applications like

RFID tags, where the stored information in the tag is sent via a radio signal. RFID tags get their power from the radio signal that they use to communicate; thus there is no constantly available power source [3]. Therefore, they cannot perform a memory refresh operation whenever necessary to prevent loss of information. A nonvolatile memory, where the information is preserved after removing the external power, is ideal

Figure. 1.3 Classification of different types of memory [2].

Non-volatile memories can be classified into read only memories and rewritable memories. Among read only category the WORM i.e. Write-Once-Read-Many is the most widely studied and reported. WORM memory with its non-volatile character can store data permanently and be read repeatedly. It can be written onto just once and thereafter the data cannot be modified. WORM memory can be used for archives, databases where large information has to be kept reliably and made available for a long time. Examples of WORM memory in daily life are digital optical disc storage devices such as Compact disc (CD) drives, Digital Versatile Disc (DVD-R) drives or Programmable Read only memories (PROMs). In the rewritable category, Flash memory is the most

widely used. It is possible to electrically reprogram the stored data and thus, it is non-volatile and rewritable. Flash memory is used in a number of systems such as Personal digital assistors (PDA's), laptops, MP3 players, digital cameras, smartphones and tablets. The current technology for flash memory is based on metal-oxide-semiconductor field-effect transistors (MOSFET) with a floating gate [2]. The problem with using flash memory is that the voltage during the write or erase process is very high and thus requires a charge pump. Furthermore the writing speed of flash memory is not fast enough (several milliseconds) and it suffers from poor endurance (up to  $10^6$  cycles) [2].

To store data, memory materials use a physical property that displays hysteresis in response to an external stimulus. By measuring the current state of the hysteresis one can retrieve the stored data. Many different physical properties can be used to obtain a memory effect. Some of the efforts in polymer memories are based on different mechanisms such as filamentary conduction, charge trapping effects, dipole alignment, and reduction-oxidation to name a few [4]. In this dissertation, the aim is to fabricate all-polymer non-volatile memory devices focused on one particular mechanism, i.e., those based on ferroelectricity particularly for flexible electronics applications. To provide the basic knowledge on materials, physical properties and concepts employed in the rest of this dissertation, this chapter is dedicated to an introduction. We first introduce ferroelectricity and ferroelectric polymers. This is followed by a discussion on the working principle of ferroelectric memory devices; in particular ferroelectric capacitors and transistors. After this we have a review on the current state of research

for ferroelectric memory devices. Lastly we end with a short summary or outlook of the field.

### 2. Ferroelectricity and Ferroelectric polymers

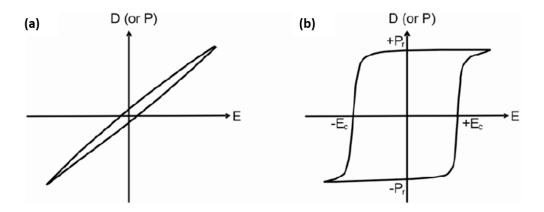

Ferroelectric memory (FeRAM) is gaining a lot of popularity due to its non-volatile and rewritable property. Ferroelectric materials have a spontaneous electric polarization which is reversible upon the application of an external electric field (EF) and more importantly they retain the polarization state even upon removal of the electric field [4]. When dielectrics are placed in a uniform external electric field, a displacement of positive and negative charges leads to the polarization of the dielectric material. This induced polarization creates a so-called depolarization field; an EF in the opposite direction, which tends to bring the displaced charges back to their equilibrium position after removing the external field. For most materials, "the polarization P", is a linear function of the "applied external electric field: EF" (Fig. 1.4(a)) [5].

Figure. 1.4 (a) Polarization loop in a normal dielectric (b) Polarization (Hysteresis) loop in a ferroelectric dielectric [5].

This is called dielectric polarization. For most dielectric materials the plot of charge displacement (or polarization) versus electric field, does not show any significant hysteresis upon applying an external electric field (Fig. 1.4(a)).

In 1921 a new property, called ferroelectricity, was discovered in Rochelle salt (KNa( $C_4H_4O_6$ )· $4H_2O$ ) by Valasek [3]. Ferroelectric dielectric materials show a non-linear polarization as a function of applied electric field. They show an electric hysteresis with a remnant polarization  $P_r$ ; polarization that is retained by the material even when the field is removed (Fig. 1.4(b)). The term ferroelectricity comes from the similarity between ferroelectrics and ferromagnets. The way the hysteresis curve of P versus EF of ferroelectrics varies is the same as M versus H for ferromagnets [3]. The hysteresis loop of polarization versus applied field of ferroelectric materials can be used for non-volatile data storage. The polarization states ( $\pm P_r$ ) up and down can be used to store "1" and "0", respectively. When the external electric field is removed, the polarization state remains unchanged. As a result, ferroelectric materials are ideal for non-volatile memory applications.

Ferroelectricity remained a theoretical curiosity for long until ceramics were discovered. It started with the discovery of ceramics such as barium titanate (BaTiO<sub>3</sub>) in 1944 and most notably lead zirconate titanate (Pb(Zr,Ti)O<sub>3</sub>, PZT). The most widely used ferroelectric materials is Pb(Zr,Ti)O<sub>3</sub> (PZT) which is a perovskite, and Sr(Bi,Ta)<sub>2</sub>O<sub>9</sub> (SBT) which is a layered material. The issue with these perovskite materials is the high

processing temperature requirements and their brittle nature which makes them unsuitable for flexible electronic applications.

Alternatively, ferroelectric polymers can be used for memory applications. Polymers have many attractive features: They can be solution processed and deposited at low temperatures on a wide different substrates using low cost techniques like gravure printing, ink jet printing, spin coating etc. [2]. Many polymers display polarization hysteresis due to charge injection or induced polarization. These mechanisms produce electrets, which display unstable piezoelectric and pyroelectric effects on a time scale of few hours to few days. However, the true definition of a polymer ferroelectric material is one which has a polar unit cell and an electric field can reverse the direction of the polarization/dipole moment [2,3,4]. Some polymers which exhibit ferroelectric properties are: (i) poly(vinylidene fluoride) (PVDF) and its copolymers, (ii) odd nylons, (iii) polyacrylonitrile, (iv) polyureas and polythioureas, and (v) ferroelectric liquid-crystalline (FLC) polymers (from attaching ferroelectric liquid-crystall molecules as side chains or pendant groups to polymer backbones) [2].

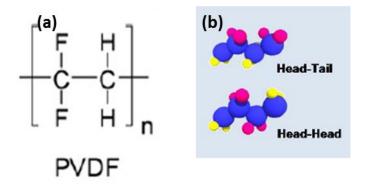

Among them, PVDF and its copolymer are the most widely used for FeRAMs. Poly(vinylidene fluoride) P(VDF) is very attractive for memory applications due to its large spontaneous polarization, short switching times, low leakage, excellent chemical stability, transparency and low temperature processability [4]. PVDF was discovered in the early 1970s to be ferroelectric. It has a simple chemical structure with a monomer unit of  $-CH_2-CF_2$  (Fig. 1.5(a)). PVDF is used for a wide variety of applications, ranging

from protective coatings to ultrasound transducers. The highly electronegative fluorine atoms with a van der Waals radius of 1.35 Å, along with electropositive Hydrogen (1.2 Å) form polar bonds with the main chain, resulting in a very high dipole moment of  $6.4 \times 10^{-30}$  Cm [2,4]. This simple structure makes it highly flexible (like Polyethylene) but at the same time gives some stereo-chemical constraints (like Polytetraflouroethylene) to PVDF. The PVDF chains usually have head-to-tail configuration, but head-to-head and tail-to-tail defects can also occur (Fig. 1.5(b)).

Figure. 1.5 (a) Chemical Structure of PVDF monomer (b) Molecular configuration in PVDF. (Fluorine atoms in Red and Hydrogen in Yellow and Carbon in Blue) [4].

PVDF can exist in at least three different stereo-chemical conformations: alternating trans (T) and gauche (G) (TGTG), all-trans (TTTT), and TTTG (Fig 1.6(a)). A major difference between these conformations is that the C-F and C-H bonds take different directions. Since the net dipole moment of the chain is the vectorial sum of dipole moment carried by individual segments, the different conformations exhibit

different net dipole moments. The all-trans conformation (TTTT) is the most polar one with dipole moment of  $7.0 \times 10^{-30}$  Cm per repeat unit perpendicular to the chain axis.

Figure. 1.6 (a) Conformation like TFTG and TTTT in ferroelectric polymers. (b) Different packing modes leads to different crystalline structures like the  $\alpha$  and  $\beta$  phase (c) Typical nature of a semicrystalline polymer with crystalline and amorphous regions. (Fluorine atoms in Red and Hydrogen in Yellow and Carbon in Blue) [4].

PVDF is a semi-crystalline polymer, which means there are both crystalline and amorphous regions (Fig. 1.6(c)). In its crystalline region the polymer chains are packed into different crystalline forms, depending not only on the conformation of each individual chain but also the way of packing. The difference in packing of the polymer chains in the unit cell leads to four polymorphic crystals, referring to as  $\alpha$ ,  $\beta$ ,  $\gamma$  and  $\varphi$  [2,3,4]. The non-polar  $\alpha$  phase, with its TGTG conformation has chains are packed in a way that their dipole moments cancel each other, resulting in zero net polarization.(Fig. 1.6(b)) The most useful and interesting phase is the polar  $\beta$  phase in which has the all Trans (TTTT) conformation. Since the fluorine atoms are all positioned on one side of a unit cell, the  $\beta$  phase is a polar phase (Fig 1.6(b)). Thus the  $\beta$  phase is ferroelectric, due

to an optimal alignment of fluorine and hydrogen atoms in the chain. The unit cell in the  $\beta$  phase is orthorhombic, space group  $C_m 2_m$ , and with lattice constants a=8.58, b=4.91, and c (chain axis) = 2.56 Å [5,6]. (Fig. 1.7(b)) When PVDF polymer is melted and subsequently cooled, the crystalline packing usually forms the non-polar  $\alpha$  phase. But by annealing, poling or stretching the packing of ferroelectric chains can be modified to have a polar configuration i.e.  $\alpha$  phase can be changed to the other three phases [2,4].

Figure. 1.7 (a)  $\alpha$  phase of PVDF (b)  $\beta$  phase of PVDF. [5]

Getting the ferroelectric phase in PVDF can be tricky. Another option is to copolymerize VDF with TrFE (CHFCF $_2$ ) (Fig. 1.8(a)). The fluorine atoms which are larger than hydrogen, impart more steric hindrance. With the addition of TrFE into the VDF chain the unit cell size increases and easily allows the formation of the  $\beta$  phase with

TTTT conformation [2]. The copolymerization of PVDF with TrFE also helps to improve the crystallinity of the semicrystalline polymer ferroelectric film which is important as only the crystalline regions give rise to ferroelectricity. The dipole moments in amorphous regions have random directions and will cancel out each other leading to a net zero polarization. Also the addition of TrFE lowers the ferroelectric–paraelectric phase transition temperature or the Curie temperature ( $T_c$ ) below the melting point. P(VDF-TrFE) is the only known ferroelectric polymer that has a measurable Curie temperature  $T_c$  which increases with increasing VDF content from 70 °C (50 mol%) to 140 °C (80 mol%) (Fig. 1.8) [6]. In PVDF homo-polymer the energy barrier for such transition is so large that no phase transition could be observed up to the melting temperature. Thus with a simple annealing step below the melting temperature and above the curie temperature, it is possible to fabricate high quality ferroelectric P(VDF-TrFE) thin films [6].

Figure. 1.8 (a) Chemical structure of P(VDF-TrFE) (b) Phase diagram of P(VDF-TrFE) [6].

P(VDF-TrFE) polymer chains have a net dipole moment pointing from the electronegative F to electropositive H (Fig. 1.9(a)). Figs. 1.9(a) and (b) show the dipole switching mechanism. The direction of the dipole is changed by a rotation of the polymer chain or molecule. This is possible due to the single C-C bonds that allow for some flexibility. The dipole switching is achieved by a large external EF opposite to the direction of polarization. "The reorientation of dipoles is not a simple 180° rotation but may progress through successive 60° rotations of the dipoles, which is consistent with the experimental observations and theoretical investigation at the molecular level" (Fig. 1.9(b)). [2,4]

Figure. 1.9 (a) Illustration of the dipole switching in PVDF. (b) Dipole switching of fluorine-hydrogen dipoles based on 60° rotation model [2, 3].

### 3. Ferroelectric memory devices

### a. Ferroelectric capacitors

The simplest ferroelectric memory device is a MFM structure i.e. Metal-Ferroelectric-Metal structure (Fig. 1.10(a)).

If we consider putting two conducting plates close to each other with vacuum in between and if we apply a voltage V across the plates, it generates an electric field E in the vacuum:

$$E = -\frac{V}{d} \tag{1.1}$$

where d is the distance between the plates.

A charge of ±Q accumulates on both plates. The charge per unit area is:

$$D = \epsilon_0 E \tag{1.2}$$

Also known as "charge displacement D", with  $\epsilon_0$  the dielectric permittivity of free space.

If a dielectric material is used instead of vacuum, then  $\epsilon_0$  is increased to the permittivity  $\epsilon_{di}$  of this dielectric, also known as the relative permittivity ( $\epsilon_r$ ) or dielectric constant [7].

$$k = \frac{\epsilon_{di}}{\epsilon_0} \tag{1.3}$$

If the Electric Field is kept constant then upon introducing a dielectric the charge displacement would increase (Eq. (1.2)). When a dielectric material is placed in an EF, it polarizes in the direction opposite to the field. This creates a small internal depolarizing field which opposed the applied external EF. This requires extra charges on the electrodes to maintain the same EF. For a ferroelectric MFM capacitor, Equation 1.2 becomes

$$D = \epsilon_{di}E + P \tag{1.4}$$

with an additional polarization P. The theoretical polarization depends on the size and direction of the dipoles and their density. Polarization P depends on the history of the applied EF or in other words its last state and not just the instantaneous applied field. The most well-known technique for measuring P is with a Sawyer-Tower circuit, shown in Fig. 1.10(a). "A sinusoidal voltage signal is applied to one of the electrodes of the ferroelectric capacitor and the amount of charge displacement in the other electrode is measured using the voltage it creates over a reference capacitor connected in series. The voltage drop over the reference capacitor is minimized by using a large reference capacitor [7]."

Figure. 1.10 (a) Sawyer-Tower circuit to measure polarization hysteresis in a ferroelectric capacitor (b) Polarization or Charge displacement versus Electric field curved for a typical ferroelectric capacitor [2,7].

Fig. 1.10(b) shows a typical hysteresis measurement of a ferroelectric capacitor. As the Electric field/Voltage is increased from 0 to  $\pm V_{cc}$ , the polarization changes from A  $\Rightarrow$  B  $\Rightarrow$  C. Point C represents the maximum or saturation polarization of the capacitor (P<sub>s</sub>) at max fields (V<sub>cc</sub>). Upon decreasing the field to zero the polarization decreases to point D. Point D represents remanent or remaining polarization (P<sub>r</sub>) at zero fields. It is slightly lower than saturation polarization due to relaxation of some dipoles (without reversing their direction). The minimum field necessary to switch or reverse the dipoles is known as the coercive field (V<sub>c</sub>). To apply ferroelectric materials in memory devices, the two net stable states, "upward polarization  $\pm P_r$ " and "downward polarization  $\pm P_r$ " can be defined as "1" and "0" signals.

To read the data one applies a field greater than the coercive voltage to detect a high/low charge displacement current depending on whether the dipoles/polarization were aligned or not with the direction of the external EF. Therefore ferroelectric capacitors suffer from "destructive read-out" since the read-out operation can erase the stored data. Thus we need a reset voltage to rewrite the erased data after every read operation [3]. The important property is the retention of polarization (remanent polarization-P<sub>r</sub>) by the ferroelectric material even after the field is removed. In addition to the hysteresis curves, ferroelectric capacitors are characterized using leakage current, switching current, fatigue endurance, and dielectric dispersion properties.

### b. Ferroelectric Field effect Transistors (FeFET's)

The organic thin film transistor (OTFT) is composed of: (i) substrate which can be glass, silicon, plastic etc. (ii) Gate electrode (iii) source (S) and drain (D) electrodes, (iv) a dielectric, and (v) a semiconductor channel layer, as shown in Fig. 1.11. The channel length can be defined as the distance between the S and D (10 to 100  $\mu$ m) and the channel width (W) is the actual width of the electrodes (100  $\mu$ m to 1mm) [2]. Thin film transistors can be in two different configurations: (i) top contact (ii) bottom contact (Fig. 1.11). In a top contact device the S&D electrodes are deposited onto the semiconductor and in a bottom contact device the semiconductor is deposited onto the S&D

electrodes. Different conducting materials such as Al, Pt, Au, Ag, ITO, highly doped Si, PEDOT:PSS can be used as the electrode. In an OTFT the active channel layer is usually a conjugated molecule or polymeric semiconductor.

Figure. 1.11. OTFT in top and bottom contact configuration. If a ferroelectric polymer is used as the gate dielectric then it becomes a Ferroelectric Field Effect Transistor (FeFET) [2].

In 1963 the first FeFET was fabricated by Moll and Tarui, with triglycine sulphate (TGS) on a CdS substrate [7]. In a FeFET, a ferroelectric material is used as the gate dielectric layer and is in contact with active SC layer (Fig. 1.11). To read the current in the channel layer ( $I_d$ ) one needs to apply a voltage between the S and D electrodes ( $V_d$ ) so the charges can flow from Source to drain and one can detect the current (Fig. 1.12(a)). The drain current ( $I_d$ ) depends strongly on the gate voltage ( $V_g$ ) (Fig. 1.12(b)).

When we apply a voltage to the gate it can align the dipoles in the ferroelectric layer and induce surface polarization. This attracts charge carriers in the semiconducting channel and can induce either a high or a low drain current depending on the direction of polarization. This current remains high/low even after removing the gate bias (Fig. 1.12(b)). On the contrary, the OFETs lose the accumulated charges when the gate bias is removed and the device turns OFF. Thus they are volatile, which means that they can't be used for non-volatile memory. In contrast in a FeFET, the dipoles maintain their polarization state even after removal of the field. Therefore the  $I_d$ - $V_g$  characteristics in a FeFET show a hysteresis effect with two stable states of high and low current ( $I_d$ ) that can be related to a 1 or 0 required for memory applications.

Figure. 1.12 (a) Layout of typical thin film transistor showing source, drain and gate contacts. (b)  $I_d$ - $V_g$  characteristics of a FeFET

Thus the way a FeFET works is due to attenuation of charge carriers in the SC by the remanent polarization ( $P_r$ ) of the ferroelectric layer. The major advantage of FeFET

over Ferroelectric capacitors is their non-destructive read out property. The drain current ( $I_d$ ) which represents "1" or "0" can be sampled for long times using a low  $V_d$  and at zero  $V_g$ . This does not disturb the dipoles/polarization in the ferroelectric dielectric. Thus, we get combined non-volatile and non-destructive read out property by using FeFETs [2,3,4]. Another added advantage of using FeFET is that they are highly scalable. In a capacitor reduction of the electrode area is highly desirable because it increases the memory density. "The switching current during a dipole switching event scales with the electrode area A, remanent polarization  $P_r$  and switching time  $t_{sw}$  as:

$$I \alpha \frac{AP_r}{t_{sw}} \tag{1.5}$$

An area reduction therefore reduces the signal. By contrast, the drain current of a FeFET working in the linear regime scales with

$$I \alpha \frac{V_d W \mu}{L} \tag{1.6}$$

It will also increase with the charge density in the semiconductor induced by the ferroelectric. According to Eq. 1.6, if L and W are reduced by the same factor, the readout signal ( $I_d$ ) is unaffected by scaling" [7]. Other important parameters for Ferroelectric transistors are the ON/OFF ratio, mobility, memory window, operating voltages and retention times.

#### 4. Review on polymer ferroelectric memories

#### a. Ferroelectric capacitors

In the past, majority of the research on ferroelectric memory has focused on ferroelectric capacitors for potential use in 1T-1C memory cells. The two polarization states ( $+P_r$  and  $-P_r$ ) of a ferroelectric capacitor are used to store "1" and "0" and can be written via an external electric field. To read the data one applies a field voltage greater than coercive voltage to obtain a high or a low switching current response (1 or 0). Some of the fundamental issues that need to be studied and resolved for polymer ferroelectric capacitors are: Reducing operating voltages, improving endurance or fatigue, improving thermal stability, decreasing switching speed and improving data retention properties.