**ADVERTIMENT**. La consulta d'aquesta tesi queda condicionada a l'acceptació de les següents condicions d'ús: La difusió d'aquesta tesi per mitjà del servei TDX (<a href="www.tesisenxarxa.net">www.tesisenxarxa.net</a>) ha estat autoritzada pels titulars dels drets de propietat intel·lectual únicament per a usos privats emmarcats en activitats d'investigació i docència. No s'autoritza la seva reproducció amb finalitats de lucre ni la seva difusió i posada a disposició des d'un lloc aliè al servei TDX. No s'autoritza la presentació del seu contingut en una finestra o marc aliè a TDX (framing). Aquesta reserva de drets afecta tant al resum de presentació de la tesi com als seus continguts. En la utilització o cita de parts de la tesi és obligat indicar el nom de la persona autora.

**ADVERTENCIA**. La consulta de esta tesis queda condicionada a la aceptación de las siguientes condiciones de uso: La difusión de esta tesis por medio del servicio TDR (<a href="www.tesisenred.net">www.tesisenred.net</a>) ha sido autorizada por los titulares de los derechos de propiedad intelectual únicamente para usos privados enmarcados en actividades de investigación y docencia. No se autoriza su reproducción con finalidades de lucro ni su difusión y puesta a disposición desde un sitio ajeno al servicio TDR. No se autoriza la presentación de su contenido en una ventana o marco ajeno a TDR (framing). Esta reserva de derechos afecta tanto al resumen de presentación de la tesis como a sus contenidos. En la utilización o cita de partes de la tesis es obligado indicar el nombre de la persona autora.

**WARNING**. On having consulted this thesis you're accepting the following use conditions: Spreading this thesis by the TDX (<a href="www.tesisenxarxa.net">www.tesisenxarxa.net</a>) service has been authorized by the titular of the intellectual property rights only for private uses placed in investigation and teaching activities. Reproduction with lucrative aims is not authorized neither its spreading and availability from a site foreign to the TDX service. Introducing its content in a window or frame foreign to the TDX service is not authorized (framing). This rights affect to the presentation summary of the thesis as well as to its contents. In the using or citation of parts of the thesis it's obliged to indicate the name of the author

# Design of Efficient Microwave Power Amplifier Systems

#### PhD Thesis Dissertation

Author: Kyriaki Niotaki

Advisors: Dr. Apostolos Georgiadis

Dr. Christos Verikoukis

Submitted to the Universitat Politècnica de Catalunya (UPC) in partial fulfillment of the requirements for the degree of DOCTOR OF PHILOSOPHY

PhD program on Signal Theory and Communications

Barcelona, November 2014

## **Abstract**

In the future communication systems, it is of key importance that the transceivers are capable of operating in multiple frequency bands and with complex signals. In this context, the power amplifier is a critical component of the transceiver, since it is responsible for most of the total power consumption in base stations and portable devices. Apart from the power consumption, the design of power amplifier systems must account for multi-band/broadband capabilities, high peak-to-average power ratio signals and the mismatch effect caused by the various operating conditions. Hence, the design of power amplifier topologies that enhance the total system efficiency and reliability is a challenging task.

This PhD dissertation introduces novel power amplifier architectures and solutions for modern communication systems. The contributions of this thesis can be divided in two parts. The first part deals with the study and design of power amplifier systems. It is of major importance that these designs provide linear amplification and operation at multiple frequency bands, which will permit the reduction of the cost and size of the devices. Additionally, the possibility to harvest the dissipated power from the power amplification process is investigated. For the development of the prototypes, lumped-element topologies, transmission line implementation and Substrate Integrated Waveguide (SIW) technology are adopted.

In the second part of the thesis, novel matching networks are introduced and their properties are studied. In particular, resistance compression topologies are proposed to overcome the performance degradation associated with the sensitivity of nonlinear devices to environmental changes. These networks can be adopted in modern power amplifier architectures, such as envelope tracking and outphasing energy recovery power amplifier topologies, in order to provide improved performance over a wide range of operating conditions.

## Resumen

Es primordial que los transceptores de los futuros sistemas de comunicación sean capaces de operar en múltiples bandas de frecuencia y con señales complejas. En este contexto, el amplificador de potencia es un componente crítico del transceptor dado que su consumo energético supone la mayor parte del consumo tanto de las estaciones base como de los dispositivos móviles. Aparte del consumo energético, los nuevos diseños de sistemas de amplificación de potencia deben considerar aspectos como la capacidad de operar en múltiples bandas o en banda ancha, el uso de señales con alta relación de potencia pico a potencia media (PAPR) y el efecto de desadaptación que aparece bajo las diferentes condiciones de funcionamiento. Por lo tanto, el diseño de nuevas topologías para amplificadores de potencia que mejoren la eficiencia total del sistema y la fiabilidad es una tarea compleja.

Esta tesis doctoral presenta nuevas arquitecturas de amplificadores de potencia y soluciones para los sistemas de comunicación modernos. Las contribuciones de esta tesis se pueden dividir en dos partes. La primera parte se centra en el estudio y diseño de sistemas de amplificación de potencia con el fin de proporcionar amplificación lineal y funcionamiento en múltiples bandas de frecuencia, lo que permitirá reducir el coste y tamaño de los dispositivos. Además, se investiga la posibilidad de reutilizar la energía disipada en el proceso de amplificación de potencia. Para el desarrollo de los prototipos, se utilizan topologías hibridas, implementaciones con líneas de transmisión y tecnología de guía de onda integrada en sustrato (SIW).

En la segunda parte de la tesis, se proponen redes de adaptación y se estudian sus propiedades. En particular, se proponen topologías de compresión de resistencia para minimizar el efecto que producen en el rendimiento la sensibilidad de los dispositivos no lineales a los cambios ambientales. Estas redes pueden ser utilizadas en arquitecturas modernas de amplificadores de potencia como pueden ser las topologías envelope tracking y outphasing energy recovery con el fin de proporcionar un rendimiento mejorado bajo múltiples condiciones de funcionamiento.

# Acknowledgements

First of all, I would like to sincerely thank my PhD advisors Dr. Apostolos Georgiadis and Dr. Christos Verikoukis for giving me the opportunity to work with such an interesting research topic. I am more than grateful for their invaluable time and help during the last three years. Thank you for being always here to provide ideas, suggestions and comments, and mostly to teach me how to reach my goals!

I am also grateful to Dr. Ana Collado for her unlimited support during the last three years. I am really thankful for all her valuable help in measuring and characterizing the prototypes. I would like to sincerely thank her for always being here to find solutions to any kind of problems!

I would also like to thank Dr. Francesco Giuppi for being always helpful and supportive. I would like to specially thank him for all the amazing tea breaks he has offered me during his stay at CTTC! I also want to sincerely thank Sangkil Kim and Marco Virili for their excellent collaboration.

I would also like to thank Dr. Javier Arrivas, Dr. Fermin Mira, David López, José Rubio, and Selva Via for their help with the laboratories facilities. Special thanks go to all of my workmates during these three years that have created a great working environment.

Of course, I could not forget to mention Prof. Katherine Siakavara and Athanasia Symeonidou for offering me valuable advice and support during my master degree.

I would like also to sincerely thank all my friends, the "old" ones and the "new" ones, for being always supporting and encouraging!

Apparently, I cannot thank enough my family for their love and support. And finally, words are not enough to express my thanks to Stratos for simply being himself!

Thank you! Gracias! Gràcies! Ευχαριστώ πολύ!

## List of Publications

This is a selected list of publications based on this PhD dissertation.

#### **Journal Publications**

- [J3] *In Preparation* K. Niotaki, A. Georgiadis, A. Collado and J. Vardakas, "Resistance Compression Networks for Improved Envelope Amplifier Performance".

- [J2] Accepted for Publication K. Niotaki, A. Georgiadis, A. Collado and J. Vardakas, "Dual-Band Resistance Compression Networks for Improved Rectifier Performance," *IEEE Trans. Microw. Theory Techn.*

- [J1] K. Niotaki, A. Collado, A. Georgiadis and J. Vardakas, "5 Watt GaN HEMT Power Amplifier for LTE," *Radioengineering*, pp. 338 344, Apr. 2014.

#### **Conference Publications**

- [C4] K. Niotaki, A. Collado, A. Georgiadis and J. Vardakas, "A dual-band power amplifier based on composite right/left-handed matching networks," *in Proc. 64th IEEE Electron. Compon. Technol. Conf.*, Orlando, FL, 2014, pp. 796-802.

- [C3] K. Niotaki, F. Giuppi, A. Collado, A. Georgiadis and J. Vardakas, "A Broadband Power Amplifier Based on Composite Right/Left-Handed Half-Mode Substrate Integrated Waveguide," *in Proc. Conf. Design Circuits and Integr. Syst.*, Donostia-San Sebastian, 2013, pp. 289 293.

[C2] F. Giuppi, K. Niotaki, A. Collado and A. Georgiadis, "Challenges in energy harvesting techniques for autonomous self-powered wireless sensors," *in Proc. 2013 European Microw. Conf.*, Nuremberg, 2013, pp. 854 - 857.

[C1] K. Niotaki, A. Georgiadis and A. Collado, "Thermal Energy Harvesting for Power Amplifiers," *in Proc. 2013 IEEE Radio and Wireless Symp.*, Austin, TX, 2013, pp. 196 - 198.

#### Talks/Presentations

[P1] K. Niotaki, A. Georgiadis and A. Collado, "Thermoelectric energy harvesting for power amplifiers," *European Union COST IC0803 RF/Microwave Communication Subsystems for Emerging Wireless Technol.*, Belfast, May 2012.

# Contents

| Abstract                                                       | iii   |

|----------------------------------------------------------------|-------|

| Resumen                                                        | v     |

| Acknowledgements                                               | vii   |

| List of Publications                                           | ix    |

| Contents                                                       | xi    |

| List of Tables                                                 | xv    |

| List of Figures                                                | xvii  |

| Notation                                                       | xxvii |

| Abbreviations                                                  | xxxi  |

| 1. Introduction                                                | 1     |

| 1.1 Motivation and Thesis Objectives                           | 1     |

| 1.1.1 Challenges of Radio Frequency (RF) Power Amplifiers      | 2     |

| 1.1.2 Resistance Compression Networks                          | 4     |

| 1.2 Thesis Structure                                           | 6     |

| 2. A Linear GaN HEMT Power Amplifier                           | 11    |

| 2.1 Introduction                                               | 11    |

| 2.2 Design of GaN HEMT Power Amplifier                         | 14    |

| 2.3 Implementation and Characterization of the Power Amplifier | 19    |

| 2.4 Linearity Measurements                                     | 25    |

| 2.4.1 One and Two-Tone Characterization                        | 26    |

| 2.4.2 LTE Environment                                          | 28    |

| 2.5 Chapter Summary                                            | 34    |

| 3. Design of Dual-Band and Broadband Power Amplifiers                | 35        |

|----------------------------------------------------------------------|-----------|

| 3.1 Introduction                                                     | 35        |

| 3.2 A Dual-Band Power Amplifier Based on Metamaterial-Inspired       | Matching  |

| Networks 37                                                          |           |

| 3.2.1 Design of Dual-Band Matching Networks                          | 37        |

| 3.2.2 Design of the Dual-Band Power Amplifier                        | 41        |

| 3.2.3 Experimental Results                                           | 43        |

| 3.3 A Broadband Power Amplifier Based on Metamaterial-Inspired       | Half-Mode |

| SIW Technology                                                       | 48        |

| 3.3.1 Preliminary Nonlinear Analysis of the Power Amplifier          | 48        |

| 3.3.2 HMSIW Sections and Power Amplifier Design                      | 51        |

| 3.3.3 Experimental Results                                           | 52        |

| 3.4 Chapter Summary                                                  | 56        |

| 4. Thermal Energy Harvesting from Power Amplifier Operation          | 57        |

| 4.1 Introduction                                                     | 57        |

| 4.2 Thermoelectric Generators                                        | 59        |

| 4.3 Thermal Model                                                    | 61        |

| 4.4 Experimental Results                                             | 64        |

| 4.5 Multiple TEG Setup                                               | 69        |

| 4.6 Chapter Summary                                                  | 71        |

| 5. Design of Resistance Compression Network based Envelope Amplifier | 73        |

| 5.1 Introduction                                                     | 73        |

| 5.2 Resistance Compression Network Theory                            | 78        |

| 5.3 Envelope Amplifier Design based on RCN                           | 81        |

| 5.3.1 Hybrid Switching Amplifier Topology                            | 81        |

| 5.3.2 Calculation of the Envelope Amplifier Efficiency               | 84        |

| 5.3.3 Design of the RCN based Envelope Amplifier                     | 87        |

| 5.3.4 Implementation and Characterization of the Hybrid Envelope     | Amplifier |

| Topologies                                                           | 89        |

| 5.4 Chapter Summary                                                  | 93        |

| 6. Dual-Band Resistance Compression Networks for Improved            | Rectifier |

| Performance.                                                         | 95        |

| 6.1 Introduction                                                     | 95        |

| 6.2 Dual-Band Resistance Compression Network Theory       | 99        |

|-----------------------------------------------------------|-----------|

| 6.3 Dual-Band RCN based Rectifier                         | 104       |

| 6.3.1 Design Considerations for the Dual-Band RCN based R | Rectifier |

| Topology                                                  | 104       |

| 6.3.2 Design of the Dual Band RCN based Rectifier         | 108       |

| 6.3.3 Final Design of the RCN based Rectifier             | 113       |

| 6.4 Experimental Results                                  | 115       |

| 6.5 Chapter Summary                                       | 120       |

| 7. Conclusions and Future Work                            | 121       |

| 7.1 Conclusions                                           | 121       |

| 7.2 Future Work                                           | 123       |

| Bibliography                                              | 125       |

# List of Tables

| Table 2.1: GaN HEMT power amplifier circuit (Figure 2.3a) component values 16        |

|--------------------------------------------------------------------------------------|

| Table 2.2: Measured and simulated output power, gain, drain efficiency and power     |

| added efficiency of the power amplifier for a fixed input power of 25 dBm at 2.4     |

| GHz and 2.45 GHz. The device is biased with 35 V drain and -3.5 V gate voltage. 25   |

| Table 2.3: Lower and upper carrier to intermodulation ratios for different frequency |

| spacing at 2.4 GHz. The measurements are made for a two-tone input signal of 22      |

| dBm power each. 28                                                                   |

| Table 2.4: Measured Bandwidth and adjacent channel center frequency offset for       |

| LTE signals with different bandwidths [7]                                            |

| Table 2.5: Measured adjacent channel power ratio of the power amplifier for various  |

| bandwidths (5 MHz, 10 MHz, 15 MHz and 20 MHz                                         |

| Table 2.6: Summarized performance of the power amplifier at 2.4 GHz 33               |

| Table 2.7: Comparison of GaN HEMT power amplifiers for P <sub>in</sub> =25 dBm       |

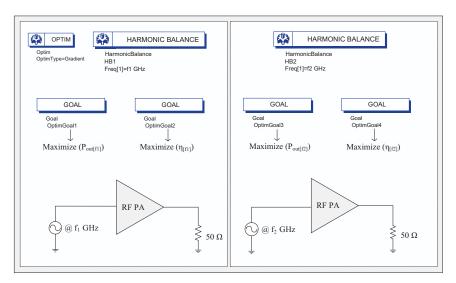

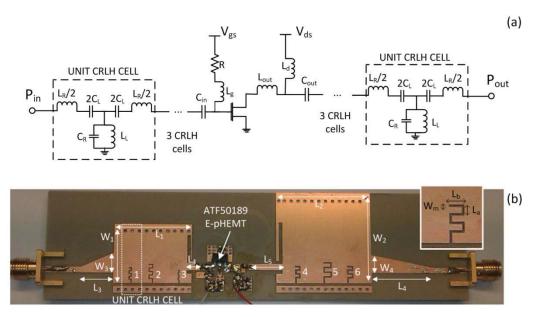

| Table 3.1: Dual-band power amplifier (Figure 3.7a) circuit component values 43       |

| Table 3.2: Comparison of the measured performance of the power amplifier with        |

| other reported dual-band power amplifiers in the literature                          |

| Table 3.3: Power amplifier (Figure 3.20a) component values                           |

| Table 3.4: Geometric dimensions of the input and output matching networks of the     |

| broadband PA (Figure 3.20b)                                                          |

| Table 4.1: Properties of the TGP-751 according to manufacturer datasheet [97] 61     |

| Table 4.2: Electrical and thermal analogy [95]62                                     |

| Table 4.3: Thermal resistances values for the thermal model of Figure 4.6. The                          |

|---------------------------------------------------------------------------------------------------------|

| values of the thermal resistances are based on the manufacturer datasheets [97] 63                      |

| Table 4.4: Power amplifier circuit (Figure 4.7a) component values                                       |

| Table 4.5: Comparison of the simulated and measured results for the thermal energy                      |

| harvesting experiment. 69                                                                               |

| Table 4.6: Measurement results for the thermal energy harvesting experiment with                        |

| one, two (Figure 4.13a) and three TEGs in series (Figure 4.13b)                                         |

| Table 5.1: Commercial components for the implementation of linear and switching                         |

| stage of the EAs of the conventional HSA (Figure 5.10) and the HSA based on RCN                         |

| (Figure 5.11)                                                                                           |

| Table 5.2: Efficiency of the conventional and proposed design for an input signal of                    |

| $V_{dclev}\!\!=\!\!1.53V/V_{pp}\!\!=\!\!1.6V$ and an output load of $R_{PA}\!\!=\!\!39~\Omega$ at 1 MHz |

| Table 5.3: Efficiency of the conventional and proposed design for an input signal of                    |

| $V_{dclev}$ =1.53 $V/V_{pp}$ =1 $V$ and an output load of $R_{PA}$ =33 $\Omega$ at 1 MHz                |

| Table 6.1: Component values used to obtain the data at Figure 6.8 and Figure 6.9.103                    |

| Table 6.2: Component values for the fabricated dual-band RCN based rectifier115                         |

# List of Figures

| Figure 1.1: Average power consumption distribution in base stations. The data are              |

|------------------------------------------------------------------------------------------------|

| taken from [5], [6]                                                                            |

| Figure 1.2: The evolution of the peak to average power ratio of wireless                       |

| communication standards. The data are taken from [8]                                           |

| Figure 1.3: Envelope amplifier topology, where the drain/collector of the RF power             |

| amplifier is represented as a resistance                                                       |

| Figure 1.4: Application of rectifiers in a) a simplified topology of an outphasing             |

| power amplifier with a power recycling network and b) an architecture for energy               |

| harvesting application. 6                                                                      |

| Figure 2.1: Measured waveform of the envelope of a downlink 5 dBm 20 MHz LTE                   |

| signal in the time domain                                                                      |

| Figure 2.2: Classes of transistors. The data come from [3]                                     |

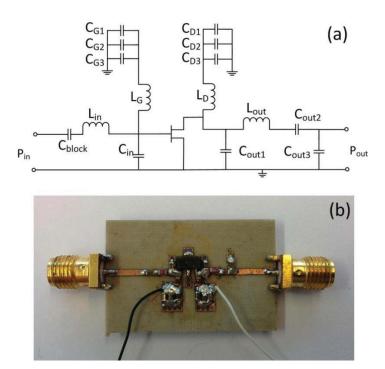

| Figure 2.3: GaN HEMT power amplifier: a) Simulated circuit topology and b)                     |

| fabricated prototype. The fabricated prototype has a total size of 6 cm x 10 cm. The           |

| active device is a GaN HEMT transistor from Cree (CGH40006P) [34] 15                           |

| Figure 2.4: Simplified schematic of the optimization process that minimizes the level          |

| of the nonlinear distortion for a two-tone input signal, using HB analysis in Agilent          |

| ADS software                                                                                   |

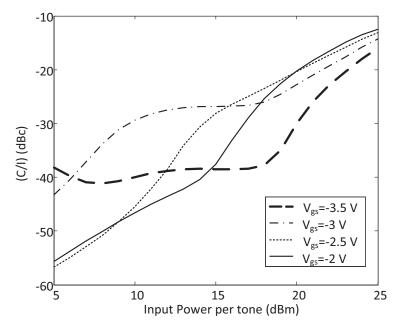

| Figure 2.5: Simulated C/I ratio versus input power level per tone for $V_{gs}$ = -3.5 V,       |

| $V_{gs}$ = -3 V, $V_{gs}$ = -2.5 V and $V_{gs}$ = -2 V. The selected operating frequencies are |

| $f_1$ =2.395 GHz and $f_2$ =2.405 GHz. The results are obtained when the device is biased      |

| with a drain bias of 35 V                                                                      |

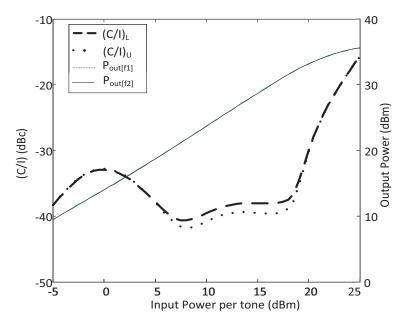

| Figure 2.6: Simulated output power and C/I ratio versus input power level of one of                |

|----------------------------------------------------------------------------------------------------|

| the tones. The selected operating frequencies are $f_1$ =2.395 GHz and $f_2$ =2.405 GHz.           |

| The results are obtained for $V_{ds}$ = 35 V and $V_{gs}$ = -3.5 V                                 |

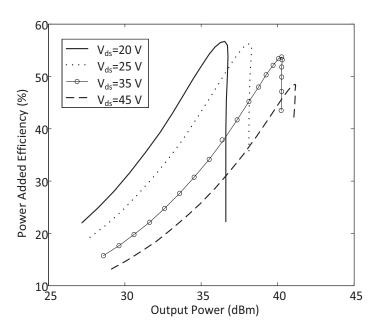

| Figure 2.7: Simulated power added efficiency versus output power for $V_{ds}$ = 20 V,              |

| $V_{ds}$ =25 V, $V_{ds}$ =35 V and $V_{ds}$ =45 V. The power amplifier operates at 2.4 GHz and the |

| selected gate voltage is -3.5 V                                                                    |

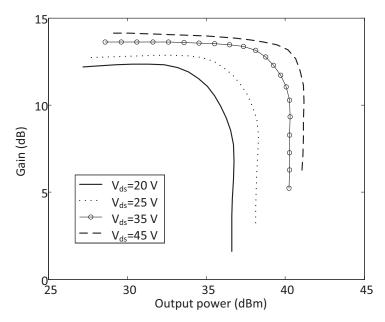

| Figure 2.8: Simulated gain of the power amplifier for different drain voltages (V <sub>ds</sub> =  |

| 20 V, $V_{ds}$ =25 V, $V_{ds}$ =35 V and $V_{ds}$ =45 V) and output power levels. The power        |

| amplifier operates at 2.4 GHz and the selected gate voltage is -3.5 V                              |

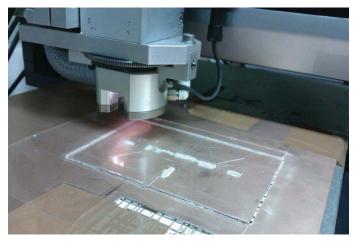

| Figure 2.9: Drilling the vias of the power amplifier using an LPKF Protomat                        |

| C100/HF circuit board plotter [39]                                                                 |

| Figure 2.10: Insertion of the conductive paste through the vias of the board [40] 21               |

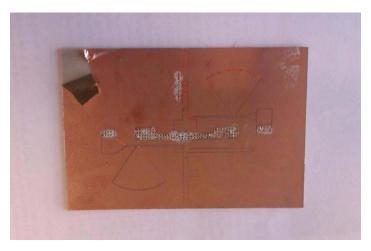

| Figure 2.11: Peeling the copper of the board manually (top view of the PCB) 21                     |

| Figure 2.12: Top view of the layout of the board after the peeling phase shown in                  |

| Figure 2.11. 21                                                                                    |

| Figure 2.13: View of the bottom side of the board after applying thermal paste on it.              |

|                                                                                                    |

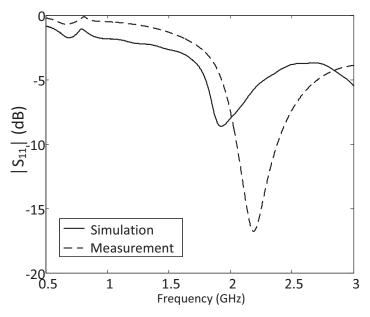

| Figure 2.14: Comparison of simulated (solid line) and measured (dashed line) small-                |

| signal $ S_{11} $ over the frequency range of 0.5 GHz to 3 GHz                                     |

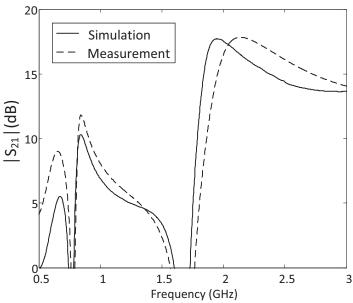

| Figure 2.15: Comparison of simulated (solid line) and measured (dashed line) small-                |

| signal $ S_{21} $ over the frequency range of 0.5 GHz to 3 GHz                                     |

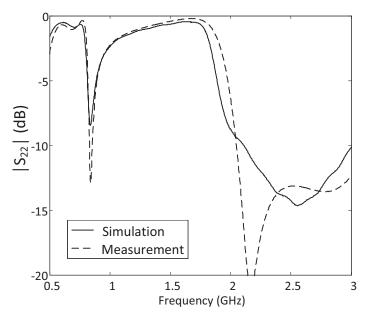

| Figure 2.16: Comparison of simulated (solid line) and measured (dashed line) small-                |

| signal   S <sub>22</sub>   over the frequency range of 0.5 GHz to 3 GHz                            |

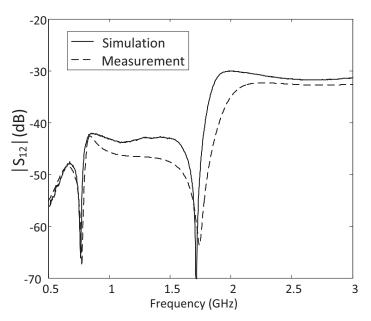

| Figure 2.17: Comparison of simulated (solid line) and measured (dashed line) small-                |

| signal $ S_{12} $ over the frequency range of 0.5 GHz to 3 GHz                                     |

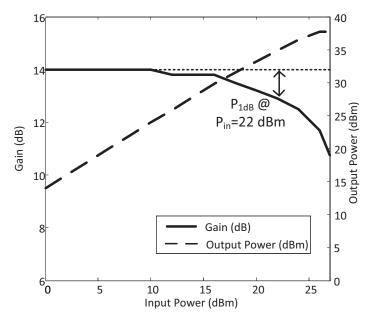

| Figure 2.18: Measured output power and gain for a 2.4 GHz input signal as a                        |

| function of the input power level. The measurements are for $V_{ds}$ =35 V and $V_{gs}$ =-3.5      |

| V                                                                                                  |

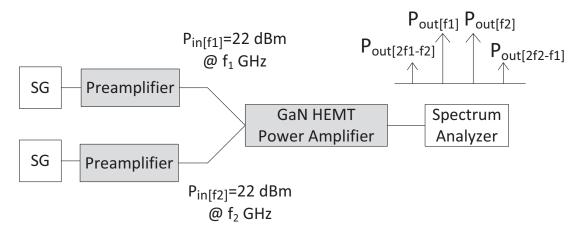

| Figure 2.19: Measurement setup for a two-tone characterization of the PA. The                      |

| device is tested for different frequency spacing at a center frequency of 2.4 GHz 27               |

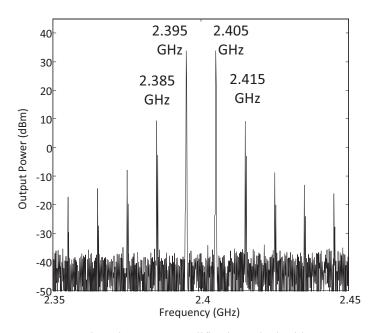

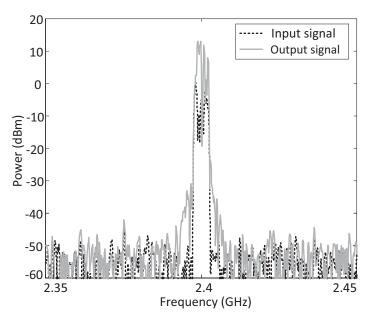

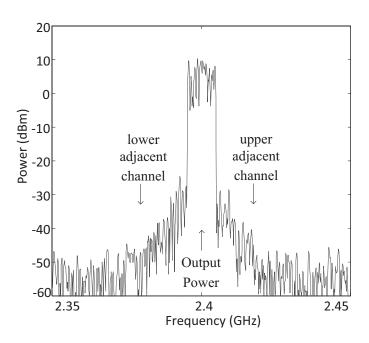

| Figure 2.20: Output spectrum when the power amplifier is excited with a two-tone                   |

| input signal (22 dBm each of them) of a center frequency of 2.4 GHz and spacing of                 |

| 10 MHz. 28                                                                                         |

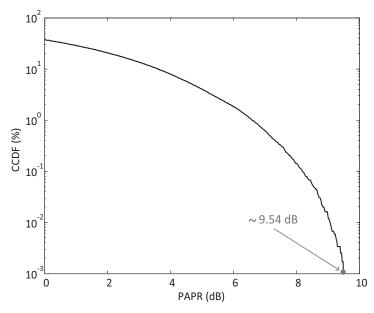

| Figure 2.21: Measured complementary cumulative distribution function of the                                                   |

|-------------------------------------------------------------------------------------------------------------------------------|

| envelope of a downlink LTE 5 dBm signal (BW=10 MHz)                                                                           |

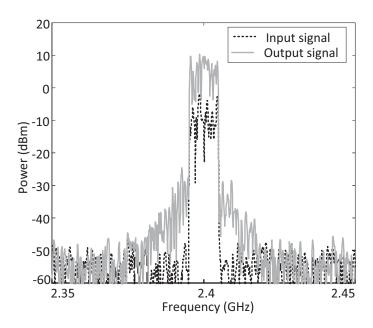

| Figure 2.22: Measured output spectrum for a 5 MHz LTE 2.4 GHz input signal (5                                                 |

| dBm)                                                                                                                          |

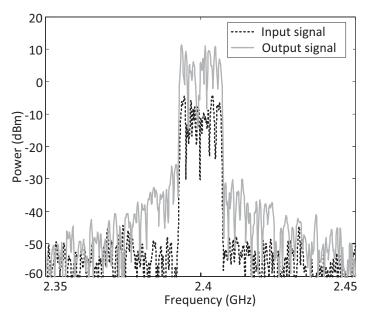

| Figure 2.23: Measured output spectrum for a 10 MHz LTE 2.4 GHz input signal (5                                                |

| dBm)                                                                                                                          |

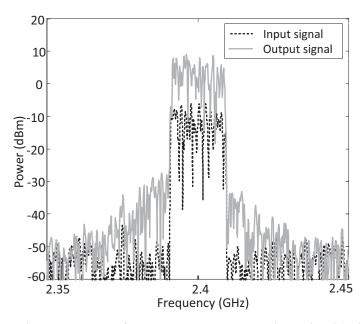

| Figure 2.24: Measured output spectrum for a 15 MHz LTE 2.4 GHz input signal (5                                                |

| dBm)                                                                                                                          |

| Figure 2.25: Measured output spectrum for a 20 MHz LTE 2.4 GHz input signal (5                                                |

| dBm)                                                                                                                          |

| Figure 2.26: Output spectrum of the power amplifier when excited with a 2.4 GHz                                               |

| LTE signal. The input power level is 5 dBm and the bandwidth 10 MHz 32                                                        |

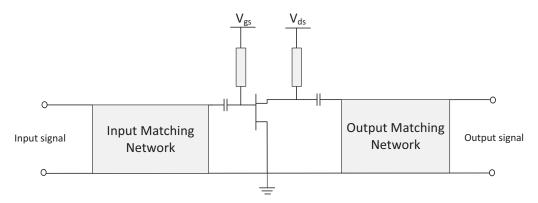

| Figure 3.1: Simplified PA circuit topology that consists of the input and output                                              |

| impedance matching networks, two DC blocking capacitors and the bias of the                                                   |

| transistor                                                                                                                    |

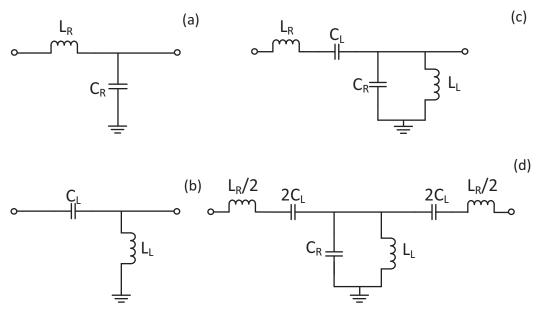

| Figure 3.2: Equivalent circuit model of: a) ideal lumped-element RH TL unit cell, b)                                          |

| ideal lumped-element LH TL unit cell, c) ideal asymmetric lumped-element CRLH                                                 |

| TL unit cell (T-shaped topology) and d) ideal symmetric lumped-element CRLH TL                                                |

| unit cell (T-shaped topology)                                                                                                 |

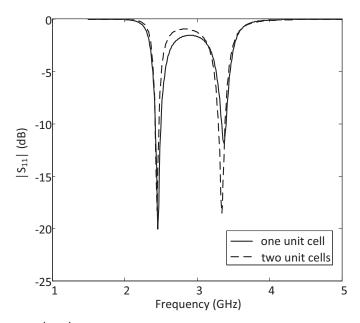

| Figure 3.3: Simulated $\mid S_{11} \mid$ versus operating frequency for two different impedance                               |

| matching networks. 39                                                                                                         |

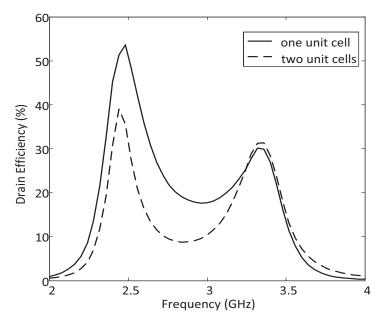

| Figure 3.4: Simulated drain efficiency versus operating frequency ( $P_{in}$ =19 dBm) for                                     |

| two different impedance matching networks                                                                                     |

| Figure 3.5: Simulated gain versus operating frequency ( $P_{in}$ =19 dBm) for two                                             |

| different impedance matching networks                                                                                         |

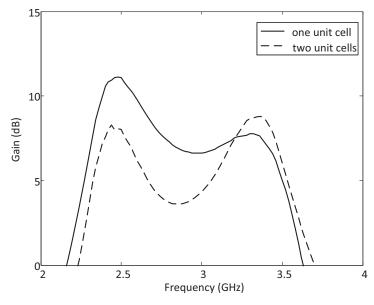

| Figure 3.6: Simplified schematic of the optimization process that results in dual-band                                        |

| frequency response, using HB analysis in Agilent ADS software                                                                 |

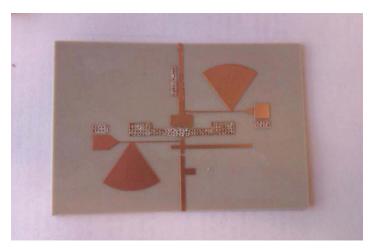

| Figure 3.7: Dual-band power amplifier: a) Schematic of the circuit topology and b)                                            |

| fabricated prototype. The fabricated prototype has a total size of 7 cm by 5 cm. The                                          |

| active device is an enhancement mode pseudomorphic HEMT (E-pHEMT) transistor                                                  |

| (ATF-50189) from Avago                                                                                                        |

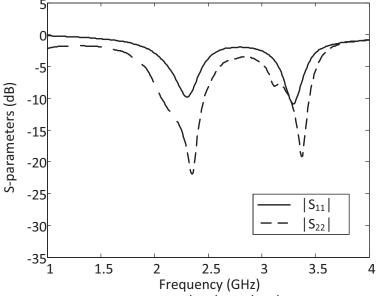

| Figure 3.8: Measured small-signal S-parameters ( $\left \:S_{11}\:\right \:$ and $\left \:S_{22}\:\right $ ) versus operating |

| frequency for an input power of 0 dBm ( $V_{ds}$ =4.5 V and $V_{gs}$ =0.54 V)                                                 |

| Figure 3.9: Measured small-signal S-parameters ( $ S_{21} $ and $ S_{12} $ ) versus operating              |

|------------------------------------------------------------------------------------------------------------|

| frequency for an input power of 0 dBm (Vds=4.5 V and Vgs=0.54 V)                                           |

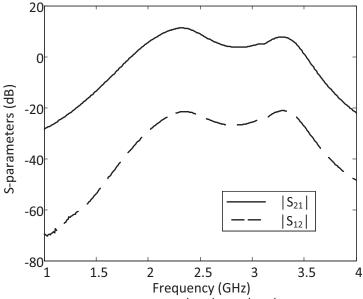

| Figure 3.10: Measured $\mid S_{21} \mid$ versus operating frequency for different gate voltages            |

| ( $V_{gs}$ = 0.45V, $V_{gs}$ = 0.48V and $V_{gs}$ = 0. 54V). The measurements are for input power          |

| $P_{in}$ =0 dBm and $V_{ds}$ = 4.5 V                                                                       |

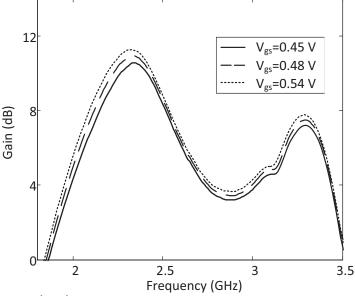

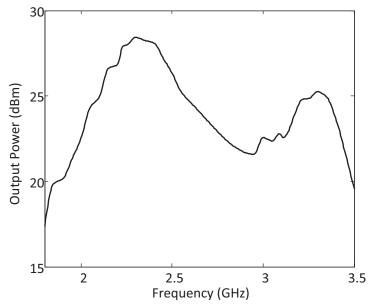

| Figure 3.11: Measured output power level versus operating frequency for an input                           |

| power of 19 dBm. The measurements are for $V_{ds}\!\!=\!4.5~V$ and $V_{gs}\!\!=\!0.54~V45$                 |

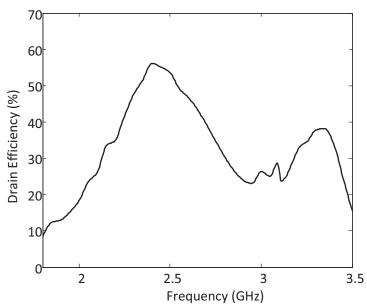

| Figure 3.12: Measured drain efficiency versus operating frequency for an input                             |

| power of 19 dBm ( $V_{ds}$ =4.5 V and $V_{gs}$ =0.54 V)                                                    |

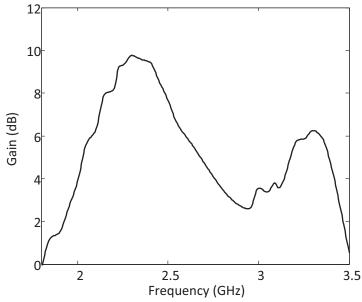

| Figure 3.13: Measured gain versus operating frequency for an input power of 19                             |

| dBm ( $V_{ds}$ =4.5 V and $V_{gs}$ =0.54 V)                                                                |

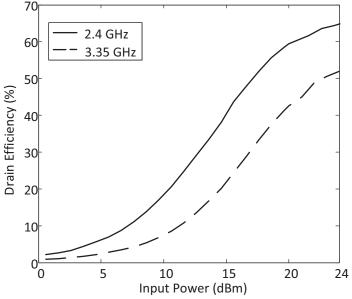

| Figure 3.14: Measured drain efficiency versus input power level for the two                                |

| operating frequencies (2.4 GHz and 3.35 GHz). The measurements are for $V_{\text{ds}}\!\!=4.5$             |

| $V$ and $V_{gs}\!\!=\!\!0.54~V.$                                                                           |

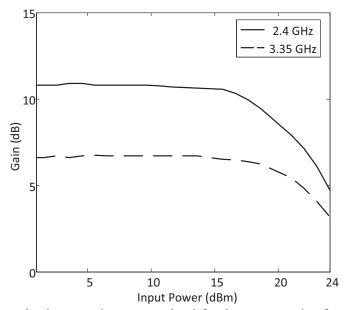

| Figure 3.15: Measured gain versus input power level for the two operating                                  |

| frequencies (2.4 GHz and 3.35 GHz). The measurements are for $V_{\text{ds}}\!\!=\!$ 4.5 V and              |

| $V_{gs} = 0.54 \text{ V}.$ 47                                                                              |

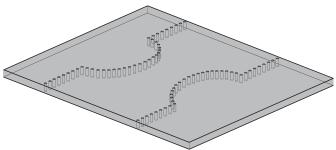

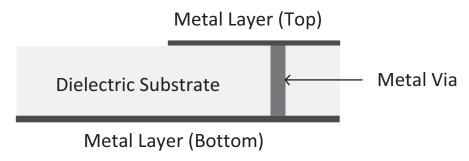

| Figure 3.16: SIW topology. It consists of two rows of conductive cylinders or slots                        |

| embedded in a dielectric substrate                                                                         |

| Figure 3.17: Half-Mode SIW topology                                                                        |

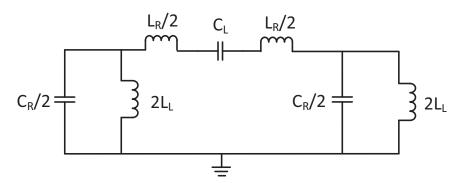

| Figure 3.18: Equivalent circuit model of ideal symmetric lumped-element CRLH unit                          |

| cell (π-shaped topology)                                                                                   |

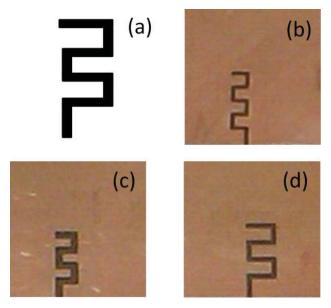

| Figure 3.19: a) Schematic of meander slot and b), c), d) implementation of meanders                        |

| with different dimensions. 50                                                                              |

| Figure 3.20: Broadband power amplifier: a) Schematic of the simulated PA topology                          |

| and b) fabricated prototype based on HMSIW CRLH waveguide. The overall size of                             |

| the prototype is 3 cm by 12 cm                                                                             |

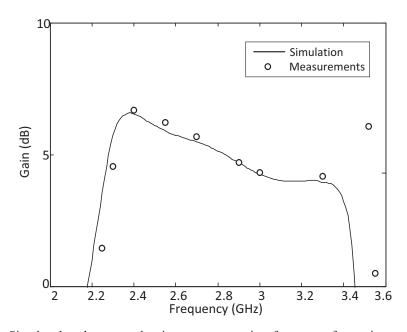

| Figure 3.21: Simulated and measured gain versus operating frequency for an input                           |

| power of 20 dBm. The measurements are for $V_{\text{ds}}\!\!=\!4.2~V$ and $V_{\text{gs}}\!\!=\!\!0.5~V$ 53 |

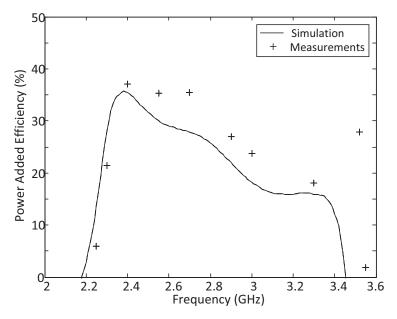

| Figure 3.22: Simulated and measured power added efficiency versus operating                                |

| frequency for an input power of 20 dBm. The measurements are for $V_{\text{ds}}\!\!=4.2~V$ and             |

| $V_{gs}=0.5 \text{ V}.$ 54                                                                                 |

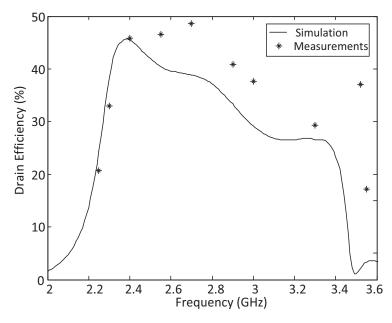

| Figure 3.23: Simulated and measured drain efficiency versus operating frequency for                     |

|---------------------------------------------------------------------------------------------------------|

| an input power of 20 dBm. The measurements are for $V_{ds}$ = 4.2 V and $V_{gs}$ =0.5 V 54              |

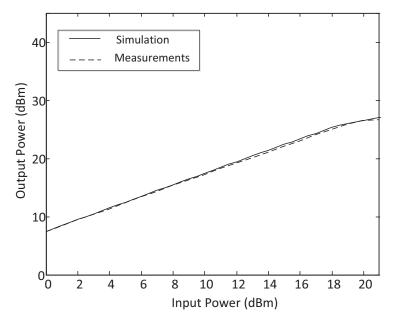

| Figure 3.24: Simulated and measured output power versus input power at 2.4 GHz                          |

| for the broadband PA. The measurements are for $V_{ds}\!\!=\!4.2~V$ and $V_{gs}\!\!=\!\!0.5~V$          |

| Figure 3.25: Simulated and measured PAE at 2.4 GHz operation for the implemented                        |

| PA. The measurements are for $V_{ds} = 4.2 \ V$ and $V_{gs} = 0.5 \ V$ .                                |

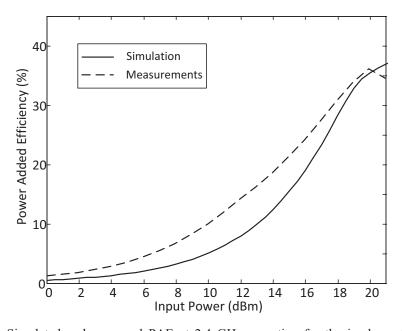

| Figure 4.1: Calculated dissipated power from the operation of efficient power                           |

| amplifiers in the literature [25], [80]-[87]                                                            |

| Figure 4.2: A voltage is generated from the temperature difference across the                           |

| junctions of dissimilar metals/semiconductors (Seebeck effect) [94]                                     |

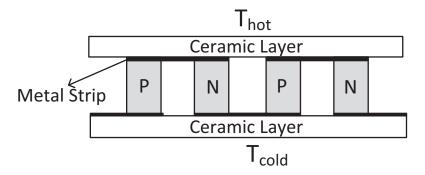

| Figure 4.3: Structure of a thermoelectric generator.                                                    |

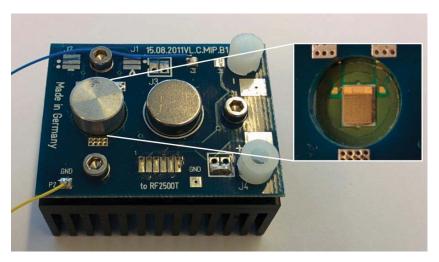

| Figure 4.4: Micropelt thermoharvesting module with integrated TGP, DC-Booster,                          |

| power management and heatsink [97]                                                                      |

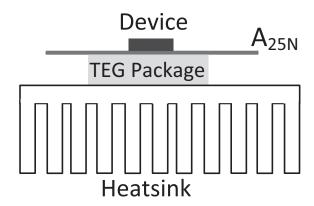

| Figure 4.5: Schematic of the thermal harvesting setup, where the TEG is attached on                     |

| the bottom side of the PCB, at the area below the transistor                                            |

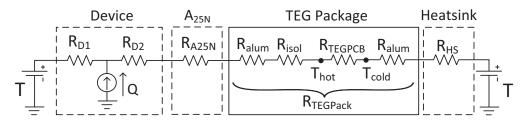

| Figure 4.6: Equivalent thermal circuit for the thermal harvesting setup of Figure 4.5.                  |

| The model consists of the total thermal resistance of the device, the substrate, the                    |

| TEG package and the heatsink                                                                            |

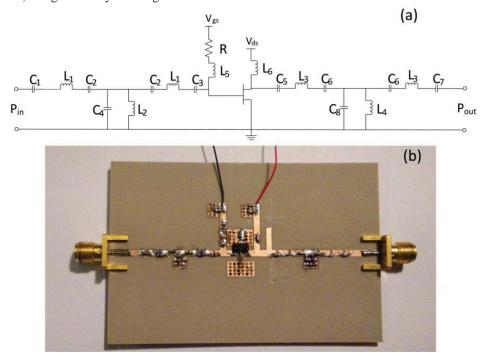

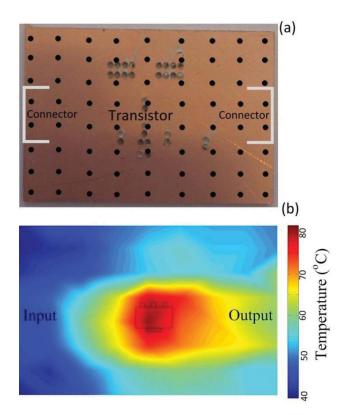

| Figure 4.7: a) Simulated power amplifier circuit schematic and b) fabricated                            |

| prototype. The fabricated prototype has a total size of 3.2 cm by 2.1 cm                                |

| Figure 4.8: Temperature distribution measurement: a) selected measurement points                        |

| on the metal ground of the power amplifier board and b) measured temperature                            |

| distribution. 66                                                                                        |

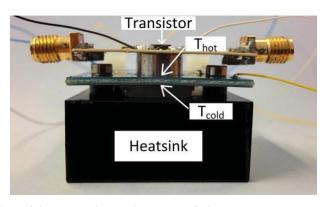

| Figure 4.9: Experimental setup for scavenging the wasted power from a power                             |

| amplifier operation. The TEG is attached on the bottom side of the PA, at the area                      |

| below the transistor. 66                                                                                |

| Figure 4.10: Side view of the energy harvesting setup of Figure 4.9 [97]                                |

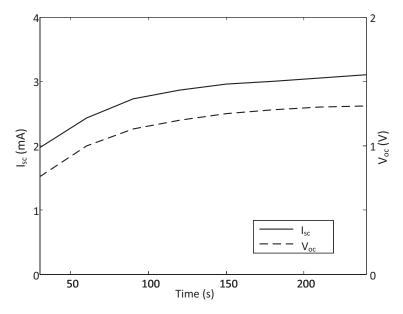

| Figure 4.11: Measured TEG open circuit voltage and short circuit current from the                       |

| experimental setup of Figure 4.9. The maximum measured values are $V_{\text{oc}}$ =1.31 $V_{\text{oc}}$ |

| and $I_{sc}$ =3.1 mA                                                                                    |

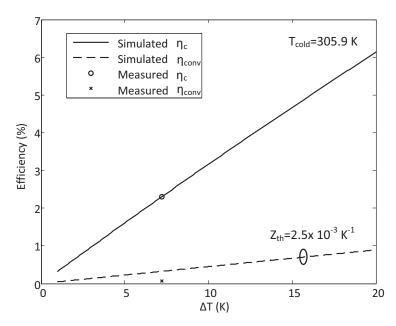

| Figure 4.12: Carnot efficiency and conversion efficiency versus temperature gradient                    |

| at the TEG contacts.                                                                                    |

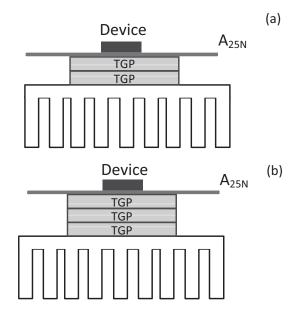

| Figure 4.13: Schematic of the thermal harvesting setup with a) two TEG packages                             |

|-------------------------------------------------------------------------------------------------------------|

| and b) three TEG packages                                                                                   |

| Figure 4.14: Equivalent thermal circuit of the setup of Figure 4.13a and Figure 4.13b.                      |

|                                                                                                             |

| Figure 4.15: Stacked TEG topology for the heat scavenging from a power amplifier                            |

| using two thermoelectric generators in series [97]                                                          |

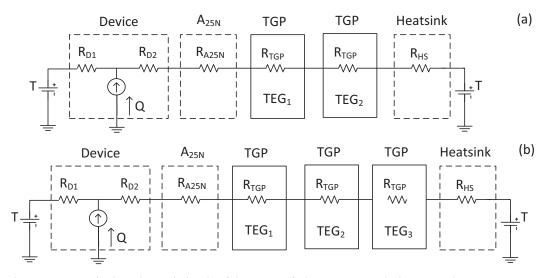

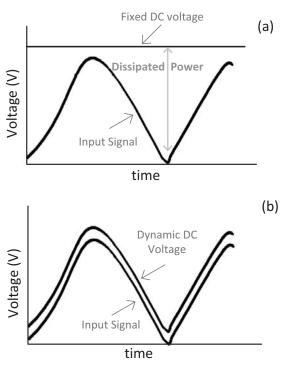

| Figure 5.1: Simplified schematics of a) fixed power supply amplifier topology, b) ET                        |

| topology and c) EER topology                                                                                |

| Figure 5.2: Power dissipation of a power amplifier with: a) fixed supply voltage and                        |

| b) dynamic supply voltage [98]                                                                              |

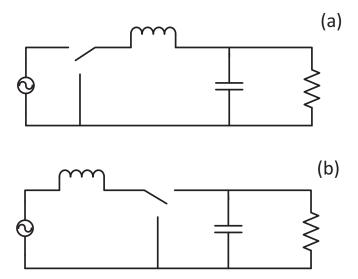

| Figure 5.3: Schematic of DC/DC converters: a) buck converter topology and b) boost                          |

| converter topology                                                                                          |

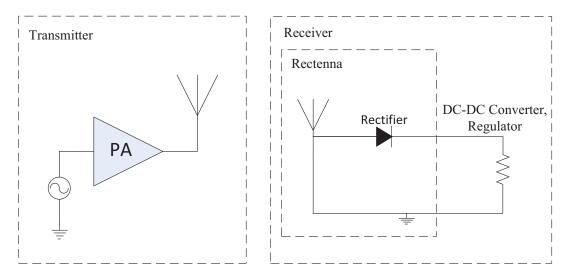

| Figure 5.4: Simplified schematic of multi-sine transmitter and receiver for wireless                        |

| power transfer application                                                                                  |

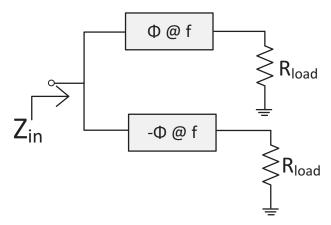

| Figure 5.5: Resistance compression networks structure. Each branch exhibits an                              |

| opposite phase response $(\phi$ and - $\phi)$ of the input impedance at the operating                       |

| frequency. 78                                                                                               |

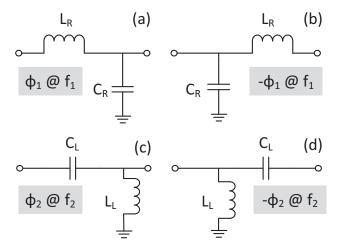

| Figure 5.6: a), b), c), d) Lumped-element LC structures for RCN topologies. Figure                          |

| 5.6b and Figure 5.6d show the rearranged structure of Figure 5.6a and Figure 5.6c. 79                       |

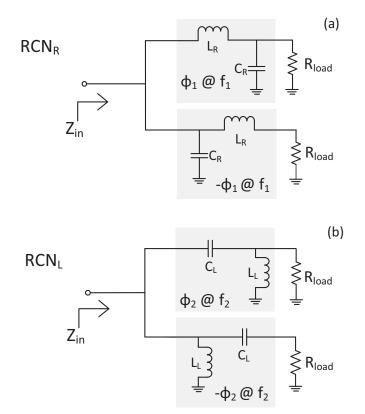

| Figure 5.7: RCN topologies: a) RCN <sub>R</sub> topology and b) RCN <sub>L</sub> topology                   |

| Figure 5.8: Magnitude of the input impedance ( $\mid Z_{in} \mid$ ) of the RCNR and RCNL                    |

| topologies versus load variations ( $R_{load}$ ). The RCN <sub>R</sub> topology operates at 123.9 MHz       |

| while the RCN $_{L}$ operates at 61.9 MHz for the same component values (L $_{R}\!\!=\!\!L_{L}\!\!=\!\!100$ |

| nH and $C_R=C_L=33$ pF).                                                                                    |

| Figure 5.9: Simplified schematic of a power amplifier architecture where the                                |

| drain/collector of the RF PA is connected to the output of an envelope amplifier that                       |

| follows the envelope of the modulated input signal                                                          |

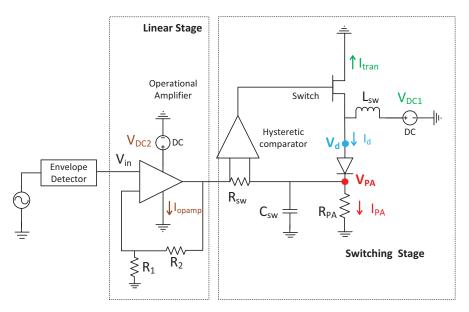

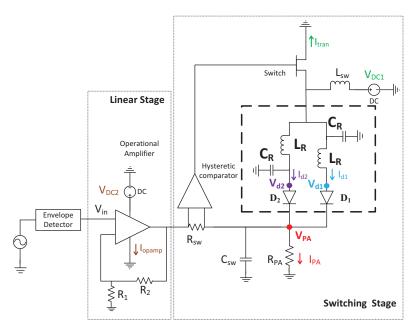

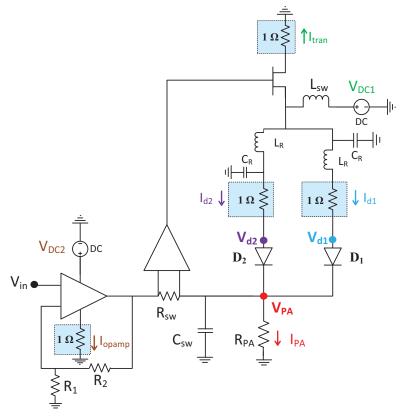

| Figure 5.10: Hybrid envelope switching topology.                                                            |

| Figure 5.11: Proposed hybrid switching amplifier topology. A resistance                                     |

| compression network is placed at the switching stage of the hybrid topology 83                              |

| Figure 5.12: Equivalent simplified schematic of the section of the HSA, where the                           |

| RCN has been placed                                                                                         |

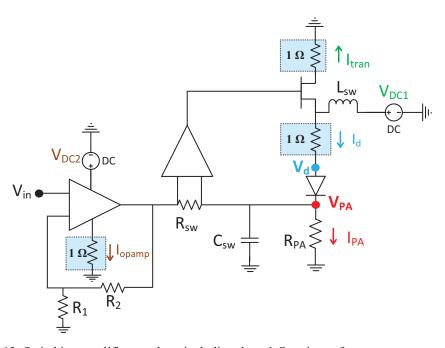

| Figure 5.13: Switching amplifier topology including three 1 $\Omega$ resistors for                               |

|------------------------------------------------------------------------------------------------------------------|

| measurement purposes. 86                                                                                         |

| Figure 5.14: Proposed hybrid switching amplifier topology including four 1 $\Omega$                              |

| resistors for measurement purposes. 87                                                                           |

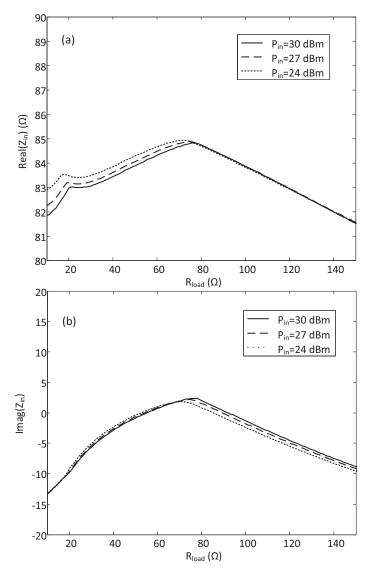

| Figure 5.15: Real and Imaginary part of the input impedance of the RCN shown in                                  |

| Figure 5.11 versus R <sub>load</sub> for various input power levels at 1 MHz                                     |

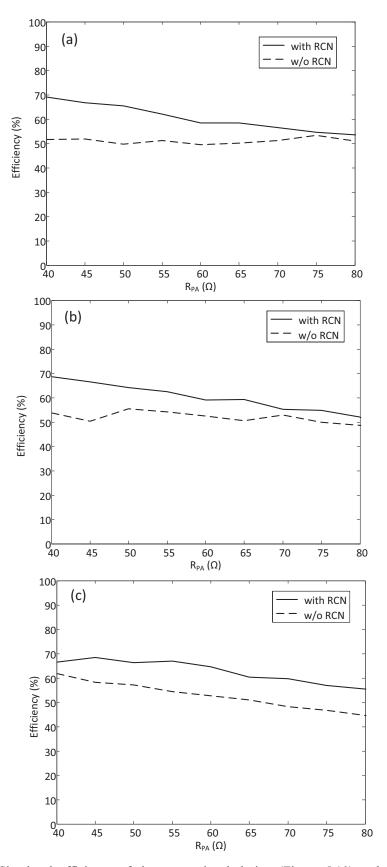

| Figure 5.16: Simulated efficiency of the conventional design (Figure 5.10) and the                               |

| proposed structure (Figure 5.11) at 1 MHz versus output load value ( $R_{PA}$ ) for                              |

| different operating conditions: a) $V_{delev}=1.5V$ , $V_{pp}=1.6$ V and $V_{DC1}=3$ V, b)                       |

| $V_{dclev} = 1.5V$ , $V_{pp} = 1.6~V$ and $V_{DC1} = 2.7~V$ and c) $V_{dclev} = 1.55V$ , $V_{pp} = 1.4~V$ and c) |

| $V_{DC1}=3.2 \text{ V}.$ 91                                                                                      |

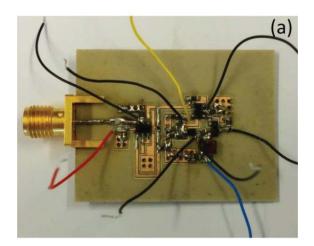

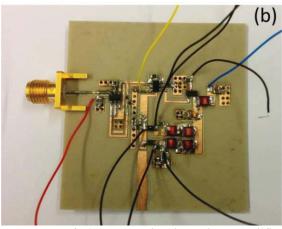

| Figure 5.17: Fabricated prototypes of: a) a conventional envelope amplifier (without                             |

| the resistance compression network) with a total size of 3.8 cm by 2.8 cm and b) are                             |

| envelope amplifier based on a resistance compression network with a total size of                                |

| 4.8 cm by 4.5 cm. 92                                                                                             |

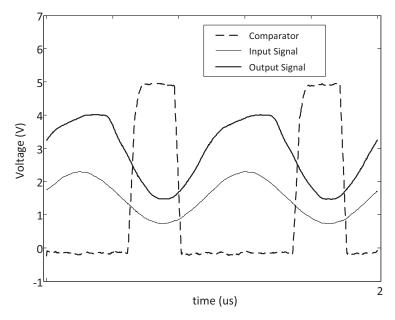

| Figure 5.18: Measured input and output signal waveforms, along with the comparator                               |

| output for the envelope amplifier based on RCN at 1 MHz                                                          |

| Figure 6.1: Application of rectifier circuits in a) an outphasing power amplifier                                |

| topology with a power recycling network and b) energy harvesting applications 96                                 |

| Figure 6.2: Schematic of RF energy harvesting setup where the input power level                                  |

| varies depending on the application, the operating frequency band and the                                        |

| propagation environment. 97                                                                                      |

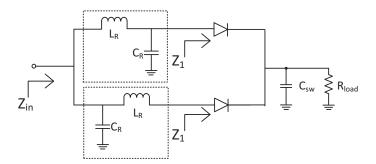

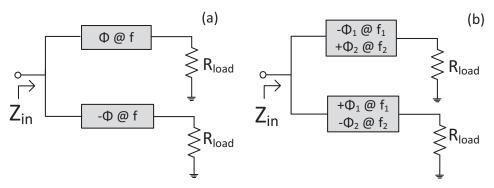

| Figure 6.3: a) Resistance compression networks operating at a single frequency. Each                             |

| branch exhibits opposite phase response ( $\phi$ and $-\phi$ ) at the operating frequency (f) and                |

| b) Dual-band RCNs. 99                                                                                            |

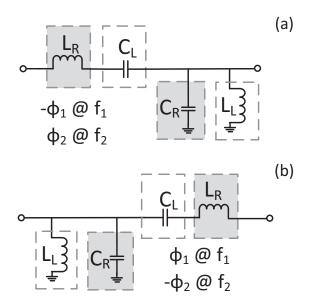

| Figure 6.4: a) Unit circuit cell consisting of a series and shunt LC network and b)                              |

| Rearranged circuit cell (the same network as Figure 6.4a with reversed input and                                 |

| output ports).                                                                                                   |

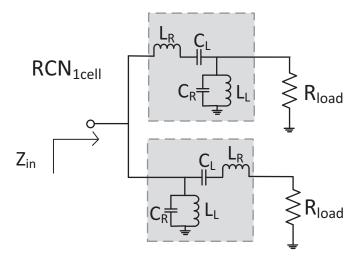

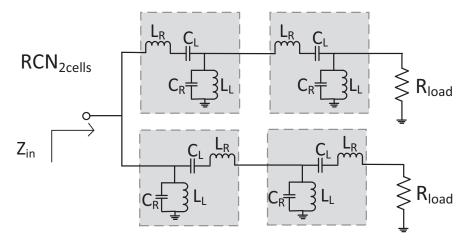

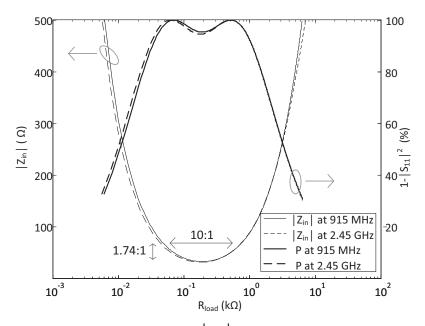

| Figure 6.5: Dual-band resistance compression network implemented with a single                                   |

| circuit cell at each branch. The proposed topology is indicated as $RCN_{1CELL}$ 101                             |

| Figure 6.6: Dual-band resistance compression network. The proposed topology (with                                |

| two unit cells at each branch of the network) is indicated as RCN <sub>2CELLS</sub> 101                          |

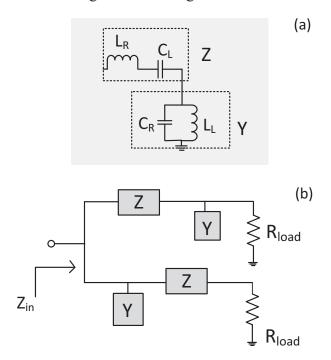

| Figure 6.7: a) Equivalent network for an ideal unit cell represented as a set of                     |

|------------------------------------------------------------------------------------------------------|

| complex impedance (Z) and admittance (Y) and b) Equivalent network of the dual-                      |

| band RCN (RCN <sub>1CELL</sub> ) in terms of complex impedances                                      |

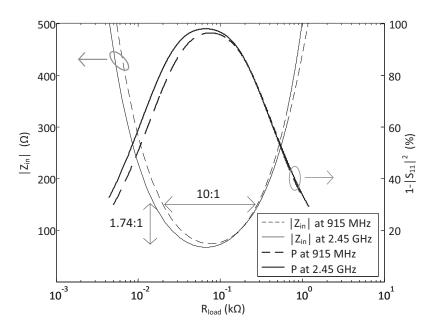

| Figure 6.8: Magnitude of the input impedance ( $\mid Z_{in} \mid$ ) and percentage of the            |

| delivered power to the input of the rectifier for the RCN <sub>1CELL</sub> topology (Figure 6.5)     |

| versus load variations (R <sub>load</sub> )                                                          |

| Figure 6.9: Magnitude of the input impedance ( $\mid Z_{in} \mid$ ) and percentage of the            |

| delivered power to the input of the rectifier for the RCN <sub>2CELLs</sub> topology (Figure 6.6)    |

| versus load variations (R <sub>load</sub> )                                                          |

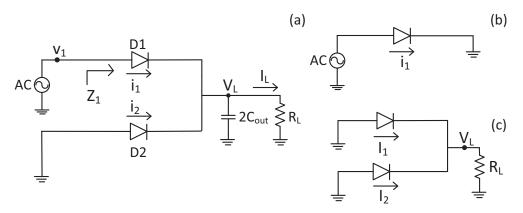

| Figure 6.10: Schematics of the simulated dual-band rectifiers: a) proposed RCN                       |

| based rectifier with $RCN_{1CELL}$ topology, b) proposed RCN based rectifier with                    |

| RCN <sub>2CELLS</sub> topology, c) conventional envelope detector topology 105                       |

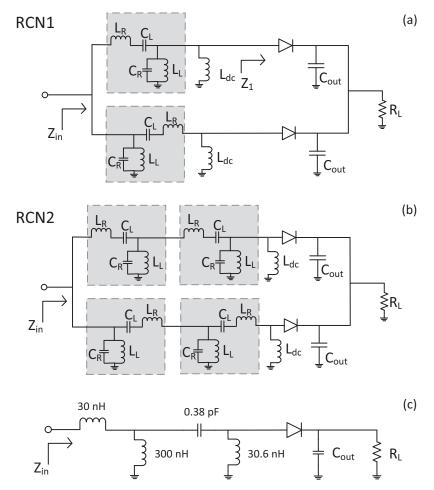

| Figure 6.11: a) Simplified circuit topology of the proposed rectifier topology, b)                   |

| equivalent circuit of the diode (D1) at RF and c) DC equivalent circuit of the                       |

| proposed structure                                                                                   |

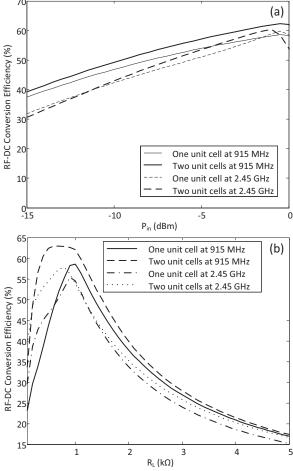

| Figure 6.12: Performance comparison of a RCN based rectifier with a single                           |

| $(RCN_{1CELL}\ topology)$ and two unit cells at each branch of the RCN $(RCN_{2CELLS}$               |

| topology): a) versus input power (for $R_L$ =1 $k\Omega$ ) and b) output load (for $P_{in}$ =0 dBm). |

|                                                                                                      |

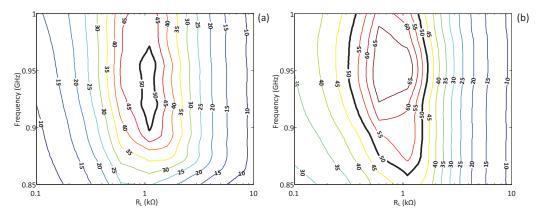

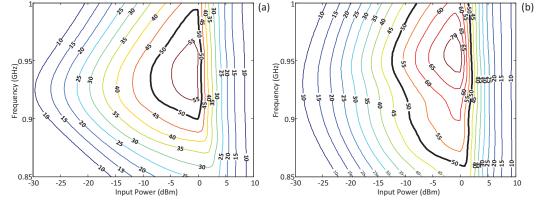

| Figure 6.13: RF-DC conversion efficiency (%) of a) the envelope detector rectifier                   |

| and b) the RCN based rectifier for an input power of 0 dBm at the 915 MHz band.                      |

|                                                                                                      |

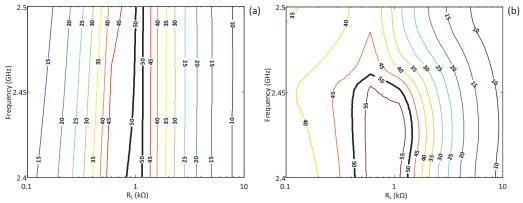

| Figure 6. 14 . RF-DC conversion efficiency (%) of a) the envelope detector rectifier                 |

| and b) the RCN based rectifier for an input power of 0 dBm at the 2.45 GHz band.                     |

|                                                                                                      |

| Figure 6. 15 RF-DC conversion efficiency (%) of a) the envelope detector rectifier                   |

| and b) the RCN based rectifier for $R_L \!\!=\!\! 1~k\Omega$ at the 915 MHz band                     |

| Figure 6.16: RF-DC conversion efficiency (%) of a) the envelope detector rectifier                   |

| and b) the RCN based rectifier for $R_L \!\!=\!\! 1~k\Omega$ at the 2.45 GHz band                    |

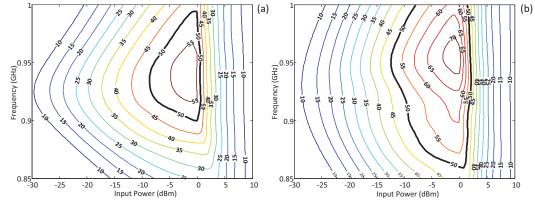

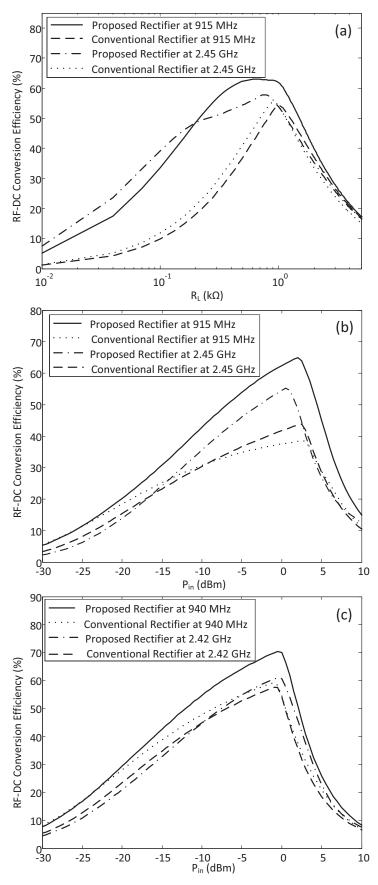

| Figure 6.17: Performance comparison of the conventional envelope detector                            |

| topology and the proposed RCN based rectifier versus a) output load (915 MHz/2.45                    |

| GHz), b) input power level for $R_L$ =0.51 k $\Omega$ (915 MHz/2.45 GHz), and c) input               |

| power level for $R_L$ =1 k $\Omega$ (940 MHz/2.42 GHz)                                               |

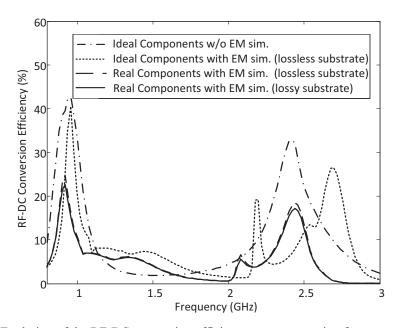

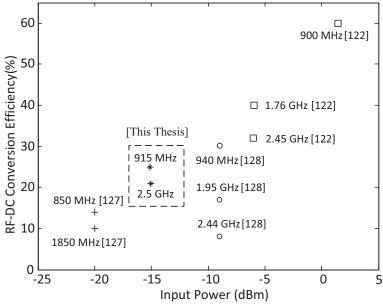

| Figure 6.18: Evolution of the RF-DC conversion efficiency versus operating                                   |

|--------------------------------------------------------------------------------------------------------------|

| frequency for $R_L$ =1 $k\Omega$ and $P_{in}$ =-15 $dBm$ .                                                   |

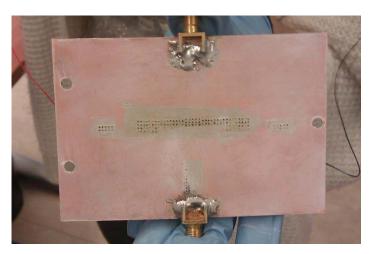

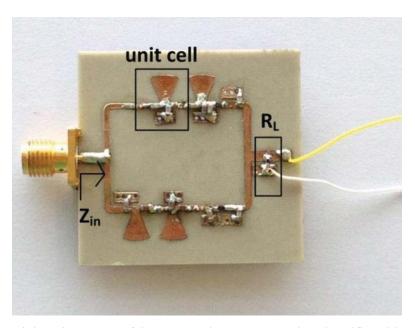

| Figure 6.19: Fabricated prototype of the 915 MHz/2.45 GHz RCN based rectifier                                |

| with a total size of 3.8 cm by 3.5 cm. 115                                                                   |

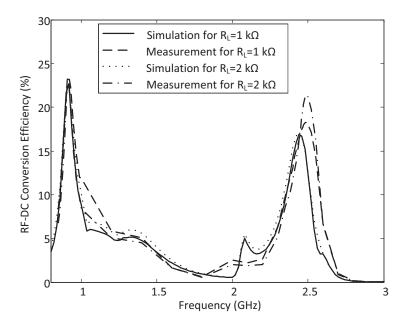

| Figure 6.20: Comparison of simulated and measured RF-DC conversion efficiency                                |

| for an input power of -15 dBm versus operating frequency for two different loads                             |

| values (1 $k\Omega$ and 2 $k\Omega$ ).                                                                       |

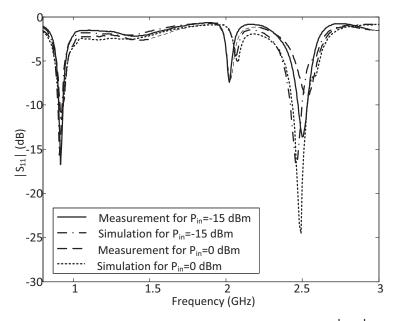

| Figure 6.21: Comparison of simulated and measured reflection coefficient ( $\mid S_{11} \mid$ )              |

| versus operating frequency for two different input power levels (-15 dBm and 0                               |

| dBm) for $R_L$ =2 $k\Omega$ .                                                                                |

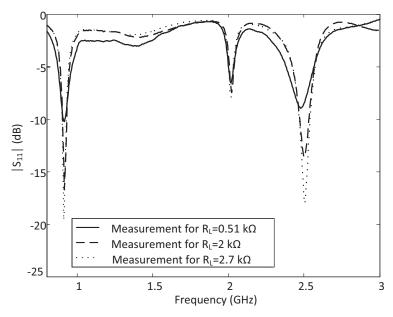

| Figure 6.22: Measured reflection coefficient ( $\mid S_{11} \mid$ ) versus operating frequency for           |

| various output loads (RL= 0.51 k $\Omega$ , 2 k $\Omega$ and 2.7 k $\Omega$ ) for an input power of -15 dBm. |

|                                                                                                              |

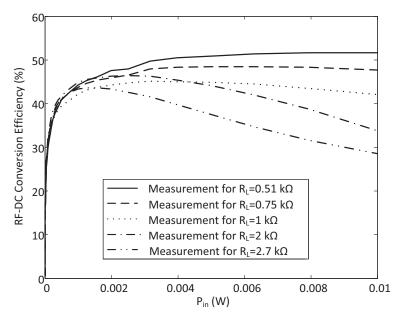

| Figure 6.23: Measured RF-DC conversion efficiency versus input power for various                             |

| load values (0.51 k $\Omega$ , 0.75 k $\Omega$ , 1 k $\Omega$ , 2 k $\Omega$ and 2.7 k $\Omega$ ) at 915 MHz |

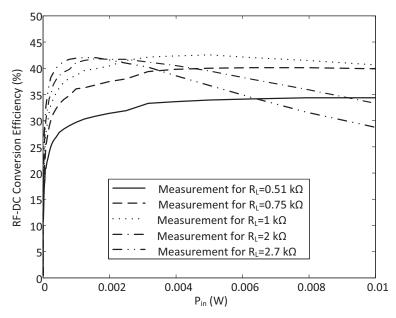

| Figure 6.24: Measured RF-DC conversion efficiency versus input power for various                             |

| load values (0.51 k $\Omega$ , 0.75 k $\Omega$ , 1 k $\Omega$ , 2 k $\Omega$ and 2.7 k $\Omega$ ) at 2.5 GHz |

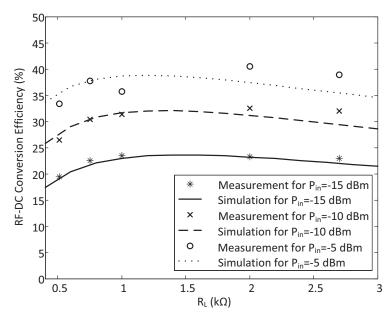

| Figure 6.25: Measured RF-DC conversion efficiency versus output load for a range                             |

| of input power levels from -15 dBm to -5 dBm at 915 MHz                                                      |

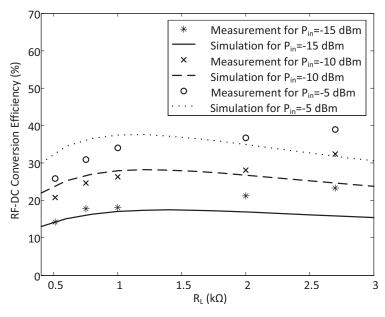

| Figure 6.26: Measured RF-DC conversion efficiency versus load for a range of input                           |

| power levels from -15 dBm to -5 dBm at 2.5 GHz                                                               |

| Figure 6.27: Comparison of state-of-the-art multi-band rectifiers                                            |

## Notation

α Seebeck coefficient

ΔT Temperature gradient

$\Delta \varphi$  Phase shift of a single unit cell

$\Delta f$  Frequency spacing

η Drain efficiency

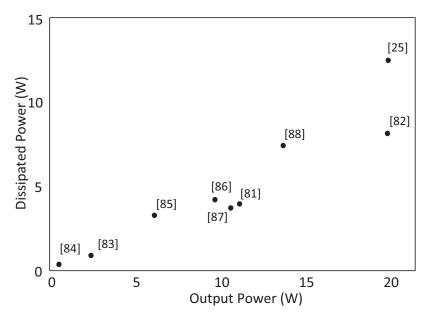

$\eta_c$  Carnot efficiency

$\eta_{conv}$  Conversion efficiency

$\eta_{PAE}$  Power added efficiency

$\eta_{RF-DC}$  RF-DC conversion efficiency

η<sub>tot</sub> Total system efficiency

$\eta_{[f1]}$  Drain efficiency at the low operating frequency (in the case of dual-band

circuit)

$\eta_{[f2]}$  Drain efficiency at the high operating frequency (in the case of dual-band

circuit)

λ Thermal conductivity

σ Electrical conductivity

φ Phase shift

ACPR<sub>L</sub> Lower adjacent channel power ratio ACPR<sub>U</sub> Upper adjacent channel power ratio

$B_n(x)$  Modified Bessel function of order n

$B_0(x)$  Modified Bessel function of order 0

C Electrical capacitance

C<sub>th</sub> Thermal capacitance

C/I Carrier to intermodulation ratio

$(C/I)_L$  Lower carrier to intermodulation ratio  $(C/I)_U$  Upper carrier to intermodulation ratio

f Operating frequency

f<sub>L</sub> Operating frequency of the RCN<sub>L</sub> topology

$f_R$  Operating frequency of the RCN<sub>R</sub> topology

f<sub>1</sub> Low operating frequency (in the case of dual-band circuit)

f<sub>2</sub> High operating frequency (in the case of dual-band circuit)

i<sub>1</sub> Diode current

G Gain

I Current

$I_{ds}$  DC current at the drain of the transistor

I<sub>gs</sub> DC current at the gate of the transistor

I<sub>PA</sub> Output current of the envelope amplifier

I<sub>sc</sub> Short circuit current

I<sub>s1</sub>, I<sub>s2</sub> Diode saturation current

K Stability factor

N Number of unit cells

P<sub>dc</sub> Dissipated power

P<sub>dc harv</sub> DC harvested power

P<sub>diode</sub> Dissipated power from the diode

P<sub>ds</sub> Dissipated power at the drain of the transistor

P<sub>EA</sub> Envelope amplifier output power

$P_{gs}$  Dissipated power at the gate of the transistor

P<sub>in</sub> RF input power

P<sub>in[f1]</sub> Input power at the low operating frequency (in the case of dual-band

circuit)

P<sub>in[f2]</sub> Input power at the high operating frequency (in the case of dual-band

circuit)

P<sub>loss</sub> Total losses from the envelope amplifier operation

P<sub>max</sub> Maximum harvested DC power

P<sub>opamp</sub> Dissipated power from the operational amplifier

P<sub>out</sub> RF output power at the fundamental frequency

P<sub>out L</sub> Total power in the lower adjacent-channel

P<sub>out U</sub> Total power in the upper adjacent-channel

P<sub>out[f1]</sub> Output power at the low operating frequency (in the case of dual-band

circuit)

P<sub>out[f2]</sub> Output power at the high operating frequency (in the case of dual-band

circuit)

P<sub>out[2f1-f2]</sub> Output power at the third-order intermodulation products at the frequency

$(2f_1-f_2)$

P<sub>out[2f2-f1]</sub> Output power at the third-order intermodulation products at the frequency

$(2f_2-f_1)$

P<sub>rf</sub> RF available power

P<sub>tran</sub> Dissipated power from the switching transistor

P<sub>1dB</sub> 1 dB compression point

Q Heat

R<sub>A25N</sub> Thermal resistance of the substrate and the contact

R<sub>D1</sub> Thermal resistance of the device (junction-ambient)

R<sub>D2</sub> Thermal resistance of the device (junction-substrate)

R<sub>elec</sub> Electrical resistance

R<sub>HS</sub> Thermal resistance of the heatsink

R<sub>L</sub> Output load of the rectifier

R<sub>load</sub> Output load of the resistance compression networks

R<sub>PA</sub> Drain/Collector resistance

R<sub>TEGPack</sub> Total thermal resistance of the TEG package

R<sub>TEGPCB</sub> Thermal resistance of the TEG PCB

R<sub>th</sub> Thermal resistance

T Temperature

$T_{cold}$  Temperature at the cold side of the TEG

T<sub>hot</sub> Temperature at the hot side of the TEG

T Mean temperature

V Voltage

V<sub>dclev</sub> DC level of the input signal

V<sub>dc1</sub> Supply voltage of the switching transistor

$V_{dc2}$  Supply voltage of the operational amplifier

$V_{ds}$  Drain voltage  $V_{gs}$  Gate voltage

V<sub>in</sub> Envelope of the transmitted signal

$V_L$  Output DC voltage  $V_{oc}$  Open circuit voltage

V<sub>PA</sub> Output voltage of the envelope amplifier

V<sub>pp</sub> Peak to peak voltage

V<sub>t</sub> Thermal voltage

Y Admittance Z Impedance

$Z_{cap}$  Capacitor reactance

$Z_{in}$  Input impedance  $Z_{ind}$  Inductor reactance

$Z_L$  Characteristic impedance of the RCN<sub>L</sub> topology

$Z_R \hspace{1cm} \hbox{Characteristic impedance of the } RCN_R \ topology$

Z<sub>th</sub> Figure of merit of thermoelectric materials

$Z_1$  Diode input impedance

## **Abbreviations**

ACPR Adjacent Channel Power Ratio

ADS Advanced Design System

AWG Arbitrary Waveform Generator

Bi<sub>2</sub>Te<sub>3</sub> Bismuth Telluride

BJT Bipolar-Junction Transistors

BS Base Station

BW BandWidth

CCDF Complementary Cumulative Distribution Function

CPU Central Processing Unit

CRLH Composite Right/Left-Handed

DC Direct Current

DC-DC Direct Current to Direct Current

DE Drain Efficiency

DPS Dynamic Power Supply

EA Envelope Amplifier

EER Envelope Elimination and Restoration

EH Energy HarvestingEM ElectromagneticET Envelope Tracking

E-pHEMT Enhancement mode Pseudomorphic High Electron Mobility Transistor

FEM Finite Element Method

FET Field Effect Transistor

FOM Figure Of Merit

GaN Gallium Nitride

GPS Global Positioning System

GSM Global System for Mobile communication

HB Harmonic Balance

HEMT High Electron Mobility Transistor

HFSS High Frequency Structural Simulator

HMSIW Half-Mode Substrate Integrated Waveguide

HSA Hybrid Switching Amplifier

IMD InterModulation Distortion

IoE Internet of Everything

IoT Internet of Things

ISM Industrial, Scientific and Medical

LC Inductor-Capacitor

LE Lumped-Element

LH Left-Handed

LSSP Large Signal S-Parameter

LTE Long-Term Evolution

LTE-A LTE-Advanced

MTM Metamaterial

OFDM Orthogonal Frequency Division Multiplexing

PA Power Amplifier

PAE Power Added Efficiency

PAPR Peak-to-Average Power Ratio

PCB Printed Circuit Board

RCN Resistance Compression Network

RF Radio Frequency

RH Right-Handed

SDD Symbolically Defined Device

SG Signal Generator

SIW Substrate Integrated Waveguide

SMD Surface Mounted Device

SoA State-Of-the-Art

TEG ThermoElectric Generator

TGP ThermoGenerator Package

TL Transmission Line

UE User Equipment

UHF Ultra High Frequency

VHF Very High Frequency

VSA Vector Signal Analyzer

Wifi Wireless Fidelity

WiMAX Worldwide Interoperability for Microwave Access

WPT Wireless Power Transfer

2G Second Generation

2.5G Second and a half Generation

3G Third Generation

4G Fourth Generation

# Chapter 1

## Introduction

## 1.1 Motivation and Thesis Objectives

In 1940s (during the World War II), the development of Radar in microwave frequencies introduced the application of microwaves in communication systems [1]. The term microwave signals refers to the alternative current signals that occupy the frequency band of 300 MHz to 300 GHz in the electromagnetic spectrum [1]. Some of the benefits provided by microwave applications are the increased bandwidth and the use of line of the sight propagation with the tradeoff of the increased complexity in the analysis and the design of microwave circuits.

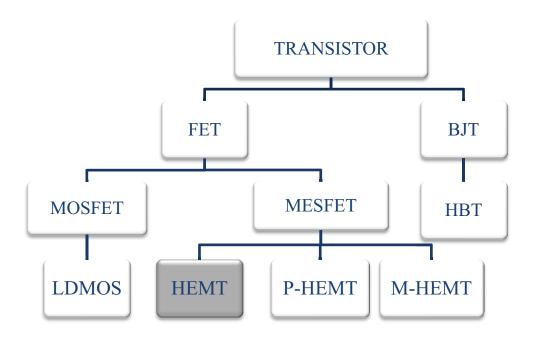

In 1947, John Bardeen, Walter Brattain and William Shockley invented the transistor, which had a significant impact in the evolution of electronics and communication systems [1]-[3]. Transistor has played a key role in the development of critical electronic components, such as power amplifiers (PAs) and oscillators. So far, numerous investigations have been carried out for the evolution of transistors that have already resulted in two main categories: the Bipolar-Junction Transistors (BJTs) and the Field Effect Transistors (FETs) [3], [4]. The best candidate for each application depends on a variety of parameters, including the desired output power level and the operating frequency.

The design of active microwave electronic circuits poses numerous challenges in developing efficient solutions for the current communication systems. Among them stands the design of efficient power amplifier circuits for modern communication standards, multi-band/broadband nonlinear devices and circuits with reduced sensitivity to environmental changes.

In this context, this thesis is focused on investigating novel solutions for the power ampification stage of modern transceivers. In particular, this work can be mainly divided in two parts: i) Chapter 2, 3 and 4 consider different approaches for the design of power amplifier systems and ii) Chapter 5 and 6 investigate resistance compression networks in order to alleviate the problem of impedance changes in power amplifier topologies.

#### 1.1.1 Challenges of Radio Frequency (RF) Power Amplifiers

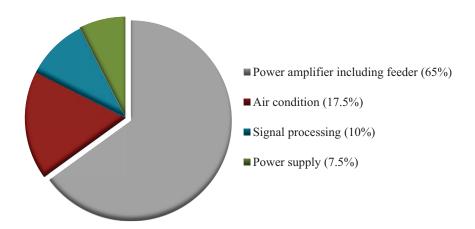

Nowadays, power amplifiers are critical components for the design of base stations (BSs) and mobile user equipment (UE). According to [5], [6], the power amplification process in a base station consumes up to 65 % of the total power consumption, as it shown in Figure 1.1. Therefore, power amplifiers are key components to reduce the power consumption in base stations, contributing to the total system efficiency and reliability. The same applies for the power amplifier components utilized in mobile user equipment, such as the smartphones, where the main goal is to boost the battery life, and thus increase the limited standby/talk time of the handset.

Figure 1.1: Average power consumption distribution in base stations. The data are taken from [5], [6].

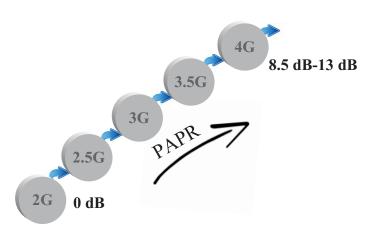

Additionally to the efficiency requirements, modern wireless communication standards imply new constraints in the design of the power amplification stage due to the emergence of new signal modulation schemes. In contrast with the second generation cellular systems (2G), modern modulation techniques produce high bandwidth signals that are characterized with a non-constant envelope. In many cases, the signal envelope (i.e. LTE-Advanced) exceeds the peak-to-average power ratio (PAPR) of 10 dB [7], [8]. Figure 1.2 shows how the peak-to-average power ratio of communication standards has evolved from the 2G to 4G systems. In order to efficiently amplify such signals, the power amplifier should operate with a good efficiency over a wide range of input power levels. Additionally to the high efficiency requirements, linearity has also become a primary concern and the power amplifier should operate at its back off power region. Thus, there is an inherent tradeoff between linearity and efficiency in modern communication systems.

Figure 1.2: The evolution of the peak to average power ratio of wireless communication standards. The data are taken from [8].

Simultaneously, the emergence of new communication standards requires transceivers capable of operating at multiple frequency bands, especially in the case of portable devices where the size of the device is of great importance. To this end, the design of multi-band and broadband PAs is a major challenge that may allow the operation of different standards in the same equipment and thus lead to cost-effective and compact devices. The major challenge that arises from the design of multi-band power amplifiers is the implementation of the impedance matching networks that should meet similar behavior at two frequency bands.

Taking into account the significance of the power amplification process in modern transceivers and the associated design challenges as part of the total system performance, Chapters 2, 3 and 4 deal with the introduction of novel power amplifier systems. In particular, Chapters 2 and 3 are mainly focused on investigating power amplifier topologies for modern communication systems with the design and characterization of various PAs topologies. In Chapter 4, a novel way to exploit the dissipated power from the power amplification process, using a commercial thermoelectric generator and its conversion to useful DC power is proposed.

#### 1.1.2 Resistance Compression Networks

Microwave circuits are usually designed for specific operating conditions, including frequency of operation, input power level and fixed output load. In many cases, the design of multi-band or broadband matching networks is needed for the implementation of multi-band and broadband microwave circuits. The design of such impedance matching networks is a complex task in which the desired tradeoff between the performances at the operating frequencies should be considered.

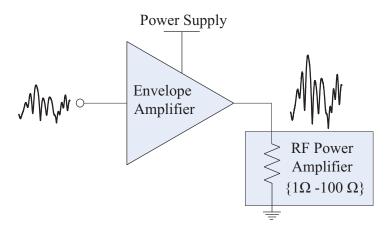

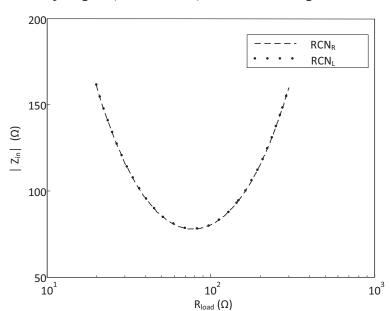

Although the nonlinear devices are usually optimized for specific operating conditions, their input power level and/or the output load usually vary due to the changes in the surrounding environment. For instance, the design of envelope amplifier circuits for dynamic power supply schemes is a major issue due to the time-varying operating conditions. In this case, the envelope amplifier should be designed to operate for a time-varying load that represents the RF power amplifier (typically in the range of 1  $\Omega$  - 100  $\Omega$  [8]), as Figure 1.3 shows. Therefore, it is a challenging task to keep the efficiency of the envelope amplifier high for a wide range of output load values.

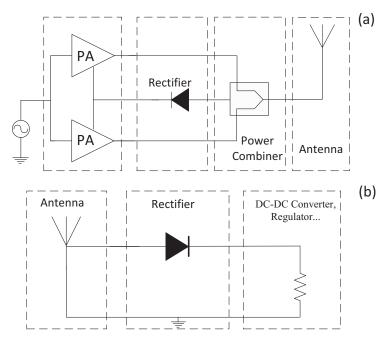

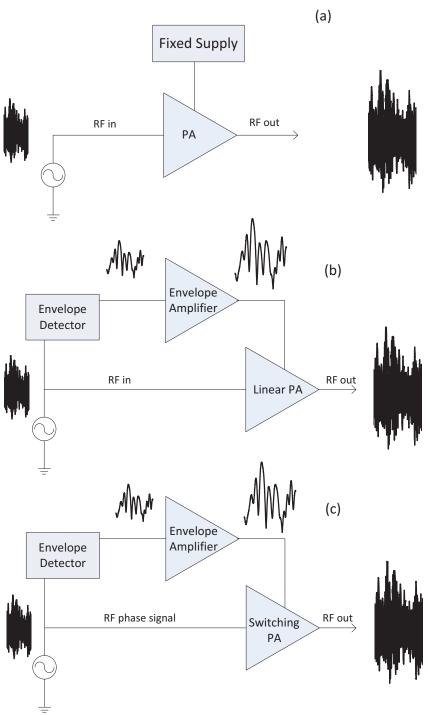

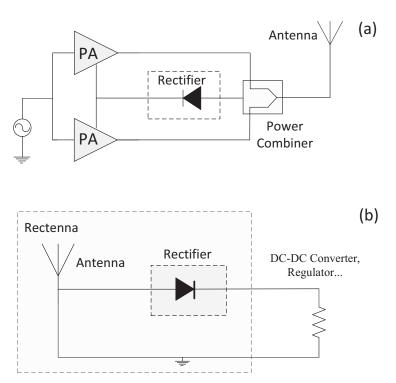

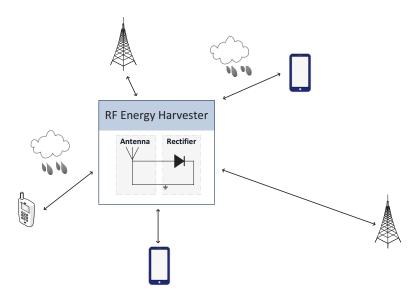

The same challenge applies for the design of rectifier circuits for outphasing power amplifier architectures (with a power recycling network) and for energy harvesting applications. In outphasing PAs, the isolation resistance of the power combiner circuity can be replaced with a rectifier topology in order to recover the dissipated power (Figure 1.4a). In such a topology, an impedance variation between the ports of the power combiner results in an impedance mismatch and non-perfect isolation between the RF power amplifier outputs [9]. Thus, the design of rectifier

circuits with reduced sensitivity to the surrounding environment conditions is of great concern in order to improve the isolation between the RF PAs and thus the performance of the outphasing energy recovery amplifier.

Figure 1.3: Envelope amplifier topology, where the drain/collector of the RF power amplifier is represented as a resistance.

In the same way, the input power of rectifiers for energy harvesting (EH) applications is not constant since the availability of the harvested power level depends on the application scenario. Such an input power variation results in an input impedance change at the input of the diode. Furthermore, the output of the rectifier is usually connected to a time-varying load (such as a DC-DC converter) that also results in an input impedance change at the input of the rectifying device (Figure 1.4b).

The impedance mismatch caused by such environmental changes results in degraded performance. Thus, the design of rectifiers with reduced sensitivity to the surrounding environment conditions is of great importance. An even more challenging task is the design of multi-band microwave circuits with reduced sensitivity to such changes.

In order to alleviate the problem of such impedance changes in microwave circuits, special consideration should be paid in the design of the impedance matching networks. Recently, the concept of resistance compression network (RCN) has been introduced as a novel kind of matching networks that alleviates the sensitivity of microwave circuits to environmental changes [10].

As part of this work, novel impedance matching networks for power amplifier topologies are proposed. Chapter 5 considers novel resistance compression networks

for the design of envelope amplifier circuits, while Chapter 6 proposes dual-band resistance compression topologies that find successful application in rectifier circuits for power recycling networks in outphasing PA systems.

Figure 1.4: Application of rectifiers in a) a simplified topology of an outphasing power amplifier with a power recycling network and b) an architecture for energy harvesting application.

#### 1.2 Thesis Structure

The contribution of this thesis is divided in two parts:

- I. The first part mainly deals with the power amplification process which dominates the power consumption in base stations and portable devices. In Chapter 2 and Chapter 3, the design of power amplifier topologies for modern transceivers is proposed, while an approach to exploit their dissipated power and convert it to useful DC power is analyzed in Chapter 4.

- II. The second part introduces the design of resistance compression networks for PA architectures, such as envelope tracking topologies and outphasing energy recovery power amplifiers. In particular, the concept of dual-band RCNs is introduced, while the resistance compression properties are applied in the design of i) an envelope amplifier topology

(Chapter 5) and ii) a dual-band rectifier (Chapter 6). Such a dual-band RCN based rectifier can find successful application in RF energy harvesting applications and wireless power transfer scenarios, where the rectifier has to operate with highly time-varying conditions.

The thesis is divided in seven Chapters. A brief description of each Chapter is given at the rest of this Section.

#### CHAPTER 2

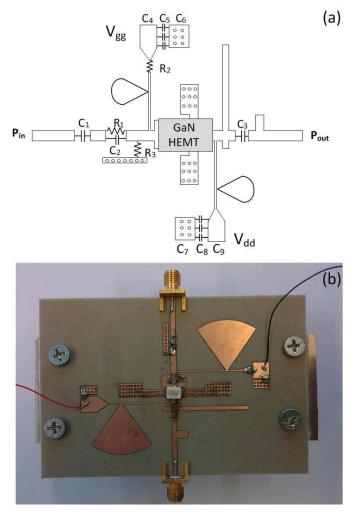

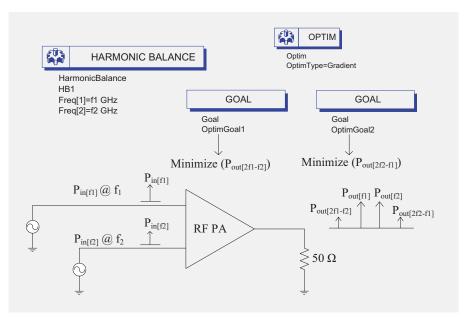

Chapter 2 considers the design of a linear stand-alone power amplifier capable of operating with modern communications signals that are characterized with time-varying envelopes. A GaN HEMT transistor is selected for the design and the implementation of the power amplifier. The linearity of the proposed topology is validated with different input signals. In order to maximize the efficiency of the proposed circuit, the concept of applying the RF power amplifier in an envelope tracking (ET) architecture is also considered. The contributions of Chapter 2 were published in the Radioengineering journal.

K. Niotaki, A. Collado, A. Georgiadis and J. Vardakas, "5 Watt GaN HEMT Power Amplifier for LTE," *Radioengineering*, pp. 338 - 344, Apr. 2014.

#### CHAPTER 3

Multi-band and broadband power amplifiers are crucial components to employ different communication standards in the same equipment. Chapter 3 considers the design of a 2.4 GHz/3.35 GHz power amplifier based on the use of Composite Right/Left-Handed (CRLH) unit cells as the impedance matching networks of the topology. In this Chapter, the approach of designing a broadband (from 2.3 GHz to 3.5 GHz) power amplifier based on the same concept is also examined. The current design investigates the implementation of CRLH unit cells in Substrate Integrated Waveguide (SIW) technology. The contributions of Chapter 3 were presented in the 2012 Conference on Design of Circuits and Integrated Systems and in the 2013 IEEE Electronic Components and Technology Conference.

- K. Niotaki, F. Giuppi, A. Collado, A. Georgiadis and J. Vardakas, "A Broadband Power Amplifier Based on Composite Right/Left-Handed Half-Mode Substrate Integrated Waveguide," in Proc. Conf. Design Circuits and Integr. Syst., Donostia-San Sebastian, 2013, pp. 289 293.

- K. Niotaki, A. Collado, A. Georgiadis and J. Vardakas, "A dual-band power amplifier based on composite right/left-handed matching networks," in Proc. 64th IEEE Electron. Compon. Technol. Conf., Orlando, FL, 2014, pp. 796-802.

#### CHAPTER 4

Chapter 4 considers the potential of exploiting the dissipated power from the power amplifier operation. A simplified thermal model that predicts the amount of DC power that can be obtained from a specific thermal harvesting scenario that includes a power amplifier is proposed. A set of experiments are carried out to predict the amount of the harvested DC power from a power amplifier circuit with a dissipated power of 1.37 Watt. The contributions of this Chapter were presented in the 2012 COST IC0803 RF/Microwave Communication Subsystems for Emerging Wireless Technologies workshop, the 2013 IEEE Radio and Wireless Week conference and the 2013 IEEE European Microwave Conference.

- K. Niotaki, A. Georgiadis and A. Collado, "Thermoelectric energy harvesting for power amplifiers," 8th COST IC0803 RF/Microwave Communication Subsystems for Emerging Wireless Technologies Group Meeting and Workshop, Belfast, May 2012.

- K. Niotaki, A. Georgiadis and A. Collado, "Thermal Energy Harvesting for Power Amplifiers," in Proc. 2013 IEEE Radio and Wireless Symp., Austin, TX, 2013, pp. 196 - 198.

- F. Giuppi, K. Niotaki, A. Collado and A. Georgiadis, "Challenges in energy harvesting techniques for autonomous self-powered wireless sensors," *in Proc. 2013 European Microw. Conf.*, Nuremberg, 2013, pp. 854 857.

#### CHAPTER 5

Chapter 5 investigates a method to improve the performance of an envelope amplifier circuit by adding a resistance compression network (RCN) at the switching stage of a hybrid envelope amplifier topology. A novel way to achieve resistance compression is introduced and applied for the design of the envelope amplifier. In order to evaluate the performance of the proposed design, a conventional hybrid envelope amplifier is also designed and fabricated. The considered design exhibits reduced sensitivity to the environmental conditions and improved performance in comparison with a conventional topology without resistance compression network. The contributions of this Chapter will be submitted in a journal.

K. Niotaki, A. Georgiadis, A. Collado and J. Vardakas, "Resistance Compression Networks for Improved Envelope Amplifier Performance," (in preparation).

#### CHAPTER 6

In Chapter 6, the concept of dual-band resistance compression networks is introduced and applied to the design of a rectifier circuit with improved performance. The operation principles of these dual-band matching networks are presented in detail. The proposed dual-band RCN can be used as the matching network located between the antenna and the rectifying element of a dual-band rectifier for energy harvesting applications or as part of an outphasing energy recovery power amplifier architecture. A dual-band (915 MHz / 2.45 GHz) rectifier based on RCN is designed and characterized showing improved performance in comparison with a conventional dual-band envelope detector by exhibiting improved RF-DC conversion efficiency and reduced sensitivity versus output load and input power variations. The contributions of this Chapter were submitted in the IEEE Transactions on Microwave Theory and Techniques.

K. Niotaki, A. Georgiadis, A. Collado and J. Vardakas, "Dual-Band Resistance Compression Networks for Improved Rectifier Performance", IEEE Trans. Microw. Theory Techn. (Accepted for Publication).

#### CHAPTER 7

Chapter 7 concludes the dissertation considering some potential research directions for future development.

# Chapter 2

# A Linear GaN HEMT Power Amplifier

#### 2.1 Introduction

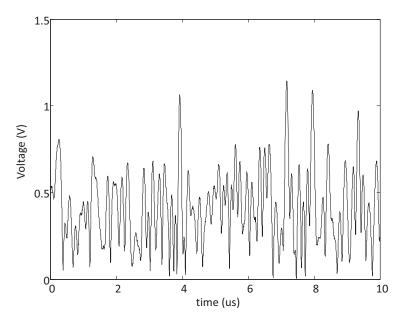

The increasing demand for radio frequency (RF) power amplifiers (PAs) in communication systems has led to enormous research efforts towards the development of reliable and low-cost circuit designs with the best tradeoff between linearity and efficiency. As communication systems evolve to higher data rates the modulation schemes generate complex signals that are characterized by non-constant envelopes with high peak-to-average power ratio (PAPR). Modern modulation schemes in 4G signals, such as Long-Term Evolution (LTE), are characterized with a PAPR that exceeds the value of 10 dB [8]. For instance, the PAPR of a Long-Term Evolution (LTE) signal is in the range of 8.5 dB to 13 dB [8]. Figure 2.1 shows the complex waveform of the envelope of a 5 dBm LTE downlink signal with a bandwidth (BW) of 20 MHz.

The high PAPR signals should be amplified linearly to avoid the signal distortion and thus the power amplifier should operate below the saturation at back off. To improve the efficiency in the back off region, several efficiency enhancement techniques have already been proposed in the literature, including the envelope tracking (ET) technique [7], [11], [12]. The ET topology consists of an RF PA operating at its linear region and a dynamic power supply (DPS) that adjusts the

power supply voltage provided to the amplifier according to the input power level. Several ET systems have been proposed in the literature recently [13]-[18].

Figure 2.1: Measured waveform of the envelope of a downlink 5 dBm 20 MHz LTE signal in the time domain.

The design of the PA usually starts with the selection of the proper device and the set of specifications. So far, various structures of transistors have been developed. Figure 2.2 shows the main classes of power devices, including the Bipolar-Junction Transistors (BJTs) and the Field Effect Transistors (FETs) transistor technologies. The best candidate for each application depends on a variety of parameters, including the desired output power level and operating frequency. Among the candidates for ET power amplifiers for base stations (BSs) stands the design of gallium nitride (GaN) high electron mobility transistor (HEMT) RF power amplifiers because of the inherent advantages of high breakdown voltage, high efficiency, high power density and large bandwidth [19]-[21].