Copyright

by

Yujia Zhai

2014

# The Dissertation Committee for Yujia Zhai Certifies that this is the approved version of the following dissertation:

# **Novel 3-D IC Technology**

| Committee:                      |  |  |

|---------------------------------|--|--|

|                                 |  |  |

| Sanjay Banerjee, Supervisor     |  |  |

| Court C. William Co. Samurian   |  |  |

| Grant C. Willson, Co-Supervisor |  |  |

| Frank Register                  |  |  |

| Rajesh Rao                      |  |  |

| Emanuel Tutuc                   |  |  |

# **Novel 3-D IC Technology**

by

Yujia Zhai, B.S.; M.S.E

## Dissertation

Presented to the Faculty of the Graduate School of

The University of Texas at Austin

in Partial Fulfillment

of the Requirements

for the Degree of

**Doctor of Philosophy**

The University of Texas at Austin MAY, 2014

Dedicated to

My family

### Acknowledgements

I would like to thank all the people who have helped and inspired me during my Ph.D. I want to express my deepest gratitude to my advisor, Dr. Sanjay Banerjee, for his guidance, assistance, and support, during my research and study. Over the past years his mentorship has been far beyond science and discovery: he has taught me not only the professional knowledge but also integrity, persistence and excellence. I have been fortunate enough to have his supervision during my Ph.D. studies.

I also appreciate my co-advisor, Dr. Grant C. Willson, for his constant advice and encouragement during my graduate study. The valuable discussions always inspired me. Without his knowledge and assistance this study would not have been successful.

I would like to acknowledge my other committee members, Dr. Frank Register, Dr. Emanuel Tutuc and Dr. Rajesh Rao for serving as the dissertation committee members.

I also appreciate the support from Applied Novel Device, Inc, especially Leo Mathew. His suggestions and technical support made this Ph.D. work better.

Special thanks go to my research team members. I really appreciate the help and suggestions from the senior group members: Dr. Shan Tang, Dr. Mustafa Jamil, Dr. Fahmida Ferdousi and Dr. Michael Ramon. They trained me on device fabrication, and taught me the electrical characterization skills. I also appreciate all the valuable support from the current group members.

All colleagues at the Microelectronics Research Center made it a friendly place to work. In particular, I would like to thank Aiting Jiang, who gives me magnificent help on

my research. Without his assistance, the fabrication process could not be set up in such a short time.

I am also thankful to the entire MER staff, especially Jean Toll, Marylene Palard, Bill Ostler, Jesse James, Gabriel Glenn, Ricardo Garcia, Johnny Johnson, Joyce Kokes, and Gerlinde Sehne, for their continuous help and support.

Lastly and most importantly, I wish to express my love and gratitude to my beloved family for their understanding through the duration of my studies.

**Novel 3-D IC Technology**

Yujia Zhai, B.S.; M.S.E.

The University of Texas at Austin, 2014

Supervisor: Sanjay Banerjee

Co-supervisor: C.Grant Willson

For many decades silicon based CMOS technology has made continual increase

in drive current to achieve higher speed and lower power by scaling the gate length and

the gate insulator thickness. The scaling becomes increasingly challenging because the

devices are approaching physical quantum limits. Three-dimensional electronic devices,

such as double gate, tri-gate and nanowire field-effect-transistors (FETs) provide an

alternative solution because the ultra-thin fin or nanowire provides better electrostatic

control of the device channel. Also high-k oxides lower the gate leakage current

significantly, due to larger thickness for the same equivalent oxide thickness (EOT)

compared with SiO<sub>2</sub> beyond the 22 nm node. Moreover, metal gate that avoids the poly-

depletion effect in poly-Si gate has become mainstream semiconductor technology.

The enabler technologies for high-κ / metal gate 3D transistors include fabrication

of high quality, vertical nanowire arrays, conformal metal and dielectric deposition and

vertical patterning. One of the main focuses of this dissertation is developing a

fabrication process flow to realize high performance MOSFETs with high-κ oxide and

metal gate on vertical silicon nanowire arrays. A variety of approaches to fabricating

highly ordered silicon nanowire arrays have been achieved. Deep silicon etching process

vii

was developed and optimized for nanowire FETs. Process integration and patterning mythologies for high- $\kappa$  / metal gate were investigated and accomplished. 3-D electronic devices including nanowire capacitors, nanowire FETs and double gate MOSFETs for power applications were fabricated and characterized.

The second part of this dissertation is about flexible electronics. Mechanically flexible integrated circuits (ICs) have gained increasing attention in recent years with emerging markets in portable electronics. Although a number of thin-film-transistor (TFT) IC solutions have been reported, challenges still remain for fabrication of inexpensive, high performance flexible devices. We report a simple and straightforward solution: mechanically exfoliating a thin Si film containing ICs. Transistors and circuits can be pre-fabricated on bulk silicon wafer with conventional CMOS process flow without additional temperature or process limitations. The short channel MOSFETs exhibit similar electrical performance before and after exfoliation. This exfoliation process also provides a fast and economical approach to produce thinned silicon wafers, which is a key enabler for three-dimensional (3D) silicon integration based on Through Silicon Vias (TSVs).

# **Table of Contents**

| List of Tables                                                      | xi  |

|---------------------------------------------------------------------|-----|

| List of Figures                                                     | xii |

| Chapter 1 Introduction                                              | 1   |

| 1.1 Overview of 3D nanowire capacitor and nanowire MOSFETs          | 1   |

| 1.2 Nanowire array fabrication and patterning techniques            | 5   |

| 1.3 Overview of power MOSFET                                        | 6   |

| 1.4 Overview of 3D flexible electronics                             | 8   |

| Chapter 2 Silicon nanowire array and nanowire devices               | 10  |

| 2.1 Vapor-Liquid-Solid silicon nanowire growth and patterning       | 10  |

| 2.2 Patterned silicon nanowire array by deep silicon etching        | 12  |

| 2.3 Single crystal nanowire capacitor                               | 14  |

| Chapter 3 Gate-All-Around Nanowire FET                              | 22  |

| 3.1 Integration challenges for GAA-nanowire FET                     | 22  |

| 3.1.1 Etching optimization for high quality nanowires               | 22  |

| 3.1.2 Plasma Enhanced ALD as gate metal.                            | 28  |

| 3.1.3 Gate isotropic etch and vertical patterning                   | 32  |

| 3.2 Process development Gate-All-Around nanowire FETs               | 38  |

| 3.3 Device characterization and discussion                          | 49  |

| Chapter 4 Double gate power MOSFET Introduction                     | 56  |

| 4.1 Process development of vertically diffused finFET               | 56  |

| 4.2 Device characterization and discussion                          | 61  |

| Chapter 5 Flexible thin-film transistors exfoliated from bulk wafer | 70  |

| 5.1 Process review of flexible electronics                          | 70  |

| 5.2 Process of wafer exfoliation                                    | 73  |

| 5.3 Performance of exfoliated thin-film transistors                 | 79  |

| Chapter 6 Future work                                  | 86  |

|--------------------------------------------------------|-----|

| 6.1 Future work for nanowire FET                       | 86  |

| 6.2 Thinned wafer for 3D-IC                            | 86  |

| Appendix A: Process flow of vertical Si nanowire FET   | 88  |

| Appendix B: Process flow of vertically diffused finFET | 90  |

| Bibliography                                           | 92  |

| Vita                                                   | 104 |

# **List of Tables**

| Table 1. 1 | Natural length in devices with different geometries[15, 17, 23]                             | 4    |

|------------|---------------------------------------------------------------------------------------------|------|

| Table 3. 1 | Process conditions of polymer deposition and silicon etching for each                       |      |

|            | DSE cycle. Tool: PlasmaTherm Silicon deep RIE.                                              | . 24 |

| Table 3. 2 | Process conditions and film qualifications of TiN deposited in $N_2$ and                    |      |

|            | NH <sub>3</sub>                                                                             | . 31 |

| Table 3. 3 | Materials and etching techniques for the nanowire FET gate metal                            |      |

|            | integration. Successful integration is achieved by utilizing PEALD Ti                       | N    |

|            | (NH <sub>3</sub> ) as the gate metal, PECVD SiO <sub>2</sub> as the gate mask and 1:1:5 SC- | -1   |

|            | as the gate metal etchant.                                                                  | . 37 |

| Table 3. 4 | Parameters and constants for hole mobility extraction in silicon                            |      |

|            | nanowire FETs.                                                                              | . 54 |

|            |                                                                                             |      |

| Table 4. 1 | Implantation and annealing conditions for vertically diffused finFET                        |      |

|            | doping.                                                                                     | . 57 |

# **List of Figures**

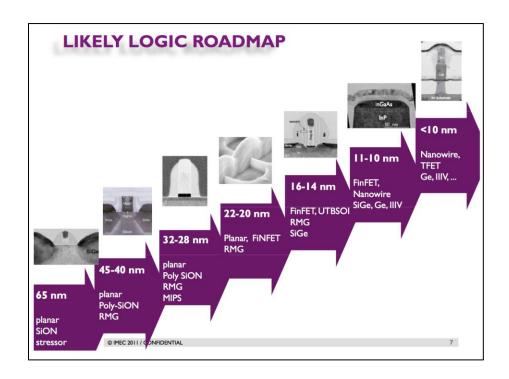

| Figure 1. 1 | Evaluation of device geometries as CMOS scale down [24] 4                          |

|-------------|------------------------------------------------------------------------------------|

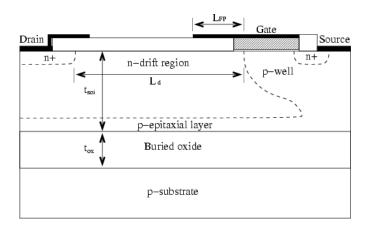

| Figure 1. 2 | The cross-sectional view of a LDMOS [35]                                           |

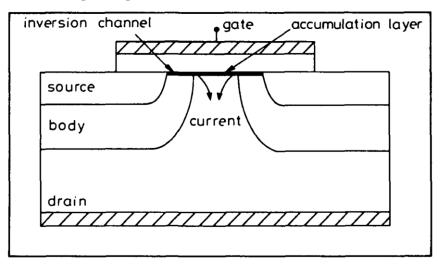

| Figure 1. 3 | The cross-sectional view of a VDMOS [36]                                           |

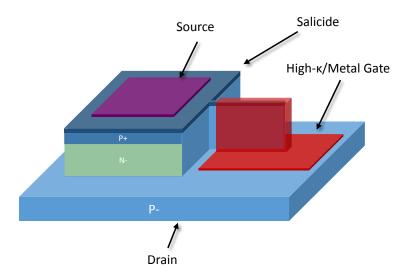

| Figure 1. 4 | Schematic of vertical diffused finFET                                              |

| Figure 2. 1 | Cross-sectional SEM image of single crystalline silicon nanowire 11                |

| Figure 2. 2 | a) SFIL/R nano-imprint process flow for patterned nanowire growth. b)              |

|             | Patterned Au dots with SiO <sub>2</sub> barrier. c) Patterned nanowire growth 12   |

| Figure 2. 3 | Silicon nanowire capacitor fabrication process flow                                |

| Figure 2. 4 | (a-d) Si-nanowire array after DSE with 4, 8, 12, and 15 etch cycles,               |

|             | respectively, resulting in nanowire arrays with an increasing height 14            |

| Figure 2. 5 | a) $70^{\circ}$ tilted SEM image of Si-nanowires after ALD $Al_2O_3$ and sputtered |

|             | TaN. b) and c) Cross-section TEM image of Si-nanowire head after                   |

|             | ALD Al <sub>2</sub> O <sub>3</sub> and sputtered TaN                               |

| Figure 2. 6 | SEM images of Si-nanowire: a) top view; b) 45° tilted view                         |

| Figure 2. 7 | C-V measurements of conventional planar capacitor and Si-nanowire                  |

|             | capacitors with nanowire etch cycles of 4, 8, and 12, delivering                   |

|             | nanowire arrays with heights between 130nm to 450nm. The $Al_2O_3$                 |

|             | dielectric thickness is 24 nm for a) and 8 nm for b)                               |

| Figure 2. 8 | C-V measurement results compared with calculated values                            |

| Figure 2. 9  | Dielectric leakage current for conventional planar capacitor and Si-                          |

|--------------|-----------------------------------------------------------------------------------------------|

|              | nanowire capacitors with nanowire etch cycles of 4, 8, and 12. Al <sub>2</sub> O <sub>3</sub> |

|              | dielectric thickness is 24nm for a) and 8 nm for b)                                           |

| Figure 2. 10 | Time-Dependent Dielectric Breakdown measurement on Si-nanowire                                |

|              | capacitors compared with conventional planar capacitors                                       |

|              |                                                                                               |

| Figure 3. 1  | High aspect ratio nanowires are achieved by deep silicon etch with metal                      |

|              | salicide mask. The aspect ratio is more than 20 on nanowires. The defect                      |

|              | in center post probably results from metal out-diffusion during salicide                      |

|              | anneal. 23                                                                                    |

| Figure 3. 2  | Cross-sectional SEM images of deep silicon etching. Samples were                              |

|              | etched with different etch/deposition ratio and sidewall undercut angels                      |

|              | were evaluated. Result shows that the combination of 1.0 sec deposition                       |

|              | and 2.0 sec etching yield almost 90° vertical sidewall                                        |

| Figure 3. 3  | Etched sidewall morphology optimization. The original recipe has 2.0                          |

|              | sec deposition time and 1.0 sec etch time in each cycle. Scallops are                         |

|              | observed on the etched sidewall. The optimized recipe reduces the                             |

|              | deposition time to 1.0 sec and the etch time to 0.5 sec, and scallops are                     |

|              | minimized on the etched sidewall. Note that the etch/deposition ratio is                      |

|              | kept as a constant (2) in the process optimization                                            |

| Figure 3. 4  | Recipe optimization result for silicon nanowire etching. The left image                       |

|              | a) shows the nanowires etched with the original recipe. Scallops are                          |

|              | observed on the sidewall of nanowires as well as undercutting defect.                         |

|              | Etching process undercuts the nanowire bottom as the cycle number                             |

|              |                                                                                               |

|              | increases. The right image b) shows the nanowires etched with the                           |                    |

|--------------|---------------------------------------------------------------------------------------------|--------------------|

|              | optimized recipe. Sidewall smoothness is improved and undercutti                            | ng is              |

|              | minimized.                                                                                  | 27                 |

| Figure 3. 5  | Illustrations of plasma enhanced ALD TiN process in $N_2$ (a) and N                         | H <sub>3</sub> (b) |

|              | respectively. Note that NH <sub>3</sub> should be turned off while pulsing TD               | MAT.               |

|              |                                                                                             | 29                 |

| Figure 3. 6  | C-V characteristics of fabricated MOS capacitors with plasma enhancement                    | anced              |

|              | ALD TiN as the gate metal                                                                   | 32                 |

| Figure 3. 7  | Illustration for resist spin-on and etch-back process to vertically pa                      | ttern              |

|              | the gate metal.                                                                             | 33                 |

| Figure 3. 8  | Resist spin-on and etch-back process to vertically pattern the gate i                       | netal.             |

|              | a) Al <sub>2</sub> O <sub>3</sub> and TiN are deposited on nanowires. b) Resist is spun and | 1                  |

|              | etched back to define the gate length. c) Exposed TiN is wet etched                         | d by               |

|              | SC-1 solution and the resist is removed                                                     | 33                 |

| Figure 3. 9  | Test structures to investigate TiN film conductivity degradation                            | 35                 |

| Figure 3. 10 | Measured I-V on TiN gate metal with different test structures of Ti                         | iN                 |

|              | process integration.                                                                        | 36                 |

| Figure 3. 11 | Schematic of a vertical nanowire field-effect-transistor.                                   | 39                 |

| Figure 3. 12 | Simulated doping concentration for nanowire FETs.                                           | 40                 |

| Figure 3. 13 | Etched silicon nanowire array patterned by e-beam lithography and                           | i                  |

|              | masked by Ti/Ni salicide. Nanowires height is ~ 720 nm and diame                            | eter is            |

|              | ~ 90 nm. Aspect ratio is ~ 1:8                                                              | 42                 |

| Figure 3. 14 | Process flow of nanowire FETs                                                               | 44                 |

| Figure 3. 15 | nanowire FET after resist thinning (left) and gate patterning (right)                       | 45                 |

| Figure 3. 16 | Silicon nanowire FETs with vertical wrapped gate pattern                         | 6  |

|--------------|----------------------------------------------------------------------------------|----|

| Figure 3. 17 | Tilted SEM image of silicon nanowire FET after PECVD $\mathrm{SiO}_2$ etch.      |    |

|              | Nanowire cores are exposed on top of the device for the drain                    |    |

|              | metallization                                                                    | .7 |

| Figure 3. 18 | Top-view microscope image of final device layout. Drain is the top               |    |

|              | nickel films and gate is buried under SiO <sub>2</sub> inter-metal dielectric. A |    |

|              | contact window is opened by photolithography                                     | .8 |

| Figure 3. 19 | Cross-sectional SEM image of a nanowire FET. The cross-section that i            | İS |

|              | created by focused ion beam (FIB) cuts through the nanowire core 4               | .9 |

| Figure 3. 20 | Measured transfer characteristics of a silicon nanowire FET with 25              |    |

|              | nanowires in parallel 5                                                          | 0  |

| Figure 3. 21 | Measured output characteristics of silicon nanowire FET with 25                  |    |

|              | nanowires in parallel. 5                                                         | 1  |

| Figure 3. 22 | Trans-conductance of silicon nanowire FET measured at $V_{DS}$ = -0.2 V.         |    |

|              | 5                                                                                | 2  |

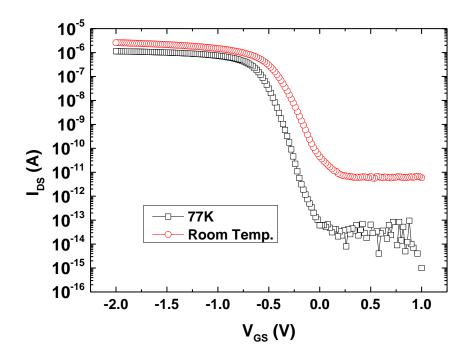

| Figure 3. 23 | Low temperature transfer characteristics compared with room                      |    |

|              | temperature5                                                                     | 5  |

|              |                                                                                  |    |

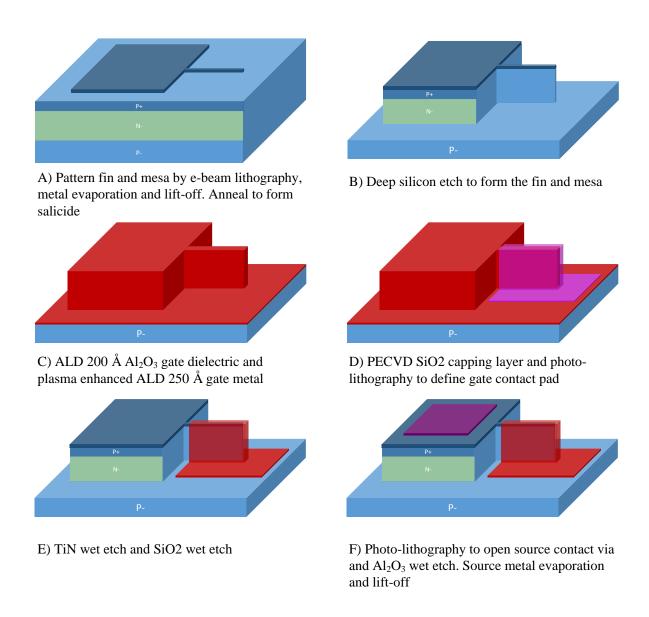

| Figure 4. 1  | Illustration of process flow for vertically diffused finFET                      | 8  |

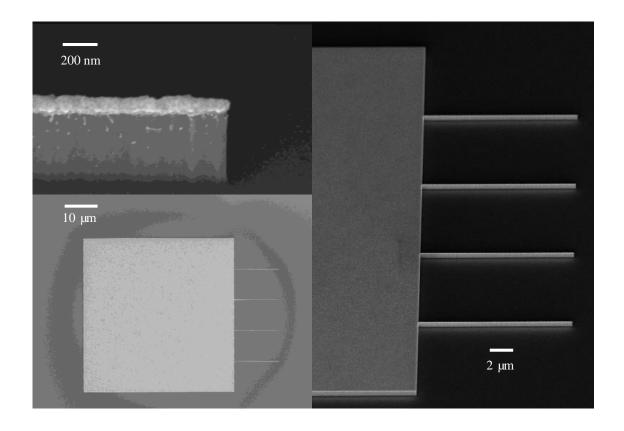

| Figure 4. 2  | Etched fins after 30 cycles of deep silicon etch. Right image is a 45°           |    |

|              | tilted SEM image of a vertically diffused finFET with 4 fins. The length         | 1  |

|              | of the fin is 15 $\mu$ m. Left upper is a close-up image of at the tip of an     |    |

|              | etched fin. The width of the fin is around 70 nm after the salicide              |    |

|              | annealing. Left Lower is the top view of the device layout                       | 9  |

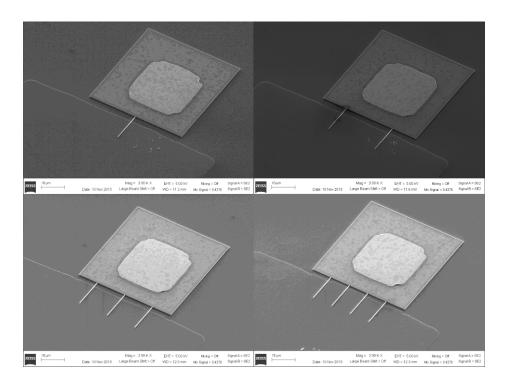

| Figure 4. 3 | Completed vertically diffused finFET.                                                      | . 60 |

|-------------|--------------------------------------------------------------------------------------------|------|

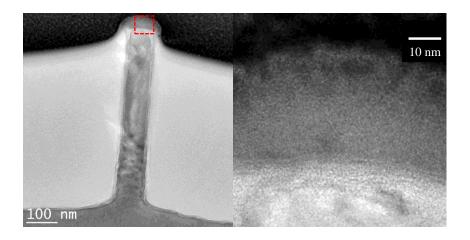

| Figure 4. 4 | TEM images of the fin cross-section and high magnification image of                        |      |

|             | salicide on top of the fin.                                                                | 61   |

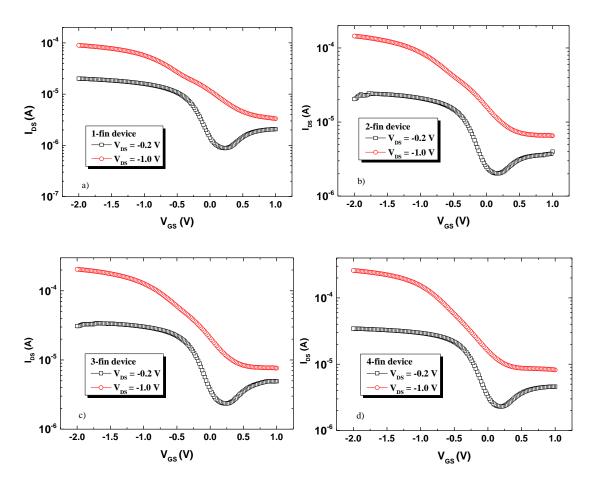

| Figure 4. 5 | Transfer characteristics of fabricated vertically diffused finFETs with                    | 1-   |

|             | fin (a), 2 fins (b), 3 fins (c) and 4 fins (d)                                             | 62   |

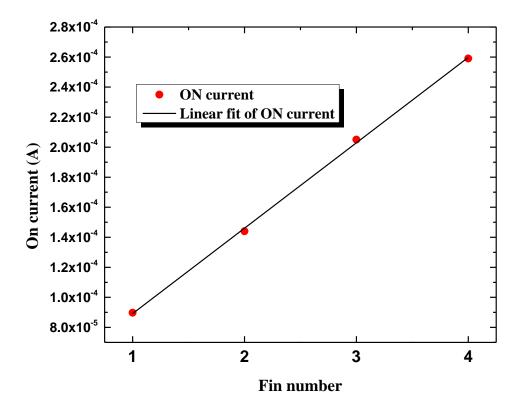

| Figure 4. 6 | ON-current versus fin number in one device. Linear dependence is                           |      |

|             | observed                                                                                   | 63   |

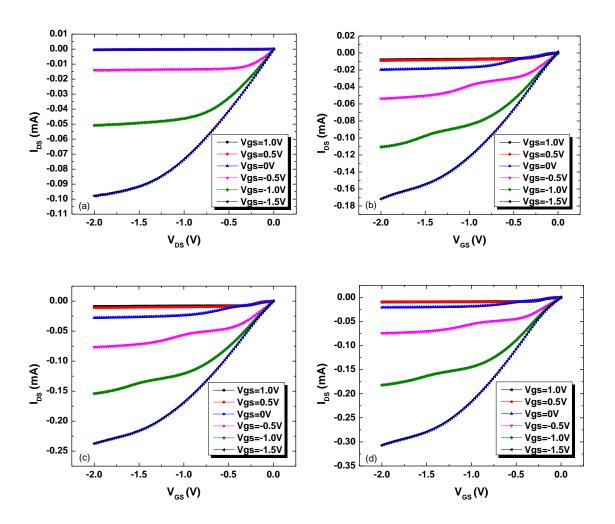

| Figure 4. 7 | Output characteristics of vertically diffused finFETs with fin number                      |      |

|             | from 1-4 in (a) to (d), respectively                                                       | . 64 |

| Figure 4. 8 | Transfer characterization comparison of the swapped S/D configuration                      | on   |

|             | and the original S/D configuration.                                                        | . 65 |

| Figure 4. 9 | Low temperature transfer characteristic comparing with room                                |      |

|             | temperature. $V_{DS} = -0.2V$                                                              | . 68 |

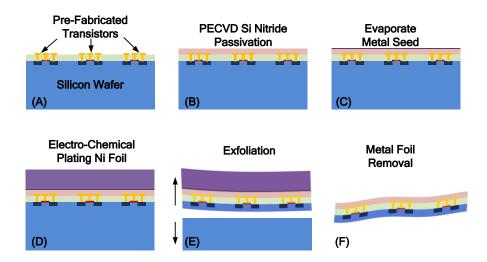

| Figure 5. 1 | Exfoliation process flow: (A) Transistors are pre-fabricated on                            |      |

|             | conventional silicon wafer with standard CMOS process flow. (B)                            |      |

|             | PECVD Si <sub>3</sub> N <sub>4</sub> for passivation. (C) E-beam evaporation of thin metal |      |

|             | seed layer. (D) Electro-chemical plating of Ni on seed layer. (E)                          |      |

|             | Thermal expansion mismatch exfoliates the film from wafer. (F) Nick                        | æl   |

|             | foil is removed by SC-2 solution.                                                          | . 75 |

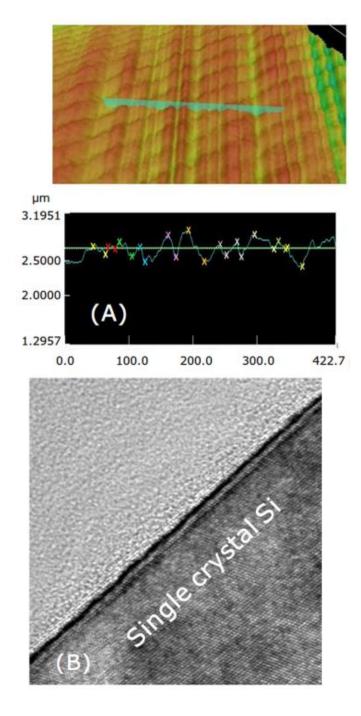

| Figure 5. 2 | (A) Surface roughness of exfoliated thin-film silicon (B) TEM image                        | of   |

|             | microstructure of the exfoliated Si                                                        | . 76 |

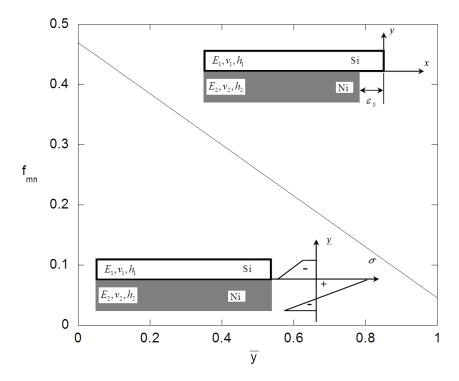

| Figure 5. 3 | The variation of stress coefficient $f_{mn}$ for $0 < \overline{y} \le 1$ . The upper inse | t    |

|             | shows the residual strain $\varepsilon_0$ between Si and Ni layers and the co-             |      |

|             | ordinate system used to compute the stress distribution. The lower              |

|-------------|---------------------------------------------------------------------------------|

|             | inset schematically shows the stress distributions in Si and Ni layers          |

|             | after the exfoliation. 78                                                       |

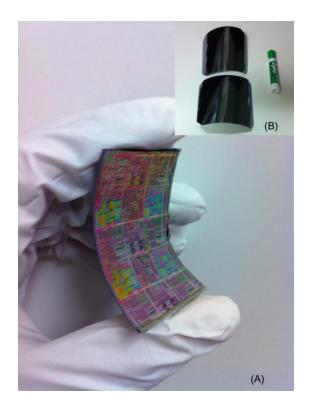

| Figure 5. 4 | Image of a bent, flexible integrated circuit with high performance              |

|             | CMOS devices. (A) is flexible IC with the size of 35 mm x 50 mm.                |

|             | (B) shows an 8-inch exfoliated wafer with metal foil                            |

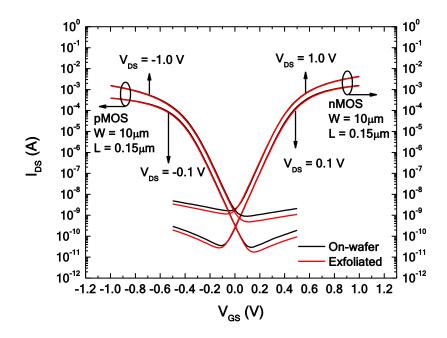

| Figure 5. 5 | Comparison of transfer characteristics before exfoliation (On-wafer,            |

|             | black curve) and after exfoliation (exfoliated, red curve) with $V_{DS}$ = 0.1  |

|             | V and 1.0 V. The channel length is 150 nm and width is 10 $\mu$ m with          |

|             | gate oxide of 20Å SiO <sub>2</sub> for both n-MOSFETs and p-MOSFETs 81          |

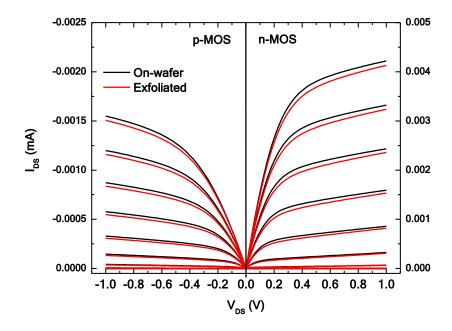

| Figure 5. 6 | Comparison of output characteristics before exfoliation (On-wafer, black        |

|             | curve) and after exfoliation (exfoliated, red curve) with $V_{GS}$ from 0.1 $V$ |

|             | to 1.0 V, in steps of 0.1 V. The channel length is 150nm and width is           |

|             | 10 μm with gate oxide of 20Å SiO <sub>2</sub> for both n-MOS and p-MOS 82       |

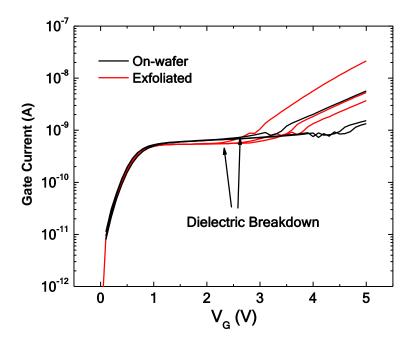

| Figure 5. 7 | Gate dielectric leakage current as a function of gate bias. Black curve         |

|             | shows the leakage current before exfoliation (on-wafer), and red curve          |

|             | after exfoliation                                                               |

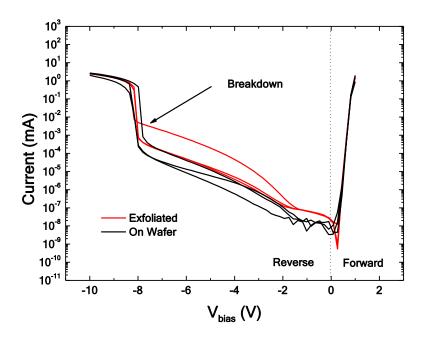

| Figure 5. 8 | Diode I-V characteristics with reverse breakdown voltage. Black curve           |

|             | shows the leakage current before exfoliation (on-wafer), and red curve          |

|             | after exfoliation 84                                                            |

## **Chapter 1 Introduction**

#### 1.1 OVERVIEW OF 3D NANOWIRE CAPACITOR AND NANOWIRE MOSFETS

Semiconductor nanowires have gained increasing interest in the last decade since this geometry provides a wide range of 3-dimensional electronic devices [1]. Because of its high aspect ratio, nanowire array or forest can dramatically enhance the effective surface area and is capable of achieving high density storage capacity in a limited silicon real estate, benefiting potential applications such as analog and mixed signal ICs. Analog and mixed signal ICs require on-chip passives with storage capacity in excess of 1  $\mu F/cm^2$ , and leakage densities less than  $\sim 1 \times 10^{-6}/cm^2$  at a voltage of  $\sim 2V$ . This can be difficult to achieve with planar capacitors. With more aggressive effective oxide thickness (EOT) and a concomitant relaxation of leakage current requirement, these 3D capacitors may be useful for DRAMs also [2]. DRAM capacity or bit density has been increasing by a factor of 4 every three years, whereas, memory cell size has been reduced by almost 1/3 each generation for the sake of cost [3, 4]. Along with scaling down, the reduced voltage pushes the capacity requirements to ensure a constant cell signal [5]. One approach to coping with the dilemma of size vs. capacitance is to reduce insulator thickness and implement high-k technology [6]. Another approach to obtaining high capacitance is to construct 3-dimensional structures such as stacked capacitors, trenches [7], pillars [8, 9], etc. For example, carbon nanotubes fabricated by bottom-up growth have been utilized to enhance the capacitance[10]. Compared to trench capacitors, the topography of nanowires is more compatible with FinFETs and vertical gate-all-around transistors, which are promising technology solutions for 22nm and beyond[11].

The ongoing scaling-down of electronic devices has become more challenging since dimensions are approaching the physical limits of semiconductors [12]. Short

channel effects, e.g. sub-threshold swing (SS) degradation and drain-induced barrier lowering (DIBL) are caused by the encroachment of electric field line from the drain into the channel region, thereby competing for the available depletion charge. DIBL effectively reduces the barrier between source and drain [13] and consequently reduces the threshold voltage ( $V_{th}$ ). Fully depleted multiple-gate field-effect-transistors (MuGFETs) that have excellent control of short-channel effects and are compatible with standard CMOS fabrication process have been proposed and under intense research as promising candidates for the next generation of CMOS technology [14-16].

To gain insight into threshold voltage roll-off and sub-threshold characteristics in fully depleted devices, Yan *et. al.* solved Poisson's equation to examine the potential distribution in the channel region:

$$\frac{d^2\Phi}{dx^2} + \frac{d^2\Phi}{dy^2} = \frac{qN_A}{\varepsilon_{Si}}$$

where  $0 \le x \le L_{eff}$  and  $0 \le y \le t_{Si}$ .  $L_{eff}$  is the effective channel length, and  $t_{Si}$  is silicon film thickness.

A natural length scale  $\lambda$  is introduced to describe the potential distribution:

$$\lambda = \sqrt{\frac{\varepsilon_{Si}}{\varepsilon_{ox}} t_{Si} t_{ox}}$$

and

$$\phi(x) = \Phi_f(x) - \Phi_{gs} + \frac{qN_A}{\varepsilon_{si}}\lambda^2$$

Then Poisson's equation can be simplified as:

$$\frac{d^2\phi}{dx^2} - \frac{d^2\phi}{d\lambda^2} = \frac{qN_A}{\epsilon_{Si}}$$

$\phi(x)$  differs from  $\Phi_f(x)$  only by a position-independent term. The derivation result indicates that short channel effects can be minimized when effective channel length is much larger than the natural length scale  $\lambda$  [17].

Colinge *et. al.* deduced the natural length scales for single gate, double gate and surrounding gate devices by applying corresponding boundary conditions. The derivation results are presented in Table 1.1. It can be inferred that the scaling requirement is more relaxed for double gate MOSFETs, and further relaxation is obtained by using the gate-all-around structure [15, 18-20]. In this structure, the wrapped gate has better electrostatic control as compared to other gate designs. Fabricated on a cylindrical pillar of silicon, this device has the benefits of both reducing the short channel effects and improving the sub-threshold slope (SS), as well as potentially higher packing densities. Simulation shows that the DIBL and SS can be maintained if scaling laws are followed [21, 22].

| Gate geometries  | Natural length                                                                                                                                                                                                                                                                             |

|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Single-gate      | $\lambda = \sqrt{rac{arepsilon_{Si}}{arepsilon_{ox}}t_{Si}t_{ox}}$                                                                                                                                                                                                                        |

| Double-gate      | $\lambda = \sqrt{\frac{\varepsilon_{Si}}{2\varepsilon_{ox}}t_{Si}t_{ox}}$                                                                                                                                                                                                                  |

| Surrounding-gate | $\lambda \approx \sqrt{\frac{\varepsilon_{Si}}{4\varepsilon_{ox}}t_{Si}t_{ox}} \text{ (square-section)}$ $\lambda = \sqrt{\frac{2\varepsilon_{Si}t_{Si}^{2}\ln\left(1 + \frac{2t_{ox}}{t_{Si}}\right) + \varepsilon_{ox}t_{Si}^{2}}{16\varepsilon_{ox}}} \text{ (circular cross-section)}$ |

Table 1. 1 Natural length in devices with different geometries [15, 17, 23]

Figure 1. 1 Evaluation of device geometries as CMOS scale down [24].

#### 1.2 NANOWIRE ARRAY FABRICATION AND PATTERNING TECHNIQUES

The approaches to fabricating semiconductor nanowires fall into two categories: bottom-up growth and top-down etching. An intensively studied bottom-up growth technique for silicon nanowire is Vapor-Liquid-Solid (VLS) growth mechanism [25]. According to this mechanism, a metal catalyst forms liquid alloy droplets at high temperature since substrate atoms dissolve into catalyst and melting point is reduced. Anisotropic crystal growth takes place at the liquid/solid interface. The growth is done in a chemical vapor deposition (CVD) chamber at temperatures ranging from 600 to 1000 °C. The precursors, SiCl<sub>4</sub> and H<sub>2</sub>, flow into the chamber and react as:

$$SiCl_4+2H_2 = Si + 4HCl$$

The droplets are preferred sinks for the arriving silicon atoms, and continuing incorporation leads to a super-saturation. Consequently, the silicon atoms in the alloy droplets begin to precipitate onto the liquid/solid interface, and finally on the substrate. As a result, anisotropic silicon growth takes place at the interface, elevating the droplets to the top of the crystalline silicon nanowire. The preferred growth direction is <111>, and sometimes also <110> [26, 27]. Selective positioning of the nanowires requires isolating the catalyst in SiO<sub>2</sub> wells, in order to prevent the catalyst from migrating during annealing. [28]

Using selective etching to fabricate silicon nanowires is more straightforward and compatible with modern semiconductor technology. Lithography patterns the hard mask (e.g. silicon nitride) as dot shapes at the location of each nanowire. Subsequent anisotropic etching removes the most of the silicon, except in regions that are protected by dots, and leaves the high aspect ratio nanowires beneath the dots. Optional sacrificial silicon oxidation and HF etching can further thin down the nanowires and improve the surface of sidewalls. However, it is difficult to pattern nanowires with small diameter by

optical lithography, while electron beam writing has low throughput and is not a manufacturable option. We use a simple and manufacturable technique, Step and Flash Imprint Lithography (S-FIL) [29] to produce the core of our semiconductor nanowires.

#### 1.3 OVERVIEW OF POWER MOSFET

Various types of mobile telecommunication devices, for example cellphone, personal digital assistant and tablet computer, as well as electric automobile, power electronic devices are gaining in importance. Power MOSFET devices are quite interesting in terms of the fast switching speed and the capability of handling high voltage in such devices [30]. There are two major categories of power MOSFET: laterally diffused MOSFET (LDMOS) and vertically diffused MOSFET (VDMOS or VMOS). The LDMOS (shown in Figure 1.2) is analogous to conventional MOSFET in terms of horizontal current-flow configuration, except that an extended, lightly doped drain region is utilized. The long, lightly doped drain extension acts as a drift-region to support a large voltage drop, enabling power applications. [30-34]

Figure 1. 2 The cross-sectional view of a LDMOS [35]

On the contrary, VDMOS, cross-sectional structure shown in figure 1.2, has a vertical current-flow pattern. Traditionally VDMOS utilizes two successive diffusion steps to define two closely spaced p-n junctions at different depths below the silicon surface. The channel length does not depend on the lithography step; rather it depends on the diffusion processes. Since the long drift-region is integrated vertically, VDMOS saves valuable silicon real estate [31, 33].

Figure 1. 3 The cross-sectional view of a VDMOS [36]

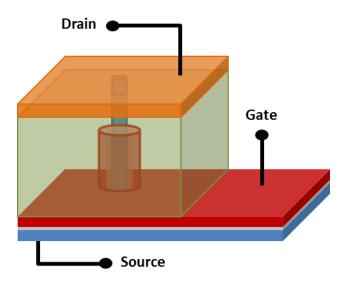

We developed, fabricated and characterized a vertically defused finFET for potential power applications. The design of the finFET structure is illustrated in figure 1.3. A narrow fin with a width of 50 nm and length of 15 µm was etched on substrate surface. One end of the fin was connected to a 50x50 µm² mesa for source contact. Gate dielectric and metal were deposited and fully cover the fin region. The desired doping profile along the fin was achieved by ion implantations and diffusions before the fin was etched. To further reduce source contact resistance, i.e. from the top of the fin to the mesa, salicide was formed, which also acted as a hard mask when etching the fin.

Figure 1. 4 Schematic of vertical diffused finFET.

#### 1.4 OVERVIEW OF 3D FLEXIBLE ELECTRONICS

Mechanically flexible integrated circuits (ICs) have gained increasing attention in recent years, with emerging markets in portable electronics, e.g. sensors, electronic textiles, and bio-medical technology [37-39]. Although a number of amorphous and single crystalline thin-film-transistor (TFT) solutions have been reported [40, 41], challenges still remain for fabrication of inexpensive, high performance flexible devices. In comparison with state-of-the-art Complementary Metal Oxide Semiconductor Field Effect Transistor (CMOS) technology, hydrogen-passivated amorphous silicon (a-Si:H) TFT has much lower carrier mobilities[42], whereas the implementation of nanowire/nano-ribbon transistors requires a complex process flow. We propose a simple and straightforward solution: mechanically exfoliating a thin silicon film containing ICs that have been pre-fabricated on a bulk silicon wafer using conventional CMOS technology. Transistors and circuits can be pre-fabricated on silicon wafer with standard

CMOS process without additional temperature or process limitations. For example, some TFT processes require low temperature condition to prevent thermal degradation of plastic substrates. We realize high performance single crystalline TFTs by mechanical exfoliation. The short channel MOSFETs exhibit similar electrical performance before and after exfoliation. This exfoliation process also provides a fast and economical approach to producing thinned silicon wafers, which is a key enabler for three-dimensional (3D) silicon integration based on Through Silicon Vias (TSVs).

## Chapter 2 Silicon nanowire array and nanowire devices

#### 2.1 VAPOR-LIQUID-SOLID SILICON NANOWIRE GROWTH AND PATTERNING

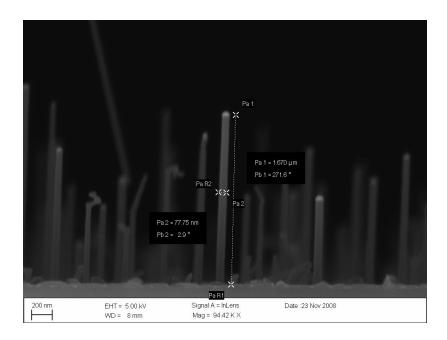

The VLS growth mechanism has been introduced in Chapter one. Silicon wafer with <111> orientation was cleaned by piranha and HF to remove organic contamination and native oxide. 7Å Au was deposited by e-beam assisted-evaporation at a rate of 0.1 Å /sec. Right after a dilute HF dip, the wafer was transferred into Reduced Pressure Chemical Vapor Deposition (RPCVD) chamber for single crystalline silicon nanowire growth. The growth started with a 15 min.  $H_2$  (15 sccm) anneal at a temperature of 650°C and pressure of 0.5 Torr. During the annealing, pre-deposited Au film began to form Si/Au alloy droplets on the wafer surface. Then SiH<sub>4</sub> was flown into the chamber (35 sccm) and silicon nanowires started to grow. Chamber pressure was maintained at 80 mTorr during the 30 min. growth. Cross-sectional SEM image after growth is shown in figure 2.1. <111> is the preferred growth direction, which is perpendicular to the plane. Some of the nanowires grew along the <110> direction. The typical nanowire has a length of 1-2  $\mu$ m and diameter of 60-100 nm. These studies were done in collaboration with Prof. Tutuc.

Figure 2. 1 Cross-sectional SEM image of single crystalline silicon nanowire.

Nanowires grow at the location where the catalyst droplets are formed, with a preferred orientation of <111> [25]. Diameter is determined by the size of the droplet [26]. Therefore it is possible to control the nanowire location if Au can be patterned. However, patterned Au dots have low fidelity with respect to their original shape under the high temperature annealing due to substantial agglomeration [28]. As a result, SiO<sub>2</sub> was used as a barrier or buffer to confine etch Au dots during the growth.

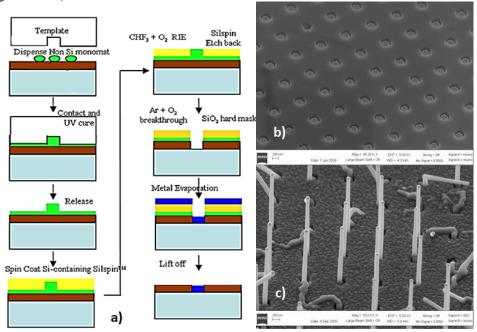

Patterning Au dots in nano scale was developed with Step and Flash Imprint Lithography (SFIL), illustrated in figure 2.2 a) [43]. In this process, 100 nm SiO<sub>2</sub> was grown on <111> silicon wafer by 7 min. wet oxidation at 1050°C. After spin coating adhesion layer on the wafer, SFIL was done by the IMPRIO 100 system (Molecular Imprints Inc): Imprint resist was ink-jet-ed onto the wafer and then a quartz template with patterned holes was pressed on. UV light exposure cured the resist and then the template

was released, leaving the resist as a form of nano-pillar array. After imprint, Silspin (Molecular Imprints Inc) was spun on the resist, followed by 3 steps of well-controlled etchings: Silspin etching (by CHF<sub>3</sub>+O<sub>2</sub>), monomat (O<sub>2</sub>) etching and SiO<sub>2</sub> (by CHF<sub>3</sub>+O<sub>2</sub>) etching, transferring the pillar array into an array of holes in the SiO<sub>2</sub>. After a buffered HF dip, 20nm Au was evaporated onto the wafer surface. Piranha solution lifted off the monomat layer, leaving Au dots isolated by SiO<sub>2</sub> barrier, as shown in figure 2.2 b). Finally silicon nanowire growth was carried out using RPCVD and the growth result is shown in figure 2.2 c).

Figure 2. 2 a) SFIL/R nano-imprint process flow for patterned nanowire growth. b) Patterned Au dots with SiO<sub>2</sub> barrier. c) Patterned nanowire growth.

#### 2.2 PATTERNED SILICON NANOWIRE ARRAY BY DEEP SILICON ETCHING

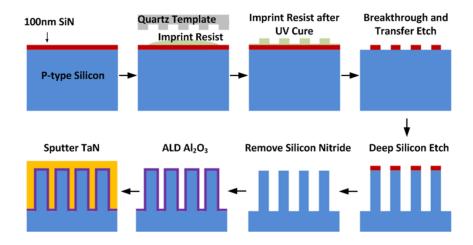

An alternative approach to fabricating nanowire arrays is by patterning dot-shaped mask and then etching silicon. The process flow is shown in figure 2.3. A 100 nm layer

of silicon nitride ( $Si_3N_4$ ) was deposited on the substrate by low pressure chemical vapor deposition (LPCVD), serving as a hard-mask for Si etching. Following imprint process utilized a quartz template with an array of holes, and it produced the resist pattern as pillar-array. Each pillar has a diameter of 130 nm and height of ~200 nm, with a residual underlying layer of around 100 nm. We patterned 1 cm<sup>2</sup> dies for each imprint in a few seconds, unlike time consuming e-beam lithography. Up to 40 imprint patterns or dies were patterned on a 100 mm wafer. An  $O_2$  plasma anisotropic etching breaks through the imprint resist residual layer and then a mixture of CHF<sub>3</sub> and  $O_2$  plasma was used to etch the  $Si_3N_4$  film, transferring the nano-pillar pattern onto  $Si_3N_4$  dot array on the silicon substrate, with a height of 100 nm and pitch of 280 nm. The dot-shaped  $Si_3N_4$  mask was used to etch dense ordered Si nanowires by deep silicon etching (DSE). The diameter of the nanowire was determined by the dot size, while the height was controlled by silicon etching Bosch process cycles that alternately etch with  $SF_6$  gas and cause polymer build-up with  $C_4F_8$  gas.

Figure 2. 3 Silicon nanowire capacitor fabrication process flow

#### 2.3 SINGLE CRYSTAL NANOWIRE CAPACITOR

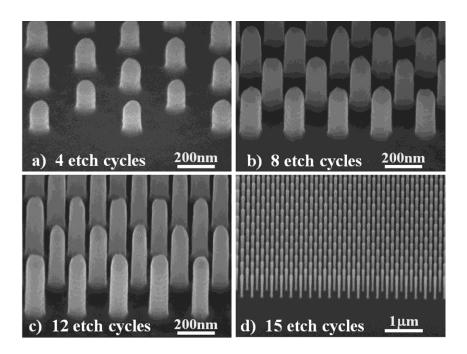

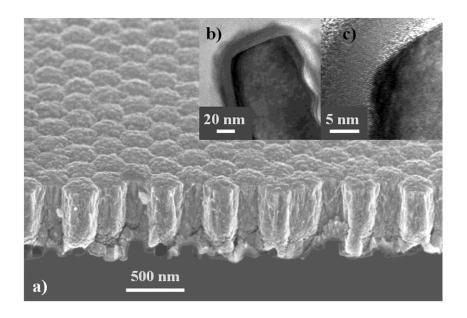

The geometry of nanowire array can be utilized as 3-dimensional nano-capacitors, as introduced in chapter 1. In this work, four splits of different deep Si etch (DSE) varying from 4 to 15 cycles spanning from 8-sec to 30-sec results in nanowire heights of 130 nm to 600 nm (Figure 2.4). Residual polymer and Si<sub>3</sub>N<sub>4</sub> mask were cleaned by dry etch and piranha. After cleaning, a high-κ gate dielectric Al<sub>2</sub>O<sub>3</sub> was deposited on the Si nanowire surface by Atomic Layer Deposition (ALD). TaN was sputtered as the top metal, and contact pads were defined by photolithography. In Figure 2.5 cross-sectional SEM (a) and TEM micrographs (b and c) of the final structures are shown.

Figure 2. 4 (a-d) Si-nanowire array after DSE with 4, 8, 12, and 15 etch cycles, respectively, resulting in nanowire arrays with an increasing height.

Figure 2. 5 a)  $70^{\circ}$  tilted SEM image of Si-nanowires after ALD Al<sub>2</sub>O<sub>3</sub> and sputtered TaN. b) and c) Cross-section TEM image of Si-nanowire head after ALD Al<sub>2</sub>O<sub>3</sub> and sputtered TaN

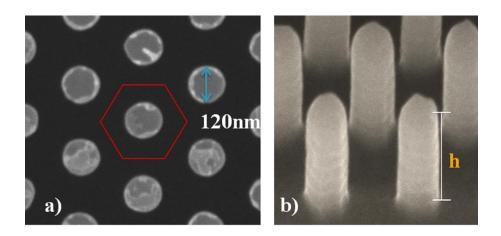

We calculated the Metal-Oxide-Semiconductor (MOS) capacitance of fabricated vertical nanowire capacitors based on the geometry of the 3-D structure. The layout of our Si-nanowire is an array of hexagons, with one nanowire in the center (Figure 2.6a). The edge of the unit is 162 nm since the pitch between each nanowire is 280 nm. Thus, each unit has an area of  $6.82 \times 10^{-10} \text{ cm}^2$ . The capacitor of each unit ( $C_{unit}$ ) consists of 3 components [44]: planar capacitor on the substrate ( $C_{plane}$ ), sidewall capacitor along the vertical nanowire ( $C_{cylinder}$ ) and top capacitor on the head of each nanowire ( $C_{hemisphere}$ ). Since, the 3 capacitors are in parallel:

$$C_{unit} = C_{plane} + C_{cylinder} + C_{hemisphere}$$

where  $C_{plane}$  is the planar capacitor of the hexagonal unit excluding the area of Si-nanowire:

$$C_{plane} = (A_{unit} - A_{SiNW}) \frac{\varepsilon_s \varepsilon_0}{d}$$

with d the dielectric thickness. In this work, we used 2 different dielectric thicknesses: 8 nm and 24 nm.

The cylindrical nanowire side wall capacitor  $C_{cylinder}$  is[45]:  $C_{cylinder} = \frac{2\pi\varepsilon_0\varepsilon_s h}{\ln(b/a)}$

$$C_{cylinder} = \frac{2\pi\varepsilon_0\varepsilon_s h}{\ln(b/a)}$$

where h is the height of the cylinder, a the radius of the Si-nanowire and b the radius to the TaN gate. Therefore we have:

$$b = a + d$$

The SEM tilted view in figure 2.6b shows that the top of the nanowire could be considered as a hemispherical capacitor,  $C_{hemisphere}$ , due to Si<sub>3</sub>N<sub>4</sub> over etching process.

$$C_{hemisphere} = \frac{2\pi\varepsilon_s\varepsilon_0}{\frac{1}{a} - \frac{1}{b}}$$

Figure 2. 6 SEM images of Si-nanowire: a) top view; b) 45° tilted view

The fabricated Si-nanowire MIS capacitors were measured by an Agilent B1500 system. Along with nanowire devices with different heights, or etching cycles during DSE, conventional planar capacitors with identical dielectric thickness were fabricated as

control samples. All capacitance measurements are normalized to microfarad per surface area in  $(\mu F/cm^2)$ . As the substrate is lightly P-type doped, MOS capacitor accumulation condition is attained when sufficient negative bias voltage is applied.

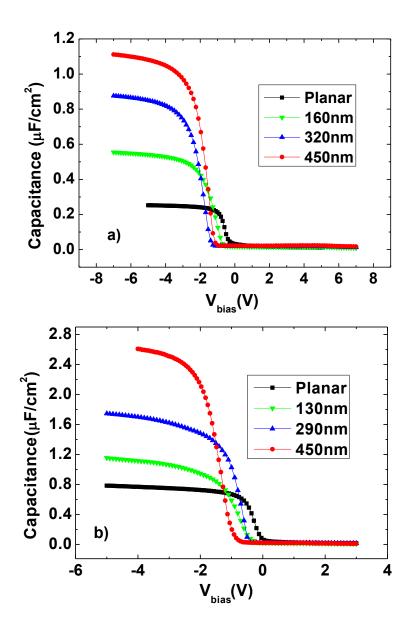

C-V measurements of 24 nm  $Al_2O_3$  dielectric thickness are shown in Figure 2.7a. The MOS capacitance measured on 160 nm-nanowire-height capacitors shows accumulation capacitance of 0.55  $\mu F/cm^2$ . MOS capacitor with double nanowire height (320 nm) leads to higher capacitance at 0.88  $\mu F/cm^2$ . Larger capacitance can be achieved by increasing etching cycles i.e. nanowire heights. The 450 nm-nanowire-height capacitor exhibits a capacitance of 1.08  $\mu F/cm^2$ , which is four times the planar control sample capacitance of 0.25  $\mu F/cm^2$ .

Similar devices with 8 nm  $Al_2O_3$  as dielectric are also fabricated and the results are presented in Figure 2.7b. The 12-etching-cycle sample (450 nm Si-nanowire heights capacitors) achieves a capacity of 2.6  $\mu$ F/cm<sup>2</sup>, which is more than three times the capacity of control planar capacitors.

Figure 2. 7 C-V measurements of conventional planar capacitor and Si-nanowire capacitors with nanowire etch cycles of 4, 8, and 12, delivering nanowire arrays with heights between 130nm to 450nm. The  $Al_2O_3$  dielectric thickness is 24 nm for a) and 8 nm for b).

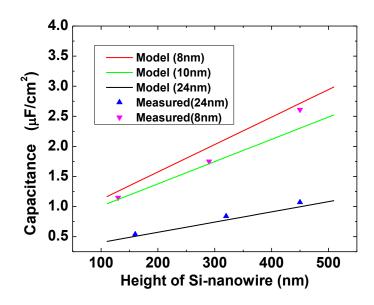

Accumulation capacitance measurements from all Si-nanowire capacitors and our theoretical calculations are summarized in Figure 2.8. As the height of silicon nanowire increases, accumulation capacitance rises linearly. Also thinner dielectric layer leads to a

higher capacitance, as expected. The simple model fits well for the 24 nm  $Al_2O_3$  thickness capacitors but overestimates the experimental capacitance for the 8 nm  $Al_2O_3$  thickness. In the case of capacitors fabricated with a thinner  $Al_2O_3$  layer, the native oxide becomes a non-negligible contributor for EOT: 1nm native oxide corresponds to  $\sim$ 2 nm  $Al_2O_3$  and therefore the device behavior is similar to 10 nm  $Al_2O_3$  dielectric.

Figure 2. 8 C-V measurement results compared with calculated values

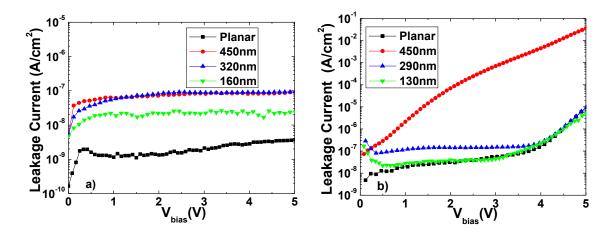

The dielectric leakage current is also measured (Figure 2.9) for our nanowire capacitors. The planar capacitors, with the both dielectric thicknesses, have the lowest leakage current (3.7x10<sup>-9</sup> A/cm<sup>2</sup> for 24 nm and 9.64x10<sup>-6</sup>A/cm<sup>2</sup> for 8nm at 5V bias). Capacitors fabricated with taller nanowires have larger leakage density due to the greater 3-D aspect ratio, possibly leading to field enhancement and dielectric thinning near the edges. We observe more than one order of magnitude higher leakage density for 450nm Si-nanowire capacitors compared with planar capacitor, for 24 nm Al<sub>2</sub>O<sub>3</sub> dielectric

thickness. Capacitors with reduced dielectric thickness have higher leakage density. The highest leakage current is obtained with the combination of thinner dielectric thickness and highest nanowire height (36 mA/cm<sup>2</sup> at 5V bias).

Figure 2. 9 Dielectric leakage current for conventional planar capacitor and Si-nanowire capacitors with nanowire etch cycles of 4, 8, and 12. Al<sub>2</sub>O<sub>3</sub> dielectric thickness is 24nm for a) and 8 nm for b).

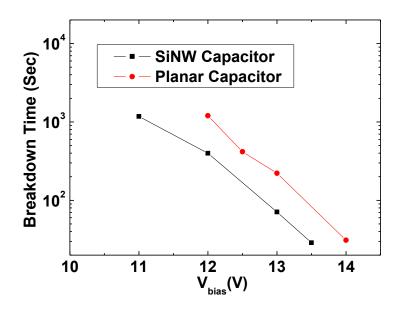

Time-dependent dielectric breakdown is also measured on Si-nanowire capacitor and compared with planar structure (Figure 2.10). The capacitor is fabricated with 450nm nanowire heights and a dielectric thickness of 24 nm Al<sub>2</sub>O<sub>3</sub>. Compared with planar structure, nanowire capacitors are slightly easier to break-down due to non-planar 3-D geometry which can enhance electric fields.

Figure 2. 10 Time-Dependent Dielectric Breakdown measurement on Si-nanowire capacitors compared with conventional planar capacitors.

# **Chapter 3 Gate-All-Around Nanowire FET**

#### 3.1 Integration challenges for GAA-nanowire FET

In chapter 2 we described a successful technique to fabricate nanowire arrays, which enables the process integration of vertical silicon nanowire field-effect-transistors. However, successful fabrication of nanowire FET requires extra steps. In this section we discuss several major challenges in the development of nanowire FET process integration:

- 1) Etching optimization for high quality nanowires.

- 2) Plasma enhanced ALD titanium nitride (TiN) as gate metal.

- 3) Gate isotropic etch and vertical patterning.

# 3.1.1 Etching optimization for high quality nanowires

There are several crucial elements to achieve vertical nanowire structure of high aspect ratio by the top-down etching approach: a nano-scale dot-shaped hard mask, high etching selectivity and very anisotropic etching technique.

It has been demonstrated in chapter 2 that silicon nitride films patterned by nano-imprint lithography can be utilized as a hard mask to etch silicon nanowires. Experimental results show that 100 nm silicon nitride film is able to sustain 1  $\mu$ m-deep silicon etching, i.e. the selectivity is around 1:10.

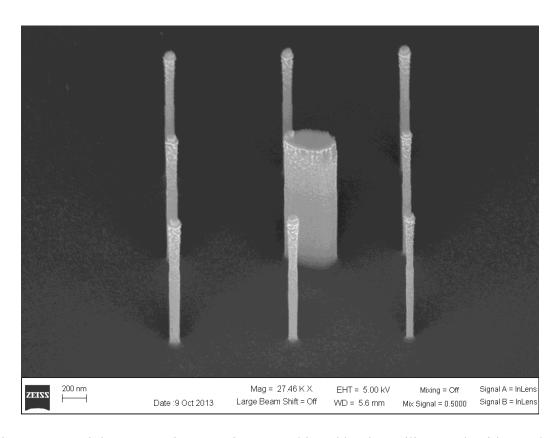

An alternative candidate for the hard mask is silicon/metal salicide[46]. In particular metal salicide is very hard to etch, so higher etch selectivity can be reached. Figure 3.1 shows a tilted SEM image of a very high aspect ratio nanowire achieved by the salicide dot mask and DSE. Also, for fabricating nanowire transistors, metal salicide is capable of reducing contact resistance to the nanowire body from top, and therefore potentially improves device performance. Electron beam lithography is compatible with

this salicide-mask-nanowire-etching process: Instead of exposing a large area on positive e-beam resist that consumes a lot of time, we exposed 100 nm-diameter area to form holes. Afterwards metal was evaporated and lifted off to achieve pillar shaped dots. Salicide was formed with 10 sec  $600^{\circ}$ C rapid thermal anneal in N<sub>2</sub> atmosphere. In Figure 3.1, the etched nanowires have a diameter of 70 nm and the height is more than 1.4  $\mu$ m.

Figure 3. 1 High aspect ratio nanowires are achieved by deep silicon etch with metal salicide mask. The aspect ratio is more than 20 on nanowires. The defect in center post probably results from metal out-diffusion during salicide anneal.

Although anisotropic silicon etching approaches by wet chemical etchants have been reported, e.g. KOH and TDMAH, it is more straightforward and controllable to etch silicon by reactive ions. HBr and Cl<sub>2</sub> plasma is able to anisotropically etch silicon with a smooth sidewall, though a well-tuned recipe is necessary[47]. In the previous chapter, we

have demonstrated another etching process (Bosch etch) that alternatively deposits polymer and etches silicon to fabricate nanowires. In our etching process, PlasmaTherm Silicon Deep RIE was utilized and  $C_4F_8$  plasma deposits polymer while  $SF_6$  etches silicon. Table 3.1 includes the detailed parameters for each process cycle that we employed in the fabrication of nanowires.

|                                                               | <b>Deposition Cycle</b>    | Etch Cycle |  |

|---------------------------------------------------------------|----------------------------|------------|--|

| Time                                                          | 0.8 sec                    | 2.0 sec    |  |

| Pressure                                                      | 20 mTorr 20 mTorr          |            |  |

| Gas Flow (Ar/SF <sub>6</sub> /C <sub>4</sub> F <sub>8</sub> ) | 10/50/125 sccm 10/50/40 sc |            |  |

| ICP Power                                                     | 1600 Watt                  | 1500Watt   |  |

| RF Bias                                                       | 10 Volt                    | 450 Volt   |  |

Table 3. 1 Process conditions of polymer deposition and silicon etching for each DSE cycle. Tool: PlasmaTherm Silicon deep RIE.

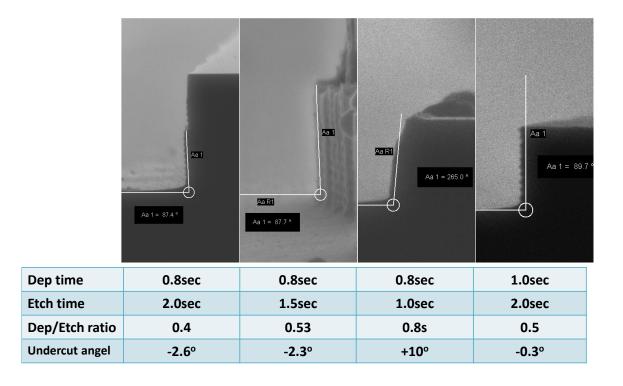

The profile of nanowire sidewall can be optimized by adjusting the ratio of etching time to deposition time in every cycle. Excessive etch/deposition ratio will undercut the etched sidewall, leading to a nail-shaped nanowire and mechanical frangibility. To investigate the influence of etch/deposition ratio on the etched sidewall, a series of experiments with a range of etch/deposition ratio were carried out, and etch results were characterized by cross-sectional SEM images, as shown in Figure 3.2. A good vertically etched sidewall is achieved when etch/deposition ratio = 0.5.

Figure 3. 2 Cross-sectional SEM images of deep silicon etching. Samples were etched with different etch/deposition ratio and sidewall undercut angels were evaluated. Result shows that the combination of 1.0 sec deposition and 2.0 sec etching yield almost 90° vertical sidewall.

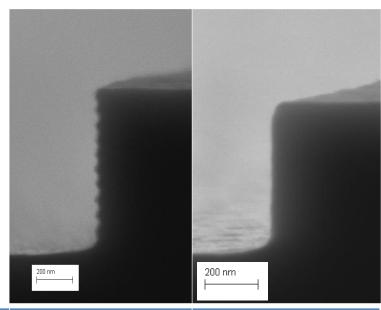

In Figure 3.2 it also can be observed that the scallops are formed on the etched sidewall, which is a signature of Bosch etching process. Each concave feature corresponds to one etch/deposition cycle. The scallops can be minimized by scaling down etching time in every cycle while keeping etch/deposition ratio as a constant. Cross-sectional SEM images of etched samples with different etching time in one cycle are shown in Figure 3.3 and the optimized sidewall was obtained when the etching time was 1.0 sec and the deposition time was 0.5 sec for each cycle. From the image, scallops were observed from the sidewall in the original recipe (left), whereas a much smoother sidewall was achieved in the optimized recipe (right). It was also noted that the etch rate

was reduced in term of the same etch time. In Figure 3.3, both samples were etched by 20 sec in total. The original recipe achieved a etch depth of ~840nm, compared to ~660nm achieved by the optimized recipe.

| Parameter       | Baseline  | Optimized |  |

|-----------------|-----------|-----------|--|

| Etch time/cycle | 2.0 sec   | 1.0 sec   |  |

| Dep time/cycle  | 1.0 sec   | 0.5 sec   |  |

| Cycle #         | 10 cycles | 20 cycles |  |

| Etch Depth*     | 839.5nm   | 660.2nm   |  |

Figure 3. 3 Etched sidewall morphology optimization. The original recipe has 2.0 sec deposition time and 1.0 sec etch time in each cycle. Scallops are observed on the etched sidewall. The optimized recipe reduces the deposition time to 1.0 sec and the etch time to 0.5 sec, and scallops are minimized on the etched sidewall. Note that the etch/deposition ratio is kept as a constant (2) in the process optimization.

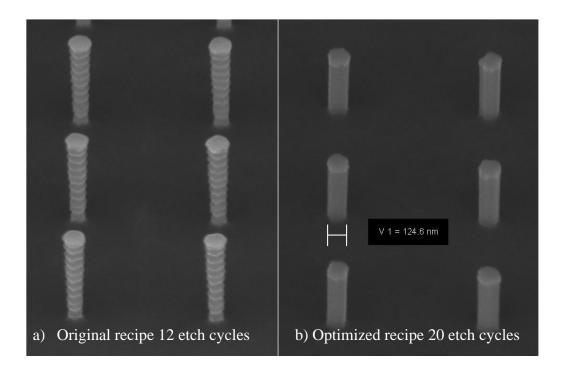

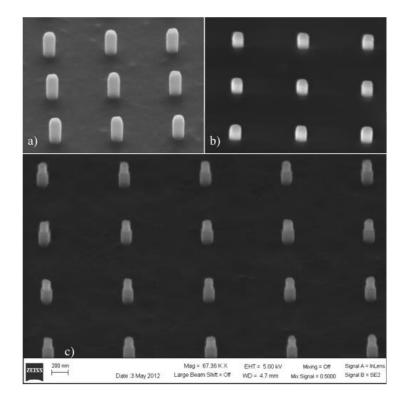

In this section we developed a new approach to fabricating high aspect ratio nanowires by e-beam lithography, metal salicide and deep silicon etching. The etched sidewall morphology highly depends on the etching conditions such as deposition/etch time, ICP power, RF bias etc,. By adjusting the etching time and deposition time in every cycle, we achieved nanowires with a smoother sidewall and undercutting defect was minimized. Figure 3.4 compares the nanowire sidewall morphologies before and after the recipe optimization. The optimized recipe greatly improves the undercutting defect and the sidewall smoothness.

Figure 3. 4 Recipe optimization result for silicon nanowire etching. The left image a) shows the nanowires etched with the original recipe. Scallops are observed on the sidewall of nanowires as well as undercutting defect. Etching process undercuts the nanowire bottom as the cycle number increases. The right image b) shows the nanowires etched with the optimized recipe. Sidewall smoothness is improved and undercutting is minimized.

### 3.1.2 Plasma Enhanced ALD as gate metal.

Gate deposition and patterning are exceedingly challenging in process integration of nanowire FETs. First, a very conformal deposition of the gate metal is necessary in order to wrap around the nanowire core and realize the gate-all-around structure. Second, the vertical gate pattern on the nanowire sidewall cannot be defined by traditional lithography approaches. The gate metal and dielectric on the upper portion of the nanowire need to be removed to expose the silicon nanowire core to the drain metal. Moreover, the gate metal should be well isolated from the drain metal on top to avoid leakage between the two metal layers.

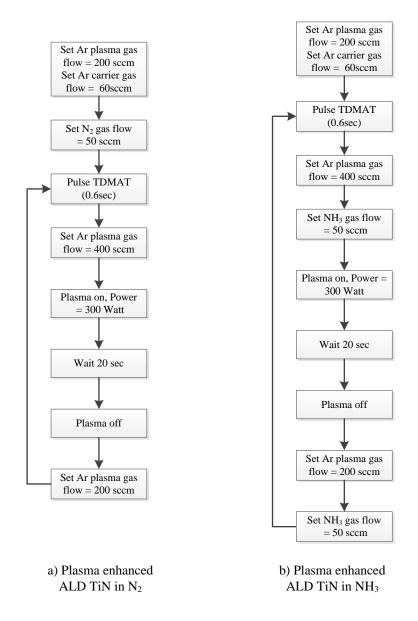

Plasma enhanced atomic layer deposition (PEALD) provides a very conformal deposition technique and is suitable for the nanowire FET process integration. ALD TiN technologies have been well studied and reported[48-50]. Several different deposition recipes were developed with Fiji plasma enhanced ALD system using TDMAT as the precursor. Figure 3.5 illustrates two typical PEALD processes in N<sub>2</sub> atmosphere and in NH<sub>3</sub>.

Figure 3. 5 Illustrations of plasma enhanced ALD TiN process in  $N_2$  (a) and  $NH_3$  (b) respectively. Note that  $NH_3$  should be turned off while pulsing TDMAT.

Since NH<sub>3</sub> is reactive to TDMAT, NH<sub>3</sub> valve must be turned off when pulsing TDMAT. The deposition rates of PEALD TiN are 0.73 Å and 1.82 Å per cycle in N<sub>2</sub> and NH<sub>3</sub> atmosphere, respectively. Sheet resistances were measured on PEALD TiN films on

silicon substrate with 100 Å  $Al_2O_3$  dielectric. Resistivity can be calculated with the measured sheet resistance and the film thickness by:

$$\rho = R_s \times t$$

where t is the film thickness.

Measured sheet resistances of TiN films deposited in  $N_2$  and  $NH_3$  are 136.2  $\Omega/\Box$  and 1132.6  $\Omega/\Box$  respectively, and therefore the calculated resistivities are 367  $\mu\Omega$  cm and 2830  $\mu\Omega\cdot$ cm.

Deposited TiN films can be etched by reactive ion etching (dry etch) or wet chemical etching. In the test vehicle 270 Å TiN was etched by  $CF_4$  plasma within 2 min with 200 watt power. To form the vertical pattern along the sidewall of nanowire, isotropic etching is preferred. TiN wet chemical etching with SC-1 solution (NH<sub>4</sub>OH:H<sub>2</sub>O<sub>2</sub>:H<sub>2</sub>O=1:1:5) had been reported[51] and etching tests were carried out on TiN samples prepared in N<sub>2</sub> and in HN<sub>3</sub> respectively. Test results show that SC-1 solution etches the TiN film prepared in NH<sub>3</sub> with a rate of c.a. 2.2 nm/min, and that prepared in N<sub>2</sub> at a very slow rate.

The properties of the films deposited by two different approaches are compared in Table 3.2.

| Process Conditions    | Recipe 1     | Recipe 2        |  |

|-----------------------|--------------|-----------------|--|

| Deposition atmosphere | $N_2$        | NH <sub>3</sub> |  |

| Plasma Power          | 300 Watt     | 300Watt         |  |

| Cycles                | 350 cycles   | 150 cycles      |  |

| Film thickness        | ~270 Å       | ~270 Å          |  |

| Deposition            | 0.77 Å/cycle | 1.8 Å/cycle     |  |

| Sheet Resistance      | 136 Ω/□      | 1133 Ω/□        |  |

| Resistivity           | 367 μΩ cm    | 3059 μΩ cm      |  |

| Etch Rate             | Very Slow    | 2.2nm/min       |  |

Table 3. 2 Process conditions and film qualifications of TiN deposited in N2 and NH3.

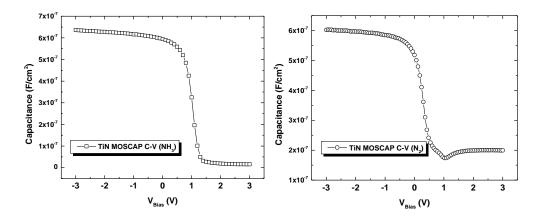

Metal-oxide-semiconductor capacitors (MOSCAPs) were fabricated with both types of TiN and test results show good C-V characteristics. The results confirm that the fabricated TiN films perform well as a gate metal material (Figure 3.6). The measured samples were fabricated on a lightly doped p-type substrate with 100 Å ALD Al<sub>2</sub>O<sub>3</sub> as the dielectric. Under a negative bias, the accumulation capacitance is  $\sim 0.6~\mu F/cm^2$ , which agrees with the theoretical parallel-plate capacitor model.

Figure 3. 6 C-V characteristics of fabricated MOS capacitors with plasma enhanced ALD TiN as the gate metal

# 3.1.3 Gate isotropic etch and vertical patterning

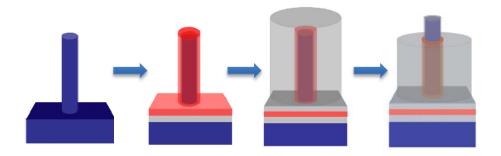

After conformal atomic layer depositions, silicon nanowires were fully covered by gate dielectric and gate metal. On the nanowire sidewall, the gate metal needs to be patterned to achieve the designed gate length, and also to expose the nanowire core to the drain metal. Since traditional lithography approaches could not define the vertical pattern, an alternative resist spin-on and etch back process was developed. As illustrated in Figure 3.7, after the gate metal and dielectric were deposited onto nanowires, resist was spun on the sample and fully covered the nanowires and planarized the surface. Following O<sub>2</sub> plasma etching slowly thinned the resist at a controllable rate, until the desired gate length was achieved. Then the uncovered metal was removed by anisotropic etching. Figure 3.8 shows tilted SEM images of a nanowire sample with this spin-on and etch-back process to form the gate pattern.

Figure 3. 7 Illustration for resist spin-on and etch-back process to vertically pattern the gate metal.

Figure 3. 8 Resist spin-on and etch-back process to vertically pattern the gate metal. a)  $Al_2O_3$  and TiN are deposited on nanowires. b) Resist is spun and etched back to define the gate length. c) Exposed TiN is wet etched by SC-1 solution and the resist is removed.

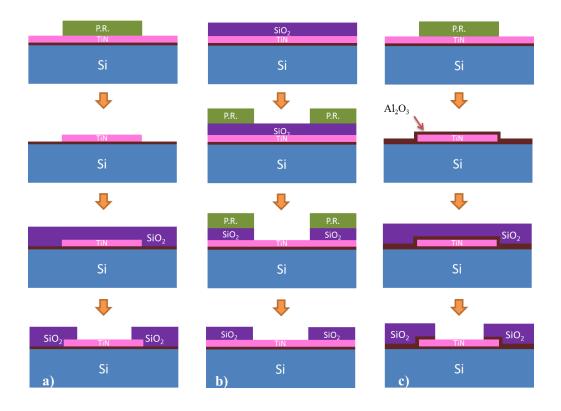

For the process integration of nanowire FETs, TiN was patterned as the gate metal pad and PECVD SiO<sub>2</sub> was used as an inter-metal dielectric to electrically isolate the drain metal from the gate metal. After the drain metallization, PECVD SiO<sub>2</sub> was locally etched away by hydrofluoric acid (HF) to access the buried gate metal, i.e. the TiN film. However, it had been found that the conductivity of the TiN film was severely degraded after a series of processes of photolithography, PECVD SiO<sub>2</sub> and HF etching. The TiN film after these processes exhibited an extraordinarily high resistivity and hindered the gate control. A set of experiments were designed to diagnose the failure and find a feasible approach to avoid the degradation: Three dummy structures were fabricated to test the TiN conductivity after the process integration:

- a) A PEALD TiN film was patterned by photolithography, followed by PECVD SiO<sub>2</sub> deposition. A contact window was opened by the second lithography and HF wet etching so that the buried TiN film was accessed. As shown in Figure 3.9a.

- b) PECVD  $SiO_2$  was deposited on TiN immediately after PEALD. Photolithography patterned the  $SiO_2$ , followed by HF etching to access the TiN film. As shown in Figure 3.9b.

- c) A PEALD TiN film was patterned by photolithography, covered by 200 Å ALD  $Al_2O_3$  capping layer. Then PECVD  $SiO_2$  was deposited on the  $Al_2O_3$ . The  $2^{nd}$  photolithography opened a contact window and HF etched  $SiO_2$  and  $Al_2O_3$  through the window to access the TiN film. As shown in Figure 3.9c.

Figure 3. 9 Test structures to investigate TiN film conductivity degradation.

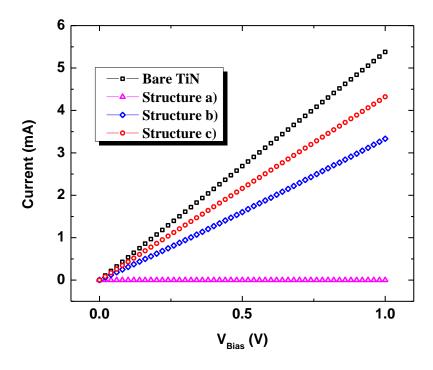

To evaluate the conductivity degradation, two probes were placed on the same TiN contact pad (size:  $100~\mu m$  x  $100~\mu m$ ) and the conducting current was measured under a voltage bias. For comparison, the I-V characteristic of a bare TiN film was also measured. It was found that the TiN film in test structure b) and c) behaved as a conductive metal, whereas in structure a) the TiN became highly resistive as an insulator. Although the degradation mechanism was unknown, the results indicated that the TiN conductivity degradation can be avoided by capping  $SiO_2$  on TiN before photolithography, or by capping  $Al_2O_3$  on post-lithography TiN before PECVD  $SiO_2$ . The measured data is plotted in Figure 3.10.

Figure 3. 10 Measured I-V on TiN gate metal with different test structures of TiN process integration.

Besides PEALD TiN, other metal candidates and potential etching techniques are also investigated for the nanowire FET process integration. For instance, sputtered TaN was deposited and tested for as the gate metal candidate. However it was very difficult to vertically pattern TaN: the poor sidewall deposition quality makes wet etch uncontrollable, wet etching. CF<sub>4</sub> dry etch also introduces contamination and lead to large C-V hysteresis. Table 3.3 summaries the materials and techniques for the gate metal integrations. Functional nanowire FET devices are achieved by utilizing PEALD TiN (NH<sub>3</sub>) as the gate metal, PECVD SiO<sub>2</sub> as the etch mask and 1:1:5 SC-1 as the metal etchant.

| Gate Metal                    | Etch<br>Mask              | Etchant                            | Patterning result   | Post Process resistivity | Other<br>Comments                |

|-------------------------------|---------------------------|------------------------------------|---------------------|--------------------------|----------------------------------|

| Sputtered<br>TaN              | Resist                    | EDTA+H <sub>2</sub> O <sub>2</sub> | Over etch           | -                        | -                                |

|                               | Resist                    | CF <sub>4</sub> dry etch           | Good                | Very low                 | Large C-V hysteresis             |

| $ m ALD~TiN \ (N_2)$          | Resist                    | 1:1:5 SC-1                         | Very slow etch rate | Very High                | No<br>significant<br>TiN etching |

|                               | Resist                    | CF <sub>4</sub> dry etch           | Recipe not stable   | Very High                | -                                |

|                               | PECVD<br>SiO <sub>2</sub> | Piranha Dip                        | Over etch           | Very low                 | Etching is uncontrollable        |

|                               | PECVD<br>SiO <sub>2</sub> | 1:2:5 SC-1<br>@60°C                | Over etch           | Very low                 | and sidewall<br>pattern is lost  |

| ALD TiN<br>(NH <sub>3</sub> ) | Resist                    | 1:1:5 SC-1                         | Good                | Very High                | -                                |

|                               | PECVD<br>SiO <sub>2</sub> | 1:1:5 SC-1                         | Good                | Low                      | Functional<br>device<br>achieved |

Table 3.3 Materials and etching techniques for the nanowire FET gate metal integration. Successful integration is achieved by utilizing PEALD TiN (NH<sub>3</sub>) as the gate metal, PECVD SiO<sub>2</sub> as the gate mask and 1:1:5 SC-1 as the gate metal etchant.

In summary, we discussed several major challenges for the nanowire FET process integration and explored mythologies to address the technical barriers. Firstly we proposed a new approach to patterning the nanowires with EBL and metal salicide. Then DSE process was optimized to achieve vertical nanowires with a smooth sidewall. We also developed conformal metal deposition methods with plasma enhanced ALD. The

film quality and etching approaches were also investigated. In order to integrate TiN film as a gate metal without compromising the conductivity, several test structures were compared and solutions were proposed.

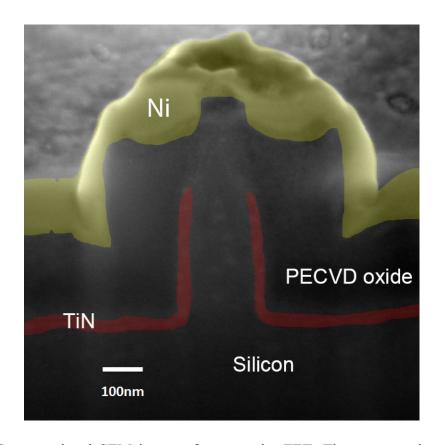

#### 3.2 PROCESS DEVELOPMENT GATE-ALL-AROUND NANOWIRE FETS

Based on the highly ordered silicon nanowire array, gate-all-around nanowire pMOSFETs were fabricated. The design of the device structure is illustrated in Figure 3.11. Similar to nanowire capacitors, the silicon nanowires that were fabricated by DSE were vertical to the substrate wafer. Multiple nanowires can be integrated in one device in parallel to contribute a larger drive current. The boron doped substrate served as the source terminal for the p-type MOSFET, and the Si nanowires were lightly doped by phosphorus as the channel. On the top of nanowires, the drain was heavily doped by boron and metal salicide was formed to reduce the contact resistance. Along the nanowire sidewall, the high-κ dielectric and gate metal were wrapped around the silicon nanowire core to achieve the gate-all-around structure. Atomic layer depositions can yield very conformal films and thus is the preferred process for dielectric and metal depositions[52]. The drain metal on top was isolated from the buried gate metal layer by an inter-metal dielectric, for example PECVD SiO<sub>2</sub>.

Figure 3. 11 Schematic of a vertical nanowire field-effect-transistor.

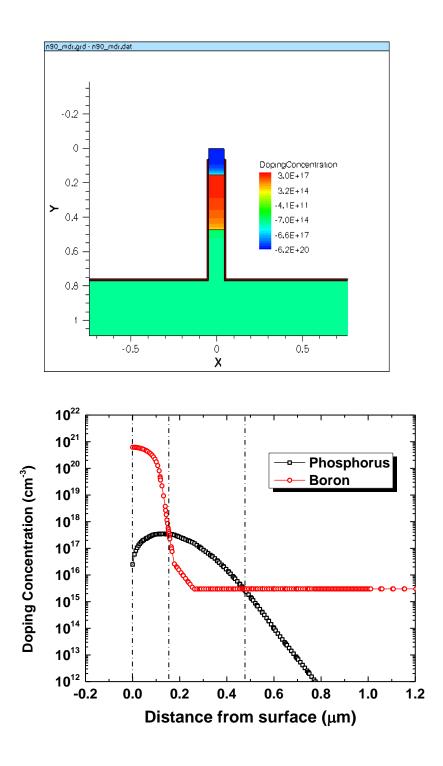

In order to achieve the desired the p-n-p doping profile for p-MOS, we used epitaxy silicon wafer and pre-doped the wafer before the nanowire was etched. The wafer had a highly doped p-type substrate and an epitaxy p- layer of 7-11  $\mu$ m in thickness, which served as the common source for the nanowire FETs. Phosphorus was implanted using 100 keV energy and  $1x10^{13}$ /cm<sup>2</sup> dose to dope the n-type channel region. After 1 hour  $1000^{\circ}$ C activation annealing, the junction depth was diffused to 470 nm below the wafer surface. Drain is doped by boron implantation with a dosage of  $5x10^{15}$ /cm<sup>2</sup> at 20 keV, followed by a 10 sec thermal activation at  $1000^{\circ}$ C. Figure 3.12 shows the simulated doping concentration profile for nanowire FETs. Simulation result indicates that the drain doping has a peak concentration of  $10^{21}$  /cm<sup>3</sup> and a junction depth of 150nm, while the peak concentration in n-type channel is  $10^{17}$ /cm<sup>3</sup> and channel length is  $\sim 320$ nm.

Figure 3. 12 Simulated doping concentration for nanowire FETs.

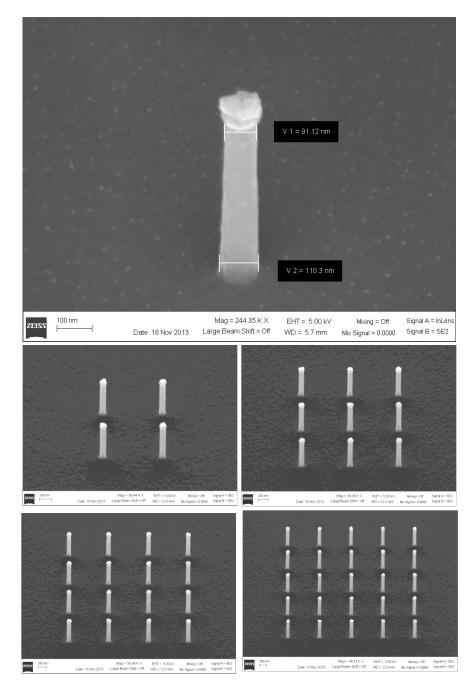

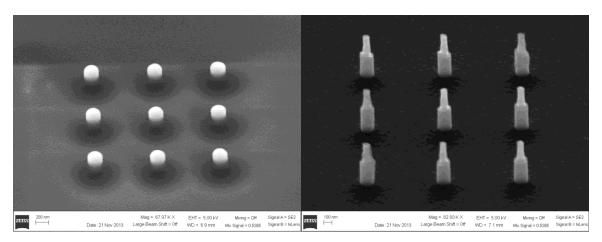

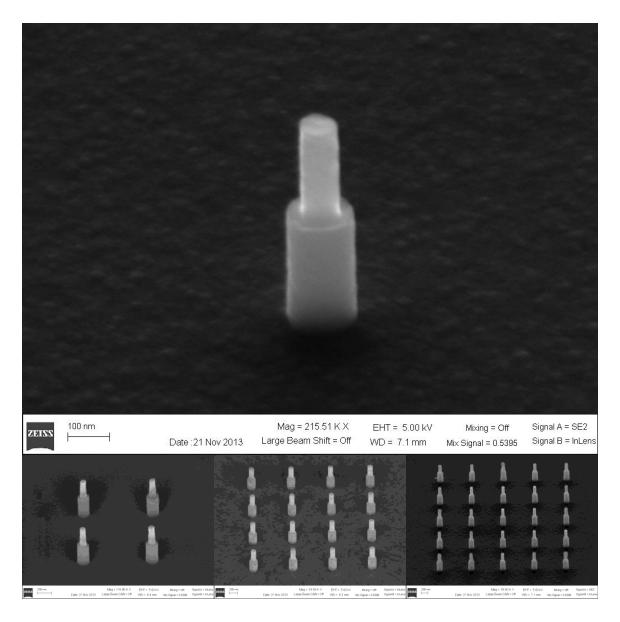

The sample was patterned by JEOL electron beam lithography after doping. First 100 nm-diameter hole-array was patterned on the ZEP resis. Next, 200Å titanium followed by 200Å nickel was deposited on the sample with e-beam assisted evaporation and consequent lift-off process left metal dots array on silicon surface. Metal/silicon salicide was formed after 600°C 10 sec rapid thermal anneal in  $N_2$ , which not only acted as a hard mask for DSE but also reduced the drain contact resistance. We patterned a variety size of arrays:  $1 \times 1$ ,  $2 \times 2$ ,  $3 \times 3$ ,  $4 \times 4$  and  $5 \times 5$ . The following 30 cycles of DSE realized the nanowire array with a height of ~720nm. 45° tilted SEM images are shown in Figure 3.13. The salicide on top of each nanowire is observed.

Figure 3. 13 Etched silicon nanowire array patterned by e-beam lithography and masked by Ti/Ni salicide. Nanowires height is  $\sim$  720 nm and diameter is  $\sim$  90 nm. Aspect ratio is  $\sim$  1:8.

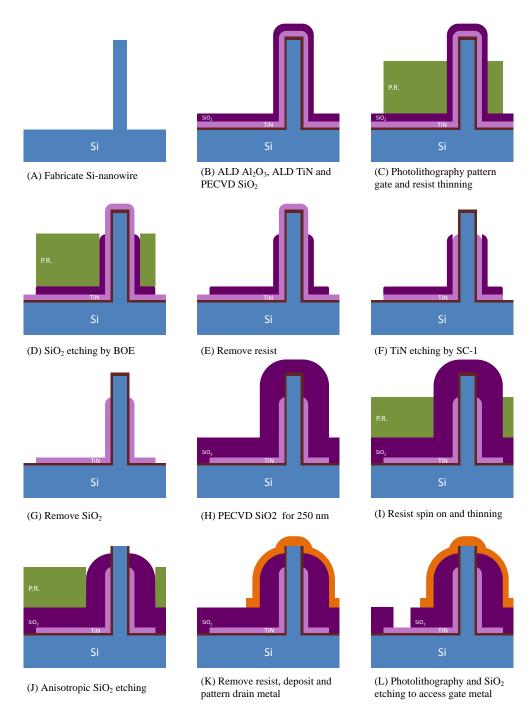

The fabrication process flow of silicon nanowire FETs is illustrated in Figure 3.14. First 200 Å Al<sub>2</sub>O<sub>3</sub> was deposited by ALD on the nanowire as gate dielectric at 250°C, followed by the PEALD 500Å TiN for gate metal in NH<sub>3</sub> atmosphere. Then a 500Å SiO<sub>2</sub> capping layer was deposited by PECVD to protect the gate metal (Figure 3.14 a-b)

Figure 3. 14 Process flow of nanowire FETs

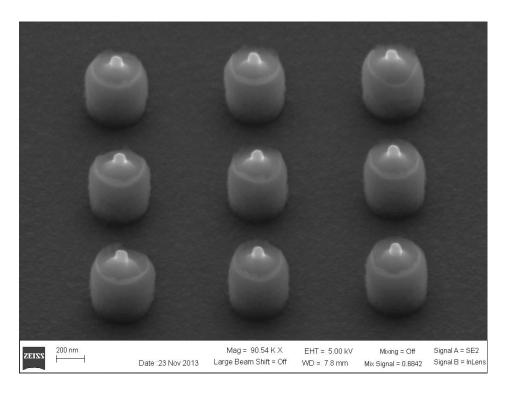

After the 3-step depositions, photolithography defined  $200\times500~\mu\text{m}^2$  gate metal pads. After development and hard bake, the photoresist had a height of 0.9  $\mu$ m so that the 720 nm-tall nanowires were completely buried by the resist. To vertically pattern the gate metal, a controllable  $O_2$  plasma etch-back process was performed to thin the resist. After 2 min etch-back, residual resist only covered the bottom portion of nanowires, as shown in Figure 3.14c. The exposed  $SiO_2$  capping layer was removed by 15sec BOE dip (Figure 3.14d) and afterwards SC-1 (NH<sub>4</sub>OH:H<sub>2</sub>O<sub>2</sub>:H<sub>2</sub>O = 1:1:5 at room temperature) solution etched upper portion of TiN to form the wrapped-gate pattern (Figure 3.14f). Figure 3.15a shows a device with 9 nanowires after the resist thinning and figure 3.15b exhibits the gate pattern after TiN was etched (resist was removed). The gate covers the lower portion of the nanowires and channel length is ~320nm. Gate overlap can be controlled by  $O_2$  plasma thinning process. Figure 3.16 shows devices with different number of nanowires when the gate-all-around pattern was accomplished.

Figure 3. 15 nanowire FET after resist thinning (left) and gate patterning (right).

Figure 3. 16 Silicon nanowire FETs with vertical wrapped gate pattern.

To isolate the gate metal layer from the drain metal layer, a 250 nm PECVD SiO<sub>2</sub> film was deposited as inter-metal dielectric (Figure 3.14h). Similar to the gate vertical patterning, resist was spun-on and thinned with 130 sec O<sub>2</sub> plasma etch-back (Figure 3.14i). PECVD SiO<sub>2</sub> cap was removed by a controllable anisotropic plasma etch with a

mix gas of CHF<sub>3</sub> and  $O_2$  (Figure 3.14j) to uncover the nanowires for the drain metallization. As shown in Figure 3.17, a 5 min etching consumed approximately 350 nm SiO<sub>2</sub> and exposed c.a. 100 nm Si nanowire core. Al<sub>2</sub>O<sub>3</sub> gate dielectric on top of the nanowire was also broken through during the excessive plasma etching. From the image it can be observed that nanowire cores are uncovered from the PECVD SiO<sub>2</sub> and exposed to the drain metallization.

Figure 3. 17 Tilted SEM image of silicon nanowire FET after PECVD SiO<sub>2</sub> etch. Nanowire cores are exposed on top of the device for the drain metallization.

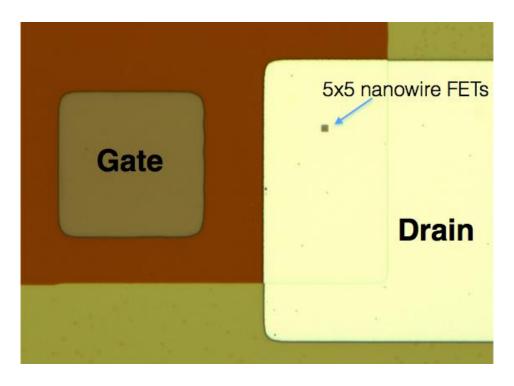

The drain contact pad was patterned by the 2<sup>nd</sup> photolithography and lifted-off. 150nm nickel film was deposited by e-beam assisted evaporation so that the metallization was formed with the salicide on nanowires (Figure 3.14k). To access the buried TiN gate

metal, contact windows through PECVD SiO<sub>2</sub> were opened by the 3<sup>rd</sup> photolithography and 2 min BOE dip (Figure 3.14l). Top-view microscope image is shown in Figure 3.18 for device layout illustration.

Figure 3. 18 Top-view microscope image of final device layout. Drain is the top nickel films and gate is buried under SiO<sub>2</sub> inter-metal dielectric. A contact window is opened by photolithography.

To gain the inside view of the fabricated nanowire FET, focused ion beam (FIB) was utilized to create a cross-section through a particular nanowire, along with the MOSFET structures. In Figure 3.19 a SEM image of the created cross-section is presented.

Figure 3. 19 Cross-sectional SEM image of a nanowire FET. The cross-section that is created by focused ion beam (FIB) cuts through the nanowire core.

### 3.3 DEVICE CHARACTERIZATION AND DISCUSSION

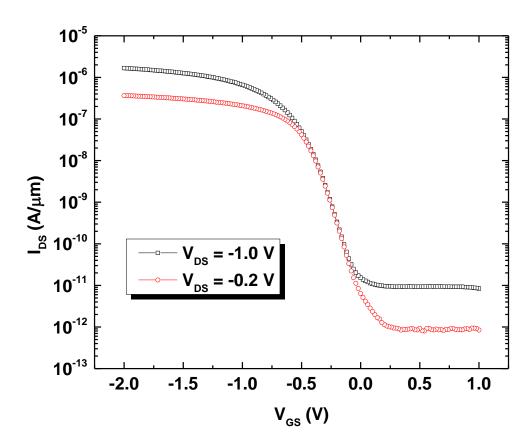

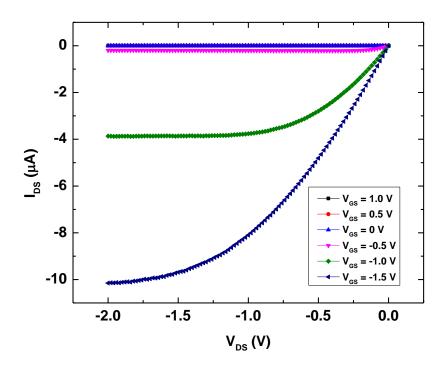

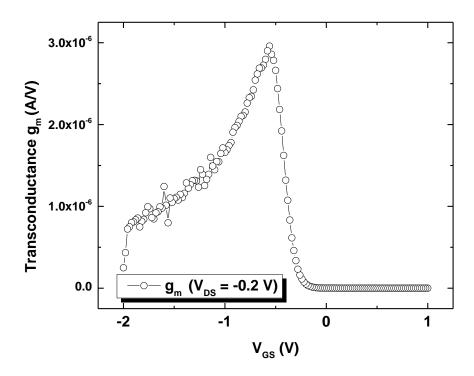

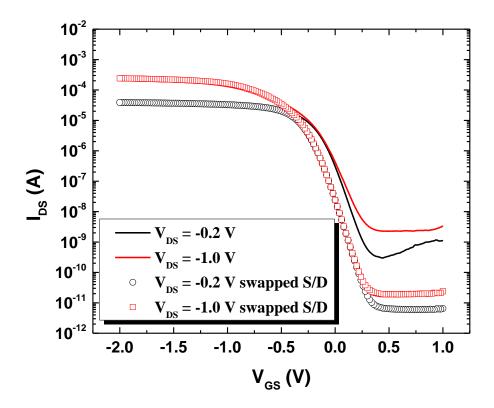

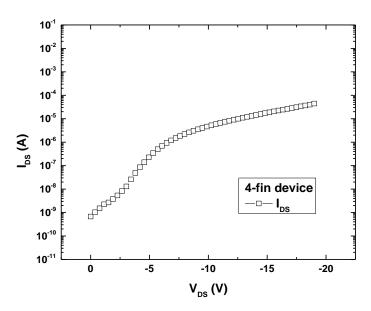

The fabricated vertical nanowire FETs were characterized at room temperature using the substrate as the source. The transfer characteristic ( $I_d$ - $V_g$ ) indicates that the Si nanowire FET behaves as a typical p-MOS field-effect-transistor and the result is plotted in Figure 3.19. This characterized device has 25 nanowires in parallel, with a channel length of approximately 320nm. Each nanowire has a diameter of 90 nm and a gate dielectric of 200 Å  $Al_2O_3$ , i.e. ~10 nm effective oxide thickness (EOT). The gate voltage is swept from 1 V to -2 V with a step of -0.02 V, while  $V_{DS}$  is kept at -0.2 V and -1.0 V. The  $I_d$ - $V_g$  curve shows a good DC characteristic with the  $I_{on}/I_{off}$  ratio >10<sup>5</sup>. The on-state