Copyright

by

Jongho Lee

2014

# The Dissertation Committee for Jongho Lee Certifies that this is the approved version of the following dissertation:

# Graphene Field Effect Transistors for High Performance Flexible Nanoelectronics

| Committee:                 |

|----------------------------|

| Deji Akinwande, Supervisor |

| Ray Chen                   |

| Ananth Dodabalapur         |

| Emanuel Tutuc              |

| Li Shi                     |

# Graphene Field Effect Transistors for High Performance Flexible Nanoelectronics

by

Jongho Lee, B.E.; M.E.

#### **Dissertation**

Presented to the Faculty of the Graduate School of

The University of Texas at Austin

in Partial Fulfillment

of the Requirements

for the Degree of

**Doctor of Philosophy**

The University of Texas at Austin

May 2014

## **Dedication**

This dissertation is dedicated to my parents for providing endless love and support, and to my wife and daughter.

#### Acknowledgements

I am grateful to all the people who supported me during my Ph.D. program. Firstly, I would like to express my special thanks to my advisor, Prof. Deji Akinwande. it was a great experience for me to have been one of his students at the University of Texas at Austin. As the academic advisor, he has given me helpful suggestions and a great guidance during my graduate study. Also I would like to thank my committee members, Dr. Ray Chen, Dr. Ananth Dodabalapur, Dr. Emanuel Tutuc, and Dr. Li Shi for their invaluable suggestions on my work.

I appreciate all the support from my colleagues. Dr. Li Tao has contributed enormously to my Ph.D. work. As a co-worker, he provided a lot of helpful suggestions while developing the process technologies. I would also express my thanks to our group members: Sk. Fahad Chowdhury, Hsiao-Yu Chang, Milo Holt, Kristen Parrish, Avinash Nayak, Maruthi Yogeesh, Nassibe Somayyeh Rahimi, and Saungeun Park.

I am grateful to Dr. Yufeng Hao and Dr. Huifeng Li in Prof. Rodney Ruoff's research lab for providing me high quality graphene films for device fabrication. I would also like to thank Dr. Wi Hyoung Lee, Dr. Ji Won Suk, and Dr. Jin-Young Kim for sharing their expertise on material science and practical knowledge on novel materials.

Additionally, the collaboration with Dr. Tae-Jun Ha in Prof. Ananth Dodabalapur's research group was unforgettable. I really appreciate his interest and feedback on my work.

I am also grateful to Jo Ann Smith. Her kind help and timely practical supports on my academic works helped me to make it successfully though my graduate study as a graduate research assistant. I want to express my thanks to my Korean friends. Dr. Junyoung Park and Dr. Jaehong Min have been my best friends and helped me a lot from the beginning of my days at the UT Austin. I really appreciate their heartwarming friendship.

Finally, special thanks should go to my lovely family for their supports and unconditional love. Especially, Dr. Mikyung Shin, my wife, has encouraged and supported me with her endless love and helped me successfully complete my study. Also thanks to my parents, and my adorable daughter, Bomi. Thank you.

**Graphene Field Effect Transistors for High Performance Flexible Nanoelectronics**

Jongho Lee, Ph.D.

The University of Texas at Austin, 2014

Supervisor: Deji Akinwande

Abstract: Despite the widespread interest in graphene electronics over the last decade, high-performance graphene field-effect transistors (GFETs) on flexible substrates have been rarely achieved, even though this atomic sheet is widely understood to have greater prospects for flexible electronic systems. In this work, we investigate the realization of high-performance graphene field effect transistors implemented on flexible plastic substrates. The optimum device structure for high-mobility and high-bendability is suggested with experimental comparison among diverse structures including top-gate GFETs (TG-GFETs), single/multi-finger embedded-gate GFETs with high-k dielectrics (EG-highk/GFETs), and embedded-gate GFETs with hexagonal boron nitride (h-BN) dielectrics. Flexible graphene transistors with high-k dielectric afforded intrinsic gain, maximum carrier mobility of 8,000 cm<sup>2</sup>/V·s, and importantly 32 GHz cut-off frequency. Mechanical studies reveal robust transistor performance under repeated bending down to 0.7 mm bending radius whose tensile strain corresponds to 8.6%. Passivation techniques, with robust mechanical and chemical protection in order to operate under harsh environments, for embedded-gate structures are also covered. The integration of functional coatings such as highly hydrophobic fluoropolymers combined with the self-passivation properties of the polyimide substrate provides water-resistant protection without compromising flexibility, which is an important advancement for the realization of future robust flexible systems based on graphene.

## **Table of Contents**

| List of Tal | ble                                                                | xi  |

|-------------|--------------------------------------------------------------------|-----|

| List of Fig | ures                                                               | xii |

| Chapter 1:  | Introduction                                                       | 1   |

|             | Graphene Field-Effect Transistor                                   | 1   |

|             | Flexible Electronics                                               | 2   |

|             | Thesis Outline                                                     | 3   |

| Chapter 2:  | Preparation of Electronic-Grade Flexible Substrates                | 4   |

|             | Requirements for Flexible Substrates                               | 4   |

|             | Commercially Available Flexible Substrates                         | 5   |

|             | Surface Preparation of Polymer Substrates for Device Fabrication . | 8   |

| Chapter 3:  | Transistor Device Topology                                         | 12  |

|             | Top-Gate Graphene Field-Effect Transistors                         | 12  |

|             | Embedded-Gate Graphene Field-Effect Transistors                    | 15  |

|             | Modified Embedded-Gate Graphene Field-Effect Transistors           | 16  |

|             | Comparison of Device Structures                                    | 19  |

| Chapter 4:  | Design Considerations for Optimization                             | 23  |

|             | Contact Resistance                                                 | 24  |

|             | Embedded-Gate Electrodes                                           | 30  |

|             | Passivation Techniques for Embedded-Gate Structures                | 35  |

|             | Thermal Management                                                 | 38  |

| Chapter 5:  | Experimental Results : Electrical / Mechanical Performances        | 40  |

|             | DC Characteristics of Graphene Field-Effect Transistors            | 40  |

|             | High Frequency Response $(f_T \text{ and } f_{MAX})$               | 45  |

|             | Mechanical Bendability                                             | 51  |

|             | Liquid Exposure                                                    | 56  |

| Chapter 6:  | Summary and Future Works                                           | 60  |

|             | Summary                                                            | 60  |

|             | Future Works60                                                                                    |  |

|-------------|---------------------------------------------------------------------------------------------------|--|

| Appendix    |                                                                                                   |  |

|             | A.1. Preparation of Double-Side Coated Polyimide Substrates62                                     |  |

|             | A.2. Wet Transfer Process of Graphene Films                                                       |  |

|             | A.3. Oxygen Plasma Reactive Ion Etch of Graphene Films66                                          |  |

|             | A.4. Capture-Release Process for Exfoliated Hexagonal Boron Nitride Embedded in Polyimide         |  |

|             | A.5. Low Power Plasma Enhanced Chemical Vapor Deposition of Si <sub>3</sub> N                     |  |

|             | A.6. Selective Dry Etch of Plasma Enhanced Chemical Vapor Deposite Si <sub>3</sub> N <sub>4</sub> |  |

|             | A.7. Multi-Finger Embedded-Gate Graphene Field Effect Transistor (MEGFET)                         |  |

| Reference   | s85                                                                                               |  |

| List of Jou | urnal Publications 94                                                                             |  |

## **List of Table**

| Table 2.1 | Material properties of commercial flexible substrates | 7  |

|-----------|-------------------------------------------------------|----|

| Table 3.1 | Comparison of 3 flexible GFET device structures       | 22 |

# **List of Figures**

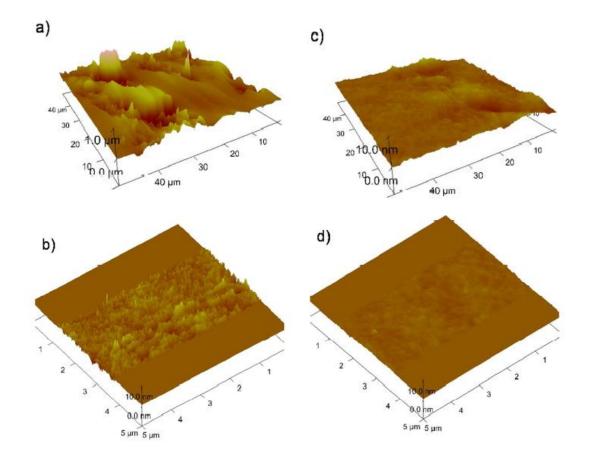

| Figure 2.1. | AFM images of polyimide surfaces. (a) $50x50  \mu\text{m}^2$ , (b) $5x2.5  \mu\text{m}^2$ scan  |

|-------------|-------------------------------------------------------------------------------------------------|

|             | on polyimide sheet as received and (c) $50x50 \mu m^2$ , (d) $5x2.5 \mu m^2$ scan               |

|             | after surface treatment9                                                                        |

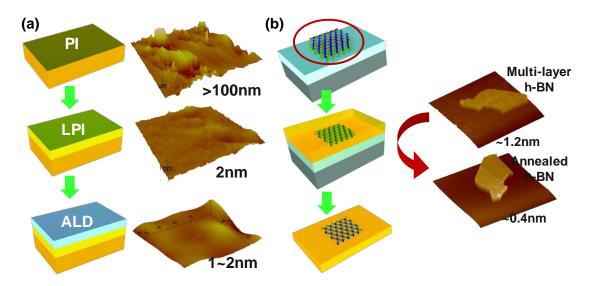

| Figure 2.2. | 3-D illustrations of different flexible substrates preparation techniques.                      |

|             | (a) The surface treatments on flexible PI films. An as-received PI film, a                      |

|             | cured liquid PI coated on a PI film, and an ALD deposited on a cured                            |

|             | film are shown with their AFM images and roughness values. (b)                                  |

|             | Preparation of an embedded h-BN film captured in a free-standing PI                             |

|             | substrate. The simplified process flow is given with the AFM images                             |

|             | scanned over an as-exfoliated h-BN film (roughness ~1.2nm) and an                               |

|             | annealed h-BN film (roughness ~0.4nm)11                                                         |

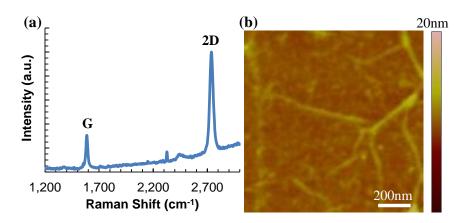

| Figure 3.1. | Monolayer graphene on copper foil (a) Raman spectrum of the                                     |

|             | synthesized monolayer graphene on copper foil indicating the 2D and G                           |

|             | peaks. (b) AFM image of graphene transferred to flexible polyimide                              |

|             | sheet with a surface roughness ~2nm and wrinkles as high as 8nm. 14                             |

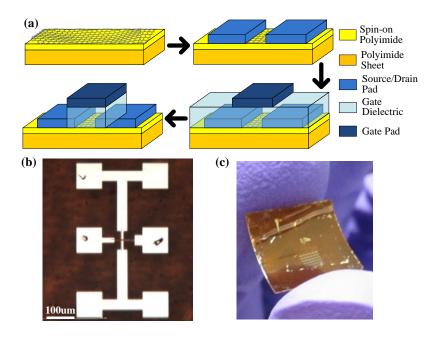

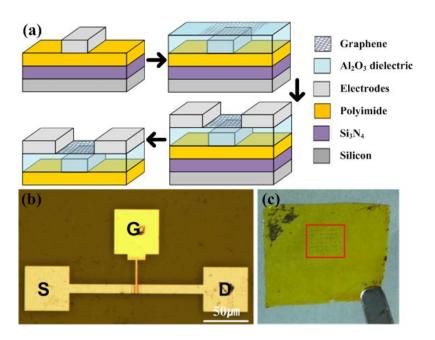

| Figure 3.2. | Top-gate graphene transistor on polyimide sheet (a) Simplified cross-                           |

|             | sectional fabrication process for graphene transistor on polyimide sheet                        |

|             | featuring transferred CVD graphene, high-k Al <sub>2</sub> 0 <sub>3</sub> dielectric, and metal |

|             | electrodes. (b) Optical image of a completed GFET with two gate                                 |

|             | fingers in a GSG configuration to facilitate high-frequency                                     |

|             | measurements. The device length and total width are $0.25\mu m$ and $10\mu m$                   |

|             | respectively. (c) Photograph of the flexible substrate with an array of                         |

|             | integrated GFETs. 14                                                                            |

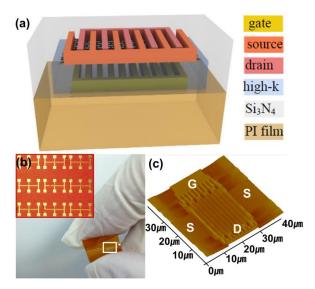

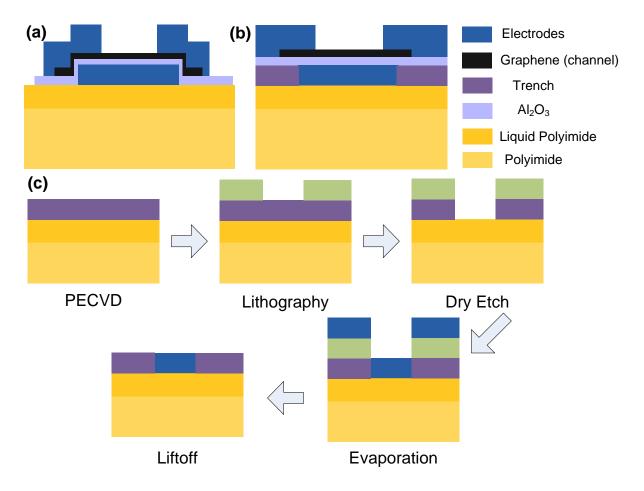

| Figure 3.3. | Embedded-gate graphene FET (a) Illustration of the EGFET fabrication          |

|-------------|-------------------------------------------------------------------------------|

|             | process on spin-coated PI on a $Si_3N_4/Si$ substrate. (b) Optical image of a |

|             | completed EGFET. The device length and width are 4 and 8 $\mu m$              |

|             | respectively. (c) Photograph of the flexible substrate with an array of       |

|             | EGFETs. The highlighted square shows the array of devices17                   |

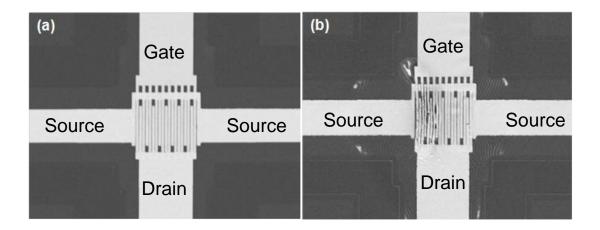

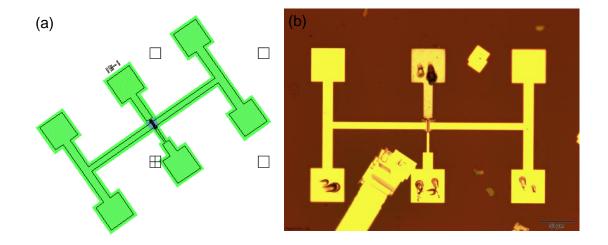

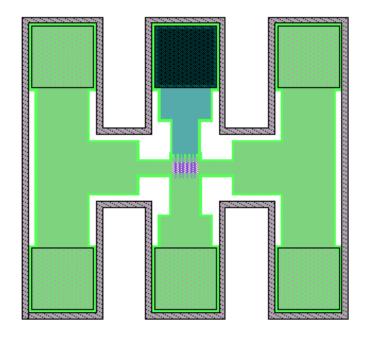

| Figure 3.4. | Multi-finger EGFET fabricated on plastic substrates. (a) 3-D image of         |

|             | the complete device of a 10-finger unit cell. (b) Optical image of the        |

|             | sample. The device area is highlighted by a white rectangle. Inset shows      |

|             | an array of the unit cells with gate (G), source (S), and drain (D) pads.     |

|             | (c) AFM image of the active channel area revealing a device with 10-          |

|             | fingers                                                                       |

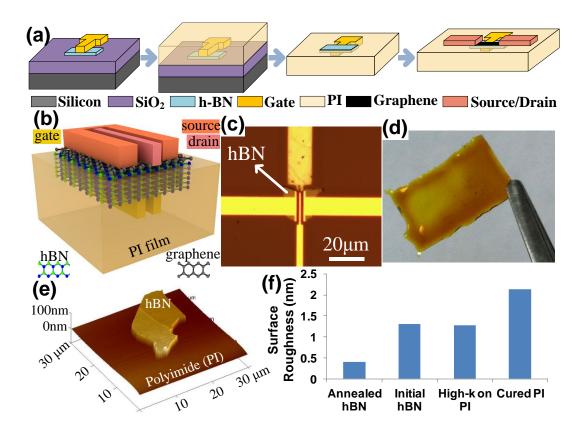

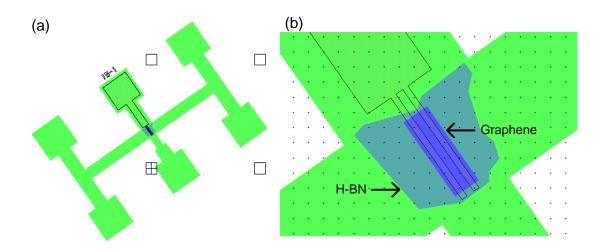

| Figure 3.5. | Illustration and images of fabricated EG-hBN GFET. (a) Simplified             |

|             | process flow. (b) Illustration of a fabricated device. (c) Optical image of   |

|             | the channel area with a dual-finger embedded-gate GFET. (d) GFETs on          |

|             | a PI film. (e) Surface of the smooth h-BN on flexible PI as measured by       |

|             | AFM. (f) Comparison of different surface roughnesses for graphene             |

|             | integration on flexible PI. The annealed h-BN surface features                |

|             | smoothness comparable to interlayer spacing in graphene20                     |

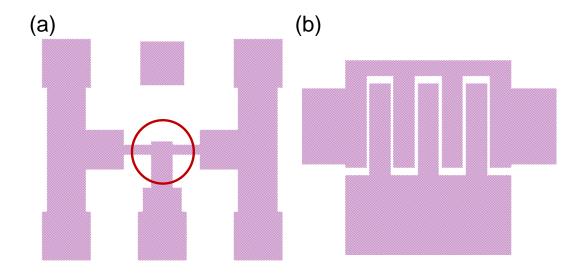

| Figure 4.1. | Contact electrodes patterns. (a) Type-I. Conventional contacts without        |

|             | edge-injection patterns. (b) Type-II. Contacts with line-type edge-           |

|             | injection patterns. (c) Type-III. Contacts with array-type edge-injection     |

|             | patterns. 29                                                                  |

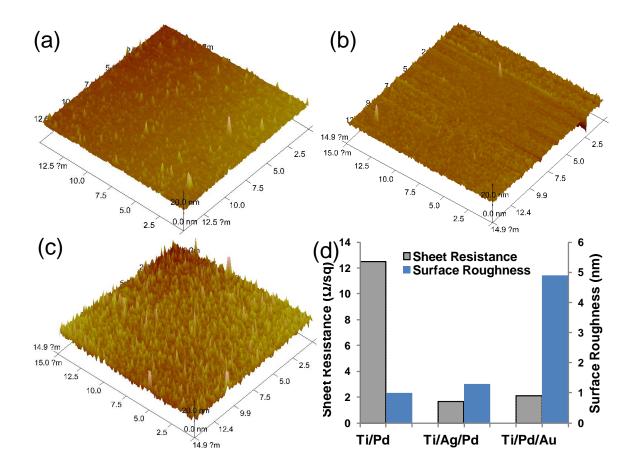

| Figure 4.2. | Comparison of gate electrodes. (a) AFM image of Ti/Pd (2nm/80nm).                                   |

|-------------|-----------------------------------------------------------------------------------------------------|

|             | (b) AFM image of Ti/Ag/Pd (2nm/70nm/10nm). (c) AFM image of                                         |

|             | Ti/Pd/Au (2nm/10nm/70nm). All images are scanned over $15\mu$ m x $15\mu$ m.                        |

|             | (d) Comparison of sheet resistances and surface roughness values for                                |

|             | three candidates                                                                                    |

| Figure 4.3. | The embedded gate structures. (a) Direct deposition of gate electrodes                              |

|             | on the substrate. (b) Gate electrodes embedded in dielectric trench                                 |

|             | structures. (c) Simplified process steps to prepare the self-aligned gate-                          |

|             | electrodes embedded in the dielectric trench                                                        |

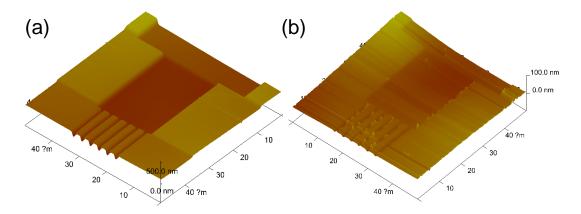

| Figure 4.4. | The trench refilling process. (a) AFM image of the patterned trenches                               |

|             | showing the area for the 6-finger gate electrodes and the pad. (b) AFM                              |

|             | image of the same area after refilling metals using the electron-beam                               |

|             | evaporation of Ti/Ag/Pd                                                                             |

| Figure 4.5. | Thermal effects on GFETs under high lateral electric fields. (a) SEM                                |

|             | image of the GFET before applying high electric fields. The device has a                            |

|             | multi-finger electrodes configuration and the graphene channel is                                   |

|             | located at the center of the image. (b) SEM image of the same device                                |

|             | (damaged) after applying high electric fields                                                       |

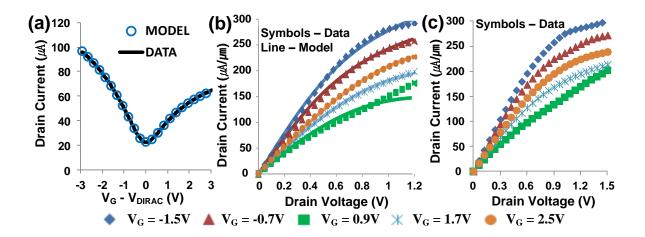

| Figure 5.1. | DC measurement of hBN-EGFET. (a) $I_D\text{-}V_G$ profile measured at $V_D$ of                      |

|             | $10\text{mV}$ . (b) $I_D$ - $V_D$ profile showing the current saturation. (c) $I_D$ - $V_D$ profile |

|             | at V <sub>D</sub> up to high-field of 1.5V41                                                        |

| Figure 5.2. | 2. Electrical measurements. (a) Gate modulation from the lithography-free            |  |  |  |

|-------------|--------------------------------------------------------------------------------------|--|--|--|

|             | GFET with the carrier mobility of 6600 cm <sup>2</sup> /V·s for hole transport and   |  |  |  |

|             | 8000 cm <sup>2</sup> /V·s for electron transport. (b) Gate modulation of the EBL     |  |  |  |

|             | GFET showing the carrier mobility of 2800 cm <sup>2</sup> /V·s for hole transport    |  |  |  |

|             | and 3900 cm <sup>2</sup> /V·s for electron transport, respectively. The device has a |  |  |  |

|             | channel length of $0.5\mu\text{m}$ , and effective width of $100\mu\text{m}$         |  |  |  |

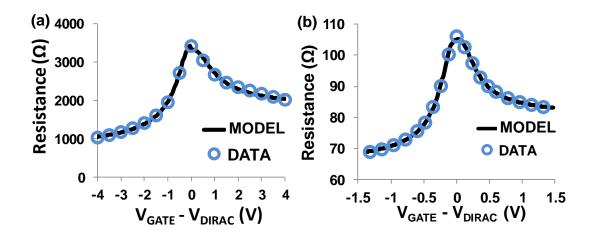

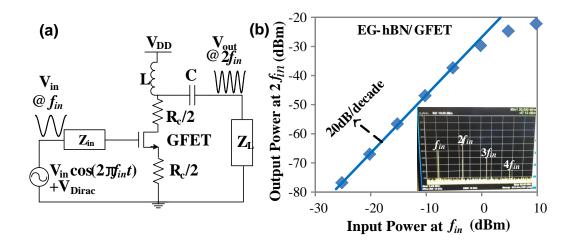

| Figure 5.3. | Experimental GFET frequency doubler circuit on flexible PI. (a)                      |  |  |  |

|             | Schematic for doubler evaluation. (b) GFET output-input doubler                      |  |  |  |

|             | characteristics (f <sub>IN</sub> =10MHz, V <sub>D</sub> =0.5V)44                     |  |  |  |

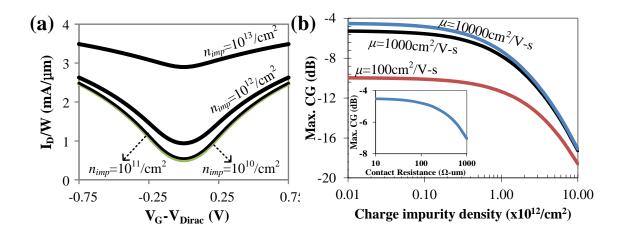

| Figure 5.4. | Simulated ultimate performance prediction of GFET frequency doubler                  |  |  |  |

|             | with ultra-scaled gate dielectric. (monolayer h-BN, L=0.2 $\mu$ m and                |  |  |  |

|             | W=100 $\mu$ m. $\mu$ =10,000cm <sup>2</sup> /V-s) (a) Detrimental impact of charge   |  |  |  |

|             | impurity density on gate modulation. (b) The dependence of the max CG                |  |  |  |

|             | on device parameters. The inset is the dependence on contact resistance.             |  |  |  |

|             | 45                                                                                   |  |  |  |

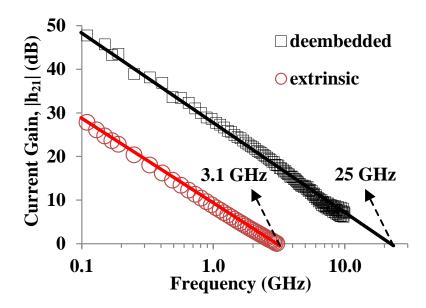

| Figure 5.5. | The extrinsic and intrinsic cut-off frequency measured from the device.              |  |  |  |

|             | The de-embedded current gain reveals an intrinsic $f_T$ of 25 GHz for                |  |  |  |

|             | flexible GFET                                                                        |  |  |  |

| Figure 5.6. | The power-gain frequency measured from the device                                    |  |  |  |

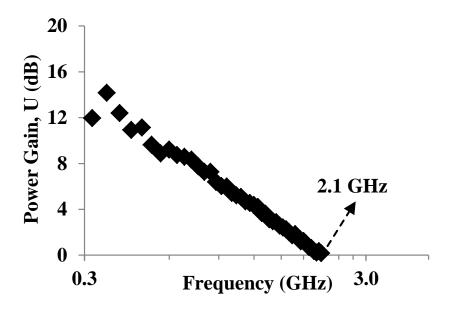

| Figure 5.7. | Channel-length scaling of GFETs. (a) Intrinsic cut-off frequency                     |  |  |  |

|             | measured from the $0.5\mu\text{m}$ channel-length device. $V_{DS} = 0.6 V_{.}$ (b)   |  |  |  |

|             | Intrinsic cut-off frequency measured from the 0.25 $\mu$ m channel-length            |  |  |  |

|             | device. $V_{DS} = 0.3V$                                                              |  |  |  |

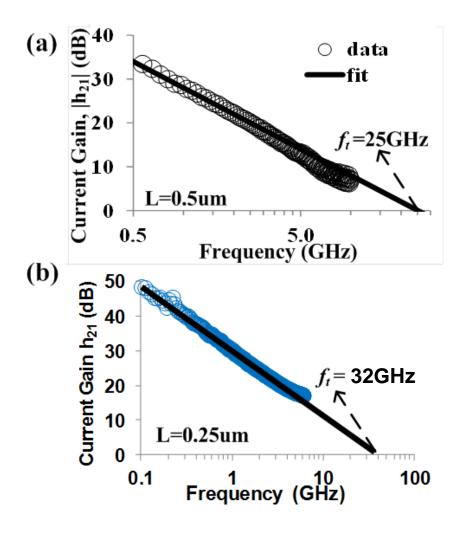

| Figure 5.8.  | Mechanical bending experiments for metal interconnects and MIM                                                                       |

|--------------|--------------------------------------------------------------------------------------------------------------------------------------|

|              | capacitors on PI films. (a) The change in conductance of metal lines. (b)                                                            |

|              | The change in normalized capacitances of MIM capacitors. CAP1,                                                                       |

|              | CAP2, CAP3, and CAP4 are $10x10\mu m^2$ , $50x50\mu m^2$ , $100x100\mu m^2$ , and                                                    |

|              | 200x200μm <sup>2</sup> , respectively. The dashed line is a visual guide indicating                                                  |

|              | invariant properties over a wide bending radius52                                                                                    |

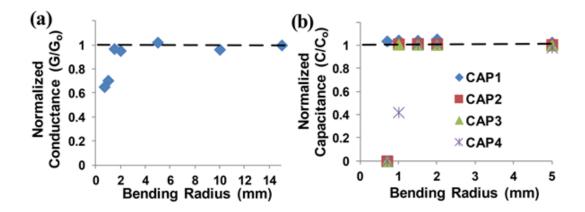

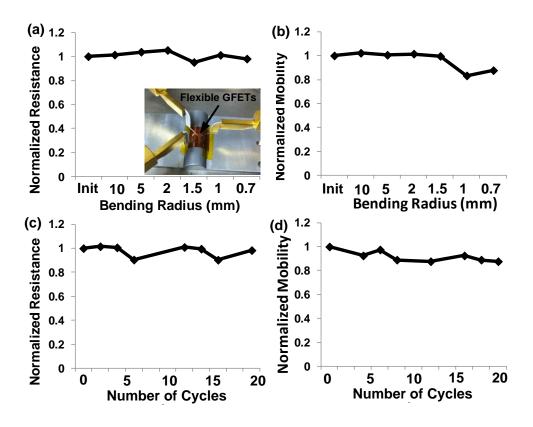

| Figure 5.9.  | Mechanical bending measurements. The change in (a) normalized                                                                        |

|              | resistance and (b) normalized mobility under different bending radii                                                                 |

|              | down to 0.7 mm. The inset in (a) shows the flexible GFETs attached to                                                                |

|              | the bending fixture. Repeated measurements of (c) normalized resistance                                                              |

|              | and (d) normalized mobility at the minimum bending radius of 0.7 mm.                                                                 |

|              | 54                                                                                                                                   |

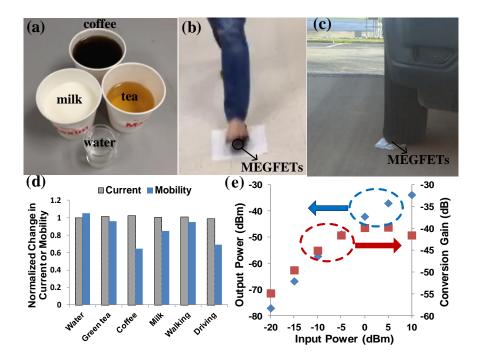

| Figure 5.10. | Experiments involving harsh conditions. (a) Still image of the devices                                                               |

|              | been walked over to emulate a slow-moving load. (b) Still image of                                                                   |

|              | 2002 Honda CRV sport-utility vehicle going over the devices. (c)                                                                     |

|              | Doubler characteristics. The output power at the doubled frequency (2f)                                                              |

|              |                                                                                                                                      |

|              | and the conversion gain as a function of the input power at the                                                                      |

|              | and the conversion gain as a function of the input power at the fundamental frequency (1f=2MHz) are given. The gate is biased at the |

|              |                                                                                                                                      |

| Figure 5.11. | fundamental frequency (1f=2MHz) are given. The gate is biased at the                                                                 |

| Figure 5.11. | fundamental frequency (1f=2MHz) are given. The gate is biased at the Dirac point and $V_D = 300 mV$                                  |

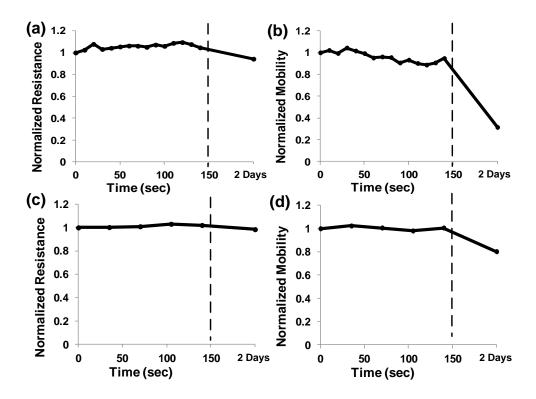

| Figure 5.12. Immersion test results for the normalized resistance and mobility. De |                                                                                      |  |  |  |  |

|------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------|--|--|--|--|

|                                                                                    | shown on the left side of the dashed line are for short-term exposure to             |  |  |  |  |

|                                                                                    | DI water, and data on the right side of the line are for long-term                   |  |  |  |  |

|                                                                                    | exposure to DI water. (a), (b) Normalized resistance and mobility                    |  |  |  |  |

|                                                                                    | measured from $Si_3N_4$ passivated devices. (c), (d) Normalized resistance           |  |  |  |  |

|                                                                                    | and mobility measured from Cytop/Si <sub>3</sub> N <sub>4</sub> passivated devices59 |  |  |  |  |

| Figure A.1.                                                                        | Process steps for embedded-gate GFETs with h-BN films70                              |  |  |  |  |

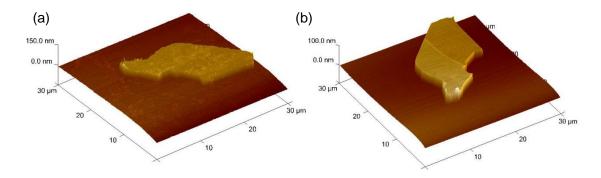

| Figure A.2.                                                                        | Exfoliated h-BN films. (a) AFM image captured as exfoliated, (b) AFM                 |  |  |  |  |

|                                                                                    | image captured after annealing under nitrogen ambient71                              |  |  |  |  |

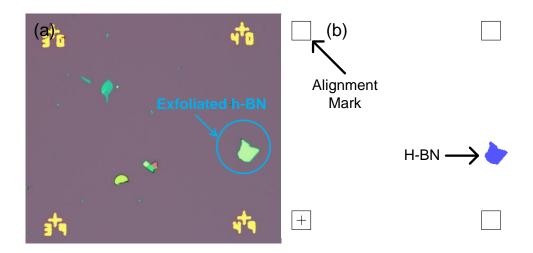

| Figure A.3.                                                                        | Digitizing locations for h-BN films. (a) Optical image of an exfoliated h            |  |  |  |  |

|                                                                                    | BN film, (b) Designed layout. h-BN is drawn as a polygon71                           |  |  |  |  |

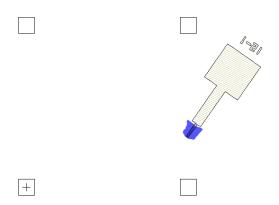

| Figure A.4.                                                                        | Define embedded gate patterns on exfoliated h-BN films72                             |  |  |  |  |

| Figure A.5.                                                                        | Define graphene active layers (a) Designed layout, (b) Zoom-in picture               |  |  |  |  |

|                                                                                    | of the channel area highlighting graphene channel and an h-BN                        |  |  |  |  |

|                                                                                    | dielectric film                                                                      |  |  |  |  |

| Figure A.6.                                                                        | Complete device structure with h-BN dielectric films. (a) Designed                   |  |  |  |  |

|                                                                                    | layout for the entire device structure including source/drain electrodes,            |  |  |  |  |

|                                                                                    | (b) Optical image captured after the liftoff of source/drain (Ti/Au)                 |  |  |  |  |

|                                                                                    | electrodes                                                                           |  |  |  |  |

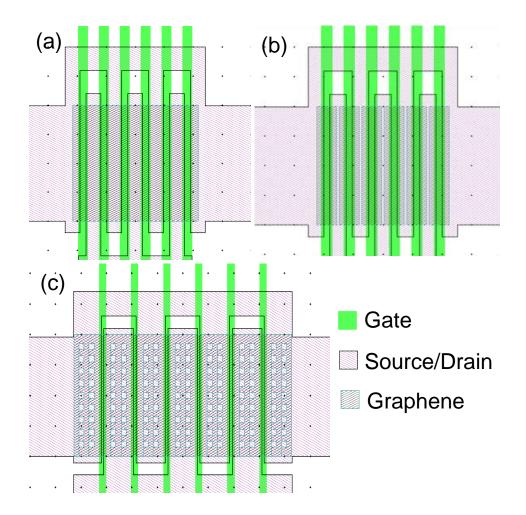

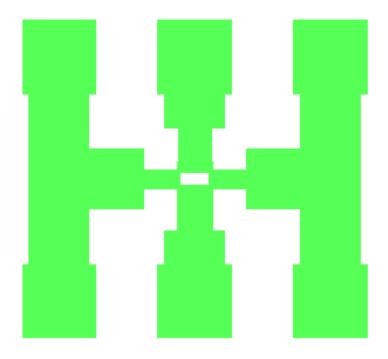

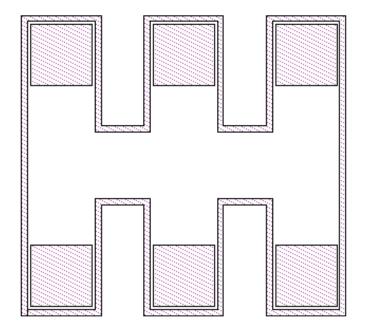

| Figure A.7.                                                                        | Mask1 for Multi-finger Embedded-gate Graphene Field-Effect                           |  |  |  |  |

|                                                                                    | Transistors to define gate fingers                                                   |  |  |  |  |

| Figure A.8.                                                                        | Mask2 for Multi-finger Embedded-gate Graphene Field-Effect                           |  |  |  |  |

|                                                                                    | Transistors to define ALD gate oxides                                                |  |  |  |  |

| Figure A.9.                                                                        | Mask3 for Multi-finger Embedded-gate Graphene Field-Effect                           |  |  |  |  |

|                                                                                    | Transistors to define graphene active areas                                          |  |  |  |  |

| Figure A.10. | (a) Mask4 for Multi-finger Embedded-gate Graphene Field-Effect         |

|--------------|------------------------------------------------------------------------|

|              | Transistors to define source and drain electrodes. (b) Zoom-in picture |

|              | over the channel area highlighted in red in (a).                       |

| Figure A.11. | Mask5 for Multi-finger Embedded-gate Graphene Field-Effect             |

|              | Transistors to define the silicon nitride passivation layer83          |

| Figure A.12. | Combined Layouts for Multi-finger Embedded-gate Graphene Field-        |

|              | Effect Transistors84                                                   |

### **Chapter 1: Introduction**

#### **Graphene Field-Effect Transistor**

The outstanding charge transport in graphene field effect transistors offers attractive prospects for high-speed analog and radio-frequency (RF) electronics. These outstanding features including high mobilities at room temperature, 1,2 sub-THz cutoff frequencies at moderate channel lengths, 3 and ambipolar electron-hole symmetry, afford linear and non-linear analog signal processing with the simplicity of a single transistor. 4,5 In addition, graphene is substrate agnostic and mechanically flexible. Hence, it is an ideal material for flexible electronics on polymeric substrates.

Although intrinsic carrier mobility of graphene approaching 100,000cm<sup>2</sup>/V-s has been reported at room temperature on suspended devices,<sup>6</sup> the carrier mobility of graphene degrades on oxide supported graphene field-effect transistors (GFETs) with values around 10,000cm<sup>2</sup>/V-s frequently measured on clean exfoliated graphene on SiO<sub>2</sub> in agreement with theoretical upper limits.<sup>7-9</sup> However, it is unclear how fast charge carriers can travel in monolayer graphene on polymeric substrates, which is an important substrate for flexible electronics. It has been suggested that remote phonon scattering from the broad continuum of modes from the polymer substrate should impact the carrier mobilities at a scale comparable to SiO<sub>2</sub>. As graphene holds great potential for fast flexible electronics, it is crucial to experimentally access its fast carrier transport on polymer supports.

#### **Flexible Electronics**

The field of flexible electronics has been active for more than a couple of decades, driven by the desire for the realization of low-cost, large-area electronics. The development of flexible electronics operating at radio-frequencies (RF) requires materials that combine excellent electronic performances and the ability to withstand high levels of strain. Circuit components required to implement flexible devices include (1) a supporting flexible film as a substrate, (2) electrically conducting films as electrodes, (3) dielectric films to be used as gate dielectrics and device isolation/passivation layers, and (4) active channel materials. The technical bottleneck in this field of research has been the preparation of high performance active channels due to the process compatibility to flexible substrates. Due to limited carrier mobilities of less than 100cm<sup>2</sup>/V-s for diverse semiconducting materials reported as flexible channels, the resulting electronic device performance has been relatively poor. 11-13 The desire to improve the performance of these devices has led to the introduction of other materials which include carbon nanotubes, 14,15 silicon thin-films and nanowires, 16-18 and compound semiconductors. 19 III-V compound semiconductors and graphene show the highest mobility up to 10,000 cm<sup>2</sup>/V-s on plastics while others show still relatively low values. However, enhancements in electronic performance have been achieved at the expense of device flexibility. In addition to the high carrier mobility and GHz cutoff-frequency, graphene is able to survive the mechanical tensile strain above 20%, 20 and offers a technical method for wafer-scalability. 21-23

#### **Thesis Outline**

This thesis is organized as follows. In chapter 2, the preparation of electronic-grade flexible substrate will be reviewed. We will take a look at candidates for flexible substrates, their material properties, and requirements to be used as supporting films for electronic applications. In chapter 3, transistor device topologies we have investigated are explained and compared with each other. Several approaches in order to optimize the performance of the fabricated devices are covered in chapter 4. The origin of the contact resistance at the graphene-metal interface will be revisited to suggest the modified contact designs for better (lower) contact resistance values. A modified layout/process for low gate resistances and passivation techniques are also covered. In chapter 5, key device data on DC/RF electrical measurements and measurements under harsh environments (mechanical deformation and exposure to common liquids) will be presented. In chapter 6, a summary of this work is presented.

#### **Chapter 2: Preparation of Electronic-Grade Flexible Substrates**

#### **Requirements for Flexible Substrates**

Substrates to be used as a flexible supporting layer replacing the conventional rigid substrates should meet several requirements. Those requirements are listed as follows.

#### 1. Surface quality/roughness

Highly uneven surface topography limiting the fine resolution of lithographic steps has to be avoided. Nanometer-scale short/long range roughness values are desirable to prepare sub-micron channel length devices. Roughness over long distance (or more generally thickness variation) larger than the unit device structure is still acceptable. Chemical-Mechanical-Planarization (CMP) or other surface treatment processes are usually required for commercial flexible substrates to achieve acceptable roughness values.

#### 2. Thermal properties

The maximum processing temperature for the flexible substrates should not exceed their glass transition temperatures (Tg). During the exposure to high temperature processes even with highest temperature less than Tg, the mismatch in thermal expansion coefficients of integrated films and its resulting built-in stress of the sample have to be minimized. Metallic foils and glass substrates are superior in this aspect than polymer substrates.

#### 3. Mechanical properties

Materials with high elastic modulus are less flexible and easier to handle during the fabrication. Highly elastic polymers and elastomers may require hard carrier wafers, where flexible substrates are attached, during the device fabrication.

#### 4. Chemical properties/compatibilities

Substrates should not react with chemicals (acids and solvents) used during device fabrication. Different coating layers may be required to protect the underlying base substrates.

#### 5. Electrical conductivity

Metallic foils are electrically conductive and require additional electrical isolation. Glass substrates and most polymers are good insulators.

#### 6. (Optional) Optical clarity

Not always required, but becoming an important metric for transparent electronics or optoelectronic applications.

#### **Commercially Available Flexible Substrates**

#### 1. Glass substrate

Even though glass plates are considered to be hard and rigid, they become flexible when their film thickness are thinned down to less than 100 µm. <sup>24,25</sup> Glass substrates have high optical transparency and thermal stabilities (low thermal expansion coefficient and high glass transition temperature) suggesting good opportunities for wide-range of electronic applications including flat-panel displays. Mechanical and chemical properties are also attractive. However, they are brittle and cannot tolerate high level of strain, which can be introduced while handling them for fabrication.

#### 2. Metallic foil

Stainless steel is one of the popular metallic foils currently being considered as a flexible substrate. They also become flexible similar to glass substrates when their film thicknesses are thinned down to 100 µm-scale, though their surface qualities are lower than that of glass substrates. He tall foils are not transparent and electrically conductive, however can be still attractive for such applications where reflective surfaces are required. Surface planarization layers are also applied to offer electrical isolation and/or further improve the surface quality. Inorganic materials such as plasmaenhanced chemical vapor deposited (PECVD) silicon nitride and oxide are also used to give the electrical isolation.

#### 3. Polymer substrate

Polymers offer great opportunities to be used as flexible substrates. Diverse candidates are commercially available and a part of them are listed in Table 2.1. These are highly flexible and inexpensive. However, thermal properties are a major concern while utilizing these materials for electronics. Low thermal conductivities along with low glass transition temperatures of polymers limit several processing, 11,30 and operating conditions. 31,32

Dimensional stabilities are also not as great as other candidate substrates listed above. Though high flexibility and low elastic modulus are among desirable features here, when these candidates are exposed to thermal processes repeatedly during device fabrication, the resulting built-in thermal stresses induce non-negligible film curvatures due to mismatch in their thermal expansion coefficients.

Material properties of commonly used flexible substrates are listed in Table  $2.1.^{33-37}$

Table 2.1

Material properties of commercial flexible substrates

|                          |        | Flexible substrates |           |         |          |                  |

|--------------------------|--------|---------------------|-----------|---------|----------|------------------|

| Property                 | Unit   | Glass               | Stainless | Polymer |          |                  |

|                          |        |                     | steel     | PEN     | PET      | PI               |

| Transparency             |        | Good                | N/A       | Good    | Good     | Poor<br>(Orange) |

| Max. process temperature | °C     | 600                 | 900       | 155     | 120      | 300              |

| CTE                      | ppm/°C | 3~4                 | 18        | 20      | 20~80    | 15~35            |

| Elastic modulus          | GPa    | 70                  | 200       | 5       | 2~4      | 2~3              |

| Electrical conductivity  |        | Low                 | High      | Low     | Low      | Low              |

| Thermal conductivity     | W/m°C  | 1                   | 16        | 0.15    | 0.15~0.4 | 0.1~0.35         |

#### Surface Preparation of Polymer Substrates for Device Fabrication

Flexible industrial polyimide sheet (50-100µm thick) was chosen as the substrate because of its high glass transition temperature (>300°C), Young's modulus (~3.5GPa), and high solvent resistance making it compatible with conventional device fabrication. The polyimide sheets used in this study are commercially available from American Durafilm Inc. (#300 FPC) and Dupont Inc. (Kapton film). Industrial polyimide (PI) has an uneven topography with surface roughness that can exceed 100nm. 38 To make the uneven surface of the industrial PI films smooth, liquid polyimide (PI 2574 from HD Microsystems) was spin-coated onto the polyimide sheet. The coated substrate was softbaked at 200°C for 30 min and subsequently cured at 300°C for 1 hour under a nitrogen atmosphere to obtain a smooth surface (RMS ~1-2nm), <sup>38</sup> necessary for preserving the quality of electronic materials and for achieving the best results in lithographic resolution and registration. This coated polyimide sheet was then carefully mounted onto a supporting Si carrier wafer to ensure the flatness for the following fabrication process. Prior to use, the polyimide sheet was rinsed again in Acetone and 2-propanol (IPA) for 5 min each. The surface roughness of the polyimide surface before and after coating was measured using a VeecoVR D-5000 atomic force microscope (AFM) in tapping mode. Figure 2.1 shows the AFM images of polyimide surfaces scanned over the as-received commercial PI film and the PI film after the surface treatment.

To further improve the surface roughness, additional step of depositing high-k atomic layer deposition (ALD) dielectrics is done to improve the surface. This ALD dielectric layer can work as i) the high quality gate dielectric for embedded-gate device structures, and ii) the heat spread layer, which is an important component for the thermal management on flexible substrates, which will be discussed in a later chapter.

Figure 2.1. AFM images of polyimide surfaces. (a)  $50x50~\mu\text{m}^2$ , (b)  $5x2.5~\mu\text{m}^2$  scan on polyimide sheet as received and (c)  $50x50~\mu\text{m}^2$ , (d)  $5x2.5~\mu\text{m}^2$  scan after surface treatment.

Despite the attractive features of graphene, diverse charge scattering mechanisms prevent access to the intrinsic electrical performance. These challenges include ionized impurity scattering which degrades the mean-free-path, <sup>39,40</sup> substrate and interface charge traps resulting in charge puddles, and random shifting of the charge-neutrality point. <sup>8,41</sup> Each of the mechanical and chemical non-idealities can result in deviation of the band structure and transport characteristics, emphasizing the need for a high purity, ultra-

smooth dielectric that is compatible with graphene devices. Hexagonal boron nitride (h-BN) is an insulating isomorph of graphene with boron and nitrogen arranged in a hexagonal lattice, with a small lattice mismatch of ~1.8% compared to graphene. <sup>42</sup> Several features of h-BN make it an excellent candidate dielectric for GFETs on flexible substrates. The ultra-flat surface of h-BN significantly reduces the electron–hole charge fluctuations, compared to polymeric interfaces or SiO<sub>2</sub>. This enables the observation of near-ideal graphene properties without the use of complex suspended structures. <sup>42</sup> Owing to its strong in-plane covalent bonds and relatively weak inter-plane bonds due van der Waals interactions, h-BN is cleaved and exfoliated in the same way as graphene. <sup>42,43</sup> Recently a series of reports have suggested that graphene/h-BN heterostructures enhance field-effect performance. <sup>42–44</sup>

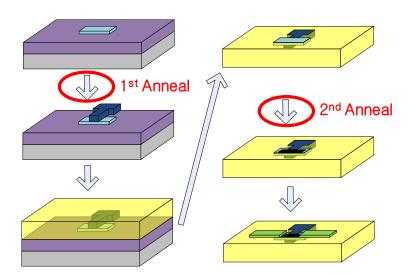

Here, we report the method of utilizing an h-BN film as a gate dielectric for flexible FETs. The preparation of the substrate is as follows. h-BN (from Momentive Performance Materials) was exfoliated on silicon wafers with 285-nm thick thermal oxide, which offers good optical contrast between thin h-BN films and substrates for easy identification. The sample was first annealed under nitrogen at 300°C for 1 hour to achieve a smooth h-BN surface and remove residual adhesive on its surface to define a better interface between gate electrodes and h-BN films. Gate electrodes can be also patterned over annealed h-BN films on SiO<sub>2</sub>/Si substrates by electron-beam lithography (EBL), e-beam evaporation, and liftoff to prepare the embedded-gate structures. Liquid-type PI (PI-2574 from HD Microsystems) was spin-coated on the patterned sample and cured under nitrogen to capture the device structures within PI. Thermal oxide was then etched by buffered-oxide-etchant (BOE) and the PI films with embedded gates and dielectrics were released (capture-release process). The released sample was then

annealed again under nitrogen to provide a clean high-quality interface between graphene and dielectrics (two-step annealing process). Figure 2.2 shows the comparison between different substrate preparation techniques.

Figure 2.2. 3-D illustrations of different flexible substrates preparation techniques. (a) The surface treatments on flexible PI films. An as-received PI film, a cured liquid PI coated on a PI film, and an ALD deposited on a cured film are shown with their AFM images and roughness values. (b) Preparation of an embedded h-BN film captured in a free-standing PI substrate. The simplified process flow is given with the AFM images scanned over an as-exfoliated h-BN film (roughness ~1.2nm) and an annealed h-BN film (roughness ~0.4nm).

### **Chapter 3: Transistor Device Topology**

#### **Top-Gate Graphene Field-Effect Transistors**

The graphene monolayer employed in this study was prepared via low-pressure chemical vapor deposition (CVD) on copper foil as reported previously. <sup>45</sup> A typical Raman spectrum of graphene synthesized with the CVD procedure on copper foil is shown in Figure 3.1a. The full width at half maximum of the 2D peak is approximately 35cm<sup>-1</sup>, the 2D/G ratio is ~3, and the D-peak is negligible, indicating high-quality monolayer graphene. The typical solution-based poly(methyl methacrylate) (PMMA) assisted graphene transfer from the copper foil, <sup>46</sup> was employed to integrate the graphene onto the PI sheet. The AFM image in Figure 3.1b shows the substrate surface after graphene transfer on polyimide sheet with roughness of about 2nm in small areas but with wrinkles as high as 8nm due to the transfer process. These wrinkles from the polymer residue are detrimental to transport and mobility. <sup>47</sup>

An array of graphene transistors were fabricated directly on to the polyimide sheet using standard microelectronic processes and electron-beam lithography with a charge compensation layer essential for patterning insulating substrates. The simplified fabrication process is illustrated in Figure 3.2a. In brief, the first e-beam lithography patterns the active area while isolating graphene channels from each other. Oxygen plasma is used to etch the superfluous graphene. After defining source and drain electrodes by lithography and evaporation, high-k gate dielectric is deposited by ALD. The gate dielectric is composed of evaporated 1nm titanium that oxidizes readily in air at 200°C and serves as the seed layer for uniform ALD of 30nm Al<sub>2</sub>O<sub>3</sub>,<sup>7</sup> with estimated capacitance of ~200nF/cm<sup>2</sup> (k~6.8). The gate electrode is subsequently patterned. The gate and source/drain metals are Ni (50nm) and Ni/Au (10nm/40nm) respectively. An

optical image of a completed device with ground-signal-ground (GSG) input (GFET gate) and output (GFET drain) pads necessary for RF measurements is shown in Figure 3.2b. Figure 3.2c is a photograph of the flexible polyimide substrate with an array of integrated GFETs.

Figure 3.1. Monolayer graphene on copper foil (a) Raman spectrum of the synthesized monolayer graphene on copper foil indicating the 2D and G peaks. (b) AFM image of graphene transferred to flexible polyimide sheet with a surface roughness ~2nm and wrinkles as high as 8nm.

Figure 3.2. Top-gate graphene transistor on polyimide sheet (a) Simplified cross-sectional fabrication process for graphene transistor on polyimide sheet featuring transferred CVD graphene, high-k Al<sub>2</sub>0<sub>3</sub> dielectric, and metal electrodes. (b) Optical image of a completed GFET with two gate fingers in a GSG configuration to facilitate high-frequency measurements. The device length and total width are 0.25μm and 10μm respectively. (c) Photograph of the flexible substrate with an array of integrated GFETs.

#### **Embedded-Gate Graphene Field-Effect Transistors**

Two types of embedded-gate graphene field-effect transistors (EGFETs) have been realized in this work. The first one is a detachable EGFET. The fabrication process for the detachable EGFET is illustrated in Figure 3.3a. 48 Liquid polyimide (PI-2574 from HD Microsystems) was spin-coated on a 50-nm thick plasma-enhanced chemical vapor deposited Si<sub>3</sub>N<sub>4</sub> sacrificial layer on silicon. The 15µm-thick spin-coated polyimide (PI) affords a smooth surface with root-mean-square (RMS) roughness of <1nm. The PI coated film is soft-baked at 200°C for 30 min and subsequently cured at 300°C for 1 hr under a nitrogen atmosphere. An array of gate electrodes were patterned on a PI-coated silicon substrate by electron-beam lithography, evaporation, and liftoff. A high-k dielectric of 20-nm thick Al<sub>2</sub>O<sub>3</sub> is deposited by ALD. A CVD grown graphene film from a Cu/SiO<sub>2</sub>/Si growth substrate was then transferred via a conventional wet-transfer process using ammonia persulfate to etch the copper. 46 Oxygen plasma reactive-ionetching (RIE) was used to pattern the active channel region while removing the superfluous graphene and ensuring channel isolation. Source and drain electrodes were defined to complete the device fabrication. The gate and source/drain metals are Ni/Au (10nm/40nm) and Ni (50nm) respectively. Lastly, buffered oxide etchant (BOE 6:1) was used to strip the Si<sub>3</sub>N<sub>4</sub> sacrificial layer and release the flexible polyimide film from the underlying silicon substrate.

The second type of EGFET is using a cured PI film as the supporting flexible substrate. The 3D image of the fabricated 10-finger multi-finger EGFET unit-cell is illustrated in Figure 3.4a. In brief, an array of gate electrodes were patterned directly on PI by electron-beam lithography (EBL), evaporation, and lift-off. A high-k dielectric of 15-nm thick  $Al_2O_3$  was deposited by ALD with estimated gate-oxide capacitance of

405nF/cm². Another EBL followed by wet-etching of Al<sub>2</sub>O<sub>3</sub> by a 1:3 diluted solution of H<sub>3</sub>PO<sub>4</sub>:DI water isolated each device while leaving local dielectric islands for the channel. High quality CVD monolayer graphene film was then transferred via the conventional poly(methyl methacrylate) (PMMA) wet-transfer process using ammonia persulfate to etch the supporting copper foil. <sup>45,46</sup> The active channel area of graphene was then patterned, and source and drain electrodes were defined to complete the device structure. The top of the sample was then covered with a 30-nm thick plasma-enhanced chemical vapor deposited (PECVD) Si<sub>3</sub>N<sub>4</sub> layer to protect the multi-finger EGFETs from the outside environment. The channel length and width for each finger were fixed at 0.5μm and 20μm, respectively. Devices with both 10-finger and 18-finger configurations were prepared resulting in effective channel widths of 200μm and 360μm, respectively, on the same PI substrate. The optical image given in Figure 3.4b shows the freestanding PI with an array of flexible MEGFETs bent with fingers. The inset shows a 3×3 array of the unit cells. Figure 3.4c is a high-resolution image of the active channel area obtained with an atomic force microscope (AFM) revealing a 10-finger electrode configuration.

#### **Modified Embedded-Gate Graphene Field-Effect Transistors**

The fabrication process for the modified EGFET is as follows. h-BN (from Momentive Performance Materials) was exfoliated on silicon wafers with 285-nm thick thermal oxide; the thickness of the h-BN flake was confirmed with AFM to be 19nm. The sample was first annealed under nitrogen at 300°C for 1 hour to achieve a smooth h-BN surface and remove residual adhesive on its surface to define a better interface between gate electrodes and h-BN films. The simplified process flow is given in Figure 3.5a. In brief, gate electrodes were patterned over annealed h-BN films on SiO<sub>2</sub>/Si substrates by

Figure 3.3. Embedded-gate graphene FET (a) Illustration of the EGFET fabrication process on spin-coated PI on a Si<sub>3</sub>N<sub>4</sub>/Si substrate. (b) Optical image of a completed EGFET. The device length and width are 4 and 8 μm respectively. (c) Photograph of the flexible substrate with an array of EGFETs. The highlighted square shows the array of devices.

EBL, evaporation, and liftoff. Liquid-type PI (PI-2574 from HD Microsystems) was spin-coated on the patterned sample and cured under nitrogen to capture the device structures within PI. Thermal oxide was then etched by buffered-oxide-etchant (BOE) and the PI films with embedded gates and dielectrics were released (capture-release process). The released sample was then annealed again under nitrogen to provide a clean high-quality interface between graphene and dielectrics (two-step annealing process). Monolayer graphene film grown by chemical vapor deposition (CVD) process was transferred via the poly(methyl methacrylate) (PMMA) assisted wet-transfer process using ammonia

Figure 3.4. Multi-finger EGFET fabricated on plastic substrates. (a) 3-D image of the complete device of a 10-finger unit cell. (b) Optical image of the sample. The device area is highlighted by a white rectangle. Inset shows an array of the unit cells with gate (G), source (S), and drain (D) pads. (c) AFM image of the active channel area revealing a device with 10-fingers.

persulfate as a copper etchant.<sup>46</sup> Redundant area of graphene film was removed by oxygen plasma etching. Finally, source and drain electrodes were defined to complete the device structure (Figure 3.5b).

A high-resolution image over the active channel area and an optical image of the free-standing PI substrate with the device are shown in Figure 3.5c and 3.5d, respectively. Figure 3.5e shows an AFM topographical scan of the h-BN film after anneal and Figure 3.5f compares the surface roughness of several gate dielectrics for GFETs on plastics. Previous works in our lab were focused on improving the surface quality of plastics by applying additional liquid-type layer and/or depositing high-k dielectrics over flexible films. The surface roughness has been remarkably improved down to 1~2nm

using these methods,<sup>48</sup> however, its roughness is still higher than monolayer graphene, which can introduce mechanical strain and result in band structure deviation and transport degradation.<sup>49,50</sup>

## **Comparison of Device Structures**

Three device structures, namely, top-gate GFET (TG-GFET), embedded-gate GFET with high-k dielectric (EG-highk/GFET), and embedded-gate GFET with h-BN dielectric (EG-hBN/GFET), which is the modified version of the previous EGFET to integrate h-BN into PI films, were fabricated on PI and evaluated in this work. Due to uneven surface topography of polymeric films, additional treatments are necessary to achieve the best lithographic resolution and registration.<sup>38</sup> In brief, PI films were spincoated with liquid polyimide (PI2574 from HD Microsystems) and cured. TG-GFETs were prepared directly on these substrates, while others require more processing steps before graphene-transfer; ALD Al<sub>2</sub>O<sub>3</sub> or exfoliated h-BN films were prepared as gate dielectrics. Optimized annealing was performed at 300°C to improve the surface smoothness of h-BN films under nitrogen ambient. Figure 3.5f compares the roughness of the surfaces evaluated in this work. While the surface of as-exfoliated h-BN film is comparable to that of high-k on PIs, it is further improved by annealing as shown in the figure. After annealing, h-BN flakes on PI show the root mean square (RMS) roughness ~0.4nm, comparable to the inter-layer spacing and indicative of an almost perfect residue-free interface.

Table 3.1 compares the merits of the three device structures, investigated in this work. TG-GFET has an issue with the need for insulating seed layer prior to deposit

Figure 3.5. Illustration and images of fabricated EG-hBN GFET. (a) Simplified process flow. (b) Illustration of a fabricated device. (c) Optical image of the channel area with a dual-finger embedded-gate GFET. (d) GFETs on a PI film. (e) Surface of the smooth h-BN on flexible PI as measured by AFM. (f) Comparison of different surface roughnesses for graphene integration on flexible PI. The annealed h-BN surface features smoothness comparable to interlayer spacing in graphene.

ultra-thin high-quality dielectric over channel, which makes it difficult to scale down the oxide thickness. For embedded gate devices, oxide scaling is not a critical issue. While h-BN offers the best interface for GFET, substantial research has to be done to synthesize large-area uniform (monolayer to few layer) h-BN films. This leads to the conclusion that

while embedded-gates with h-BN dielectric is ideal, EG-highk/GFET is the best practical device structure for now because further synthesis progress is needed for the integration of h-BN/graphene layers.

Table 3.1

Comparison of 3 flexible GFET device structures

| Device structure Device process      | TG-GFET | EG-hBN/<br>GFET | EG-highk/<br>GFET | Comments                                                                                                    |

|--------------------------------------|---------|-----------------|-------------------|-------------------------------------------------------------------------------------------------------------|

| Finger scalability in a single layer | No      | Yes             | Yes               | Realizing large # of fingers is straight - forward without the need for 2 <sup>nd</sup> interconnect level. |

| Gate dielectric seed layer           | Needed  | None            | None              | Seed layer is needed for<br>even coating of high-k on<br>graphene. Not needed for<br>embedded-gate.         |

| Gate dielectric scalability          | No      | Yes             | Yes               | For top-gate devices, seed layer prevents ultra-thin dielectrics (<5nm).                                    |

| Automated gate dielectric process    | Yes     | No              | Yes               | Currently, growth and transfer of uniform large-area sheets of h-BN is not available.                       |

| Expected GFET performance            | Good    | Excellent       | Very<br>good      | h-BN gate dielectric is<br>expected to yield the best<br>GFET performance                                   |

# **Chapter 4: Design Considerations for Optimization**

The two most important metrics to quantify the high frequency response of the RF device are the transit frequency, f<sub>T</sub>, and the maximum oscillation frequency, f<sub>MAX</sub>. These are highly dependent on intrinsic and extrinsic device parameters. In order to achieve the highest RF performance, we need to take a look at which parameters affect the metrics. The following equations ((1) - (3)) are for (1) the intrinsic transit frequency, (2) the extrinsic transit frequency, and (3) the maximum oscillation frequency.<sup>51</sup>

$$f_{T,int} = \frac{g_m}{2\pi C_{as}} \tag{1}$$

$$f_{T,ext} = \frac{g_m}{2\pi (c_{qs} + c_{p,qs} + c_{p,qd})((R_{p,s} + R_{p,d})g_d + 1) + c_{p,qd}g_m(R_{p,s} + R_{p,d})} \dots (2)$$

$$f_{T,int} = \frac{g_m}{2\pi c_{gs}}$$

(1)

$$f_{T,ext} = \frac{g_m}{2\pi (c_{gs} + c_{p,gs} + c_{p,gd}) ((R_{p,s} + R_{p,d})g_d + 1) + c_{p,gd}g_m(R_{p,s} + R_{p,d})}$$

(2)

$$f_{MAX} = \frac{f_T}{\sqrt{2g_d(R_{p,s} + R_{gate}) + 2\pi f_T c_{p,gd}R_{gate}}}$$

(3)

where  $g_m$  is the transconductance,  $g_d$  is the drain-conductance,  $C_{gs}$  is the gate capacitance,  $C_{p,gd}$  and  $C_{p,gs}$  are the parasitic gate-to-drain and gate-to-source capacitances,  $R_{p,s}$  and  $R_{p,d}$  are the parasitic resistances at the source and drain electrodes, and  $R_{\text{gate}}$  is the gate resistance.

The reduction in the channel length is the most straightforward way to improve the intrinsic  $f_T$  since the intrinsic  $f_T$  scales proportional to  $\frac{1}{L}$ . The extrinsic  $f_T$  can be dominated by the device parasitics. Currently, the source/drain electrodes for our devices show much higher resistances than the values frequently obtained from other reports on GFETs; the contact resistances from our devices range from 1k  $\Omega \cdot \mu m$  to 5k  $\Omega \cdot \mu m$ , while other reports show mostly less than 1k  $\Omega \cdot \mu m$  or even less than 100  $\Omega \cdot \mu m$ . This requires more investigations on the interface between graphene and metal electrodes and proper designs to reduce the contact resistance.

The power gain,  $f_{MAX}$ , is also the important metric for RF devices. The improvements on  $f_{MAX}$  can be achieved by (1) reduction in parasitics by better layouts or fabrication, and (2) reduction in the gate resistance.

#### **Contact Resistance**

The contact resistance of graphene transistors consists of the following components: the metal electrode interconnection, the un-gated graphene resistance, and the resistance at the metal-graphene interface. By utilizing the highly conductive metals like gold as the electrodes, the first term can be improved, while the second term can be neglected with the proposed gate-overlap device structure. This makes the last term, the resistance at the metal-graphene interface, becomes the most critical component determining the overall contact resistance of the fabricated device. The low quality interface, leading to the high contact resistance, is the fundamental limiting factor on the electrical performance of graphene devices. It can degrade the transconductance and the cutoff frequency of GFETs by more than an order of magnitude.<sup>53</sup>

Previously, the fundamental charge transport physics on the graphene metal contacts and interface quality were investigated to provide better understanding on the graphene-metal contact resistance. 47,54-57

The chemical residues can be introduced onto graphene films during the transfer of graphene films from Cu foils to desired substrates for fabrication. PMMA used during this transfer process can reside on the graphene surface and it is difficult to be completely removed from the surface by acetone during the cleaning process. The detrimental effects from these residues on graphene devices result in poor electrical performances with low field-effect mobilities. High vacuum annealing (1 x 10<sup>-9</sup> mbar) at 300°C for 3 hours has

been suggested to remove them.<sup>47</sup> However, annealing samples at 300°C for extended time is not feasible for flexible substrates which are not thermally stable. Another approach suggested using an Al sacrificial layer prior to lithographic steps defining contact patterns.<sup>54</sup> In this case, the effect from the chemical residue can be minimized since the chemical is not touching the graphene surface at any time during the entire lithographic procedures, which results in up to 10X improvement in a contact resistance.

The selection of contact metals also plays a role determining the electrical performances of graphene FETs. A theoretical study using density functional theory suggested that the doping of graphene can be induced by adsorption on metal films and the cross-over of doping from p-type to n-type can be also expected by utilizing different metals (more importantly utilizing their work-functions).<sup>55</sup> Another experimental study also showed the p-n junction formation at the interface of graphene/metal can be induced by utilizing different metals; high work-function metals afford a more transparent interface (p-type to p-type) for hole transport in contrast to electron transport that involves a p-n junction interface with an additional contribution to the contact resistance.<sup>58</sup> This effect can lead to the asymmetry in the contact resistance between electron and hole transports.<sup>48,59</sup>

Recently, another publication suggested an interesting idea to further reduce those values. In order to improve the carrier injection at the metal-graphene interface, the contact regions of graphene devices are patterned into multiple cuts. <sup>60</sup> By simply modifying the design under the contact areas, two carrier injecting mechanisms, "edge-contacted" injection and "top-contacted" injection, contribute to lower the contact resistance values by 22~32% compared to those values without patterns. <sup>60</sup>

In our work, the contact resistances coming from source and drain metal electrodes interfacing with the graphene channel offers a great portion of the total resistance, limiting its extrinsic electrical performance. In order to access the complete usefulness of the fascinating properties of graphene, we introduced the patterned contacts to improve the carrier injection at the interface between metal contacts and the graphene channel.

The total contact resistance is the parallel combination of the interface resistance at the metal-graphene interface by the top-contacted injection,  $R_{\text{Top}}$ , and the resistance coming from the edge-injection effects,  $R_{\text{Edge}}$ .

$$R_{Total} = R_{Top} // R_{Edge}$$

.....(4)

The equation given above can be also expressed in terms of the conductance for analysis.

$$G_{Total} = G_{Top\ Total} + G_{Edge\ Total} \dots (5)$$

$$G_{Total} = \sigma_{Top/width} \cdot W_{Channel} + \sigma_{Edge/width} \cdot W_{Edge}$$

.....(6)

where  $G_{Total}$  is the total conductance through the contacts,  $G_{Top\_Total}$  is the contribution through the metal-graphene interface, and  $G_{Edge\_Total}$  is for the contribution from the edge charge injection. Again, the equation can be further expanded considering the channel width,  $W_{Channel}$ , and the electrode width for the edge injection,  $W_{Edge}$ , and the per-width partial conductances from the top-contacted injection and the edge-contacted injection effects.

In the experiment, we fabricated devices with different contact patterns as given in Figure 4.1. Figure 4.1a is the conventional contact layout without edge-injection patterns. The device has a multi-finger (6 fingers) configuration with narrow metal

electrodes for minimum edge-injection effect. Figure 4.1b is the proposed contact layout with line-type edge-injection patterns and Figure 4.1c is another proposed contact layout with array-type edge-injection patterns.

The contributions from the top-injection at the metal-graphene interface and the edge-injection can be extracted from electrical measurements. Firstly, the devices are measured to extract the contact resistance values for each patterned structure. Then, a simple matrix calculation can be used to extract the individual contributions as follows.  $R_{Total}$  is extracted directly from the electrical measurements, while other parameters of  $W_{Channel}$  and  $W_{Edge}$  are from the physical layouts.

$$G_{Total} = \frac{1}{R_{Total}} \tag{7}$$

$$\begin{pmatrix} W_{Channel\_1} & W_{Edge\_1} \\ W_{Channel\_2} & W_{Edge\_2} \end{pmatrix} \cdot \begin{pmatrix} \sigma_{Top/width} \\ \sigma_{Edge/width} \end{pmatrix} = \begin{pmatrix} G_{Total_1} \\ G_{Total_2} \end{pmatrix} \dots (8)$$

$$\begin{pmatrix} \sigma_{Top/width} \\ \sigma_{Edge/width} \end{pmatrix} = \begin{pmatrix} W_{Channel\_1} & W_{Edge\_1} \\ W_{Channel\_2} & W_{Edge\_2} \end{pmatrix}^{-1} \cdot \begin{pmatrix} G_{Total_1} \\ G_{Total_2} \end{pmatrix} ....$$

(9)

From the electrical measurements, the total contact resistances are extracted as follows.

$$R_{\text{Total},\text{Type-I}} = 93.03 \,\Omega$$

$$R_{Total,Type-II} = 53.67 \Omega$$

$$R_{Total,Type-III} = 40.28 \Omega$$

After calculating the partial contributions, the resistances from each component are also extracted.

$$\begin{split} R_{Top} &= \frac{1}{\sigma_{Top/width} \cdot W_{Channel}} = 108 \, \Omega \\ R_{Edge,Type-III} &= \frac{1}{\sigma_{Edge,Type-II/width} \cdot W_{Edge}} = 114 \, \Omega \\ R_{Edge,Type-III} &= \frac{1}{\sigma_{Edge,Type-III/width} \cdot W_{Edge}} = 63.9 \, \Omega \end{split}$$

The patterned contacts, Type-II and Type-III, offered lower contact resistances compared to the conventional one, Type-I. The data confirm the array-type (Type-III) patterned contacts offer the effective reduction in the total contact resistance while providing an additional 25% reduction in the contact resistance compared to the line-type (Type-II) patterned contacts.

Figure 4.1. Contact electrodes patterns. (a) Type-I. Conventional contacts without edge-injection patterns. (b) Type-II. Contacts with line-type edge-injection patterns. (c) Type-III. Contacts with array-type edge-injection patterns.

#### **Embedded-Gate Electrodes**

Since the power gain, f<sub>MAX</sub>, strongly depends on the gate resistance, we investigated different options for preparing the embedded-gate electrodes. While selecting the materials, several things to be considered in this process are i) surface oxidation of the metal, which leads to higher resistance over time, ii) high electrical conductivity for lower resistance, iii) structure of the embedded-gates in order to minimize the device parasitics, and iv) surface roughness over the metal film. The last requirement is crucial since the graphene devices are currently prepared on top of the gate metals covered with dielectric films to have an embedded-gate structure to access high electrical performance as mentioned in the previous chapter.

In this work, we compared Ti/Pd (2nm/80nm), Ti/Ag/Pd (2nm/70nm/10nm), Ti/Pd/Au (2nm/10nm/70nm) for preparing gate electrodes. The first one stands for the reference device that we routinely utilize to implement graphene field-effect transistors. Palladium offers reasonably low resistance while providing smooth surface where short-channel devices are easily implemented. Silver and Gold are considered in order to further reduce the gate resistances. Since the surface oxidation of Silver is detrimental while that has negligible effects on Gold, we covered the Silver electrodes with an additional Palladium of 10nm to prevent this surface oxidation.

The electrical conductivities of the three candidates are compared via the TLM (transmission line method) measurements to extract their sheet resistance values. The surface roughness values are also compared using an atomic force microscopy scanning over  $15\mu$ m x  $15\mu$ m area for each candidate. Figure 4.2 shows the comparison of these candidates.

Figure 4.2. Comparison of gate electrodes. (a) AFM image of Ti/Pd (2nm/80nm). (b) AFM image of Ti/Ag/Pd (2nm/70nm/10nm). (c) AFM image of Ti/Pd/Au (2nm/10nm/70nm). All images are scanned over 15 µm x 15 µm. (d) Comparison of sheet resistances and surface roughness values for three candidates.

As shown in Figure 4.2d, Ti/Ag/Pd offers the highest electrical conductivity along with a reasonable surface roughness making it as the most fascinating choice among the compared candidates. Ti/Pd offers the best (lowest) surface roughness while providing relatively higher sheet resistance, which may severely limit the power gain performance of the fabricated device. The last option of Ti/Pd/Au also offers a reasonable sheet

resistance, however the un-even surface limits its usefulness as the embedded gate electrodes.

Another way to further improve the electrical conductivity of the gate electrodes is increasing the thickness of the metal stacks. The direct deposition of high metal stacks leads to proportionally lower resistance at the cost of higher parasitic capacitances as shown in Figure 4.3a. The better way to deal with this issue would be introducing the trench structure where the gates electrodes are fully embedded (Figure 4.3b). The extension length of source and drain electrodes over the gate electrodes is 200nm for the prepared device leading to the parasitic overlap capacitance, C<sub>OV,TOP</sub>. With 50nm-thick gate electrodes, the parasitic component of the side-wall overlap capacitance, C<sub>OV,SIDE</sub>, increases the overall parasitic capacitance by additional 25%. Increase in the thickness of this metal stack would also increase this parasitic part leading to the limited extrinsic high frequency performance. In order to avoid this trade-off, we suggest the trench-type gate electrodes as shown in Figure 4.3b to remove the side-wall overlap capacitance while lowering the gate-overlap capacitance and also effectively increasing the cutoff frequency performance of the device. Figure 4.3c shows the simple self-aligned patterning technique to define the dielectric trench and deposit the embedded gates in one lithography step. The electron-beam lithography is used to define the trench patterns and the fluorine-based dry etch etches the nitride trenches where the metal electrodes are refilled via the electron-beam evaporation and the subsequent liftoff process.

Figure 4.3. The embedded gate structures. (a) Direct deposition of gate electrodes on the substrate. (b) Gate electrodes embedded in dielectric trench structures. (c) Simplified process steps to prepare the self-aligned gate-electrodes embedded in the dielectric trench.

The successful patterning of trenches strongly depends on the high-aspect ratio reactive-ion-etching and the high-selectivity between the e-beam resist (PMMA) and the dielectric material used for the trench structures. Here, we used the plasma-enhanced chemical vapor deposited silicon nitride for the dielectric material. This process enables

the deposition of thick dielectric films and its low-temperature process (250°C) is compatible with the flexible substrates.

For the reactive ion etching of nitrides, CF<sub>4</sub> is commonly used, however it also shows a very high etch rate for PMMA. Introducing Ar can significantly improve the etching selectivity while lowering the etch rate for PMMA. We used the 790 Plasma Therm RIE Etcher during this process. The process condition is as follows. 50 sccm of CF<sub>4</sub>, 20 sccm of Ar, RF power of 100W, and the pressure of 80mTorr. Figure 4.4 shows the results. Figure 4.4a is the AFM image of the patterned trenches showing the area for the 6-finger gate electrodes and the pad. Figure 4.4b is another AFM image of the same area after refilling metals using the electron-beam evaporation of Ti/Ag/Pd. The height of the metal stack and the depth of the trench are determined to be the same (80nm) to provide the flat surface where the devices are to be implemented. The etch rate for the nitride and PMMA are 114nm/min and 88nm/min, respectively, offering the good etch selectivity of over 1.29:1. The thickness of the resist layer is 250nm.

Figure 4.4. The trench refilling process. (a) AFM image of the patterned trenches showing the area for the 6-finger gate electrodes and the pad. (b) AFM image of the same area after refilling metals using the electron-beam evaporation of Ti/Ag/Pd.

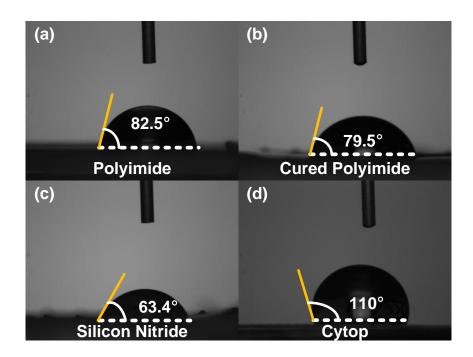

#### **Passivation Techniques for Embedded-Gate Structures**

While the embedded-gate GFETs outperform the conventional top-gate GFETs as described in Table 3.1, the still remaining issue is the passivation of exposed graphene channel. The proper passivation is required for 1) improved hysteresis, 2) preventing degradation during device operation, 3) mechanical robustness, and 4) protection over direct liquid exposures. Several approaches have been reported for GFETs on conventional rigid substrates: bilayer (organic/inorganic) passivation, 61 PECVD silicon nitride directly on graphene, 59,62 and hydrophobic organic polymer spincoated on graphene. 63

Here, we have investigated different options: ALD high-k dielectrics, PECVD Si<sub>3</sub>N<sub>4</sub>, bilayer films of PECVD Si<sub>3</sub>N<sub>4</sub> covered with CYTOP fluoropolymer.

#### **ALD Dielectrics**

The first one we investigated is using ALD dielectrics. ALD films offer high quality dielectric films good for both gate oxides and device passivation layers. Several high-k dielectric materials are available including Al<sub>2</sub>O<sub>3</sub>, HfO<sub>2</sub>, and ZrO<sub>2</sub>. However, this process requires the deposition of an insulating seed layer prior to deposit dielectrics over graphene due to the chemical inertness of graphene surface and not reliable.<sup>64</sup> While preparing this film as the gate dielectric, we can still avoid this issue by adopting the embedded-gate FET structure.<sup>59,65</sup>

#### **PECVD Dielectrics**

PECVD is another option and oxides and nitrides are routinely deposited on substrates as interlayer dielectrics, passivation layers, or gate dielectrics. PECVD oxide is excluded among the feasible candidates for the device passivation since it requires the deposition involving oxygen radicals, which effectively etch the graphene channel leaving pin-holes after the deposition. The conventional PECVD recipe for Si<sub>3</sub>N<sub>4</sub> is also evaluated. However, still the graphene channel has been degraded during plasma process significantly degrading the field-effect mobility of the device after passivation. The modified recipe using low power N<sub>2</sub>-rich PECVD<sup>62,65</sup> could prevent this degradation in its electrical properties and also offers good mechanical robustness. When the nitride-passivated sample is exposed to liquids, the nitride passivation layer fails to protect the underlying FET device and the device experienced significant reduction in quality over time, which will be covered shortly in the later chapter.

#### **Integration of Organic Polymers on Graphene**

Several publications suggest the usefulness of organic polymers introduced on graphene surfaces as promising options to enhance or modify the electrical properties of graphene devices prepared on rigid substrates. 66-68

Self-assembled monolayers (SAMs) are molecular thin films formed via chemical or physical interactions of molecules with a substrate without the utilization of high-temperature or vacuum processes. B. Lee et al reported that they could successfully grow uniform and stable fluoroalkyl silane self-assembled monolayer (FTS SAM) on the graphene surface, which leads to a high level of hole doping effect with a density of up to  $1.5 \times 10^{13} \text{ cm}^{-2.66}$  Even though the field-effect mobility from the graphene device

degraded significantly, this approach highlights the potential of SAM layers for graphene electronics with the capability of modifying the electronic properties of devices.