# MODELING, DESIGN AND DEMONSTRATION OF THROUGHPACKAGE-VIAS IN PANEL-BASED POLYCRYSTALLINE SILICON INTERPOSERS FOR HIGH PERFORMANCE, HIGH RELIABILITY AND LOW COST

A Dissertation Presented to The Academic Faculty

by

Qiao Chen

In Partial Fulfillment

of the Requirements for the Degree

Doctor of Philosophy in the

School of Electrical and Computer Engineering

Georgia Institute of Technology May 2015

COPYRIGHT© 2015 BY QIAO CHEN

# MODELING, DESIGN AND DEMONSTRATION OF THROUGHPACKAGE-VIAS IN PANEL-BASED POLYCRYSTALLINE SILICON INTERPOSERS FOR HIGH PERFORMANCE, HIGH RELIABILITY AND LOW COST

## Approved by:

Dr. Rao R. Tummala, Advisor School of Electrical and Computer Engineering Georgia Institute of Technology

Dr. Ajeet Rohatgi School of Electrical and Computer Engineering Georgia Institute of Technology

Dr. Sung Kyu Lim School of Electrical and Computer Engineering Georgia Institute of Technology Dr. Suresh Sitaraman School of Mechanical Engineering Georgia Institute of Technology

Dr. Venky Sundaram School of Electrical and Computer Engineering Georgia Institute of Technology

Date Approved: April 1st, 2015

### **ACKNOWLEDGEMENTS**

I would like to start by thanking my advisor Prof. Rao R. Tummala for his guidance and support throughout my PhD study. His vision and advice have been a great source for my research and help to shape my dissertation. More importantly, he provided me the opportunity to learn in the world's best packaging research center. I also wish to thank Dr. Venky Sundaram, my mentor, for his constant help and advice through the last few years.

I would like to express my sincere gratitude to my committee members: Dr. Ajeet Rohatgi, Dr. Sung Kyu Lim, and Dr. Suresh Sitaraman for all the valuable feedback and discussions.

My stay in Atlanta has been a joyful experience thanks to my friends: Yuya, Sri, Vijay, Xi, Wei, Christine, Koushik, Dibyajat, Jialing, Yushu, Tapo, Bruce, Brett, Xian, Zihan, Nathan, Hao, Timothy, Saumya, Partha, Kaya, Tailong, Gokul, Min Suk, Scott, Bhupender, Ichiro, Toshi, Sangbeom and Chandra.

I would also like to thank Dr. Raj, Dr. Fuhan, Dr. Himani, Dr. Vanessa and Mr. Sung Jin for their guide, suggestion and help. Also, the help and support from Jason, Chris, Patricia, Karen and Brian are highly appreciated.

Special thanks to the members in Silicon and Glass Interposer Consortium. The great advice from the industry mentors and visiting engineers help build up my knowledge about the industry and spark ideas to address issues in the real life. This is really a good learning experience. I believe such experience will greatly aid my career in the future.

Finally, I would like to thank my grandma, my parents and my wife Yanling for their great support in my life.

# TABLE OF CONTENTS

|                                                                 | Page |

|-----------------------------------------------------------------|------|

| ACKNOWLEDGEMENTS                                                | iv   |

| LIST OF TABLES                                                  | X    |

| LIST OF FIGURES                                                 | xi   |

| SUMMARY                                                         | XV   |

| CHAPTER                                                         |      |

| 1 INTRODUCTION                                                  | 1    |

| 1.1 Evolution of Interposer Technology                          | 2    |

| 1.2 Rational of Polycrystalline Silicon Interposers with TPVs   | 4    |

| 1.3 Research Objectives, Challenges and Tasks                   | 10   |

| 2 LITURATURE SURVEY                                             | 13   |

| 2.1 Prior Art on Silicon Interposers with TSVs                  | 13   |

| 2.1.1 Electrical Modeling and Performance of TSVs               | 13   |

| 2.1.2 Mechanical Modeling and Reliability of TSVs               | 15   |

| 2.1.3 TSV Fabrication in Single-Crystalline Silicon Interposers | 17   |

| 2.2 Prior Art on Polycrystalline Silicon                        | 21   |

| 3 MODELING AND DESIGN OF TPVS                                   | 23   |

| 3.1 Electrical Modeling and Design of TPVs                      | 23   |

| 3.1.1 Electrical Performance Comparison between TPV and TSV     | 26   |

| 3.1.2 Effect of Sidewall Liner Thickness                        | 29   |

| 3.1.3 Design Guidelines for Electrical Consideration            | 30   |

| 3.2 Mechanical Modeling and Design of TPVs                      | 30   |

| 3.2.1 Stress Comparison between TPV and TSV                     | 31   |

|   | 3.2.2 Effect of Sidewall Liner Thickness                                                   | 39         |

|---|--------------------------------------------------------------------------------------------|------------|

|   | 3.2.3 Design Guidelines for Mechanical Consideration                                       | 43         |

|   | 3.3 Summary and Overall Design Guidelines for TPVs                                         | 44         |

| 4 | FORMATION, LINER FABRICATION AND METALLIZATION OF TPV POLYCRYSTALLINE SILICON              | S IN<br>46 |

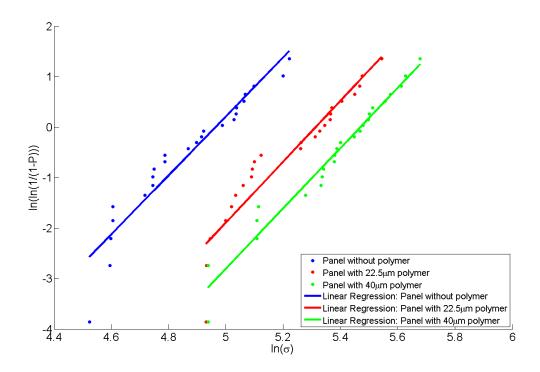

|   | 4.1 Fracture Strength of Thin Polycrystalline Silicon Panels                               | 48         |

|   | 4.2 TPV Formation                                                                          | 57         |

|   | 4.2.1 DRIE-based TSV vs. Laser-drilled TPV                                                 | 57         |

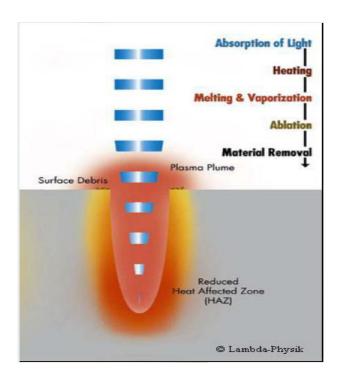

|   | 4.2.2 Theory of Laser Ablation in Silicon                                                  | 61         |

|   | 4.2.3 Picosecond Laser                                                                     | 64         |

|   | 4.2.4 Excimer Laser                                                                        | 66         |

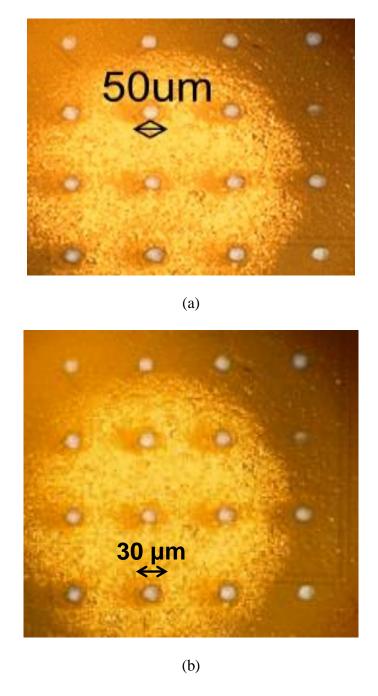

|   | 4.2.5 UV Laser                                                                             | 69         |

|   | 4.3 TPV Liner Fabrication                                                                  | 75         |

|   | 4.3.1 Spray Coating                                                                        | 76         |

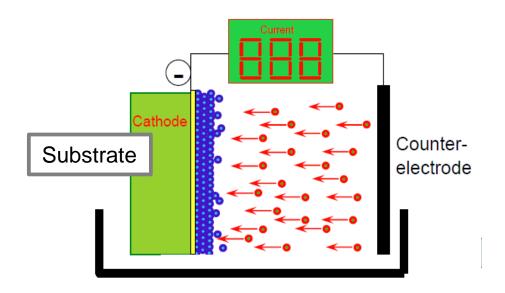

|   | 4.3.2 Electrophoretic Deposition                                                           | 78         |

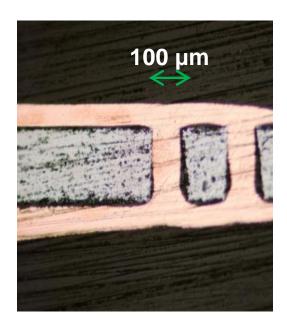

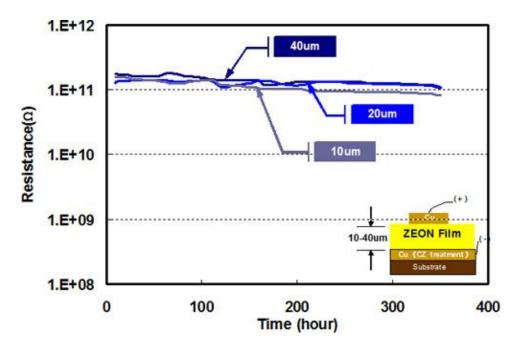

|   | 4.3.3 Double Laser Method                                                                  | 80         |

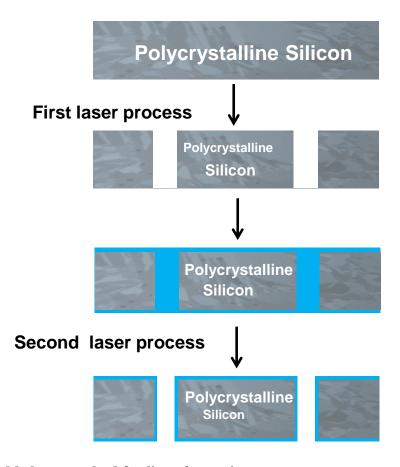

|   | 4.3.3.1 Liner Material Selection                                                           | 82         |

|   | 4.3.3.2 Polymer Filling in TPVs and Surface Liner Formation                                | 84         |

|   | 4.3.3.3 Laser Ablation in Polymer                                                          | 95         |

|   | 4.4 TPV Metallization                                                                      | 96         |

|   | 4.4.1 Cu Electroless Plating                                                               | 96         |

|   | 4.4.2 Cu Electrolytic Plating                                                              | 99         |

|   | 4.5 Summary                                                                                | 101        |

| 5 | ELECTRICAL AND RELIABILITY CHARACTERIZATION OF TPVS IN POLYCRYSTALLINE SILICON INTERPOSERS | 104        |

|   | 5.1 Electrical Test Vehicles with TPVs                                                     | 104        |

|   | 5.1.1 Electrical Test Vehicles with TPVs and Two Metal RDLs                                | 105           |

|---|--------------------------------------------------------------------------------------------|---------------|

|   | 5.1.1.1 Design of Test Vehicles                                                            | 105           |

|   | 5.1.1.2 Fabrication of Test Vehicles                                                       | 107           |

|   | 5.1.1.3 Characterization of Test Vehicles                                                  | 110           |

|   | 5.1.2 Electrical Test Vehicles with Four Metal RDLs                                        | 115           |

|   | 5.1.2.1 Design and Fabrication of Test Vehicles                                            | 115           |

|   | 5.1.2.2 Characterization of Test Vehicles                                                  | 119           |

|   | 5.2 Reliability Test Vehicles with TPVs                                                    | 122           |

|   | 5.2.1 Design and Fabrication of Test Vehicles                                              | 122           |

|   | 5.2.2 Thermal Cycling Tests and Resistance Measurement                                     | 125           |

|   | 5.2.3 SEM imaging                                                                          | 126           |

|   | 5.3 Summary                                                                                | 128           |

| 6 | RESEARCH SUMMARY AND CONCLUSIONS                                                           | 130           |

|   | 6.1 Research Summary                                                                       | 131           |

|   | 6.1.1 Modeling and Design of TPVs                                                          | 131           |

|   | 6.1.2 Formation, Liner Fabrication and Metallization of TPVs in Polycrystalline Silicon    | 132           |

|   | 6.1.3 Electrical and Reliability Characterization of TPVs in Polycryst Silicon Interposers | alline<br>134 |

|   | 6.2 Key Contributions                                                                      | 136           |

|   | 6.3 Future Extensions                                                                      | 138           |

|   | 6.4 Publications, Patents and Awards                                                       | 138           |

|   | 6.4.1 Peer-reviewed Journals                                                               | 138           |

|   | 6.4.2 Conference Proceedings                                                               | 139           |

|   | 6.4.3 Patents                                                                              | 142           |

|   | 6.4.4 Awards                                                                               | 142           |

REFERENCES 143

# LIST OF TABLES

|                                                                                                                         | Page |

|-------------------------------------------------------------------------------------------------------------------------|------|

| Table 1: Through-via processes in single-crystalline silicon interposer vs. proposed polycrystalline silicon interposer | 8    |

| Table 2: Comparison between TSV and TPV                                                                                 | 11   |

| Table 3: Key parameters for electrical modeling                                                                         | 26   |

| Table 4: Material properties used in mechanical modeling                                                                | 34   |

| Table 5: Cu properties used in mechanical modeling                                                                      | 34   |

| Table 6: Summary of stresses for different liner types and sidewall liner thicknesses                                   | 43   |

| Table 7: Parameter values for fracture strength after linear regression                                                 | 56   |

| Table 8: Process comparison between DRIE and Laser                                                                      | 59   |

| Table 9: Throughput comparison between DRIE and Laser                                                                   | 61   |

| Table 10: Unique properties of ZIF material                                                                             | 82   |

| Table 11: Parameters for electrical test vehicle with TPV and two metal RDLs                                            | 107  |

| Table 12: Parameters for reliability test vehicle                                                                       | 124  |

# LIST OF FIGURES

| 1                                                                                                                                                            | Page      |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|

| Figure 1: SOP concept for 3D system integration (Prof. Tummala)                                                                                              | 2         |

| Figure 2: Schematic drawing of traditional silicon interposer (Xilinx)                                                                                       | 3         |

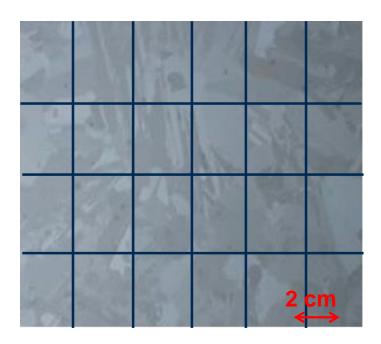

| Figure 3: Top view of the polycrystalline panel used in this study                                                                                           | 5         |

| Figure 4: Manufacturing process for polycrystalline silicon panels [12, 13]                                                                                  | 5         |

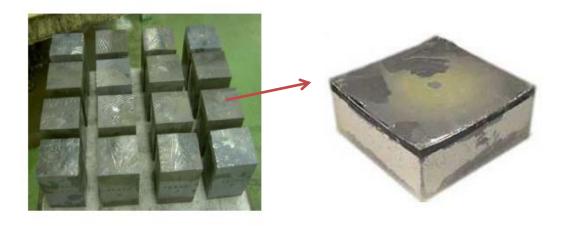

| Figure 5: 700 mm x 700 mm polycrystalline silicon blocks [13]                                                                                                | 6         |

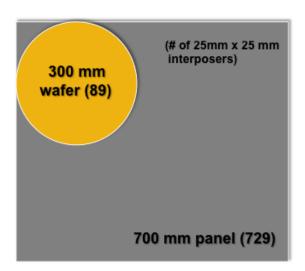

| Figure 6: Comparison of large square panel versus round wafer (GT-PRC)                                                                                       | 6         |

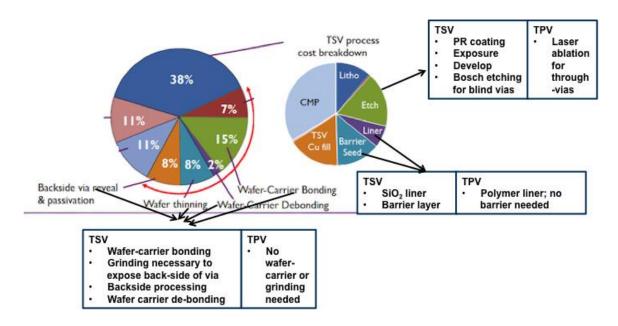

| Figure 7: Cost breakdown of TSV process (modified from IMEC [14])                                                                                            | 7         |

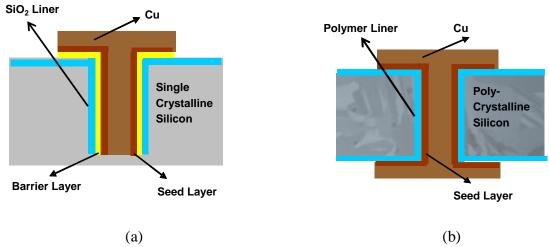

| Figure 8: Schematic cross-section comparison between (a) TSV in traditional Si interposer and (b) TPV in proposed polycrystalline Si interposer              | 8         |

| Figure 9: Cross-section schematic of polycrystalline silicon interposer with TPVs, RD wiring and assembly with different ICs on both sides                   | DL<br>10  |

| Figure 10: Typical insertion loss simulation for TSVs [23]                                                                                                   | 14        |

| Figure 11: Interfacial crack around SiO <sub>2</sub> [25]                                                                                                    | 16        |

| Figure 12: Cushion effect due to polymer material [29]                                                                                                       | 16        |

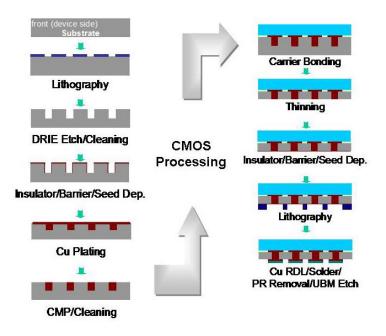

| Figure 13: Typical TSV fabrication process [31]                                                                                                              | 18        |

| Figure 14: (a) Top view and (b) cross-section view of the GSG model                                                                                          | 24        |

| Figure 15: (a) Insertion loss and (b) FEXT plots for TPV in polycrystalline silicon interposer (3 µm liner) and TSV in single-crystalline silicon interposer | 27        |

| Figure 16: FEXT plots for TPV in polycrystalline (5 µm liner) silicon interposer and in single-crystalline silicon interposer                                | TSV<br>28 |

| Figure 17: (a) Insertion loss and (b) FEXT plots for TPV with different in-via liner thickness                                                               | 29        |

| Figure 18: Schematic cross-section drawing of TPV for mechanical modeling                                                                                    | 32        |

| Figure 19: Schematic cross-section drawings and meshed models for (a) TPV and (b)                                                                            | 33        |

| Figure 20: Thermal loading curve for mechanical modeling                                                                                                  | 35         |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------|------------|

| Figure 21: First principal stress in silicon for (a) TPV and (b) TSV at 125 $\ensuremath{^{\circ}}$                                                       | 36         |

| Figure 22: Shear stress in (a) TPV and (b) TSV at 125 $^{\circ}\mathrm{C}$                                                                                | 38         |

| Figure 23: First principal stress in Si for TPV with sidewall liner thickness of (a) 5 $\mu n$ (b) 10 $\mu m$ and (c) 15 $\mu m$ at 125 $^{\circ}{\rm C}$ | m,<br>40   |

| Figure 24: Shear stress in TPV with sidewall liner thickness of (a) 5 $\mu$ m, (b) 10 $\mu$ m at (c) 15 $\mu$ m at 125 $^{\circ}$ C                       | nd<br>41   |

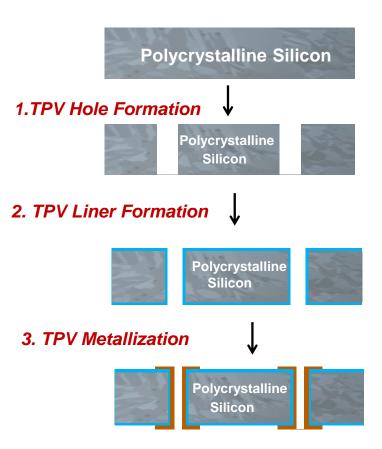

| Figure 25: TPV fabrication process flow                                                                                                                   | 47         |

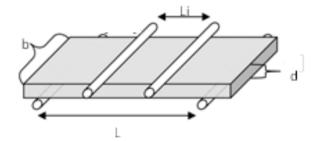

| Figure 26: Four-point bend testing tool to evaluate fracture strength                                                                                     | 49         |

| Figure 27: Top view of an as-cut polycrystalline silicon panel                                                                                            | 50         |

| Figure 28: Top view of polycrystalline silicon panel with (a) large grain and (b) multi-<br>small grains                                                  | iple<br>50 |

| Figure 29: Schematic drawing of the sample diced into small pieces                                                                                        | 51         |

| Figure 30: Schematic drawing of Fixture setup for four-point bending test (modified [59])                                                                 | from<br>52 |

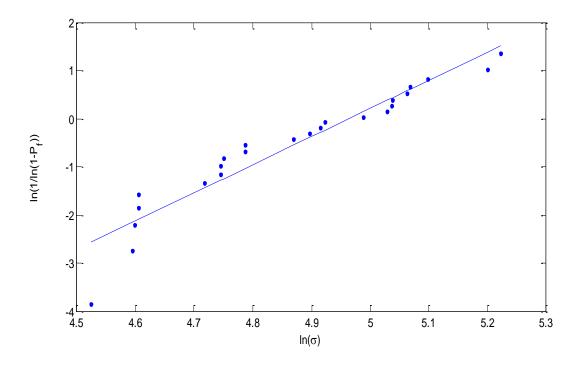

| Figure 31: Weibull plot for fracture strength of polycrystalline silicon panel                                                                            | 54         |

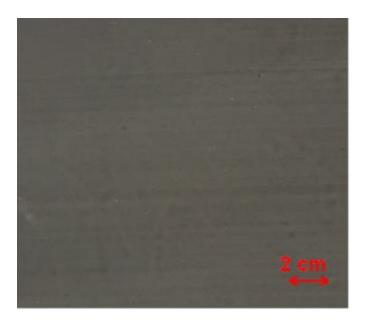

| Figure 32: Top view of polymer-laminated polycrystalline silicon panel                                                                                    | 55         |

| Figure 33: Weibull plots of fracture strength for silicon panels with and without polynliners                                                             | mer<br>56  |

| Figure 34: Schematic drawing of Bosch process [67]                                                                                                        | 58         |

| Figure 35: Schematic drawing of laser ablation [68]                                                                                                       | 59         |

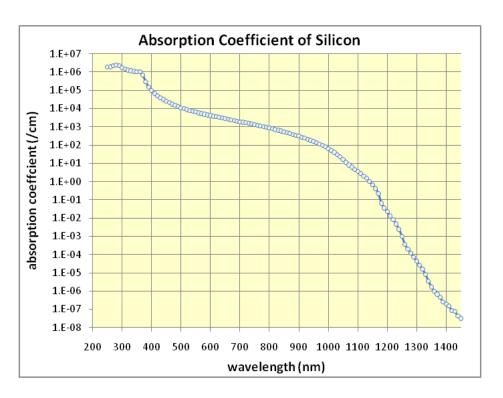

| Figure 36: Absorption coefficient of silicon for light with different wavelength [70]                                                                     | 63         |

| Figure 37: (a) Entrance and (b) exit view of the via drilled by picosecond laser                                                                          | 65         |

| Figure 38: Trepanning method for via drilling [71]                                                                                                        | 66         |

| Figure 39: Top view of vias drilled by excimer laser with diameter of (a) 6 $\mu$ m, (b) 12 and (c) 15 $\mu$ m                                            | 2 μm<br>68 |

| Figure 40: Percussion method for via drilling [71]                                                                                                        | 70         |

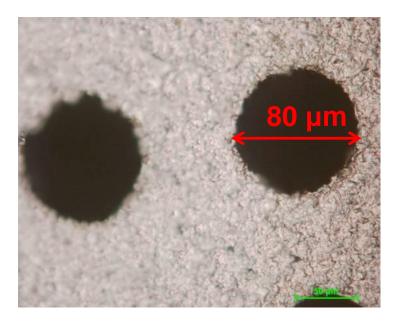

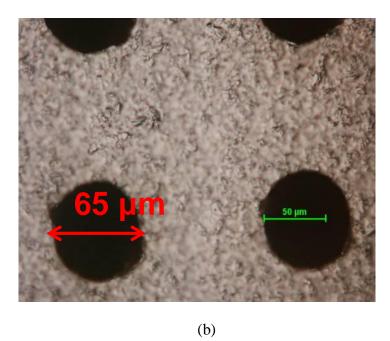

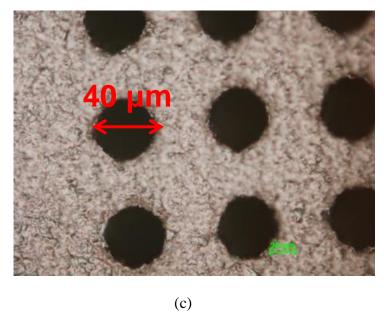

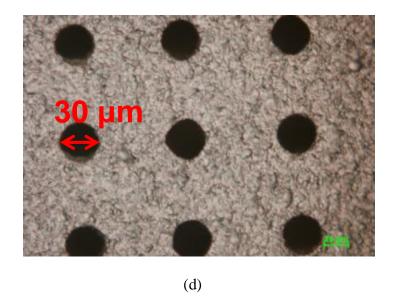

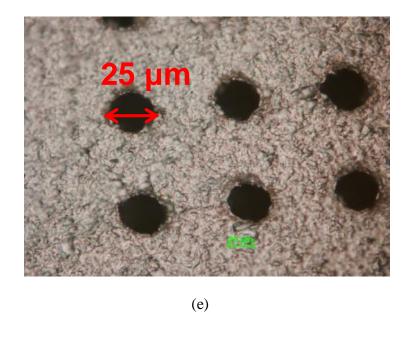

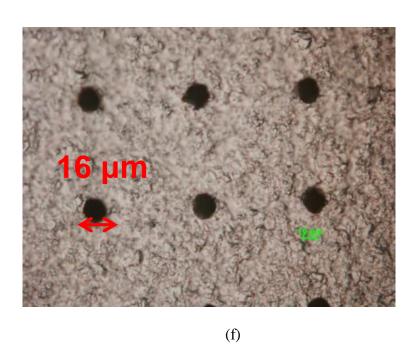

| Figure 41: Optical images of vias drilled by UV laser with (a) 80 μm entrance and (b μm exit; and (c) 40 μm entrance and (d) 30 μm exit; and (e) 25 μm entrance and (f) 16 μm exit |           |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|

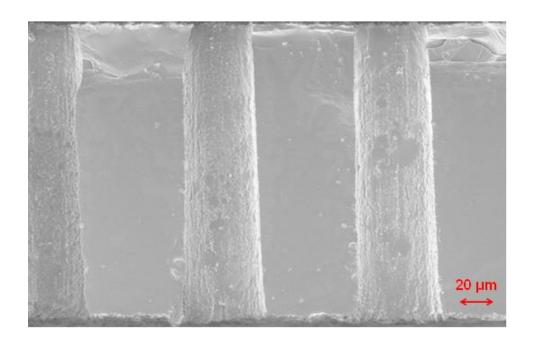

| Figure 42: SEM cross-section image of TPV drilled by UV laser                                                                                                                      | 74        |

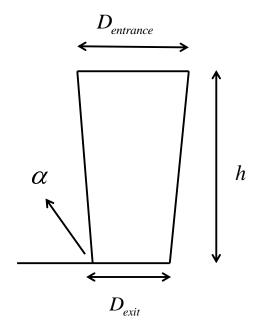

| Figure 43: Schematic cross-section drawing of via tapering                                                                                                                         | 74        |

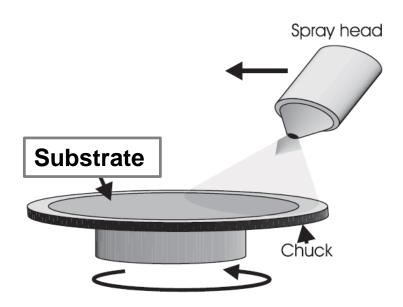

| Figure 44: Schematic drawing of spray coating system (modified from [72])                                                                                                          | 76        |

| Figure 45: Cross-section image of TPV with polymer liner by spray coating                                                                                                          | 77        |

| Figure 46: Physical behavior of liquid around edge [73]                                                                                                                            | 78        |

| Figure 47: Schematic drawing of ED system (modified from [74])                                                                                                                     | 79        |

| Figure 48: Cross-section view of metalized TPV with ED polymer                                                                                                                     | 80        |

| Figure 49: Double laser method for liner formation                                                                                                                                 | 81        |

| Figure 50: High insulation reliability of ZIF polymer [75]                                                                                                                         | 84        |

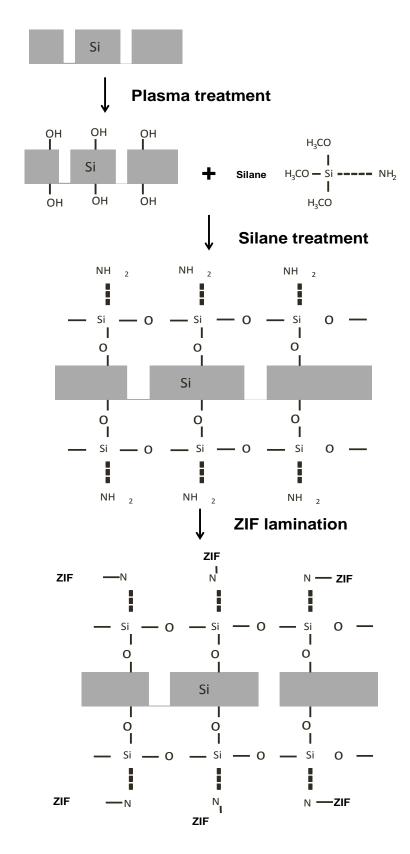

| Figure 51: Mechanism of silane treatment for adhesion improvement process                                                                                                          | 86        |

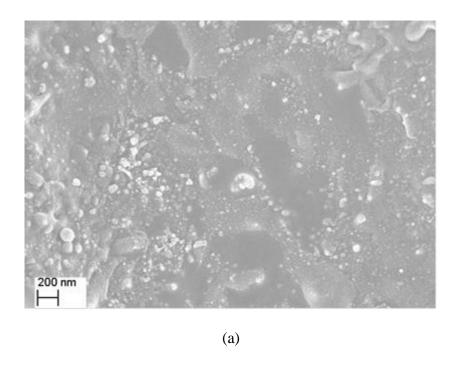

| Figure 52: SEM images for silicon surfaces (a) before and (b) after silane treatment                                                                                               | 87        |

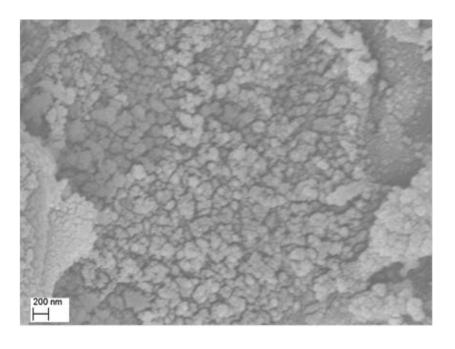

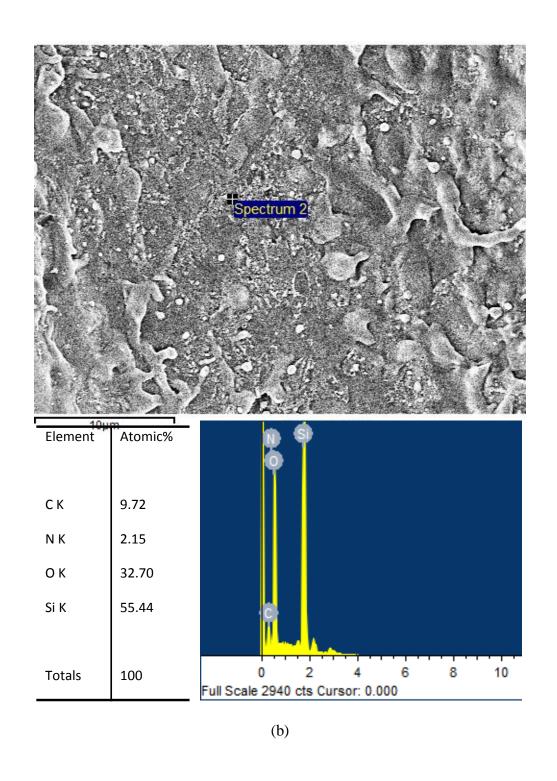

| Figure 53: EDS results of TPV sidewall (a) before plasma treatment and (b) after pla treatment                                                                                     | sma<br>89 |

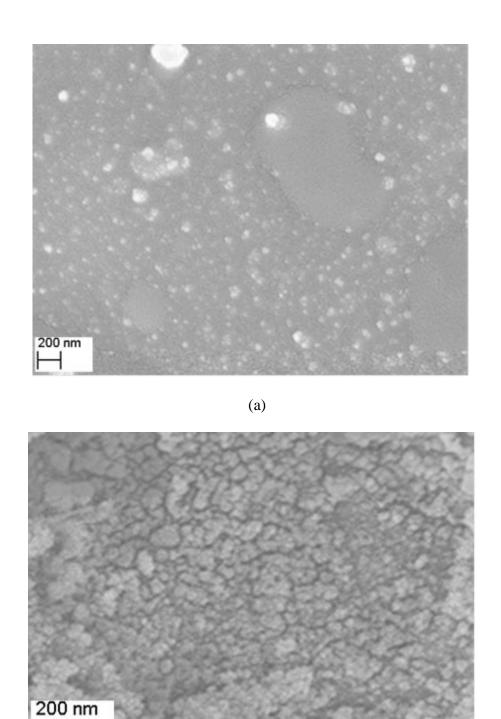

| Figure 54: SEM images of TPV sidewall (a) before silane treatment and (b) after sila treatment                                                                                     | ne<br>91  |

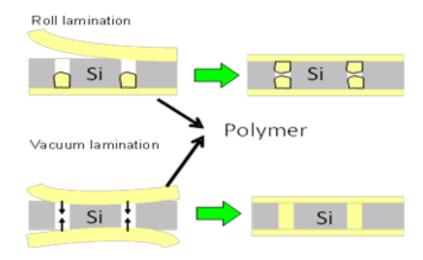

| Figure 55: Single-side roll lamination vs. double-side vacuum lamination                                                                                                           | 93        |

| Figure 56: Schematic drawing of setup for vacuum lamination                                                                                                                        | 93        |

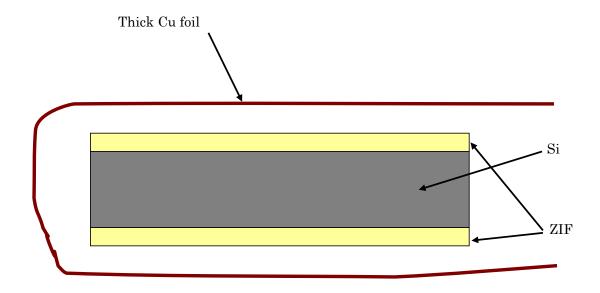

| Figure 57: Schematic drawing of stack-up for hot-press                                                                                                                             | 94        |

| Figure 58: Thermal profile for ZIF polymer curing                                                                                                                                  | 95        |

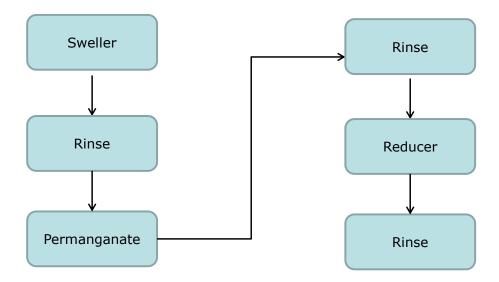

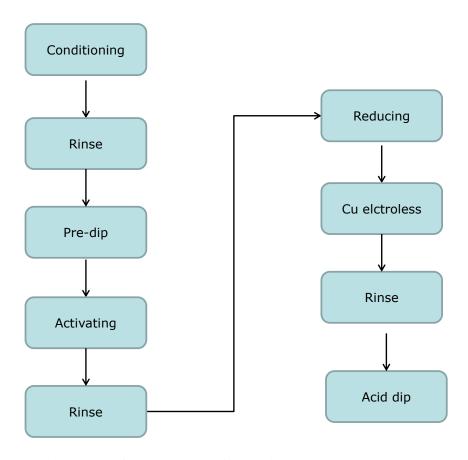

| Figure 59: Detailed steps for Desmear process                                                                                                                                      | 97        |

| Figure 60: Detailed steps for electroless Cu plating                                                                                                                               | 98        |

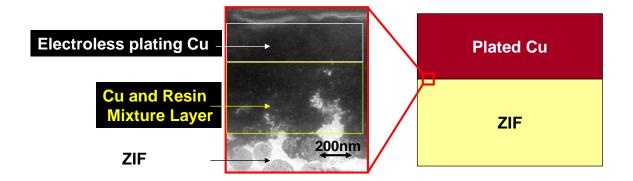

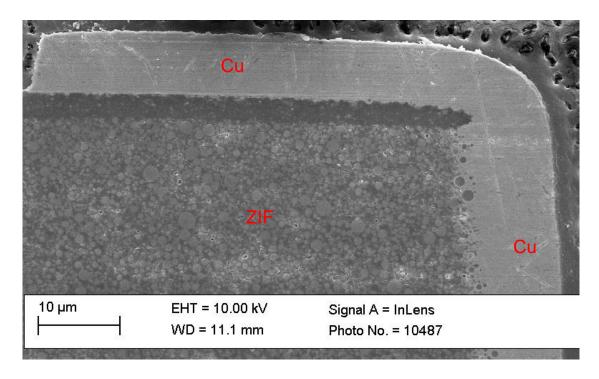

| Figure 61: Cross-section of interface between electroless plated Cu and ZIF [79]                                                                                                   | 99        |

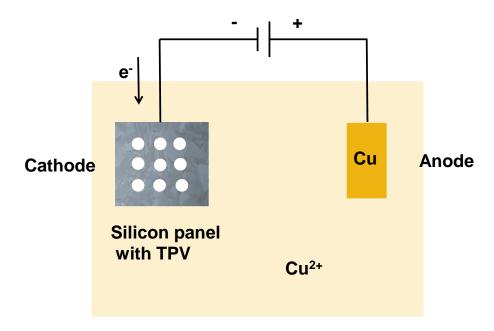

| Figure 62: Schematic drawing of Cu electrolytic plating system                                                                                                                     | 100       |

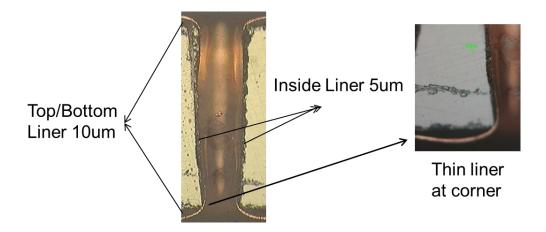

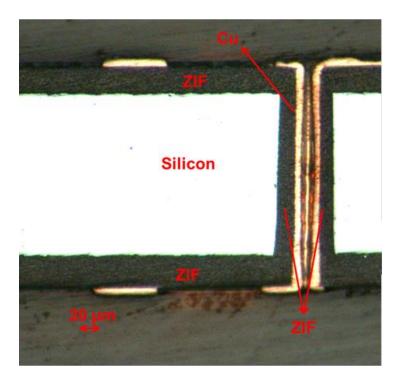

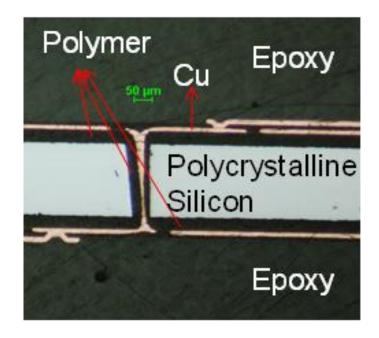

| Figure 63: Optical cross-section image of metalized TPV with ZIF liner                                                                                                             | 101       |

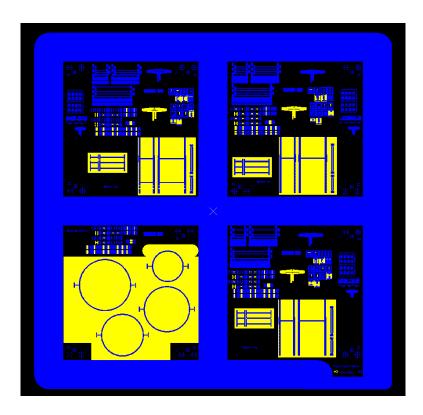

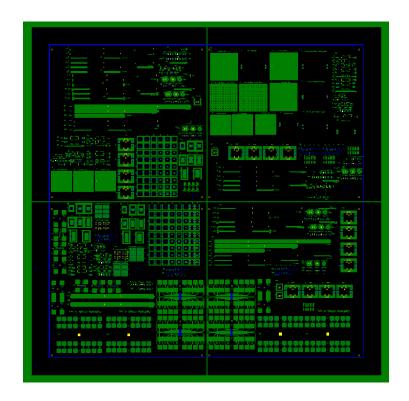

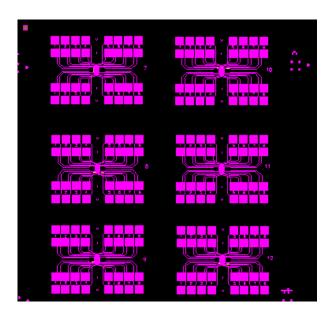

| Figure 64: Snapshot of the mask for electrical test vehicle with two metal RDLs                                                            | 106         |

|--------------------------------------------------------------------------------------------------------------------------------------------|-------------|

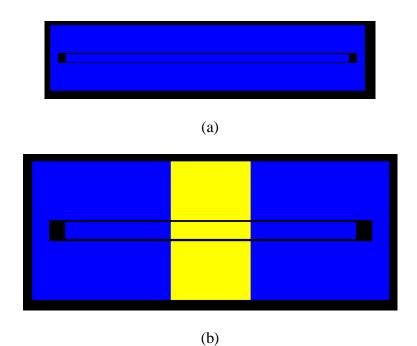

| Figure 65: Snapshot of designed (a) CPW lines and (b) CPW-TPV structure with two transitions                                               | 106         |

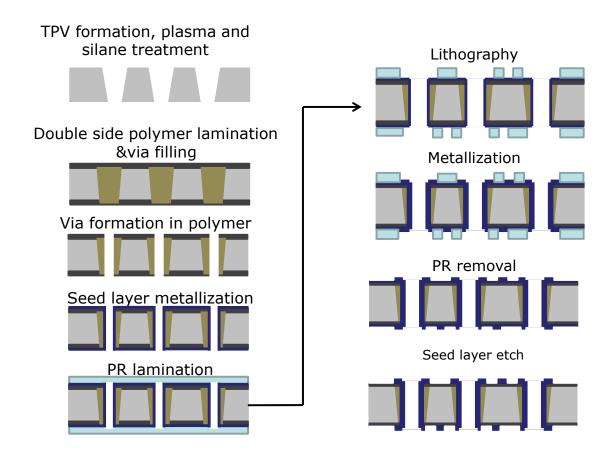

| Figure 66: Process flow for electrical test vehicle with TPVs and two metal RDLs                                                           | 108         |

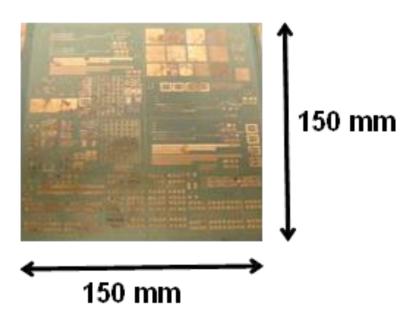

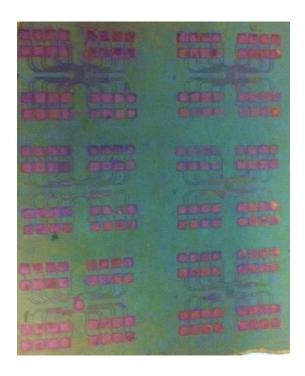

| Figure 67: Top view of the electrical test vehicle with TPVs and two metal RDLs                                                            | 110         |

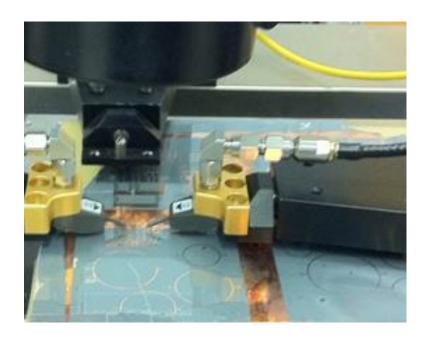

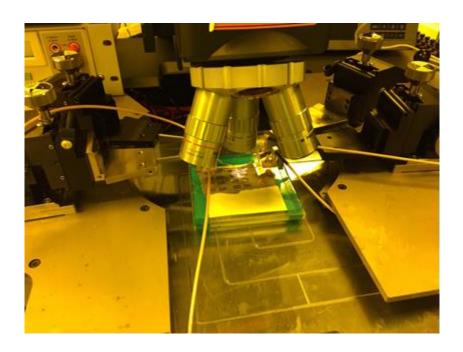

| Figure 68: High frequency measurement for polycrystalline silicon interposer                                                               | 111         |

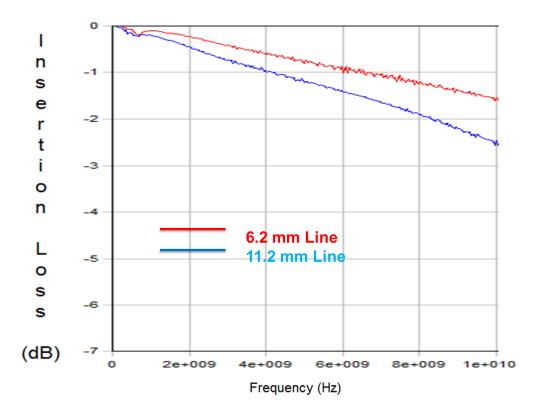

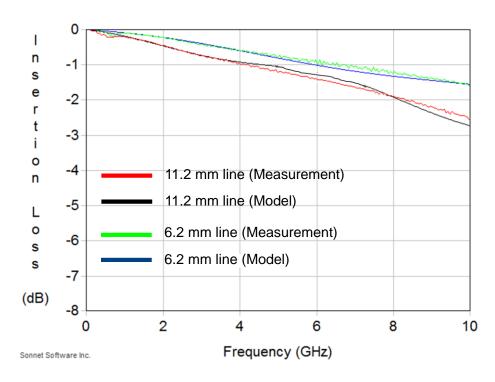

| Figure 69: Insertion loss measurements for CPW lines with different lengths                                                                | 112         |

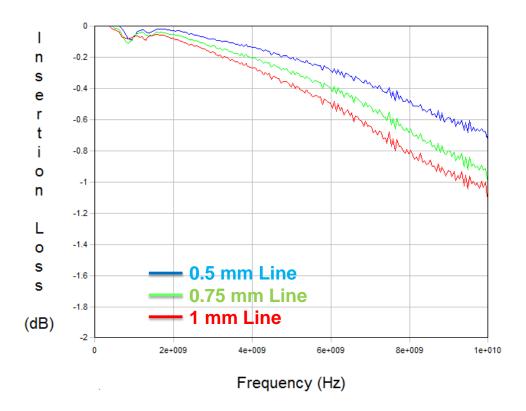

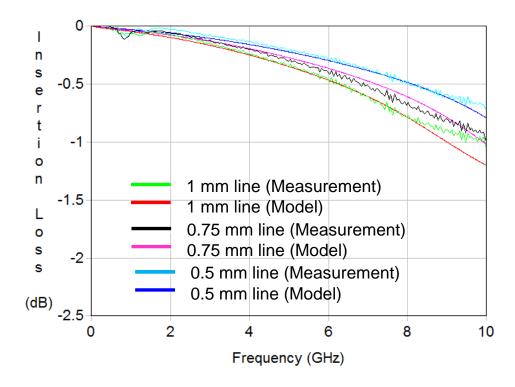

| Figure 70: Insertion loss measurements for CPW-TPV transitions with different trace length                                                 | e<br>113    |

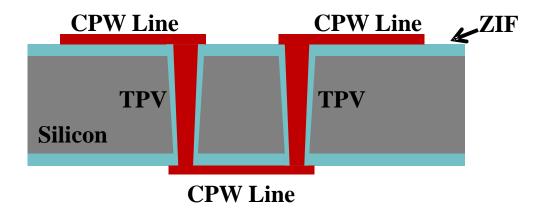

| Figure 71: Schematic cross-section drawing of CPW-TPV transition (2 transitions)                                                           | 114         |

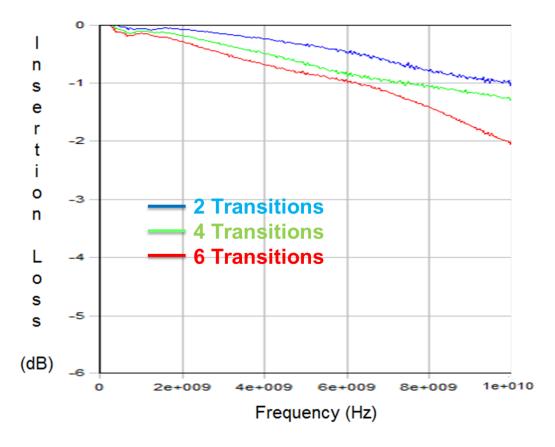

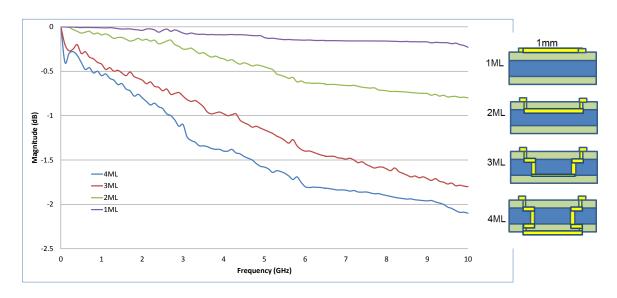

| Figure 72: Insertion loss measurements for CPW-TPV structures with different number of transitions                                         | oers<br>115 |

| Figure 73: Snapshot of mask design for electrical test vehicle with four metal RDLs                                                        | 116         |

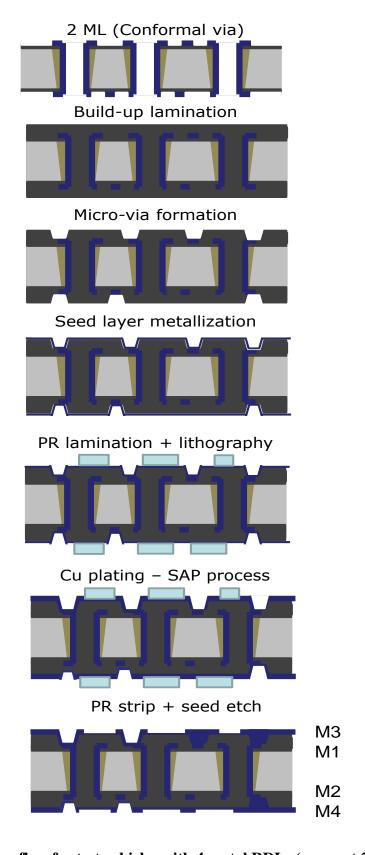

| Figure 74: Process flow for test vehicles with 4-metal RDLs (segment 2)                                                                    | 117         |

| Figure 75: Top view for polycrystalline silicon interposer with TPVs and four metal RDLs                                                   | 118         |

| Figure 76: Optical image of cross-section for polycrystalline silicon interposer with and four metal RDLs                                  | ΓPVs<br>119 |

| Figure 77: Simulation and test results of Insertion loss for CPW lines                                                                     | 120         |

| Figure 78: Simulation and test results of Insertion loss for CPW-TPV transitions                                                           | 120         |

| Figure 79: Measurements of insertion loss in CPW lines, TPVs and blind via transition in structures with different numbers of metal layers | ons<br>122  |

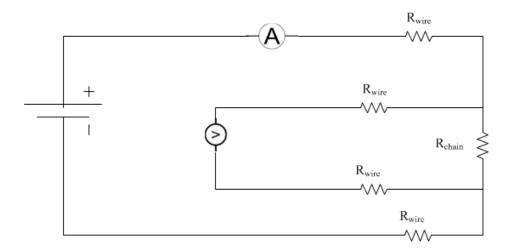

| Figure 80: Schematic circuit drawing for four-point probe method                                                                           | 123         |

| Figure 81: Snapshot of the designed test structures                                                                                        | 124         |

| Figure 82: Top view of fabricated test structures                                                                                          | 125         |

| Figure 83: Resistance measurement of reliability sample                                                                                    | 126         |

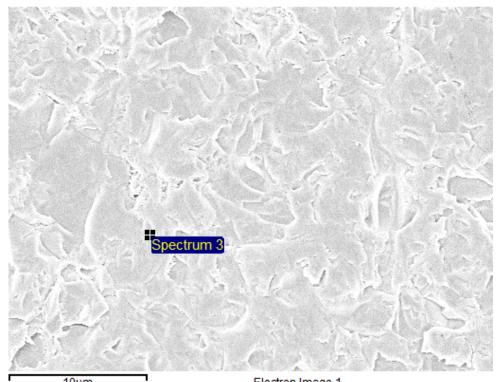

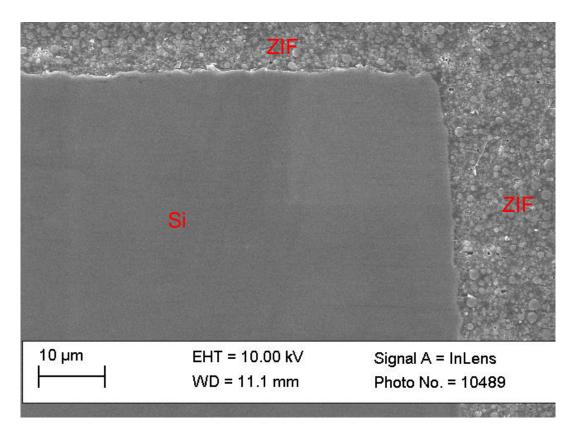

| Figure 84: SEM image of Cu/ZIF interface                                                                                                   |             |

| 2.26.1.2 0 11 2.2.2 11.11.160 0.1 0.11. 11.00.11.00                                                                                        | 127         |

### **SUMMARY**

Interconnections between integrated circuits (ICs) and print circuit boards (PCBs) are primarily achieved currently with organic packages at low I/O pitch. Organic packages, however, have limitations in increasing these I/Os due to their poor thermal and dimension stabilities for them to be fabricated as fine pitch interposers. To address these challenges, silicon interposers have been developed and manufactured. Current silicon interposers, based on through-silicon-via (TSV) techniques, however, suffer from high production cost because of expensive CMOS (Complementary metal-oxide semiconductor) processes and small wafer sizes. They also suffer from electrical loss issues in spite of thin SiO<sub>2</sub> layers. In addition, the thin SiO<sub>2</sub> layers can also lead to reliability problems. To address these issues, this research, for the first time, presents an entirely different approach by proposing and demonstrating polycrystalline silicon in large panel form, which is widely used in solar industry, as an interposer material at much lower cost.

The objective of this research is to study, explore and demonstrate thin panel-based, low-resistivity polycrystalline silicon as a suitable interposer material to achieve high electrical performance at lower cost with reliable through-package-vias (TPVs) for interposer applications. A thick, low loss polymer, with double-side processing, has been developed to address the electrical challenges presented by the much lower resistivity of polycrystalline silicon panel. The TPV structure in polycrystalline silicon, combined with polymer coating with low Young's modulus, is also proposed to achieve reliability under

thermal cycling. Such polymer layers can also help to improve the handling and processing of thin panels.

Both electrical and mechanical models have been developed for the polymer-lined TPV in polycrystalline silicon panels. Parametric studies have also been carried out. The fabrication of TPV in polycrystalline silicon has been developed without any carriers for handling and processing the thin panels. The fracture strength, which is critical in handling and processing large thin panels, has been fundamentally quantified by using both four-point bending tools and Weibull plots. Surface liners are used to improve the handling of silicon panels and the results are quantitatively studied. Several TPV formation methods and mechanisms are explored, including UV laser, excimer laser and picosecond laser ablation. The technical approach for the liner formation involved polymer-filling of TPV, followed by laser ablation to form an "inner" via, leading to invia polymer liners with controlled thickness. The mechanisms of both silane treatment to improve polymer-silicon adhesion and polymer filling are discussed. The TPV metallization consists of a low cost, double-side all-wet electroless copper seed layer, followed by Cu electroplating. By integrating all these processes, polycrystalline silicon interposer test vehicles have been demonstrated with up to four metal RDLs (redistribution layers) and characterized for their insertion loss. The model-to-hardware correlation has also been carried out. Reliability test vehicles are fabricated for thermal cycling tests and SEM (scanning electron microscope) cross-section imaging.

The key contributions and novelty of this study are as follows:

- First demonstration of TPV in polycrystalline silicon to achieve

- High performance

- High reliability

- Panel-based approach for potential low cost

- Simpler TPV vs. traditional TSV

- Large size polycrystalline silicon panel vs. small size singlecrystalline silicon wafer

- Laser-based TPV vs. DRIE (deep reactive-ion etching)-based TSV

- Simpler process with reduced number of steps vs. complex processes for TSV

- In addition, demonstration of double-side processed dry film polymer in TPV with

- Low dielectric loss to improve TPV performance

- Low modulus to act as stress buffer in TPV

- Improvement on handling of thin polycrystalline silicon panels

### **CHAPTER 1**

### INTRODUCTION

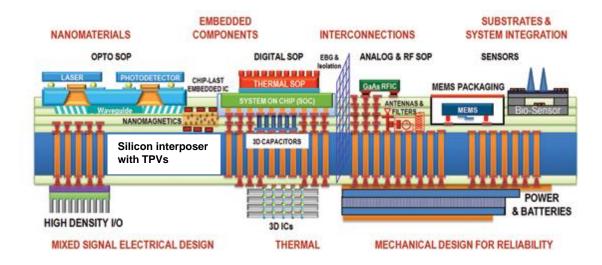

The rapid development of microelectronic systems, such as smartphones and tablets, has fueled the growing interest of improving the advanced packaging technologies, including: a) higher performance, b) smaller form factor, c) multifunctionality, d) better reliability and e) lower cost. Such a need continues to drive rapid transistor scaling with system-on-chip (SOC) [1]. However the implementation of SOC has several critical issues including design complexity, fabrication challenges and high cost. More importantly, transistor scaling following Moore's law is being predicted to reach performance and cost barriers beyond 16 nm technology node [2]. Therefore, in order to continue miniaturizing the size of electronic systems, the industry focus has begun to shift to three-dimensional (3D) integration techniques, such as 3D IC (integrated circuits) stacking enabled by through-silicon-vias (TSVs). Georgia Tech Packaging Research Center (GT-PRC), on the other hand, proposes 3D interposer with throughpackage-vias (TPVs) to package entire system with the concept of system-on-package (SOP) technology. Such concept tends to eliminate the gap between ICs, packages and print-circuit-boards (PCBs), aiming to revolutionize the system functionality with smallest system size and lowest cost, yet achieving high performance and good reliability [3]. The schematic cross-section drawing of SOP has been shown in Figure 1.

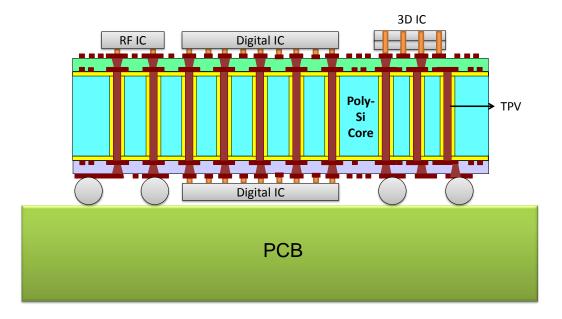

Figure 1. SOP concept for 3D system integration (Prof. Tummala)

As presented in Figure 1, TPVs in the interposer serve as the high-density interconnections between different components and are important for enabling the SOP concept for next generation 3D system integration. Hence this study is focused on modeling, design and demonstration of TPVs in the interposer, targeting at high performance and reliability with low cost.

### 1.1 Evolution of Interposer Technology

Interposers by definition connect ICs with fine pitch I/Os (Inputs/Outputs) on the top side and to BGA (ball grid array) packages on the bottom side with larger-pitch with flip-chip assembly. Currently, the package approach for interconnections is mainly based on organic packages at low pitch and not as interposers [4, 5]. But interposers are necessary for pitches below 40 microns. Organic substrates are limited in achieving this pitch, due to poor dimensional and thermal stabilities and high CTE (Coefficient of Thermal Expansion) [6]. Therefore silicon interposers with TSVs processed on passive silicon wafers are being pursued [7, 8]. The fabrication of such traditional silicon

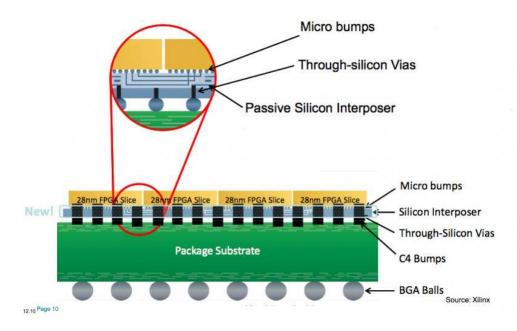

in single-crystalline silicon wafers. Inside these TSVs, thin layers of SiO<sub>2</sub> are widely used as the liners to insulate the lossy silicon. There is also the need for diffusion control between copper inside TSV and silicon, which is typically accomplished by using barriers such as Ti, TiN and TaN. The Cu seed is then formed using sputtering process and the via is then filled with Cu by electrolytic plating. A CMP (chemical mechanical polishing) process is necessary to expose the Cu vias. Figure 2 is a typical traditional silicon interposer with TSVs from Xilinx [9].

Figure 2. Schematic drawing of traditional silicon interposer (Xilinx)

Although silicon interposers have been developed to address the limitations of organic interposers, they have their own challenges [10, 11]. Since the number of interposers coming from 200 or 300 mm silicon wafers is low, particularly if the interposers are large, 50-60 mm in size, serious cost concerns remain as the biggest barriers for adoption of silicon interposers. The high cost is also attributed to the

expensive process to form TSVs as well as the process for single-side redistribution layers (RDLs). Additional challenge with silicon interposers is to do with electrical loss of silicon in spite of SiO<sub>2</sub> dielectric layer. This is always recognized as the second major concern with traditional silicon interposers. The thin insulation layer can also result in reliability problems, leading to cracking, current leakage and finally signal loss.

### 1.2 Rational of Polycrystalline Silicon Interposers with TPVs

This study tends to address the shortcomings of traditional silicon interposers by presenting an entirely different approach. The strategy of interposer technology of Georgia Tech Packaging Research Center is a panel-based polycrystalline silicon aimed at lowering the total cost of fabricating the interposer that includes raw polycrystalline silicon cost as well as all other materials and processes required to form the interposer wiring with high performance and reliability.

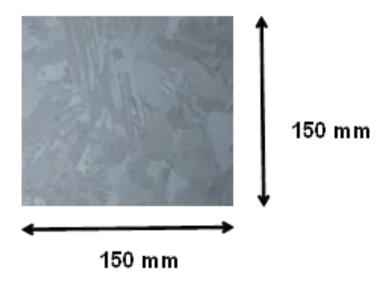

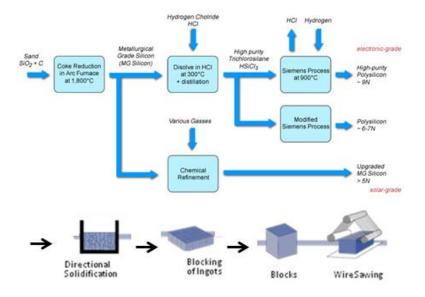

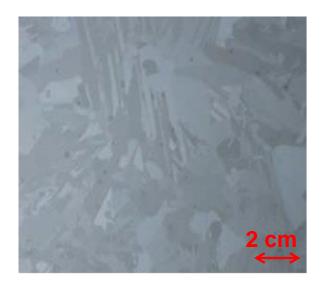

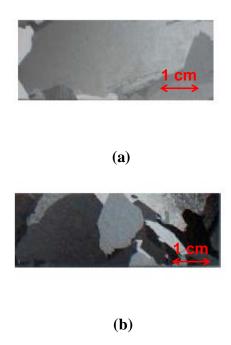

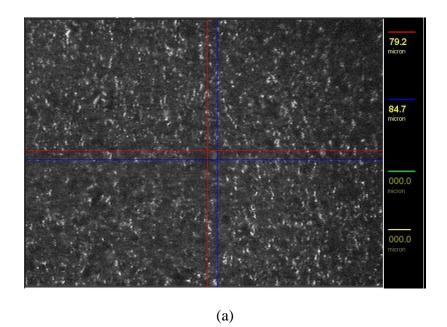

The top view of the 200 µm polycrystalline silicon panel used in this study is shown in Figure 3. Polycrystalline silicon panels have been widely used in photovoltaic industry as the substrate material for solar cell applications. The manufacturing process for polycrystalline silicon panels is summarized in Figure 4 [12, 13]. In this particular study, solar-grade polycrystalline silicon panels are used. The fabrication process of polycrystalline silicon panel starts with sand or quartz. Metallurgical-grade (MG) silicon is obtained from the reduction of silicon oxide in the presence of carbon, followed by chemical refinement through various gasses to achieve solar grade polycrystalline silicon. Such silicon is then transformed into ingots by directional solidification. Finally the large ingots are cut to blocks and wire-cut to form polycrystalline silicon panels. The specific process has led to lower purity and resistivity of solar grade polycrystalline silicon in

contrast to electrical grade single-crystalline silicon. But the manufacturing costs are also reduced significantly.

Figure 3. Top view of the polycrystalline panel used in this study

Figure 4. Manufacturing process for polycrystalline silicon panels [12, 13]

Polycrystalline silicon panel to form the interposer substrates has a few advantages, namely: simpler and cheaper to fabricate than single-crystalline wafer and

can be scaled to large sizes, up to 700 mm, as shown in Figure 5. More importantly, the larger size substrate means, it yields more numbers of interposers. Figure 6 presents a comparison of 700 mm by 700 mm square panel versus 300 mm round wafer, in yielding numbers of 25 mm by 25 mm interposers. As the calculation shows, the large-size panels (729) produce about 8X more interposers than from 300 mm wafer (89), promising to lower the cost of single unit interposers.

Figure 5. 700 mm x 700 mm polycrystalline silicon blocks [13]

Figure 6. Comparison of large square panel versus round wafer (GT-PRC)

Furthermore, the double-side process for fabricating the TPVs simplifies and replaces the costly steps used in TSV techniques. Figure 7 breaks down the cost for TSV fabrication process. It can be seen that for particularly high cost processes such as etching and liner formation, TPV presents a significantly simpler process with reduced steps, leading to lower production cost. Steps such as wafer thinning and bonding/de-bonding are also completely eliminated.

Figure 7. Cost breakdown of TSV process (modified from IMEC [14])

Besides lower cost than traditional silicon interposers, the polycrystalline silicon interposer also targets at higher performance and reliability. Figure 8 illustrates a cross-section schematic, comparing TSV in traditional single-crystalline silicon interposers with TPV in proposed polycrystalline silicon interposers. Table 1 summarizes and compares substrate size and key process steps in two technologies. In the TPV process, thick polymer liner is proposed to replace the combination of thin SiO<sub>2</sub> and diffusion barrier layer for TSV. Such a low loss polymer material improves the electrical

performance of TPVs in comparison with the low resistivity of the polycrystalline silicon substrate. Furthermore, the polymer material presents good mechanical properties such as low modulus, which help to achieve good reliability of TPV under thermal attack.

Figure 8. Schematic cross-section comparison between (a) TSV in traditional Si interposer and (b) TPV in proposed polycrystalline Si interposer

Table 1. Through-via processes in single-crystalline silicon interposer vs. proposed polycrystalline silicon interposer

|               | Traditional Si Interposer               | Polycrystalline Si Interposer    |

|---------------|-----------------------------------------|----------------------------------|

| Material Form | Single-crystalline silicon wafer        | Polycrystalline silicon panel    |

| Manufacturing | 200~300 mm                              | Up to 700 mm                     |

| Size          |                                         |                                  |

| Hole          | Bosch process                           | Laser ablation                   |

| Formation     | (Need polishing to expose via on        |                                  |

|               | the back side)                          |                                  |

| Liner         | SiO <sub>2</sub> by CVD (chemical vapor | Double-side                      |

| Formation     | deposition) + Barrier by PVD            | polymer filling and laser via    |

|               | (physical vapor deposition)             |                                  |

| Seed Layer    | Sputtering                              | Electroless plating              |

| RDL Process   | Single-side process                     | Double-side dry film lithography |

|               |                                         | and plating                      |

In general, the proposed polycrystalline silicon interposer has the potential to achieve the same performance as the traditional silicon interposer at significantly lower cost, for the following reasons:

- 1) A panel-based approach that is as much as 8X larger substrate size using polycrystalline silicon

- 2) Polycrystalline silicon is a lower cost material than single-crystalline silicon

- 3) Lower cost TPV processes not requiring Bosch process for TSV and SiO<sub>2</sub> liner

- 4) Thick polymer liner within TPV, for higher performance and higher reliability

- 5) Double-side, low cost process for fabrication of RDLs

A cross-section schematic of the polycrystalline silicon interposer with TPVs and assembly of multiple ICs is presented in Figure 9. The double-side approach used in integrating the components on both sides results in a reduced interposer size, leading to miniaturized packages at even lower cost. This study presents a first, pioneering research to explore polycrystalline silicon in large panel form as a low cost and high performance interposer. It presents a combination of materials and processes to form TPVs and RDLs.

Figure 9. Cross-section schematic of polycrystalline silicon interposer with TPVs, RDL wiring and assembly with different ICs on both sides

## 1.3 Research Objectives, Challenges and Tasks

The objective of the proposed research is to explore and demonstrate thin polycrystalline silicon as a suitable interposer material to achieve high performance and high reliability but at lower cost. The critical parameters, which this study is targeting, are listed in Table 2. The high electrical performance and reliability are proposed to be achieved by development of the thick polymer liner with low electrical loss and low modulus.

Table 2. Comparison between TSV and TPV

| Parameters                 | TSV in traditional silicon interposer                                         | TPV in polycrystalline silicon interposer                                                                                                    |

|----------------------------|-------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------|

| Electrical     Performance | Low performance due to thin SiO <sub>2</sub> insulator                        | High performance with thick insulating polymer                                                                                               |

| 2. Reliability             | Failure due to thin SiO <sub>2</sub> cracking or breakdown                    | High reliability due to low modulus polymer liner                                                                                            |

| 3. Cost                    | High cost due to  • Small wafer size, up to 300 mm  • High process complexity | Lower cost due to  • Low cost of polycrystalline silicon  • Large panel size, up to 700 mm  • Simpler double-side process with reduced steps |

To achieve the above goals, three main research challenges are identified:

- a) High electrical performance: Due to its lower purity level, polycrystalline silicon material presents a much lower resistivity (0.5  $\Omega$ -cm) than the traditional wafer. Hence addressing this higher loss and yet achieve higher performance is a major challenge.

- b) TPV reliability: achieving reliability in spite of the CTE mismatch between Cu and polycrystalline silicon.

- c) Handling and processing: Polycrystalline silicon is a brittle material and it has never been studied as the interposer substrate. So the handling of the thin substrate and its processability to form interposers are very critical.

To address these challenges, three research tasks are proposed and carried out.

The details are organized into following chapters. Chapter 2 summarizes the prior art of

research in fabricating traditional TSVs and in polycrystalline silicon. Chapter 3 describes the electrical and mechanical modeling and design of TPVs in polycrystalline silicon. Chapter 4 addresses the challenges in handling and fabrication of TPVs in polycrystalline silicon, including via formation, liner fabrication, and metallization. Both the electrical and reliability characterization of TPVs in fabricated-polycrystalline silicon interposers are summarized in Chapter 5. The final chapter, Chapter 6, summarizes the key contributions and future extensions.

### **CHAPTER 2**

### LITURATURE SURVEY

The previous chapter discussed the motivation for TPVs in polycrystalline silicon research, and defined the research objectives, fundamental challenges and research tasks. This chapter summarizes the prior art literature on traditional silicon interposers with TSVs and polycrystalline silicon materials.

### 2.1 Prior Art on Silicon Interposers with TSVs

The first research on silicon interposers dated back to the 1980s by IBM and Bell Labs [15, 16]. The early silicon interposers were fabricated on small wafers with copper-polymer re-distribution layers, but without TSVs, and had to be interconnected to the system using wire bonds. The development of TSV processes in the 1990s and 2000s led to thin silicon interposers with TSV interconnections to packages or printed wiring boards (PWB) [17, 18]. Most of the recent research has focused on TSVs in single-crystalline silicon for high-density 2.5D interposers. This section provides a brief overview of TSV and TSV-based interposer research pursued in both industry and academia.

### 2.1.1 Electrical Modeling and Performance of TSVs

The high electrical loss of silicon and the performance limits of TSVs were identified as a key motivation for this research. This section reviews selected published literature in the electromagnetic simulation and characterization of TSVs.

Bandyopadhyay [19, 20] presented an accurate equivalent circuit model for TSVs by considering the semiconducting effect of silicon substrates. The need for low capacitance signal vias to reduce the propagation delay was highlighted. A parametric study was performed on TSV capacitance, leading to a recommendation of small via diameters and thick liners for improving signal TSV performance. Other options proposed to reduce the TSV capacitance and improve TSV performance in single crystalline-silicon include the use of low-k dielectrics, high-resistivity silicon substrates, and TSVs filled with low work function metals.

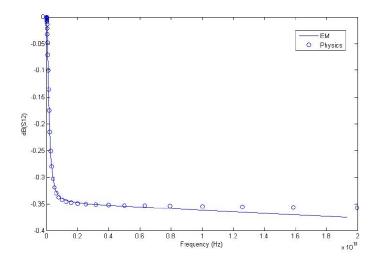

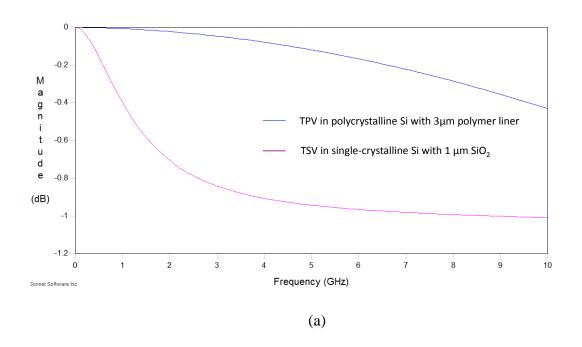

The insertion loss of TSVs was studied by Xu [21, 22], where the effect of different TSV configurations on TSV performance was analyzed using 3D electromagnetic solvers. It was shown that TSVs of smaller height and radius reduced the insertion loss. Swaminathan [23] also reported simulation results for TSVs with 15  $\mu$ m radius, 100  $\mu$ m height and with 0.1  $\mu$ m thickness of SiO<sub>2</sub>. However, it was observed that the obtained insertion loss (Figure 10) was higher than expected for TSVs with such short lengths.

Figure 10. Typical insertion loss simulation for TSVs [23]

As mentioned in Chapter 1, the electrical performance of the silicon via is limited by the lossy silicon substrate. Thick oxide layers and high resistivity silicon substrate reduce the insertion loss, but are viewed as high cost solutions. Therefore, the electrical performance issues remain a fundamental challenge for traditional silicon interposers with TSVs.

### 2.1.2 Mechanical Modeling and Reliability of TSVs

The second fundamental challenge for silicon interposers with TSVs is their thermo-mechanical reliability, driven by the difference in CTE (Coefficient of Thermal Expansion) between Cu of 17 ppm/°C and silicon of 3 ppm/°C. There have been a number of published studies on the mechanical modeling and reliability analysis of TSVs in single-crystalline silicon, but no publications on polycrystalline silicon TPV reliability.

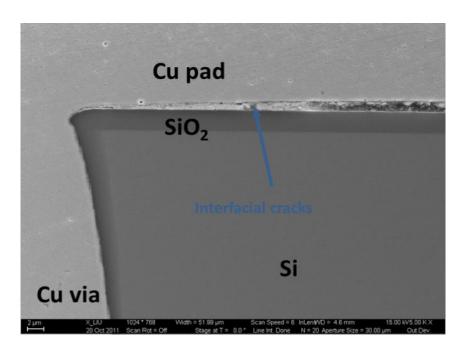

Liu [24-28] have reported extensively on the finite element modeling (FEM) simulations of the stress distribution in copper filled TSVs. These models showed that the stresses in the Cu/SiO<sub>2</sub> interface and in the SiO<sub>2</sub> layer lead to potential failure mechanisms in TSVs, such as liner delamination and cracking. Arrays of TSVs with 40 µm diameter and 260 µm height were fabricated and characterized to verify the modeling results. X-ray diffraction (XRD) was used to measure the average stress distribution in the TSVs and to determine the stress-free temperature in the Cu. These parameters were used as inputs in the finite-element models for better accuracy. The TSV samples that were reliability tested by thermal shock from -55 °C to 125 °C for 4000 cycles showed both delamination of the Cu/SiO<sub>2</sub> interface and cracks in the SiO<sub>2</sub> liner (Figure 11). Liu also reported in a later publication [29] that a low modulus SU-8 polymer helped to improve the TSV reliability due to a "cushion effect" (Figure 12).

Figure 11. Interfacial crack around SiO<sub>2</sub> [25]

Figure 12. Cushion effect due to polymer material [29]

Cassidy [30] studied TSV reliability with blind vias of 250 µm depth and 100 µm diameter. The oxide liner thickness was 400 nm, and the conformally plated metal had a nominal thickness of 200 nm. Key parameters impacting the reliability, such as residual stress, leakage and dielectric breakdown, were discussed. It was reported that the residual stresses localize around the TSV sidewalls, leading to a high potential for failures. In addition, the thin oxide liner was susceptible to other problems such as leakage and dielectric breakdown. It was pointed out that the TSV sidewall defect density may be critical to the reliability of the TSVs.

From these published studies, it can be summarized that TSV failures in single-crystalline silicon are more likely to occur in or around the thin oxide liner, which remains as the primary concern for the reliability of TSV-based interposers.

### 2.1.3 TSV Fabrication in Single-crystalline Silicon Interposers

Traditional silicon interposers are based on single-crystalline silicon wafers and TSV interconnections (Figure 13 [31]). This section discusses the typical steps in TSV fabrication, including via formation, insulation liner fabrication and metallization, and summarizes the published work on silicon interposer integration.

Figure 13. Typical TSV fabrication process [31]

The ability to form through vias is the first and most essential step to convert the raw silicon material into a functional silicon interposer. The most common method for via hole formation is deep reactive-ion etching (DRIE), also called the Bosch process. However, this process suffers from scalloped profiles in the via sidewall, especially for high aspect ratio (HAR) TSVs. Therefore, a large body of research has focused on improving via profiles and increasing the aspect ratio of the vias. Knizikevicius [32] and Abhulimen [33] have reported that the etch anisotropy was improved by configuring the process parameters such as temperature and pressure. Blauw [34] developed an advanced time-multiplexed plasma etch process by adding a third step called de-passivation. Abdolvand [35] reported a similarly-etched via profiles using mixed Ar and O<sub>2</sub> plasma in the de-passivation step, and structures with aspect ratios as high as 40:1 were successfully demonstrated. However, the challenges in forming high aspect ratio TSVs at low cost remain, and through vias in silicon substrates beyond a certain thickness are not practical.

Because silicon is a semiconductor substrate, a dielectric insulation layer is necessary to electrically isolate the silicon via wall from the signals traveling in the filled Cu. SiO<sub>2</sub> is the most widely used insulator for TSVs, and it is typically deposited by using plasma-enhanced chemical vapor deposition (PECVD) at 500-800 ℃. In addition, a barrier layer is needed between the SiO<sub>2</sub> and plated copper to prevent the Cu from diffusing into SiO<sub>2</sub>. A number of studies have been conducted in the area of formation and characterization of diffusion barrier layers. Takeyama [36] compared Ti with TiN as barrier layers by using XRD and Auger electron spectroscopy, with the conclusion that TiN was better due to its stability after annealing at 850 °C. Lee [37] deposited TaN as the barrier layer by using an ionized metal plasma process, and found that it had a better barrier effect than traditional CVD (chemical vapor deposition) deposited TaN, since the plasma made the TaN structure more close-packed and consequently more resistant to Cu diffusion into SiO<sub>2</sub>. However, the results showed that diffusion induced failures happened at 900 °C, when a new compound Cu<sub>5</sub>Ta<sub>11</sub>O<sub>30</sub> was formed. Len [38] used Ti/TiN and Ta/TaN multi-layer structures as the barrier, and XRD, Atomic Force Microscopy (AFM) and Current-Voltage measurements were used to test the film stability. The results showed that the multi-layer structures had better performance than the single-barrier layers because of the additional diffusion blocking effect.

As discussed in sections 2.1.1 and 2.1.2, the thin SiO<sub>2</sub> liner layers are the major cause of the electrical and reliability problems. Therefore, studies have been carried out to replace the SiO<sub>2</sub> with polymer liners for their improved insulating properties. IMEC [39, 40] used spin-on polymer dielectrics to replace the traditional CVD oxide liner for TSVs with different heights. For TSVs with 50 µm height, the polymer liner was coated

in two Bosch-etched small trenches. The silicon core between the two trenches was then opened and etched in order to expose the polymer liner. For the TSVs with 100 µm height, a more traditional spin-on method was used for a conformal coating around the via sidewall. Improved electrical and reliability performance was observed with the polymer liner in these studies.

Metallization in TSV holes is necessary for electrical interconnections, and copper is the most widely used metal due to its high electrical conductivity. The metallization process usually consists of two major steps: Cu seed formation to create a conductive layer for current, and Cu electrolytic plating to the final thickness desired. Most of the recent studies have focused on the filling of copper in high aspect ratio vias by advanced electrolytic plating processes. Dixit [41] demonstrated completely void-free electroplating in 500 µm deep silicon, by continuously varying the current during the plating process to minimize void formation. TSV interconnections with aspect ratios as high as 15:1 were reported. Wolf [42] explored different seed layers to study their effects on high aspect ratio Cu filling in TSVs, and recommended a combination of CVD and sputtering processes as an improved approach to Cu seed layer formation.

By integrating the aforementioned processes, silicon interposers with TSVs and re-distribution layers have been fabricated and studied. Sunohara [43-45] built a TSV-based silicon interposer module with 200-300 µm thick single crystalline-silicon substrates by CMP (Chemical Mechanical Polishing) with fine line multilayer wiring. Good electrical performance of TSVs was reported with the use of high resistivity silicon substrates. Improved reliability of chip-to-interposer interconnections was reported, compared to organic interposers, due to better CTE matching of silicon chips to silicon

interposers. Rao [46] demonstrated silicon interposers with similar thicknesses and process flows, but used support wafer bonding and de-bonding processes to thin down the silicon substrate. Such interposers were fabricated for large dies and the TSV interconnections were reliability tested without any failures. Other published research has focused on thinner silicon interposers. Chaware [47] and Zoschke [48] reported the demonstration of 100 µm thick silicon interposers with TSV holes of 10 to 20 µm diameters. In order to achieve such thicknesses, carrier wafer bonding and de-bonding, and CMP processes were necessary to achieve good interposer yield.

In summary, published research on TSVs in traditional wafer silicon interposers highlighted the process complexity and cost challenges. Since interposers and packages require re-distribution wiring layers on both sides of the silicon core, the high cost and complexity of single-crystalline silicon wafer interposers form the basis for motivation of this research on panel-based, double-side polycrystalline silicon interposers with throughpackage-vias (TPVs).

## 2.2 Prior Art on Polycrystalline Silicon

Polycrystalline silicon panels have been widely used in the photovoltaic industry as the substrate for solar cell production. This section reviews the prior art in fabrication, laser drilling and characterization of polycrystalline silicon panels, that form the basis of this novel research on low cost and high performance silicon interposers.

The fabrication process and purity control of polycrystalline silicon are two main factors that control the performance and cost of polycrystalline silicon [49-52]. The solar-grade polycrystalline silicon is fabricated from metallurgical grade silicon, obtained by silicon oxide reduction with carbon. There are two ways to produce polycrystalline

silicon; a chemical route, using the gas-based Siemens process, and a metallurgical route by purifying directly from metallurgical grade silicon. Generally, the latter experiences much lower energy consumption and thus lower cost. Direct solidification is one of the metallurgical methods to produce polycrystalline silicon, which segregates the impurities in the melt, and polycrystalline silicon panels made by this method were used in this study.

Laser drilling in polycrystalline silicon has been used for wrap-through silicon solar cells. The drilled 50 µm diameter through-vias were used to contact the front and back sides of the panel. A variety of laser technologies have been implemented and high throughputs have been reported by controlling the laser parameters [53-56].

Since polycrystalline silicon is a brittle material, the processing and handling of polycrystalline silicon panels are recognized as an engineering challenge, especially for panels with thickness of 200-300 µm. Therefore, fundamental understanding of the fracture strength of polycrystalline silicon panels is very important. Four-point bending methods and the statistical method of Weibull plots were used to characterize the fracture strength of polycrystalline silicon panels [57-60]. These studies showed that the fracture strength was directly related to the defect density in the polycrystalline silicon panels.

# **CHAPTER 3**

## MODELING AND DESIGN OF TPVS

This chapter discusses electrical and mechanical modeling of TPVs in polycrystalline silicon interposers. Simulation results of TPVs are compared to TSVs in traditional single-crystalline silicon interposers. Parametric studies are also carried out. These investigations aim to provide solutions to address the electrical (lossy silicon substrate) and mechanical (CTE mismatch) challenges defined in Chapter 1. The analysis also targets to present design guidelines for TPV fabrication and test vehicle demonstration, which will be discussed in the following two chapters.

## 3.1 Electrical Modeling and Design of TPVs

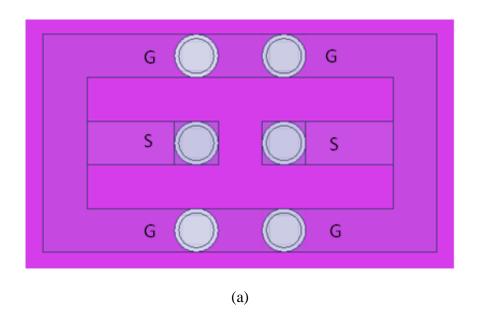

One of the fundamental challenges with polycrystalline silicon is its low resistivity (high conductivity), lower than single-crystalline silicon, due to low purity level resulting from the fabrication processes. This issue is proposed to be addressed by thick and low loss insulating polymer liner on the walls of TPV. To evaluate the effect of the thick polymer liner, in this section, the electrical performance of TPVs in polycrystalline silicon was simulated and compared to TSVs in single-crystalline silicon. The 3D electromagnetic software HFSS was used to simulate the through-via structure, as shown in Figure 14. The structure consists of two signal vias (marked as "S") and four ground vias (marked as "G"). Both insertion loss and crosstalk of the silicon via were generated from the model.

Figure 14. (a) Top view and (b) cross-section view of the GSG model

It has been previously reported [61] that the through-via capacitance and substrate conductance are two of the most critical factors impacting the electrical performance. Generally, lower via capacitance and lower substrate conductance are favorable for smaller insertion loss and crosstalk. The via capacitance is generally dominated by insulator capacitance and can be written as:

$$C_{insulator} = \varepsilon_{liner} \times \frac{2\pi h_{TV}}{\ln(\frac{r_{TV} + t_{liner}}{r_{TV}})}$$

(1)

where  $C_{insulator}$  is the capacitance of the insulation liner,  $\varepsilon_{liner}$  is the dielectric constant of the insulation liner,  $h_{TV}$  is the height of the via,  $r_{TV}$  is the radius of the via, and  $t_{liner}$  is the thickness of the insulation liner. It can be seen from the equation that the electrical properties and thickness of the liner impact the via capacitance and thus the electrical performance. On the other hand, the conductance of the silicon substrate is governed by following equation:

$$G_{Si\_sub} = \frac{\pi \times \sigma_{Si} \times h_{TV}}{\cosh^{-1}(\frac{p_{TV}}{d_{TV}})}$$

(2)

where  $G_{Si\_sub}$  is the conductance of the silicon substrate,  $\sigma_{Si}$  is the conductivity of the silicon,  $h_{TV}$  is the height of the via,  $p_{TV}$  is the pitch of the via and  $d_{TV}$  is the diameter of the via. The physical origin of substrate conductance is the conductivity of silicon material, which can greatly affect the electrical performance.

Therefore, in this section, through-vias with silicon substrates of different conductivity (resistivity) and with different types of liners are simulated. Parametric study has also been carried out for the thickness of in-via liner.

# 3.1.1 Electrical Performance Comparison between TPV and TSV

A typical 10  $\Omega$ -cm silicon material with SiO<sub>2</sub> liner was used as an example for TSV in single-crystalline silicon interposer while a much lower, 0.5  $\Omega$ -cm silicon, with thick and low electrical loss polymer liner (tan $\delta$ =0.002) was used for TPV in polycrystalline silicon interposer. The key parameters used in the simulation are listed in Table 3.

Table 3. Key parameters for electrical modeling

| Parameters                   | TSV in traditional silicon | TPV in polycrystalline |  |

|------------------------------|----------------------------|------------------------|--|

|                              | interposer                 | silicon interposer     |  |

| Substrate thickness(µm)      | 200 μm                     | 200 μm                 |  |

| Via diameter size(μm)        | 30 μm                      | 30 μm                  |  |

| In-via liner thickness(μm)   | 1 μm SiO <sub>2</sub>      | 3 μm polymer           |  |

| Surface liner thickness( µm) | 1 μm SiO <sub>2</sub>      | 3 μm polymer           |  |

| Substrate Resistivity        | 10 Ω-cm                    | 0.5 Ω-cm               |  |

| Liner dielectric constant    | 4                          | 3.1                    |  |

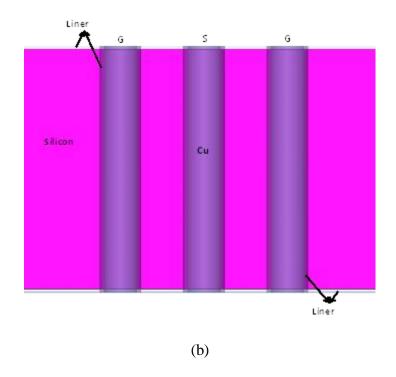

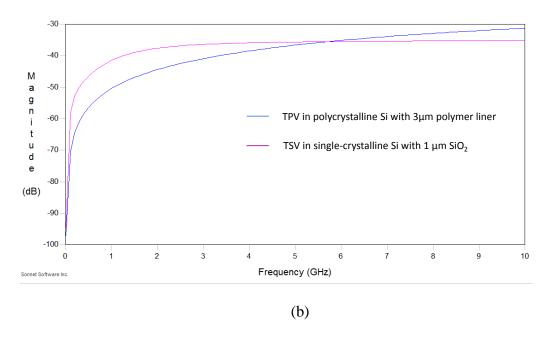

Figure 15 compares the insertion loss and FEXT (far end crosstalk) between TPV and TSV. It can be observed that TPV in polycrystalline silicon interposer shows lower insertion loss up to 10 GHz and crosstalk up to 6 GHz. The superior electrical performance of TPV is attributed to the thick insulating polymer liner. This helps reduce the electrical loss and coupling in the silicon substrate.

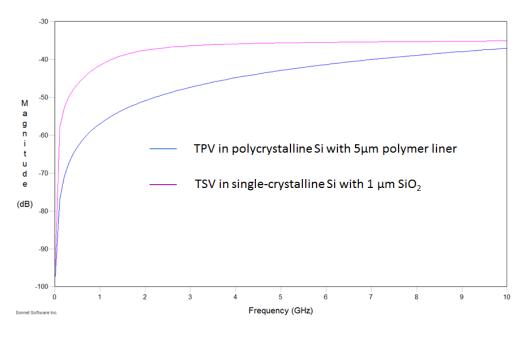

However, it can also be observed that, as the frequency increases, the crosstalk tends to increase a lot for TPV and is worse than TSV at higher frequency, as shown in Figure 15(b). This is because the coupling of TPV increases with frequency, primarily decided by substrate conductance at high frequency. Hence, the lower crosstalk of TPV, due to thick polymer, starts to be offset because of high conductivity of the polycrystalline silicon substrate. TPVs designed with even thicker polymer liners help to maintain a better crosstalk for TPV over TSV at higher frequency, as shown in Figure 16 with 5 µm liner.

Figure 15. (a) Insertion loss and (b) FEXT plots for TPV in polycrystalline silicon interposer (3 µm liner) and TSV in single-crystalline silicon interposer

Figure 16. FEXT plots for TPV in polycrystalline silicon interposer (5 µm liner) and TSV in single-crystalline silicon interposer

## 3.1.2 Effect of Sidewall Liner Thickness

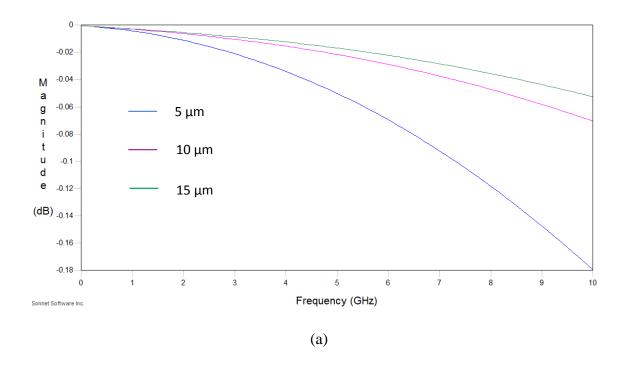

The parametric study of in-via liner thickness is necessary since it can provide important design guidelines for TPV. The effect of the sidewall liner thickness (5  $\mu$ m, 10  $\mu$ m and 15  $\mu$ m) on the insertion loss and crosstalk in TPVs is studied in Figure 17. The TPV diameter and pitch were 30  $\mu$ m (diameter of the Cu filled region) and 120  $\mu$ m respectively. The silicon substrate resistivity and thickness were 0.5  $\Omega$ -cm and 200  $\mu$ m respectively. It is seen from Figure 17 that the insertion loss and crosstalk can be reduced by using a thicker in-via liner. This is because, as the thickness increases, the capacitance of TSV decreases, resulting in lower insertion loss and crosstalk.

Figure 17. (a) Insertion loss and (b) FEXT plots for TPV with different in-via liner thickness

# 3.1.3 Design Guidelines for Electrical Consideration

It has been shown by electrical simulations that the thick polymer liner is effective in addressing the fundamental challenge of low resistivity for the polycrystalline silicon material. As the results show, a polymer liner as thin as 3 µm is able to maintain better insertion loss up to 10 GHz and crosstalk up to 6 GHz for TPV than TSV with 1 µm SiO<sub>2</sub>. However as the frequency increases such positive effect on crosstalk is compromised by the low resistivity of the silicon substrate. Therefore, to address this problem, a liner thicker than 5 µm is recommended.

## 3.2 Mechanical Modeling and Design of TPVs

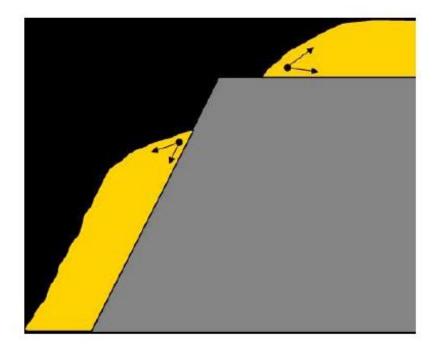

Another fundamental challenge with TPV in polycrystalline silicon is the difference in CTE between silicon and Cu. Such CTE mismatch, in combination with

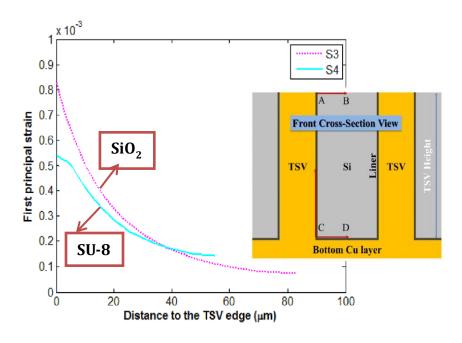

temperature change, will lead to stress localization and finally reliability problems. The polymer liner, introduced to provide insulation for electrical purpose, can also improve TPV reliability due to its low modulus. The thick polymer liner tends to play the role as "cushion" during thermal attack to buffer the stresses in the TPV system. In this part, Finite Element (FE) modeling was performed using Ansys to simulate proposed TPV structure with polymer liner in comparison to TSV with thin SiO<sub>2</sub> liner. Both interfacial shear stresses and first principal stresses in silicon due to thermal loading were generated and analyzed. As is the case with electrical modeling, parametric studies were also performed with in-via liner thickness.

# 3.2.1 Stress Comparison between TPV and TSV

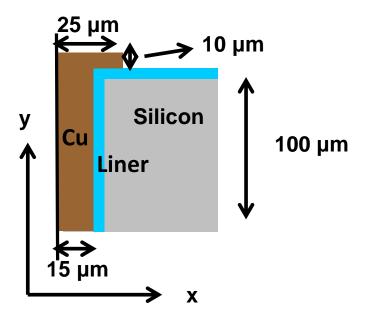

A two-dimensional axisymmetric model was built in Ansys to simulate the stress in TPV and TSV. The schematic cross-section (1/4 via) is presented in Figure 18 with geometry values. The Cu via size was 30  $\mu$ m with a height of 200  $\mu$ m. The diameter of the pad was 50  $\mu$ m and the thickness was 10  $\mu$ m. The liner thickness varied for different cases.

Figure 18. Schematic cross-section drawing of TPV for mechanical modeling

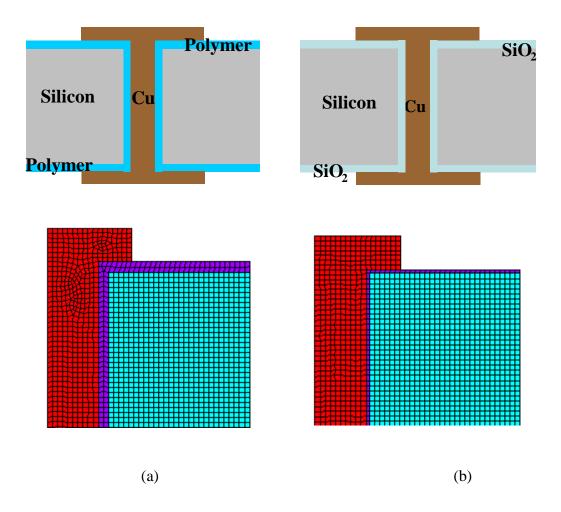

Figure 19 compares the schematic cross-section and meshed models for TPV and TSV. In this study, TPV was simulated with 3  $\mu$ m thick polymer liner on top and bottom surfaces and 3  $\mu$ m thick via sidewall liner compared with 1  $\mu$ m thick SiO<sub>2</sub> liner on top and bottom surfaces of silicon and 1  $\mu$ m thick via sidewall liner for TSV. The effect of the very thin diffusion barrier was neglected in TSV modeling.

Figure 19. Schematic cross-section drawings and meshed models for (a) TPV and (b) TSV

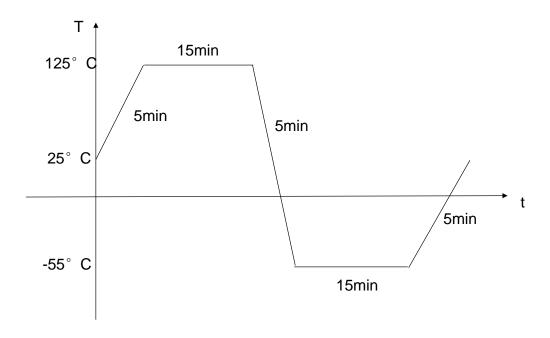

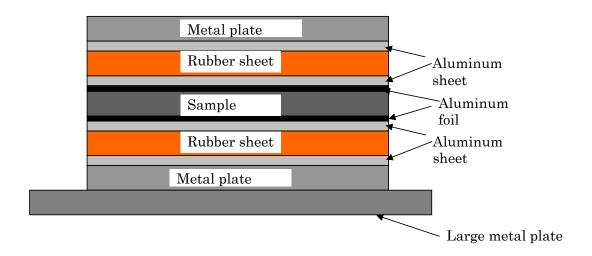

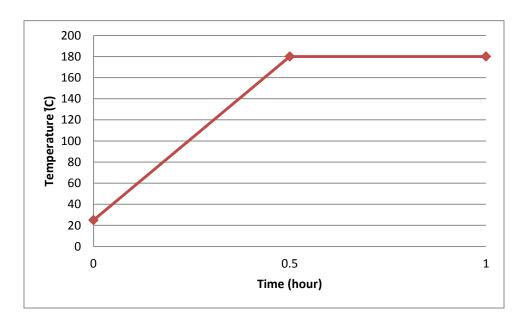

The material properties used in the simulations are given in Table 4 and Table 5. The polymer presents much lower modulus than  $SiO_2$ . The non-linear model of Cu was used based on our previous studies. A standard thermal load cycle of -55  $^{\circ}$ C to 125  $^{\circ}$ C (Figure 20) was used in the analysis with dwelling time of 15 minutes at both extreme temperatures.

Table 4 Material properties used in mechanical modeling

|                            | Young's Modulus | Poisson's | CTE     | Stress free      |

|----------------------------|-----------------|-----------|---------|------------------|

|                            | (GPa)           | Ratio     | (ppm/℃) | Temperature (°C) |

| Single-                    | 169             | 0.28      | 2.6     | 25               |

| crystalline<br>Silicon[62] |                 |           |         |                  |

| Poly-Silicon[62]           | 161             | 0.26      | 2.4     | 25               |

| G:0 F2.47                  | 51.4            | 0.16      | 0.5     | 250              |

| SiO <sub>2</sub> [24]      | 71.4            | 0.16      | 0.5     | 250              |

| Polymer[63]                | 6.9             | 0.3       | 31      | 180              |

| Copper[24]                 | Table 5[24]     | 0.3       | 17.3    | 25               |

|                            |                 |           |         |                  |

Table 5 Cu properties used in mechanical modeling

| Temperature ( $^{\circ}$ C)                                                                      | 27           | 38     | 95     | 149    | 204    | 260    |

|--------------------------------------------------------------------------------------------------|--------------|--------|--------|--------|--------|--------|

|                                                                                                  |              |        |        |        |        |        |

| Young's Modulus                                                                                  | 121.00       | 120.48 | 117.88 | 115.24 | 112.64 | 110.00 |

| (GPa)                                                                                            |              |        |        |        |        |        |

| Temperature ( $^{\circ}\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!$ | 27           |        |        |        |        |        |

| Plastic Curve                                                                                    | 121@ 0.001ε  |        |        |        |        |        |

| -stress (MPa) vs.                                                                                | 186@ 0.004 ε |        |        |        |        |        |

| strain                                                                                           | 217@ 0.01 ε  |        |        |        |        |        |

|                                                                                                  | 234@ 0.02 ε  |        |        |        |        |        |

|                                                                                                  | 248@ 0.04 ε  |        |        |        |        |        |

Figure 20. Thermal loading curve for mechanical modeling

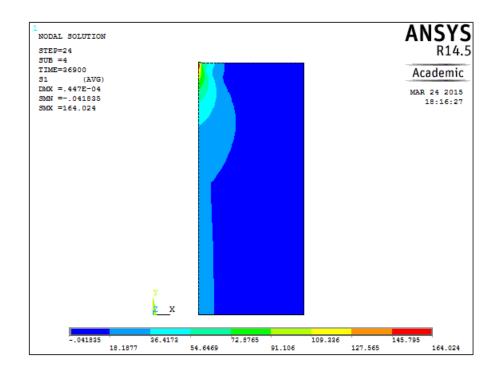

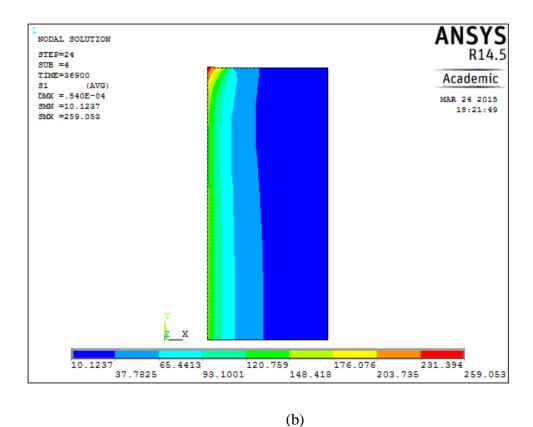

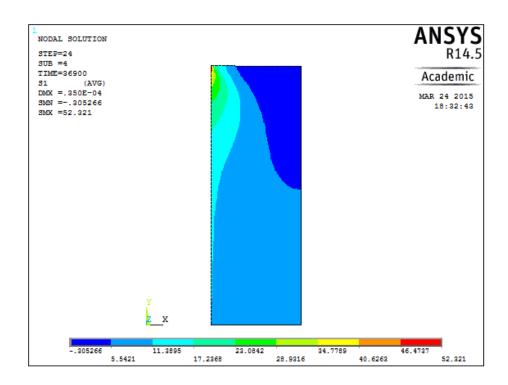

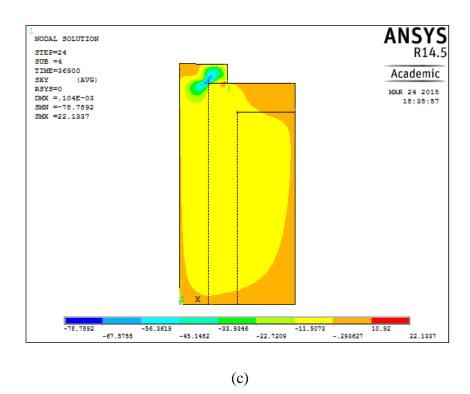

Figure 21 compares the first principal stress in TPV and TSV at  $125\,^{\circ}$ C. It can be observed that the first principal stress in silicon is significantly reduced in TPV (164 MPa) compared to TSV (259 MPa). This is due to the low modulus and "cushion" effect of the polymer material. The much smaller stress in TPV can mitigate the possibility of failures.

(a)

Figure 21. First principal stress in silicon for (a) TPV and (b) TSV at  $125\,^{\circ}\mathrm{C}$

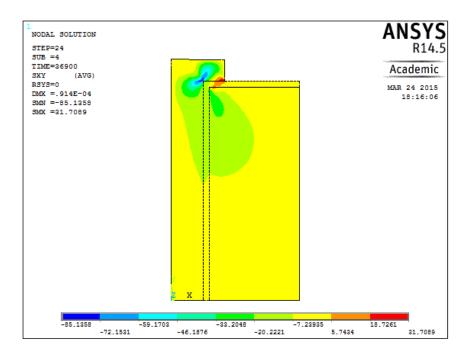

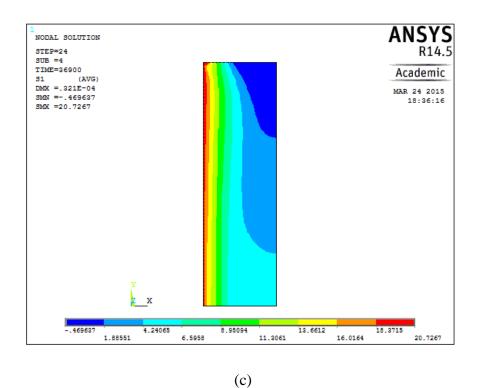

Similarly, Figure 22 illustrates the shear stress in TPV and TSV at  $125\,^{\circ}$ C. It can be concluded that shear stress localization occurs at the interfaces of different materials, such as Cu/liner and silicon/liner joints. As expected, TSV shows larger (137 MPa) shear stress than TPV (85 MPa). The relatively higher interfacial shear stress localization in TSV structures can be attributed to the higher CTE mismatch of  $SiO_2$  with Cu vias. This makes it more susceptible to interfacial failures compared to TPV structures.

Based on the discussions above, thick polymer liners in TPV act as buffer layers and can reduce the risk of failures. On the other hand, TSV shows higher stress in spite of the thinner layer of SiO<sub>2</sub>. Furthermore, due to higher stiffness of SiO<sub>2</sub>, the TSV structures are more prone to cohesive cracks in liners compared to TPV structures. It is also expected that TSV structures would experience additional stresses during the backgrinding processes required for fabricating these structures.

(a)

(b)

Figure 22. Shear stress in (a) TPV and (b) TSV at 125  $^{\circ}\mathrm{C}$

#### 3.2.2 Effect of Sidewall Liner Thickness

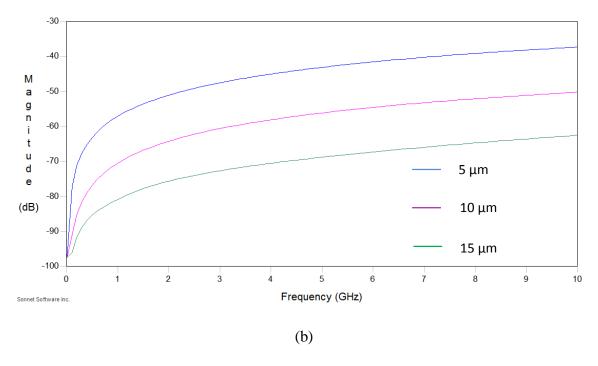

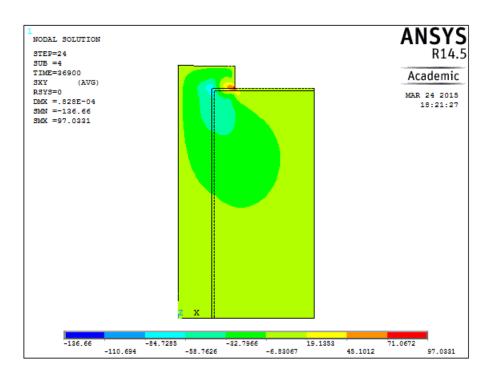

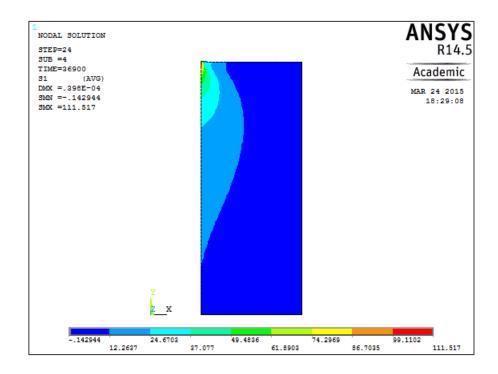

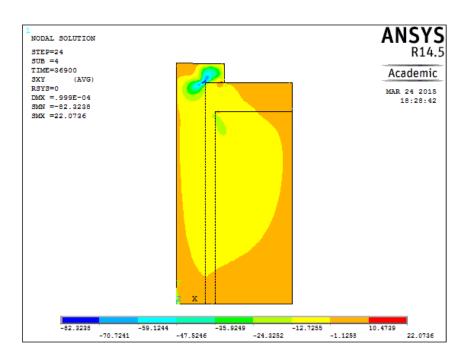

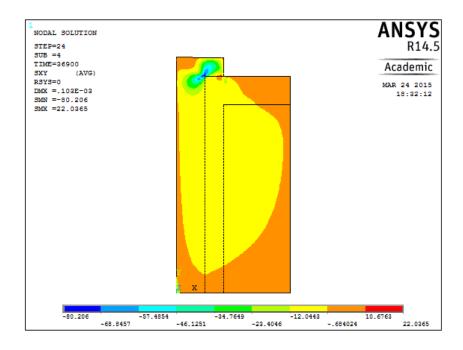

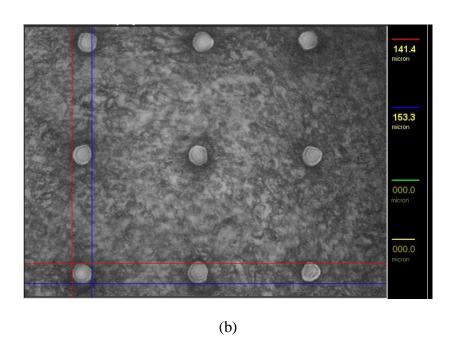

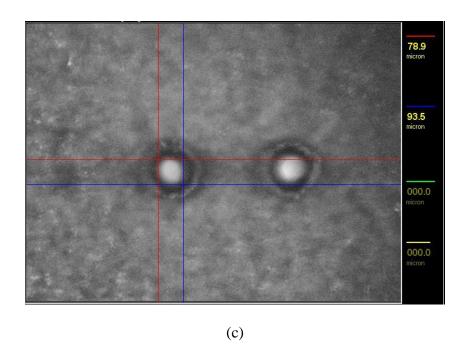

It has been shown that thicker sidewall liners help to improve the electrical performance of TPVs. This section investigates the effect of the in-via liner thickness on the first principal stress and shear stress in TPVs. Three different cases, with 5 μm, 10 μm and 15 μm in-via liners were studied and compared. The substrate thickness was 200 μm and the diameter of the via (Cu filled) was 30 μm. The surface liner was 15 μm thick. As the contour plots presented in Figure 23, when the liner becomes thicker (5 μm, 10 μm and 15 μm) the first principal stress at 125 °C gradually decreases (111 MPa, 52 MPa and 21 MPa). Hence, at elevated temperature, larger polymer liner thicknesses absorb the stresses more effectively and lead to less first principal stresses in silicon and thus less risk of cohesive cracking in the substrate. It can also be summarized from Figure 24 that the shear stresses for TPV are 82 MPa, 80 MPa and 79 MPa for TPVs with 5 μm, 10 μm and 15 μm liners, respectively. As expected, the shear stresses localize at material interfaces and larger liner thicknesses help also to reduce the shear stresses, thus leading to a smaller possibility of interfacial failures.

(a)

(b)

Figure 23. First principal stress in Si for TPV with sidewall liner thickness of (a) 5  $\mu$ m, (b) 10  $\mu$ m and (c) 15  $\mu$ m at 125  $^{\circ}$ C

(a)

(b)

Figure 24. Shear stress in TPV with sidewall liner thickness of (a) 5  $\,\mu m$  , (b) 10  $\,\mu m$  and (c) 15  $\,\mu m$  at 125  $^{\circ}{\rm C}$

# 3.2.3 Design Guidelines for Mechanical Consideration

The first principal stress in Si and shear stress in TPVs at 125 °C for different liner types and thicknesses are summarized in Table 6. It can be observed that the introduction of thick polymer liners can greatly lower the stress by acting as "cushion" layer due to the low modulus. This enables improved mechanical stability of TPVs than TSVs. These investigations also suggest that thicker sidewall liners can help to mitigate the possibility of failures. Generally, TPVs with a sidewall liner more than 10 μm should be able to experience good reliability under thermal attack.

Table 6 Summary of stresses for different liner types and sidewall liner thicknesses

| Sidewall Liner                                              | First principal stress in Si (MPa, 125 °C) | Shear stress (MPa, 125 ℃) |

|-------------------------------------------------------------|--------------------------------------------|---------------------------|

| 1 μm SiO <sub>2</sub> (1 μm SiO <sub>2</sub> surface liner) | 259                                        | 137                       |

| 3 μm polymer (3 μm polymer surface liner)                   | 164                                        | 85                        |

| 5 μm polymer (15 μm polymer surface liner)                  | 111                                        | 82                        |