**ADVERTIMENT**. La consulta d'aquesta tesi queda condicionada a l'acceptació de les següents condicions d'ús: La difusió d'aquesta tesi per mitjà del servei TDX (<a href="www.tesisenxarxa.net">www.tesisenxarxa.net</a>) ha estat autoritzada pels titulars dels drets de propietat intel·lectual únicament per a usos privats emmarcats en activitats d'investigació i docència. No s'autoritza la seva reproducció amb finalitats de lucre ni la seva difusió i posada a disposició des d'un lloc aliè al servei TDX. No s'autoritza la presentació del seu contingut en una finestra o marc aliè a TDX (framing). Aquesta reserva de drets afecta tant al resum de presentació de la tesi com als seus continguts. En la utilització o cita de parts de la tesi és obligat indicar el nom de la persona autora.

**ADVERTENCIA**. La consulta de esta tesis queda condicionada a la aceptación de las siguientes condiciones de uso: La difusión de esta tesis por medio del servicio TDR (<a href="www.tesisenred.net">www.tesisenred.net</a>) ha sido autorizada por los titulares de los derechos de propiedad intelectual únicamente para usos privados enmarcados en actividades de investigación y docencia. No se autoriza su reproducción con finalidades de lucro ni su difusión y puesta a disposición desde un sitio ajeno al servicio TDR. No se autoriza la presentación de su contenido en una ventana o marco ajeno a TDR (framing). Esta reserva de derechos afecta tanto al resumen de presentación de la tesis como a sus contenidos. En la utilización o cita de partes de la tesis es obligado indicar el nombre de la persona autora.

**WARNING**. On having consulted this thesis you're accepting the following use conditions: Spreading this thesis by the TDX (<a href="www.tesisenxarxa.net">www.tesisenxarxa.net</a>) service has been authorized by the titular of the intellectual property rights only for private uses placed in investigation and teaching activities. Reproduction with lucrative aims is not authorized neither its spreading and availability from a site foreign to the TDX service. Introducing its content in a window or frame foreign to the TDX service is not authorized (framing). This rights affect to the presentation summary of the thesis as well as to its contents. In the using or citation of parts of the thesis it's obliged to indicate the name of the author

# MPI Layer Techniques to Improve Network Energy Efficiency

a dissertation presented by Branimir Dickov to

The Department of Computer Architecture

IN PARTIAL FULFILLMENT OF THE REQUIREMENTS

FOR THE DEGREE OF

DOCTOR OF PHILOSOPHY

IN THE SUBJECT OF

COMPUTER SCIENCE

Universitat Politècnica de Catalunya Barcelona, Spain December 2015 ©2015 – Branimir Dickov all rights reserved. Author: Branimir Dickov

Thesis director: Professor Eduard Ayguadé

Thesis co-directors: Paul Carpenter and Miquel Pericàs

#### MPI Layer Techniques to Improve Network Energy Efficiency

#### ABSTRACT

Interconnection networks represent the backbone of large-scale parallel systems. In order to build ultra-scale supercomputers larger interconnection networks are being designed and deployed. As compute nodes become more energy-efficient, the interconnect is accounting for an increasing proportion of the total system energy consumption. The interconnect's energy consumption is, however, only starting to receive serious attention. Most of this power consumption is due to the interconnection links. The problem, in terms of power, of an interconnect link is that its power consumption is almost constant, whether or not it is actively exchanging data, since both ends stay active to mantain synchronization.

This thesis complements ongoing efforts related to power reduction and energy proportionality of the interconnection network. The thesis contemplates two directions for power savings in the interconnection network; one is the possibility to use lower bandwidth links during the communication phases and thus save energy, while the second one addresses shifting links to low-power mode during computation phases when they are unused. To address the first one we investigate the potential benefits from MPI data compression. When compression of MPI data is possible, the reduction in link bandwidth is enabled without incurring any performance penalty. Consecutively, lower bandwidth leads to lower link energy consumption. In the past, several compression techniques have been proposed as a way to improve the performance and scalability of parallel applications. Those works have shown significant speed-ups when applying compressors to the MPI transfers of certain algorithmic kernels. However, these techniques have not seen widespread adoptation in current supercomputers.

In this thesis we will show that although data compression naturally leads to improved performance, the benefit is small, for modern high-performance networks, and it varies greatly between applications. In contrast, combining data compression with switching to low-power mode preserves performance while delivering effective and consistent energy savings, in proportion with the reduction in data rate. In general, application developers view time spent in a communication as an overhead, and therefore strive to keep it at minimum. This leads to high peak bandwidth demand and latency sensitivity, but low average utilization, which provides significant opportunities for energy savings. It

Author: Branimir Dickov

Thesis director: Professor Eduard Ayguadé

Thesis co-directors: Paul Carpenter and Miquel Pericàs

is therefore possible to save energy using low-power modes, but link wake-up latencies must not lead to a loss in performance. Thus, we propose a mechanism that can accurately predict when links are idle, allowing them to be switched to more power efficient mode. Our runtime system called the Pattern Prediction System (PPS) can accurately predict not only when a link will become unused but also when it will become active again, allowing links to be switched off during the idle periods and switched back on again in time to avoid incurring a significant performance degradation. Many HPC application benefit from prediction, since they have repetitive computation and communication phases. By implementing the energy-saving mechanisms inside the MPI library, existing MPI programs do not need to be modified. We also develop more advanced version of the prediction system, Self-Tuned Pattern Prediction System (SPPS) which is capable of automatically tuning to the current application communication characteristic and shaping the switching on/off of the links in the most appropriate way.

The proposed compression and prediction techniques are evaluated using an event-driven simulator, which is able to replay the traces from real execution of MPI applications. Experimental results show significant energy savings in the IB links while the performance overhead due to wake-up latencies and additional computation time have negligible effects on the final application performance.

# Contents

| Ι | Int                                                     | RODUCTION                                                   | I  |

|---|---------------------------------------------------------|-------------------------------------------------------------|----|

| 2 | Background                                              |                                                             |    |

|   | 2.I                                                     | System Area Network (SAN) - Interconnection Network for HPC | 7  |

|   | 2.2                                                     | Communication in Parallel Programs                          | 8  |

|   | 2.3                                                     | Data Compression                                            | Ю  |

|   | 2.4                                                     | Interconnection Network Power Consumption                   | 13 |

|   | 2.5                                                     | Power-saving Support in Interconnection Network Links       | 13 |

|   | 2.6                                                     | InfiniBand technology                                       | 14 |

| 3 | Exp                                                     | erimental Methodology                                       | 17 |

|   | 3.1                                                     | TestBed platforms                                           | 17 |

|   | 3.2                                                     | HPC workloads                                               | 18 |

|   | 3.3                                                     | Extrae - Tracing Tool                                       | 20 |

|   | 3.4                                                     | Paraver - Visualization Tool                                | 21 |

|   | 3.5                                                     | Dimemas - MPI simulator                                     | 22 |

|   | 3.6                                                     | Venus - Network Simulator                                   | 23 |

| 4 | Enhancing Network Efficiency Using MPI Data Compression |                                                             |    |

|   | 4.I                                                     | Motivation for MPI message compression                      | 27 |

|   | 4.2                                                     | Evaluation of Performance Benefits                          | 29 |

|   | 4.3                                                     | Real Machine Tests                                          | 30 |

|   | 4.4                                                     | Simulation Tests                                            | 47 |

|   | 4.5                                                     | Data compression for Network Energy Savings                 | 57 |

|   | 4.6                                                     | Conclusions                                                 | 65 |

| 5  | Runtime Software-Managed Power Savings in IB Links | 67   |

|----|----------------------------------------------------|------|

|    | 5.1 Motivation                                     | 67   |

|    | 5.2 Pattern Prediction System                      | 69   |

|    | 5.3 Self-Tuned Pattern Prediction System           | 89   |

|    | 5.4 Conclusions                                    | 99   |

| 6  | Related Work                                       | 103  |

| 7  | Conclusion                                         | 109  |

| 8  | Future Work                                        | 113  |

| 9  | Publications                                       | 115  |

| Rε | FFFRENCES                                          | 12.2 |

# Listing of figures

| I.I          | System stack architecture with our proposals in MPI layer                              | 5   |

|--------------|----------------------------------------------------------------------------------------|-----|

| 2.I          | Communication path in a large-scale interconnected system                              | 8   |

| 2.2          | GROMACS execution trace                                                                | Ю   |

| 3.I          | Tracing scripts for GROMACS application                                                | 2.1 |

| 3.2          | Dimemas parameters used to simulate GROMACS application                                | 22  |

| 3.3          | Task-to-nodes mapping in Dimemas and Venus                                             | 24  |

| 3.4          | Dimemas & Venus co-simulation toolchain                                                | 24  |

| 4.I          | Parallel scaling of CG and PME kernel on IBM compute cluster machine                   | 28  |

| 4.2          | MPI_Sendrecv latency on IBM J21 Myrinet cluster                                        | 28  |

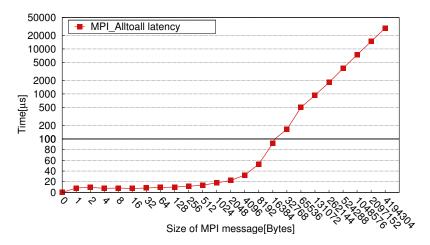

| 4.3          | MPI_Alltoall latency on IBM J21 Myrinet cluster                                        | 29  |

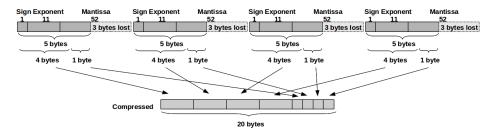

| 4.4          | Packing algorithm <sup>2</sup> for doubles when reduction to 5 bytes is chosen         | 32  |

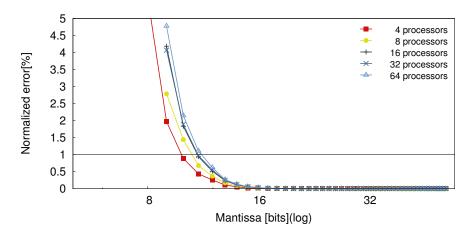

| 4.5          | Normalized error as a function of size of mantissa in SMVM communication               | 34  |

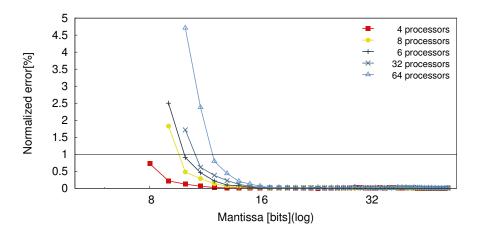

| 4.6          | Normalized error as a function of size of mantissa in SMVM communication               | 34  |

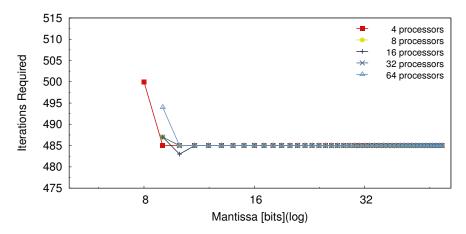

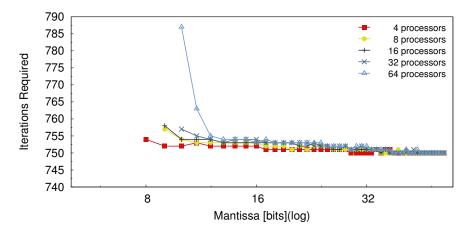

| 4.7          | Iterations Required as size of mantissa in SMVM communication                          | 35  |

| 4.8          | Iterations Required as size of mantissa in SMVM communication                          | 35  |

| 4.9          | Profile of Alya CG <i>Input A</i> kernel with 1 process per node                       | 36  |

| <b>4.</b> IO | Profile of Alya CG <i>Input B</i> kernel with 1 process per node                       | 37  |

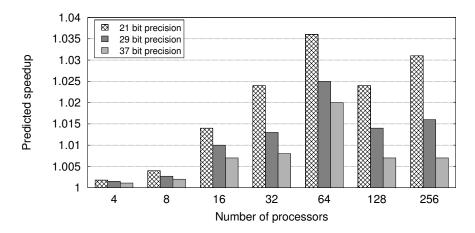

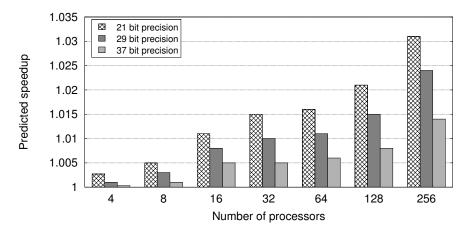

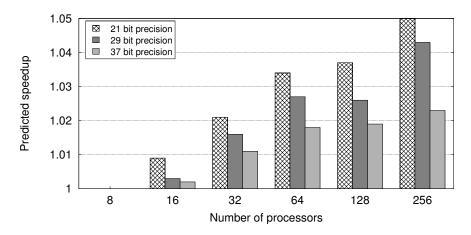

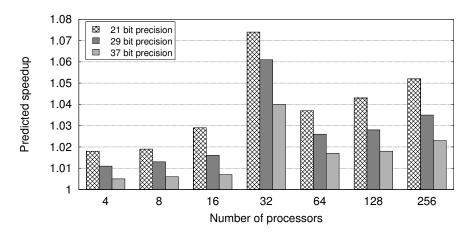

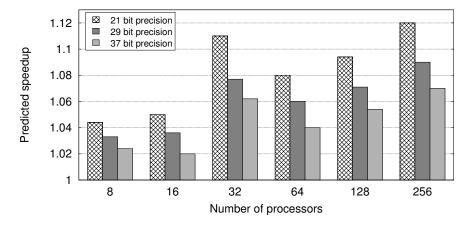

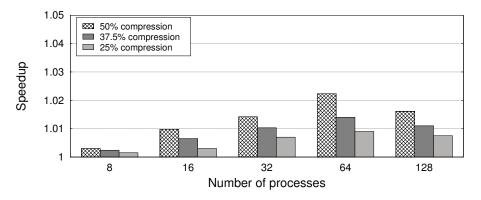

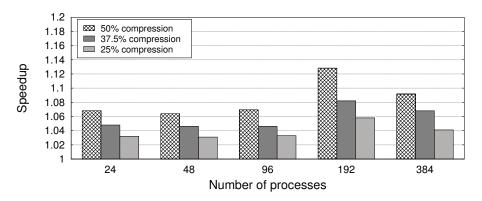

| 4.II         | Speedup factors for $Input\ A$ achieved applying lossy compression on MPI messages     |     |

|              | in SMVM part of CG with 1 process per node                                             | 38  |

| 4.I2         | Speedup factors for <i>Input B</i> achieved applying lossy compression on MPI messages |     |

|              | in SMVM part of CG with 1 process per node                                             | 38  |

| 4.13         | Profile of Alya CG $Input\ A$ kernel with 4 processes per node                         | 39  |

| 4.I4         | Profile of Alya CG <i>Input B</i> kernel with 4 processes per node                     | 39  |

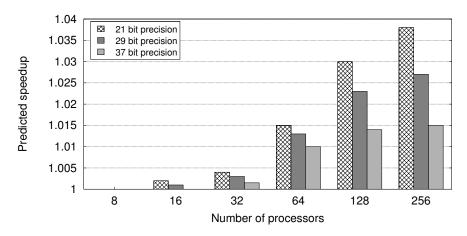

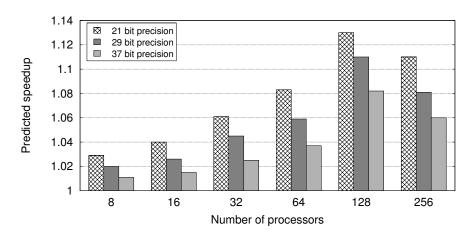

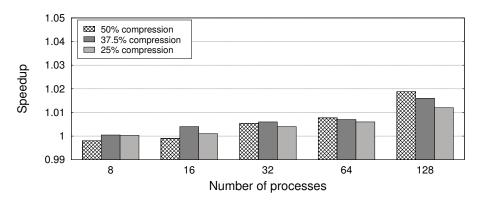

| 4.15 | Speedup factors for $Input A$ achieved applying lossy compression on MPI messages           |    |

|------|---------------------------------------------------------------------------------------------|----|

|      | in SMVM part of CG with 4 processes per node                                                | 40 |

| 4.16 | Speedup factors for <i>Input B</i> achieved applying lossy compression on MPI messages      |    |

|      | in SMVM part of CG with 4 processes per node                                                | 40 |

| 4.I7 | Profile of Gromacs PME <i>Input A</i> kernel with 1 process per node                        | 43 |

| 4.18 | Profile of Gromacs PME <i>Input B</i> kernel with 1 process per node                        | 43 |

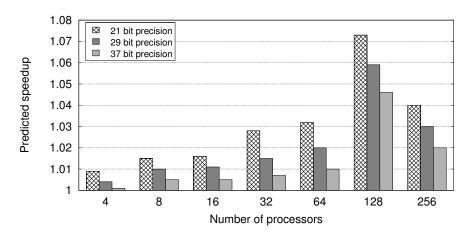

| 4.19 | Speedup factors for $\mathit{Input}\ A$ achieved applying lossy compression on MPI messages |    |

|      | in 3DFFT part of PME kernel with 1 process per node                                         | 44 |

| 4.20 | Speedup factors for <i>Input B</i> achieved applying lossy compression on MPI messages      |    |

|      | in 3DFFT part of PME kernel with 1 process per node                                         | 44 |

| 4.2I | Profile of Gromacs PME <i>Input A</i> kernel with 4 processes per node                      | 45 |

| 4.22 | Profile of Gromacs PME kernel <i>Input B</i> with 4 processes per node                      | 46 |

| 4.23 | Speedup factors for $\mathit{Input}\ A$ achieved applying lossy compression on MPI messages |    |

|      | in the 3DFFT part of the PME kernel with 4 processes per node                               | 46 |

| 4.24 | Speedup factors for <i>Input B</i> achieved applying lossy compression on MPI messages      |    |

|      | in the 3DFFT part of the PME kernel with 4 processes per node                               | 47 |

| 4.25 | Profile of the Alya CG <i>Input A</i> kernel - 1 MPI process per node                       | 50 |

| 4.26 | Profile of the Alya CG <i>Input B</i> kernel - 6 MPI procecesses per node                   | 50 |

| 4.27 | Speedup factors for $Input\ A$ from applying lossy compression on MPI messages in           |    |

|      | SMVM kernel of CG with 1 MPI processes per node                                             | 51 |

| 4.28 | Speedup factors for <i>Input B</i> from applying lossy compression on MPI messages in       |    |

|      | SMVM kernel of CG with 1 MPI processes per node                                             | 51 |

| 4.29 | Speedup factors for $Input\ A$ from applying lossy compression on MPI messages in           |    |

|      | SMVM kernel of CG with 6 processes per node                                                 | 52 |

| 4.30 | Speedup factors for <i>Input B</i> from applying lossy compression on MPI messages in       |    |

|      | SMVM kernel of CG with 6 processes per node                                                 | 53 |

| 4.3I | Profile of Gromacs PME <i>Input A</i> kernel                                                | 54 |

| 4.32 | Profile of Gromacs PME <i>Input B</i> kernel                                                | 54 |

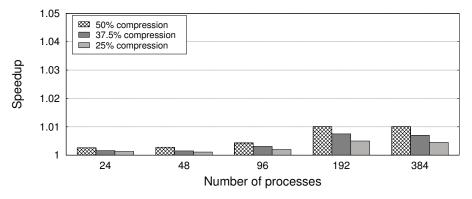

| 4.33 | Speedup factors for $Input\ \mathcal{A}$ from applying lossy compression on MPI messages in |    |

|      | the 3D FFT part of PME with one MPI process per node                                        | 55 |

| 4.34 | Speedup factors for <i>Input B</i> from applying lossy compression on MPI messages in       |    |

|      | the 3D FFT part of PME with one MPI process per node                                        | 55 |

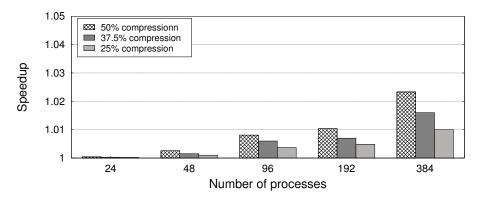

| 4.35 | Speedup factors for $Input\ A$ from applying lossy compression on MPI messages in           |    |

|      | the 3D FFT part of the PME kernel with six MPI processes per node                           | 56 |

|      |                                                                                             |    |

| 4.36 | Speedup factors for <i>Input B</i> from applying lossy compression on MPI messages in the 3D FFT part of the PME kernel with six MPI processes per node         | 56         |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|

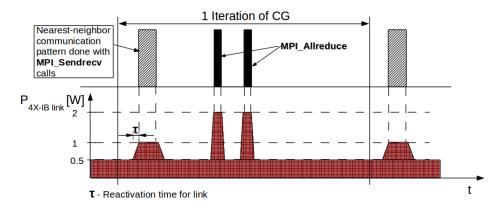

| 4.37 | Traces showing whether Alya CG kernel is in the application or MPI library (grey or black). The lower traces show 4X-IB link power using the proposed technique | 59         |

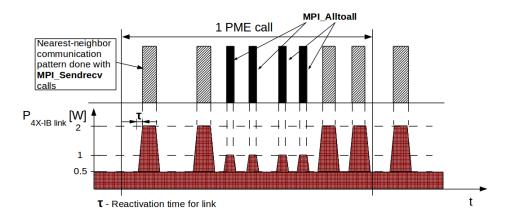

| 4.38 | Traces showing whether Gromacs PME kernel is in the application or MPI library                                                                                  |            |

|      | (grey or black). The lower traces show $4X$ -IB link power using the proposed technique                                                                         | 60         |

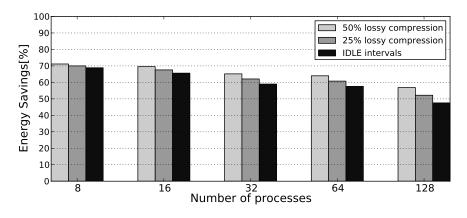

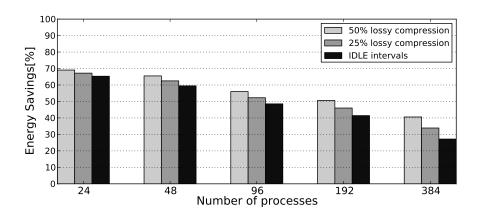

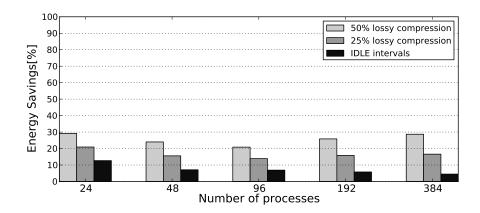

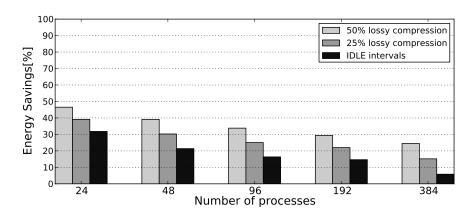

| 4.39 | IB edge switch link energy savings for Alya CG kernel for one MPI process per node with $Input\ A$                                                              | 60         |

| 4.40 | IB edge switch link energy savings for Alya CG kernel for one MPI process per node                                                                              |            |

|      | with Input B                                                                                                                                                    | 61         |

| 4.4I | IB edge switch link energy savings for Gromacs PME kernel for one MPI process per                                                                               |            |

|      | node with Input A                                                                                                                                               | 61         |

| 4.42 | IB edge switch link energy savings for Gromacs PME kernel for one MPI process per node with <i>Input B</i>                                                      | 62         |

| 4.43 | IB edge switch link energy savings for Alya CG kernel for six MPI processes per node                                                                            |            |

|      | with Input A                                                                                                                                                    | 62         |

| 4.44 | IB edge switch link energy savings for Alya CG kernel for six MPI processes per node with <i>Input B</i>                                                        | 63         |

| 4.45 | IB edge switch link energy savings for Gromacs PME kernel for six MPI processes per node with $Input\ A$                                                        | 63         |

| 4.46 | IB edge switch link energy savings for Gromacs PME kernel for six MPI processes                                                                                 | <i>c</i> , |

| 7.7. | per node with $Input B$                                                                                                                                         | 64         |

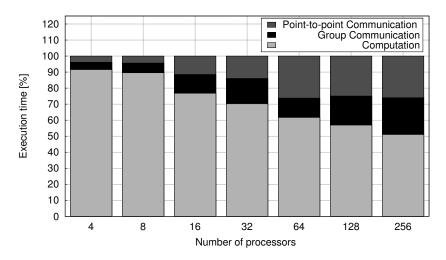

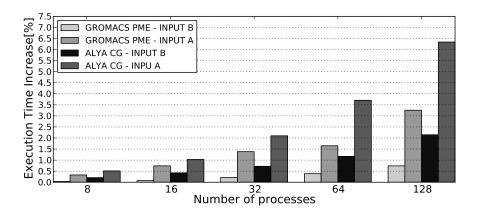

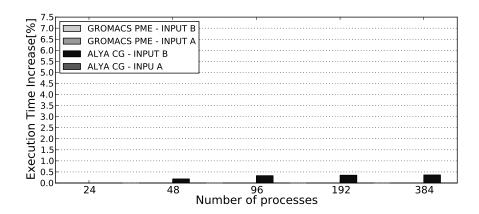

| 4.47 | Applications kernels execution time increase due to reactivation time penalty and                                                                               |            |

|      | lossy compression for one process per node configuration                                                                                                        | 64         |

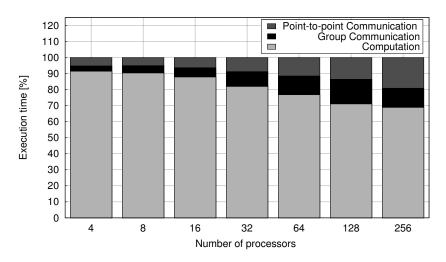

| 4.48 | Applications kernels execution time increase due to reactivation time penalty and                                                                               |            |

|      | lossy compression for six processes per node configuration                                                                                                      | 65         |

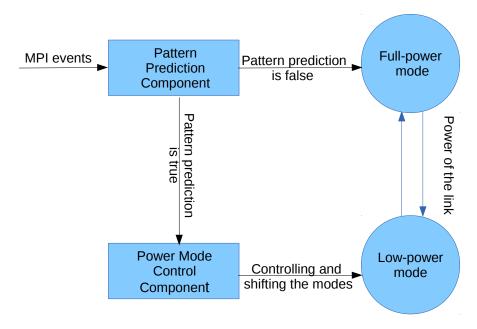

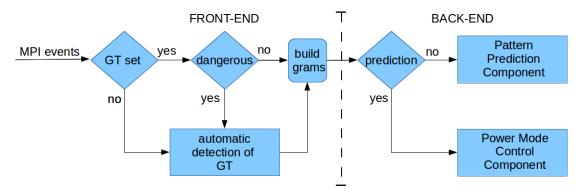

| 5.I  | Simplified diagram of MPI process pattern prediction system                                                                                                     | 70         |

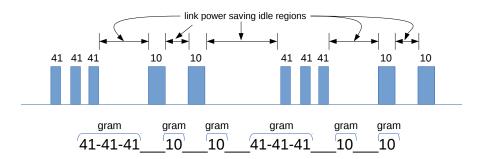

| 5.2  | Forming the array of grams from the MPI event stream (Alya). Event IDs are 41 for                                                                               |            |

|      | MPI_Sendrecv and 10 for MPI_Allreduce                                                                                                                           | 7I         |

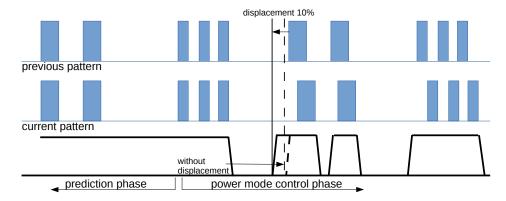

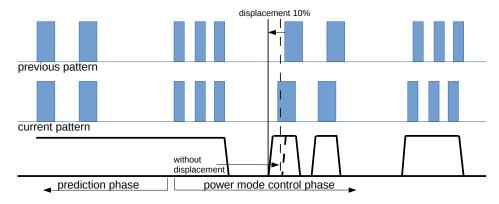

| 5.3  | Example execution of the PPA algorithm for Alya workload                                                                                                        | 77         |

| 5.4  | Controlling IB link power mode during execution of Alya, with displacement factor                                                                               |            |

|      | of 10%. Real idle interval turned out to be larger than expected                                                                                                | 79         |

| 5.5   | Controlling IB link power mode during execution of Alya, with <i>displacement factor</i>           |    |

|-------|----------------------------------------------------------------------------------------------------|----|

|       | of 10%. Real idle interval turned out to be shorter than expected.                                 | 79 |

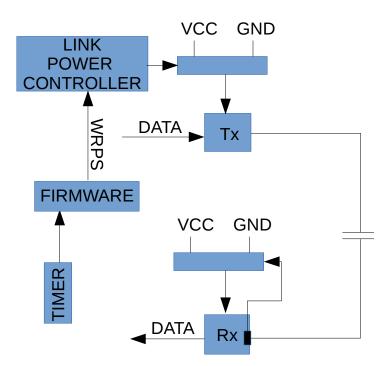

| 5.6   | Link Block diagram                                                                                 | 80 |

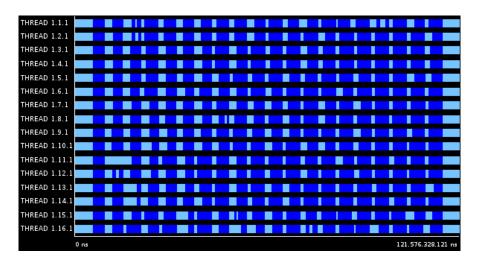

| 5.7   | Execution trace of the Gromacs application with 16 MPI processes, showing when                     |    |

|       | IB links enter low-power mode                                                                      | 82 |

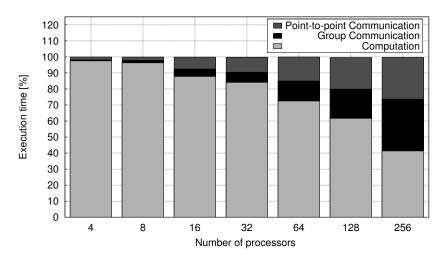

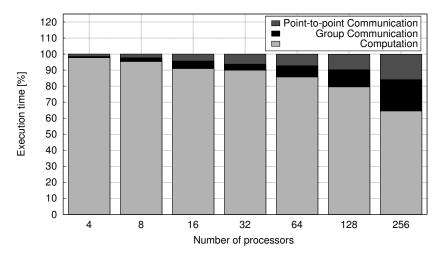

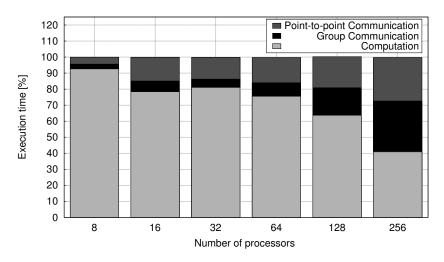

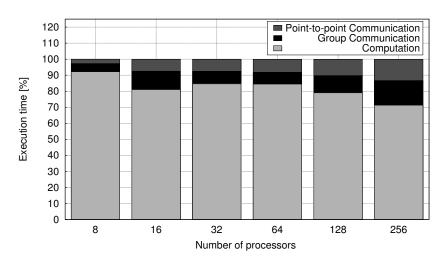

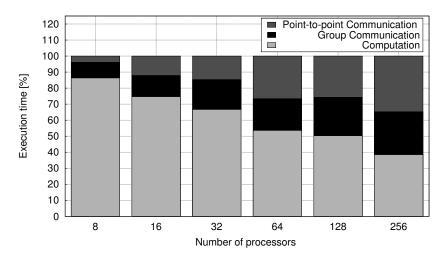

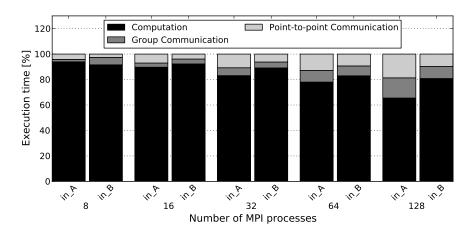

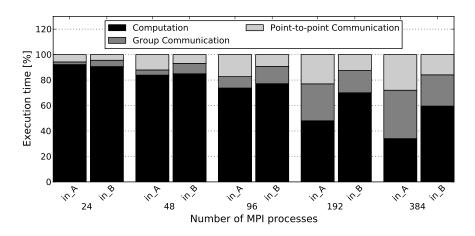

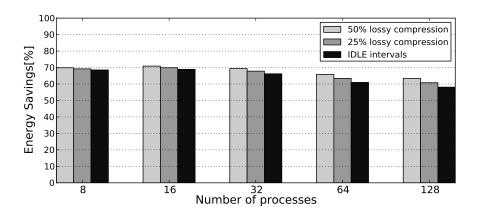

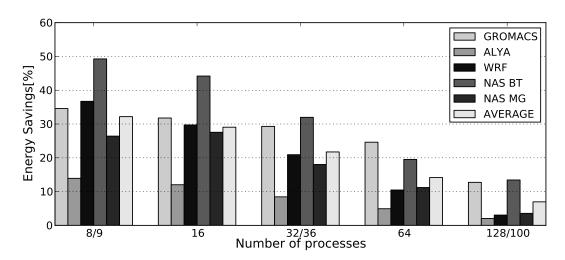

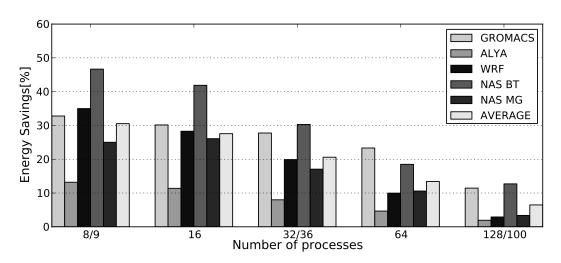

| 5.8   | Energy savings in IB edge switch links - strong scaling results                                    | 83 |

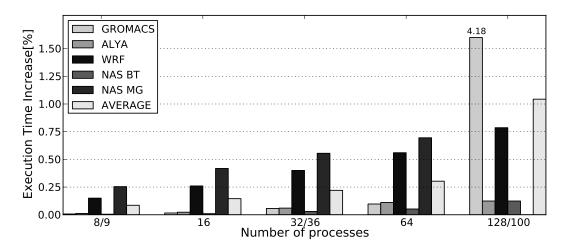

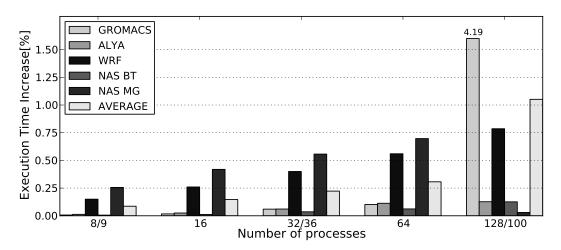

| 5.9   | Applications execution time increase - strong scaling results                                      | 83 |

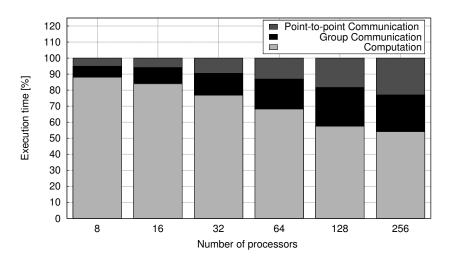

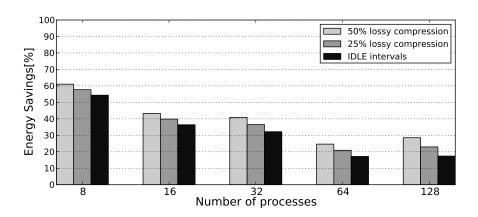

| 5.10  | Energy savings in IB edge switch links when large <i>displacement factor</i> of 10% is used.       | 84 |

| 5.11  | Applications execution time increase when large <i>displacement factor</i> of 10% is used.         | 89 |

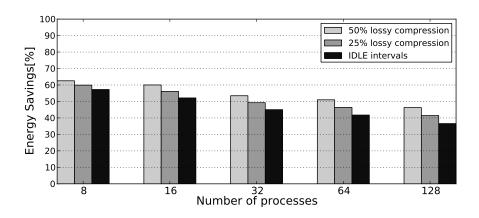

| 5.12  | Energy savings in IB edge switch links when small displacement factor of 1% is used.               | 89 |

| 5.13  | Applications execution time increase when small <i>displacement factor</i> of 1% is used           | 86 |

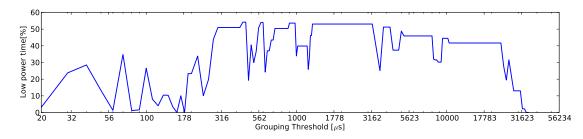

| 5.14  | Effect of Grouping Threshold on time in low power mode                                             | 89 |

| 5.15  | Simplified block diagram of Self-Tuned Pattern Prediction System (SPPS)                            | 90 |

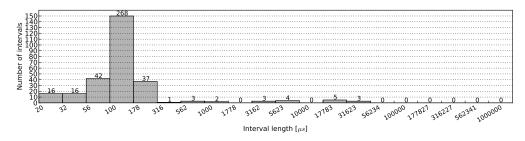

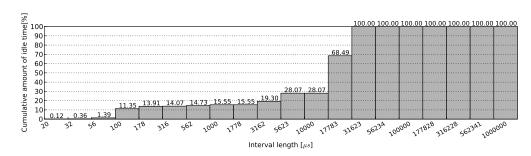

| 5.16  | $\mathit{Histogram}_f$ : Histogram of number of IDLE intervals for NASMG benchmark                 | 9  |

| 5.17  | <i>Histogram</i> <sub>cumt</sub> : Cumulative histogram of IDLE interval time for NASMG benchmark. | 9  |

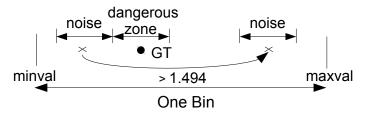

| 5.18  | Necessary gap in the finalization stage for successful GT allocation                               | 94 |

| 5.19  | Value of dangNum used in main phase of ADGT                                                        | 99 |

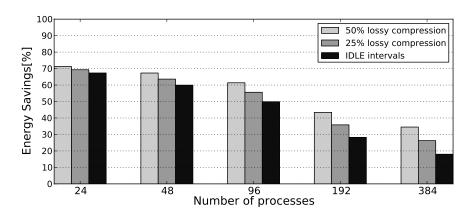

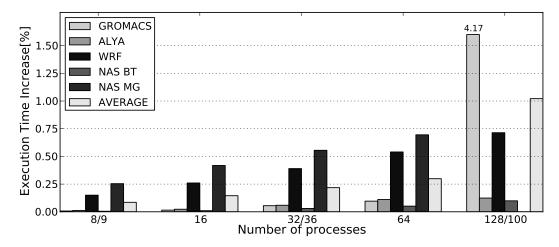

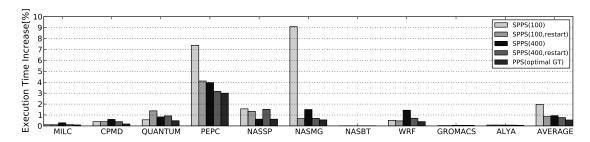

| 5.20  | Applications execution time increase                                                               | 98 |

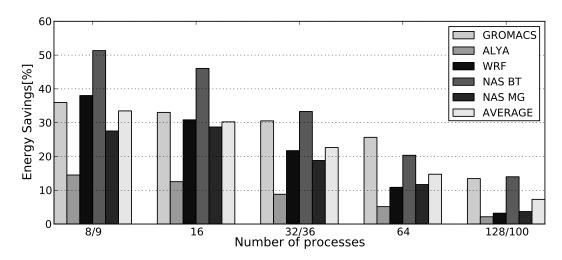

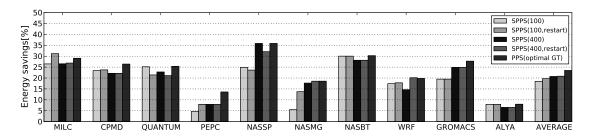

| 5 2 1 | Fnerov savings in InfiniBand edge switch links                                                     | 08 |

To my parents and sister/ Mami, tati i sestri

# Acknowledgments

I would like to express my gratitude to my supervisors, without whom this dissertation would not have been possible. First of all, I would like to thank Professor Eduard Ayguadé for his unconditional support, motivation and encouragement during this large journey. His guidance helped me throughout the research and writing of this thesis. Also, I would like to thank him for encouraging my research and for allowing me to grow as a research scientist.

I would like to thank Miquel Pericas for his valuable and constructive suggestions during the planning and development of this research work, for the stimulating discussions, and most of all for his willingness to participate in the thesis development until the end.

A very special thanks goes out to Paul Carpenter without whom completion of this thesis would have been much more difficult. His assistance in writing papers and making presentations was crucial for the completion of the thesis.

Also, I would like to thanks Nacho Navarro for his suggestions and advice during the research process. His always positive attitude and support helped me a lot to persist in the completion of the thesis.

I gratefully acknowledge the funding sources that made my Ph.D. work possible. I was funded by the Catalan Government with Pre-doctoral Scholarship FI (reference no. 2009FI-B00077) for the first three years and by BSC the following years.

At the same end, I would like to thanks all my friends in Barcelona, at BSC/UPC and other places, that I have met throughout all these years. They have helped me to stay sane and fresh during and most importantly after completing the thesis.

Lastly, I would like to thank my family for their love and encouragement throughout my life.

## Chapter 1

## Introduction

High-Performance Computing (HPC) is a crucial tool for modern science and engineering. There is a constant demand for more powerful supercomputers, leading to increasing levels of energy consumption. The industry is working toward a target of 1 ExaFlop in 20 MW, which implies a seven-fold improvement in energy efficiency, compared with today's most energy-efficient machine.\* Such a large reduction in system energy consumption is only possible if there are significant improvements in the energy efficiency across all subsystems. Power-saving techniques for processors and memory are progressing quickly, but there is less progress in reducing the power consumption of the interconnect. With energy-efficient processing elements and larger networks, the interconnection network is expected to account for up to 30% of the system's total power<sup>52</sup>. This fraction can even reach 50% for data center servers since the CPUs operate at lower levels of utilization.

Most of this power consumption is due to the interconnection links. For example, the links in an IBM eight-port InfiniBand 12× switch consume 64% of the switch power<sup>9</sup>. The problem, in terms of power, of an interconnect link is that its power consumption is almost constant, whether or not it

<sup>\*</sup>The Shoubu machine at RIKEN leads the June 2015 Green500 list with 7.0 GF/W.

is actively exchanging data, since both ends stay active to maintain synchronization.

One possibility to save network power could be to use lower bandwidth links. In this thesis, to address this possibility, we investigate the potential benefits of MPI data compression. If compression of MPI data is possible, this will allow a reduction in link bandwidth which consequently leads to lower link energy consumption, while the original performance is preserved. Even though they are always on, high-speed channels still offer dynamic range, in the terms of their ability to vary data rate and power consumption. Considering the InfiniBand architectural specification, each link is constructed from several serialized lanes each operating at the same data rate. To reduce the energy consumption without affecting performance, the link bandwidths are dynamically adjusted by changing the number of active InfiniBand lanes. This is done in inverse proportion to the compression rate in order to maintain the original bandwidth of the uncompressed data.

Although compression can reduce considerably the necessary bandwidth and therefore, the energy consumption of the interconnect, still, a lot of power is wasted during long idle intervals. Our second goal is to provide a network that supports energy proportional communication, which means that the amount of energy consumed is proportional to the traffic intensity (volume) in the network. In general, application developers view the time spent in communication as overhead and therefore try to minimize it. This leads to high peak bandwidth demands and latency sensitivity, but low average utilisation, having the network largely idle. This provides significant opportunities for energy savings but unfortunately, as mentioned above, current interconnects are not energy proportional, so the potential energy savings are lost <sup>59</sup>.

One approach to reduce network energy consumption during long idle periods is to turn off the network links (or put them in some low-power mode). The problem is that link state changes, from off to active, can take up to 10 µs 35. Since state changes add to the latency of MPI messages, and many HPC applications are highly sensitive to latency, this leads to an unacceptable loss in performance. An alternative is to lower the voltage and bandwidth of links when utilization is low, which has faster

link reactivation, at about 100 ns, but the potential power saving is much lower <sup>15</sup>. Both mechanisms switch between power modes using low-level hardware schemes <sup>59</sup>, <sup>56</sup>, <sup>17</sup>. Common drawbacks are the inability to capture significant energy savings, as well as an unknown and uncontrollable performance penalty. In this thesis, we propose runtime power management support that identifies the structure of the MPI layer communication behavior of an application over the interconnect. Performing end-to-end, recognition of communication behavior on a higher MPI layer level, provides us with a more accurate high-level view of order and timing of the link usage. This software-managed technique will allow us to predict when the link will stay idle, instructing hardware support not only to shift links to low-power modes when idle but also to get switched back on again in time to avoid incurring a significant performance degradation.

Another option to save network power could be to force applications to use the network more efficiently. Overlapping communication and computation will lead to a steady use of the network allowing a reduction in required network bandwidth and most important will reduce time to solution. Unfortunately, overlapping communication and computation is generally hard for HPC workloads. Most HPC applications follow the bulk synchronous programming paradigm, in which application processes are synchronised, either all performing computation at the same time or all involved in communication. Instead of asking to change programs we want to propose techniques that can work with the most frequent software stacks and applications.

The contributions of the thesis are the following:

• We introduce the main concepts of compression technology for energy savings and evaluate a set of compressors. Compression is applied to the data sent and received by MPI¹ library calls. Our techniques are designed for double-precision floating-point (FP) data, which is the most common data type passed in the messages of scientific applications. We consider both lossless compression algorithms as well as lossy compression algorithms, where the compressor reduces

precision based on a target accuracy specification. When applicable, compression allows to design systems with slower components, therefore enabling a reduction in energy and installation costs.

- While compression is targeted to cover link power optimization during communication phases, additional link energy can be saved during large idle phases. The majority of the execution time in most HPC applications is spent in a large number of iterative execution phases. Since the communication pattern inside each phase is essentially the same, it is possible to observe the communication behaviour in one iteration and use the knowledge gained to predict the behaviour of the subsequent iterations. Specifically, this means detecting the patterns of MPI calls that are repeating within each MPI process. To achieve this, we propose to use a software-managed runtime prediction system that will provide us with insight on when to turn off/on the links. We developed Pattern Prediction System (PPS) which allows an on-the-fly detection of consecutive repeatable MPI communication patterns. This provides a high-level view of the order and timing of link usage, which permits the transition between different link power modes to be made with a minimum impact on performance.

- The basic Pattern Prediction System (PPS) is prone to instability if the chosen critical idle interval length does not match the critical idle interval length of the chosen application. Critical idle interval length is the minimal idle interval length during which link power can be saved. We refer to this value as the Grouping Threshold (GT), and it has an important influence on the level of prediction and therefore on energy savings, depending on the application in a complex way. A larger value of the Grouping Threshold usually leads to higher prediction accuracy, but lower values can provide better energy savings. We, therefore, propose a histogram-based self-tuned prediction mechanism that automatically determines the critical idle interval, which distinguishes short and long idle intervals. The resulting mechanism obtains energy savings in

the network edge links of up to 21% with negligible performance overhead.

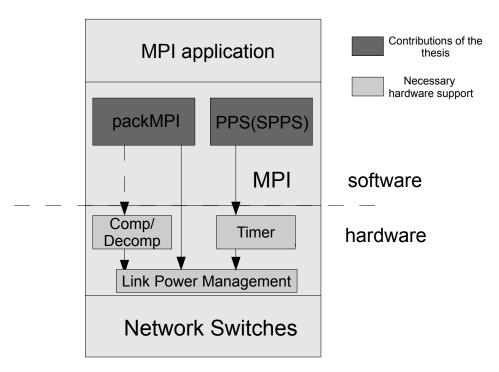

Figure 1.1: System stack architecture with our proposals in MPI layer.

Figure I.I summarizes our techniques developed in MPI layer. The dashed lines show the hardware approach for the *packMPI* library, in which the MPI layer is bypassed and directly communicates with the Host Channel Adapter (HCA) where the compressor (decompressor) rate is set. Therefore, when communication is started, the original data is transferred to the HCA buffers from where appropriate bit-lines are activated in correspondence with the chosen compression rate. Compression can also be done in software with the higher compression/decompression overheads introduced in the total MPI data latency. In correspondence with the compression rate, the number of lanes of InfiniBand link is also deactivated using Link Power Management (LPM) firmware on the HCA. Pattern Prediction System (PPS) exploits the MPI profiling interface PMPI to implement its functionality. PPS is wrapped around actual MPI library invocations. This makes the PPS technique portable that can be applied on

any MPI application without changing their source code. When a prediction is confirmed, switching the link to low-power mode is done using the LPM firmware.

The thesis is organized as follows. Chapter 2 provides the necessary background on network performance issues, possibilities of data compression to enhance network efficiency, network power consumption breakdown and Infiniband network technology. Chapter 3 describes the methodology and the toolchain used for the experiments. Chapter 4 introduces the main concepts of compression technology for link power savings and evaluates a set of compressors. Effects of compression on application performance are also discussed. The following Chapter 5 introduces the design of our prediction techniques for link power savings. The related work is summarized in Chapter 6. Finally, in Chapter 7 we give the main conclusions of this thesis.

# Chapter 2

# Background

# 2.1 System Area Network (SAN) - Interconnection Network for HPC

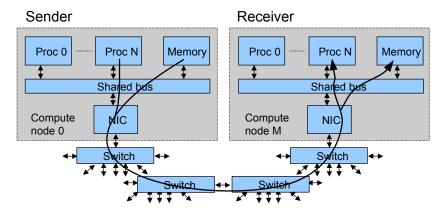

In the current High Performance Computing (HPC) landscape, clusters have become the ubiquitous architecture for accelerating many scientific and engineering applications. These systems consist of multiple computer nodes that communicate over a network. Figure 2.1 illustrates the communication path in a large-scale interconnected system from a sender (compute node o) to a receiver node (compute node M), which consists of the following steps:

- Data are fetched from a processor local memory and sent to the memory on the Network Interface Card (NIC), also known as Host Channel Adapter (HCA) in the InfiniBand terminology, which is used for attaching the processing node to a network

- · NIC transforms data messages into network packets

- Packets go through a number of switches before reaching the destination

Figure 2.1: Communication path in a large-scale interconnected system.

At the destination packets are reformatted by the receiving NIC and sent to the receiving processor's local memory

Communication is not only costly in time, energy costs also need to be taken into account. Therefore, data transfers are an important component of parallel systems that need to be extensively optimized.

## 2.2 Communication in Parallel Programs

Scientific applications solve complex problems by splitting the problem into several smaller parts, each assigned to a single application's process. The interconnect's role is to satisfy remote data dependencies between application's processes that are executing on different nodes. Depending on the algorithm applied to solve the problem, the processes may communicate messages following different patterns, such as, a single pair of processes at a time, i.e., point-to-point communication or multiple processes at time, i.e., usually referred as collective communications.

In general, application's communication time is the time that an application spends in communication routines. Depending on the problem size and scale, i.e., the number of processes involved in

the computation, the message sizes may vary as well, making application's communication bandwidth or latency-sensitive. Single message transfer would require the following time:

$$T_{message} = T_{latency} + \frac{Message\_Size}{B}$$

Latency is the time it takes to send zero-byte message from source to destination, whereas bandwidth is the actual speed of transmission, or bits per unit time. As communication time doesn't advance the actual computation, it is rather seen as an overhead and must be minimized to get the best performance improvement.

In order to successfully accomplish message delivery, two common message passing protocols are generally employed:

- Eager An asynchronous protocol that allows a send operation to complete without acknowledgement from a matching receive

- Rendezvous A synchronous protocol which requires an acknowledgement from a matching receive in order for the send operation to complete.

While eager protocol reduces synchronization delays (send process does not need acknowledgement from receive process that it's OK to send message) the most important disadvantage is that it is not scalable. Significant buffering may be required to provide space for messages from an arbitrary number of senders. On the other side rendezvous protocol is scalable compared to eager but his disadvantage is that it introduces synchronization delays due to necessary handshaking between sender and receiver. Thus, eager protocol is typically used for "short" messages, while rendezvous protocol is used for "long" messages.

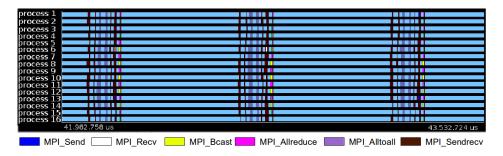

The performance of a parallel program can be presented by its execution time consisting of computation and communication components. Figure 2.2 shows the structure of the GROMACS application, where with light blue is shown computation phase while the communication phase is represented with all the rest of the colors.

Figure 2.2: GROMACS execution trace with corresponding computation and communication phases

In this thesis, to reduce network power consumption we are mainly focused on the bandwidth component of the actual transfer time. A reduction in the bandwidth of the link will automatically reduce its power consumption, but these decisions when to switch to low-power mode are critical, especially in HPC, where the primary design objective is performance. Therefore, any proposed energy-saving technique will only be adopted if there is no significant performance deterioration.

#### 2.3 Data Compression

Data compression, both lossless and lossy, is widely used, across many application domains, to reduce the demands on storage capacity and communication bandwidth. In HPC, data compression has been applied to messages on the network in order to minimise application execution time <sup>30,38,23,39,41</sup>. However, in our study, of the impact of compression on performance in Section 4.2, we concluded that the gains obtained are lower than expected by Amdahl's law for the used compression rates, where compression rate is defined as follows:

$$Compression\_rate = \frac{(uncompressed \ size)}{(compressed \ size)}$$

Thus, in this thesis we aim to apply data compression to the problem of energy efficiency.

There is an important distinction between lossless and lossy compression. Although lossless compression can be applied to scientific applications indiscriminately, always leading to correct results, our

results validate previous studies, which have shown that the resulting compression rate is low <sup>25</sup>, <sup>41</sup>, <sup>29</sup>. This is because scientific applications pass high entropy floating-point data, which is hard to compress. In contrast, applying lossy compression requires the involvement of the scientific application or library developer. Previous studies have, however, found that these experts have a good understanding of the numerical stability of their algorithms, and can determine the required data precision.

#### 2.3.1 Lossless Compression

Lossless compression is the method of choice where preserving the numerical precision of the data is necessary for correctness, since introducing error in the system may cause a significant deviation in the final result. General purpose algorithms like GZIP<sup>8</sup> or BZIP2<sup>5</sup> can be used for floating-point data, but generally compressors designed specifically for floating point data will yield better results<sup>22</sup>. Usually they are based on a predictive scheme which tries to predict the next value based on the sequence of previous values. Depending on how they calculate the predicted value, lossless compression algorithms can be classified into two major groups. The first group uses arithmetic predictors based on a polynomial function to predict the next value<sup>38</sup> whereas the second group relies on context based predictors that store the previous values in a hash table<sup>23</sup>. These values are then used to predict the following ones. The difference between the predicted and true value is then computed. If the prediction is close to the true value the difference can then be encoded with fewer bits, resulting in a compressed form. This can be very effective in the case of scientific applications where communicated data represents adjacent physical quantities, such as in Finite-Difference Time-Domain (FDTD) or Lattice Boltzmann method<sup>38</sup>, whose values tend to be highly correlated. Such data patterns may then be effectively captured by predictors.

In this thesis we used following lossless compressors:

FPC (Floating-Point Compressor) from Burtscher et al.<sup>23</sup> is a lossless compression algorithm

for a linear stream of 64-bit floating-point data which relies on context based predictors. FPC reportedly achieves good compression rates and it has a compression speed one or two orders of magnitude faster than competing algorithms.

- MAF (MAkichan for Floating) is another lossless compressor developed by Tomari et al. <sup>60</sup>. In MAF, only the exponential part of the double-precision floating point data is compressed. This approach can be very effective if the entropy of the data is very high but the magnitudes (i.e. exponents) do not change much. It is also notable for its high speed which enables low-latency communication even in software based approaches.

- GZIP is based on the DEFLATE algorithm <sup>27</sup>, which is a combination of LZ<sub>77</sub> <sup>65</sup> and Huffman coding <sup>37</sup>.

To benefit from transferring compressed data the additional time for compression should be less than the time saved during the communication primitive. Considering that sending data involves a message setup overhead and that messages might be very small, some amount of data is established as a minimum threshold in order to apply compression. The critical size of message is defined as a product of latency and bandwidth, which means that all messages smaller than this product will have latency as a dominant factor in a transfer time and, therefore, the impact of compression would be negligible.

#### 2.3.2 Lossy Compression

In the case of lossy compression, the most straightforward way to compress is to discard the least significant mantissa bits. However, care needs to be taken not to jeopardize the correct execution of the application. It is necessary to provide a criteria of minimum accuracy so that compression does not invalidate the final result. For the case of lossy compression it is necessary that the application experts determine the acceptable error and develop models to predict the required precision of the computation.

In this thesis, in order to apply lossy algorithms, the following criteria of accuracy has been established:

$$L^2_{relative\_error\_norm} = rac{\sqrt{\sum\limits_{i=1}^{N}(P_i^{s2}-G_i^k)^2}}{\sqrt{\sum\limits_{i=1}^{N}(P_i^{s2})^2}}$$

where  $F_i$  is exact solution (with 52-bits of double-precision floating point mantissa) and  $G_i$  is newly calculated solution after lossy compression is applied (with k- bits of double-precision floating point mantissa).

Upon consulting with application developers we determined 1 % error from the final result to be acceptable, thus, if the newly obtained result with lossy compression is within a margin of 1% we take it as a valid result.

## 2.4 Interconnection Network Power Consumption

The network fabric power consumption is due to the switch fabric, HCAs, and interconnect links. The power consumption of the HCAs and switches varies with the data injection rate, being dominated by the active power of the memory elements. In contrast, the power consumption of an interconnect link is almost constant, whether or not is actively exchanging data 59, since both ends stay active to maintain synchronization. It has been shown that the majority of the total network fabric power consumption is due to the interconnect links; e.g. for an IBM InfiniBand 8-port 12× switch, the links are estimated to take 64% of the total switch power 9. For this reason, in this thesis our focus will be on link power.

## 2.5 Power-saving Support in Interconnection Network Links

Most energy optimization research is focused on reducing link energy consumption in interconnection networks using different kinds of power-aware techniques. These techniques can be classified in two

classes: dynamic voltage-frequency scaling and on/off links.

The on/off technique allows entering to a deeper low-power mode, thus saving more power. The problem is that link state changes, from off to active, can take up to 10 µs 35. Since state changes add to the latency of MPI messages, and many HPC applications are highly sensitive to latency, this leads to an unacceptable loss in performance. Also as links are turned off, a fault-tolerant routing algorithm has to be used, increasing hardware complexity and possibly introducing additional penalty in network performance. An alternative is to lower the voltage-frequency pair, thus reducing the bandwidth of links when utilization is low, which has faster link reactivation, at about 100ns, but the potential power saving is much lower 16. Here, the advantage is that the connectivity throughout the network is preserved and the same routing algorithm can be used regardless of the power consumption level, simplifying router design.

#### 2.6 InfiniBand technology

The adapter and switch architecture parameters used throughout the thesis are based on the current Infiniband adapter and switch architecture employed in many computing systems today. The typical link bandwidth supported in InfiniBand is 10—40 Gbit/s and the switch latency is 100 ns.

InfiniBand links support two physical mechanisms that can be used for power saving. First one allows links to operate at different data rates, for example between Quad Data Rate (QDR), at 10 Gbit/s per serial lane, and Single Data Rate (SDR), at 2.5 Gbit/s per lane. This gives a tradeoff between bandwidth and energy consumption. The switching time between rates is small, on the order of hundreds of nanoseconds<sup>15</sup>, but the power savings are also small.

Second power saving mechanism is derived from the actual InfiniBand link architecture, where the link is formed by aggregating one or more serial lanes. It is common to use more than one lane, in order to increase the link's bandwidth, though power consumption is also multiplied by the same

factor. Mellanox has recently announced Width Reduction Power Saving (WRPS), a technique that allows the link's number of active lanes to be dynamically reconfigured, assuming firmware support is enabled in the HCAs and switches <sup>12</sup>. For example, using WRPS a 40 Gbit/s 4× QDR port can run as 10 Gbit/s 1× QDR by shutting down three of its four QDR lanes. This reduction in link width reduces the power consumption of Mellanox Switch SX6036 to only 43% of its nominal power (when all four lanes are active) <sup>12</sup>. We use this published value of 43% in the evaluation section as the power consumption of an IB switch in low-power mode. The energy to transfer a single message remains the same, because energy is power multiplied by time. The energy savings come from relatively short idle periods between messages.

# Chapter 3

# Experimental Methodology

We used two classes of tests for the evaluation of application and system performance. When possible, we evaluated the performance on a production HPC machine. When our proposals depend on features that are not supported on current systems, then we used simulation tools. Since this study is exploring the HPC traffic in conjuction with the specific network technology, we used an MPI simulator that allows a replay of the application's MPI activity while respecting the communication dependencies between MPI processes which is coupled with an event-driven network simulator which simulates the network architecture in detail. In this chapter we introduce the TestBed platforms where real execution tests were done, as well as the platform used to generate input traces for the simulator. Also we describe the set of simulation tools deployed in this thesis, along with the workloads used in simulation.

## 3.1 TestBed platforms

The main features of the clusters and MPI implementations used for our evaluation are:

- 1. MareNostrum II is an compute cluster based on IBM JS21 blades, each with two dual-core IBM 64-bit PowerPC 970MP processors running at 2.3 GHz and with 8 GB of RAM. Communication itself occurs over a 2Gbps Myrinet network with a fat tree topology. MPICH-MX is used as message passing library, which implements the MPI-1 standard.

- 2. Mino Tauro is a machine based on Bull B505 nodes, with six-core Intel Xeon E5649 processors at 2.53 GHz with 24 GB RAM. All nodes are connected through InfiniBand network running at 40Gbps and organized as 2-level fat tree network. OpenMPI-1.6.4 is the MPI implementation used for trace collection on Mino Tauro.

#### 3.2 HPC workloads

To evaluate the potential for link power reduction using our MPI layer techniques we have chosen a wide breadth of HPC production application and benchmarks. For the data compression evaluation just the main kernels of real applications were observed while for link power reduction using prediction system entire applications were considered.

#### Real applications:

- I. ALYA<sup>3</sup> is a computational mechanics system that is capable of solving different physics problems. The problems that we selected in our investigation use the conjugate gradient(CG) method as the main kernel.

- 2. GROMACS<sup>7</sup> is a molecular dynamics simulator. For the calculation of forces it uses the Particle Mesh Ewald (PME) method which is the main kernel.

- 3. MILC<sup>34</sup> performs large scale numerical simulations to study quantum chromodynamics (QCD). QCD is the theory of the strong interactions of subatomic physics.

- 4. PEPC<sup>32</sup> is a tree code for solving the N-body problem.

- 5. CPMD<sup>24</sup> is an *ab initio* electronic structure and molecular dynamics (MD) program using a plane wave/pseudopotential implementation of density functional theory (DFT).

- 6. QUANTUM ESPRESSO<sup>31</sup> is an integrated suite of computer codes for electronic-structure calculations and materials modeling, based on density-functional theory, plane waves, and pseudopotentials (norm-conserving, ultrasoft, and projector-augmented wave).

- 7. WRF (Weather Research and Forecasting model)<sup>47</sup> is a next-generation mesoscale numerical weather prediction system designed for both atmospheric research and operational forecasting needs.

#### · Kernels:

- 1. CG (Conjugate Gradient)<sup>57</sup> is an iterative method for solving systems of linear equations that arise from the finite element method (FEM).

- 2. PME (Particle Mesh Ewald)<sup>53</sup> is a method for computing long-range interactions in periodic systems. In PME the sum of long-range forces is processed in Fourier space where this sum converges much faster as compared to real space.

#### · Benchmarks:

- NAS MG (Multi Grid)<sup>13</sup> approximates the solution to a three-dimensional discrete Poisson equation using the V-cycle multigrid method.

- 2. NAS BT (Block Tridiagonal)<sup>13</sup> is an algorithm used for solving a synthetic system of non-linear partial differential equations.

- 3. NAS SP (Scalar Pentadiagonal)<sup>13</sup> is another algorithm used for solving a synthetic system of nonlinear partial differential equations.

### 3.3 Extrae - Tracing Tool

In order to collect the application communication characteristics and its performance it is necessary to insert instrumentation during its execution. Instrumentation captures information during the program execution creating an application trace. This process of receiving informative messages about the execution of an application at runtime is called tracing. To obtain traces of parallel applications at run time we used Extrae <sup>20</sup>, the tracing tool developed at Barcelona Supercomputing Center (BSC).

To create traces of MPI calls the MPI profiling interface (PMPI) defined by the MPI standard is used. This interface allows a tool such as Extrae to interpose a library between the application and the MPI substrate and intercept one or more MPI calls. The MPI standard requires that each routine is available with both the MPI and PMPI prefix. The application calls with MPI prefix are intercepted and recorded, while PMPI calls are executed. Therefore, Extrae intercepts the MPI calls that are coded with MPI prefix. Usually the collective MPI calls are implemented using PMPI point-to-point communication calls, thus, they are not being recorded by Extrae. For our study, the internal structure of collectives is very important, thus, to instrument low-level operations of collectives we used adapted versions of MPICH-MX and OpenMPI libraries that allow the translation of low-level operations to MPI -like names.

To intercept the MPI calls Extrae uses the LD\_PRELOAD mechanism where at runtime the original symbols (MPI) are substituted by those provided by the intstrumentation package (PMPI). Aslo for the tracing of internals of collective calls the modified MPI library is loaded. In the Figure 3.1 is shown the an example script used for trace generation.

During the instrumentation, each sequence of computation activities from the same process is translated into a trace record indicating a busy time for a specific CPU whereas the details of the actual computation performed are not recorded. Communication operations are recorded as send, receive, or collective operations records, including the sender, receiver, message size, and type of operation.

#### bsc18511@nvb127:/gpfs/scratch/bsc18/bsc18511/mnsubmit run.sh #! /bin/bash @ job\_name @ initialdir = nucleo\_256 #initial directory = mpi\_%j.out #output file @ output = mpi\_%j.err @ total\_tasks #number of processes #number of processes per node #number of processes per CPU 0 tasks\_per\_node 0 cpus\_per\_task = 6 # @ wall\_clock\_limit = 00:30:00 export MDRUN=/gpfs/scratch/bsc18/bsc18511/GROMACS time srun trace.sh export LD\_LIBRARY\_PATH=\${MPI\_INTERNALS\_LIBRARY}/lib export EXTRAE\_HOME=/gpfs/apps/NVIDIA/CEPBATOOLS/extrae/openmpi/64 export EXTRAE\_CONFIG\_FILE=./mpitrace.xml export LD\_PRELOAD=\${EXTRAE\_HOME}/lib/libmpitrace.so

\$MDRUN/bin/mdrun\_d -s run\_twover\_200step.tpr -v -dlb yes -npme 0

Figure 3.1: Tracing scripts for GROMACS application.

#### 3.4 Paraver - Visualization Tool

Paraver <sup>14,51</sup> is the visualization tool developed at BSC and it is used in multiprocessor systems to visualize multithreaded program traces (including MPI and OpenMP) that are obtained at runtime using the Extrae tool. It allows the user to view runtime information of function calls and hardware counters. In Paraver metrics are not hardwired on the tool but programmed. Using a filter and a semantic module, the analyst can create time-lines, profiles and histograms from trace-files to selectively display a huge number of performance metrics. The different views can be easily combined to find correlations among the causes of performance drawbacks. To capture the expert's knowledge, any set of views can be saved as a Paraver configuration file, to be reused in subsequent analyses. With Paraver it is easy to visualize communication patterns, including the number of bytes exchanged between each pair of tasks.

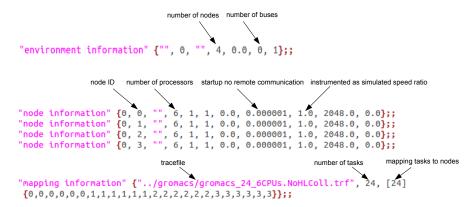

Figure 3.2: Dimemas parameters used to simulate Gromacs application with 24 MPI processes where six processes are run on each node

#### 3.5 Dimemas - MPI simulator

Dimemas 19,42 is an event-driven simulator, which replays a trace of the application's computation bursts and MPI activity, preserving its causal relationships and timings. It is driven by traces generated by the *prv2dim* tool which converts the original traces suited for Paraver to traces expected by Dimemas. Each trace contains a sequence of operations for each thread of each task. It contains CPU intervals and MPI/communication event information (message size, identifiers, type, source-destinations) from the original execution. Dimemas models an architectural machine model with SMP nodes interconnected with a simple point-to-point network with duplex links. The model is highly parameterizable, allowing the specification of parameters such as number of nodes, number of processors per node, relative CPU speed, number of communication buses, mapping task to nodes, etc. Computation bursts are not actually performed, but represented by the time the actual computation would last. Communication operations are send and receive point-to-point communications.

In Figure 3.2 is shown an example set of parameters used in our study. Dimemas generates trace files that are suitable for Paraver enabling the user to conveniently examine any performance problems indicated by a simulator run.

# 3.6 Venus - Network Simulator

Venus <sup>49,48</sup> is a generic interconnection simulator capable of simulating many different kinds of networks. It is based on OMNET++ <sup>61</sup> and provides a socket-based co-simulation interface to the MPI task simulator, which replays traces obtained using an instrumentation package. It is able to provide a detailed simulation of the network topology and the processing inside the switches. Detailed models of switch and adapter hardware corresponding to different networking technologies, including Ethernet, InfiniBand, Myrinet are supported.

Network topology, routing and mapping of application processes to the nodes are specified in separate configuration files. Although it can supports different network topologies our switch models are arranged in a fat tree topology - specifically an Extanded Generalized Fat Tree (XGFT). By using Venus xgft tool with option -m and passing the parameters that define the desired fat tree topology, the intermediate topology file is generated. For example, to create a topology for a two-level fat-tree with switch radix 2 is neccessary to run the xfgt tool with following parameters:

$$xgft - m 2:2,4:1,2 > 2level_ft.map$$

Than *map2ned* tool converts a map file to an OMNEST Network Description file (2level\_ft.ned) corresponding to the specified topology and a matching initialization file (2level\_ft.ini) containing network address and host/switch labels.

The routing file is generated using xgft tool followed by -r option and a number that represents specific routing scheme (e.g. 3 for random routing).

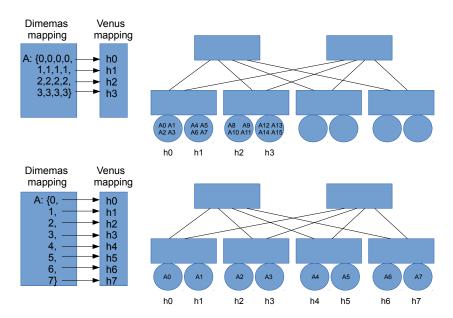

Mapping is done through configuration file (.scb) that contains one hostname (as known to Venus) per line; task n is mapped to the host corresponding to the hostname specified on line n. Relation in between task mapping in Dimemas and Venus is shown in Figure 3.3.

The link bandwith is defined by two parameters where first one is the *unit size* which is equal to the

**Figure 3.3:** Task-to-nodes mapping in Dimemas and Venus. The upper figure shows how various Dimemas tasks are mapped to the same Venus node while the bottom figure is showing how each Dimemas task is mapped to different Venus node.

flit size of the real network while the second parameter is *unit\_time* which is time needed to transfer volume of data defined by *unit\_size* over the newtork link.

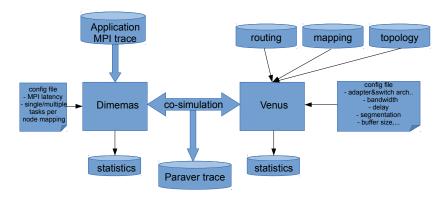

Dimemas has bus-based interconnect model that does not capture important network-related aspects, such as topology, routing policies, flow control, traffic contention and congestion, deadlock

Figure 3.4: Dimemas & Venus co-simulation toolchain.

prevention, and anything relating to switch and adapter hardware implementations. Therefore, in order to increase simulation accurancy we use Dimemas integrated with Venus. The complete toolchain of Dimemas-Venus co-simulation is given in the Figure 3.4.

# Chapter 4

# Enhancing Network Efficiency Using MPI

# Data Compression

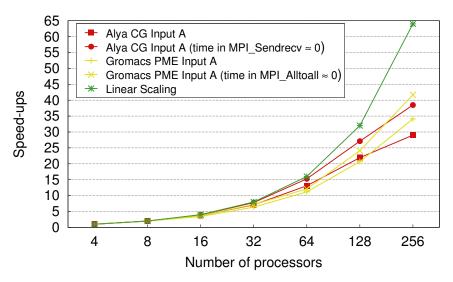

# 4.1 Motivation for MPI message compression

In order to motivate this work we first determined an upper bound on the improvement in performance due to data compression. Figure 4.1 shows the speedup of the two kernels, Alya's Conjugate Gradient (CG), with Input A, which consists of 500,000 doubles, and GROMACS's Particle Mesh Ewald (PME), with more than 1,000,000 doubles. This plot also shows the upper bounds, which are the ideal case where the time spent in certain MPI communication routines is reduced to zero. In this case, the absolute maximum increase in speedup, due to absence of communication, is 32% for CG (38.5× instead of 29×, for 256 processors). The absolute maximum increase in speedup for PME is 22% (42.5× instead of 34×, for 256 processors).

The transmission time of MPI messages occupies an important part in the total latency of the MPI routines. As the size of a message gets bigger, so does the time spent in transmission. In

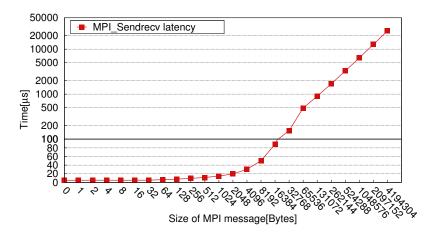

Figure 4.1: Parallel scaling of CG and PME kernel on IBM compute cluster machine with 1 process per node

Figure 4.2: MPI\_Sendrecv latency on IBM J21 Myrinet cluster.

order to measure the latency of MPI\_Sendrecv and MPI\_Alltoall calls for different sizes of measures we used the IMB-MPII part of Intel MPI Benchmarks<sup>II</sup>. We measured the performance for MPI\_Sendrecv and MPI\_Alltoall functions in order to understand the impact of message size on the total latency of the MPI call. Figures 4.2 and 4.3 show the latencies for messages of various sizes.

The results show that for messages smaller than 1 KB almost no savings in time can be obtained by reducing the message size. For message sizes larger than 1 KB, reducing the message size can result in

Figure 4.3: MPI\_Alltoall latency on IBM J21 Myrinet cluster.

significantly reduced message latency. To reduce the size we apply compression to the MPI messages and analyze if the reduced transmission time can also result in improved application performance.

# 4.2 Evaluation of Performance Benefits

Compression schemes have been proposed to compress data on the network in order to reduce the overall execution time of applications. In scientific applications this data is frequently formatted as IEEE-754 double-precision floating point numbers.

In this thesis, we consider both lossless compression algorithms as well as lossy compression algorithms, where for the latter the compressor reduces precision based on a target accuracy specification. Besides our goal of using compression to increase the effective network bandwidth, it can also be used to improve memory bandwidth <sup>38</sup> and disk bandwidth in I/O intensive applications <sup>63</sup>. When applicable, compression allows to design systems with slower components, therefore enabling a reduction in energy and system costs. In the case of HPC applications it is important that compression can be done in a single pass in order to minimize the compression latency. When runtime compression of MPI messages is considered, the overheads introduced by compression and decompression opera-

tions play an important role. If the communication to computation ratio in an application is not big enough then these overheads can prevent the compression technique to achieve the expected speedups. In MPI compression it is necessary to perform one compression and one decompression routine for every single data transfer. The sum of all these transfers may lead to performance degradation. One option to remove compression/decompression overheads is to overlap the process of compressing data with the interchange of previously compressed data, exploiting parallelism to achieve negligible performance degradation as much as possible. An alternative approach is to consider streaming compression/decompression hardware. In such a scenario the task of compressing the data can be performed on the fly when data is copied from main memory to the memory on the network interface card. The procedure is inverted for decompression. Such a compressor/decompressor can appear in the form of an ASIC, FPGA or it can be a dedicated microcontroller.

# 4.3 Real Machine Tests

## 4.3.1 Methodology

To measure the impact of compression and decompression on the execution time of parallel programs we use the Paraver tool <sup>21</sup> to visualize the traces obtained at runtime using the Extrae tool (both are described in more details in Section 3.3) together with the execution times that programs themselves output. Computation time, communication time and the execution overheads due to compression/decompression are measured using Paraver. In order to predict execution times without compression overheads, which would be the case when assuming streaming compression hardware or overlapped compression/communication, we subtract the original average communication time from the unmodified trace and add the average communication time obtained from the traces with MPI compression. These numbers are averaged over a series of executions. The resulting number is

an approximation. The effects of compression are distributed across program threads and may also impact scheduling decisions. It is thus not possible to give an accurate prediction. However, as will be seen the trends that are observed are consistent with expectations, which raises the confidence towards the obtained results.

The programs are executed on the MareNostrum compute cluster described in more details in Section 3.1. Although the machine contains over 10k cores, we did not run simulations larger than 256 processors. Since we use rather small inputs for our workloads, we already reach a communication-dominated strong scaling scenario with a medium number of processors (~256). Each node of MareNostrum machine has two dual-core processors. Therefore, we chose to run the tests with one process per node and four processes per node. Communication between processes on the same node is done through shared memory. Our tests for the configuration with 4 processes per node starts with 8 MPI processes in order to also have inter-node communication and not just intra-node communication. When 1 process per node is used, we avoid any other effects that could be provoked by multiple process sharing the same memory and NIC. In the case of configuration with 4 processes per node, we may have more traffic through the NIC and thus, compression should help more, reducing the contention on the NIC.

In order to analyze compression we adapted several publicly available compressors to the PowerPC970 platform. Among lossless compressors, MAF and GZIP were directly available and did not require further modification. In the case of FPC, we had to adapt the code to the big-endian format of the PowerPC platform. This was not trivial as FPC uses many tricks that rely on the little-endian format. Our final port of FPC is not as efficient as the original little-endian code, but the difference is negligible (just a few additional bytes per message).

An important consideration when using lossless compression is that the resulting message size after compression cannot be deterministically computed. This is important in the case of MPI compression because it means that the receiving process does not know how many bytes it needs to read. In our

Figure 4.4: Packing algorithm<sup>2</sup> for doubles when reduction to 5 bytes is chosen

implementation we solved this problem by splitting the send procedure into two steps. In the first step just the size of the message is communicated and in the second step the message is sent. This solution is not optimal as it introduces overheads. A better solution would be to allocate the data buffers inside the MPI stack dynamically.

To apply lossy compression on CPUs we used a freely available code <sup>2</sup> that discards low-order bytes and packs double-precision floating point data into an array of 32-bit unsigned integers. Thus, a double-precision floating point number originally of 8 bytes can be cut to 5 or 6 bytes, which corresponds to 29 or 37 bits of mantissa. We modified the code so that double-precision floating numbers can be further cut to 3 and 4 bytes, corresponding to 13 and 21 bits precision.

Upon receiving compressed data the unpacking is done. The decompressed data is returned by extending with zeros to the original double-precision format but now having a reduced accuracy due to the quantization error resulting from cutting the mantissas. The necessary code for packing and unpacking along with the original MPI functions is inserted in an MPI wrapper function. A new library called packMPI was created with all MPI wrapper functions. They have the same arguments as the original MPI functions plus one to specify how many bytes of the original double value to keep. Thus, the original MPI functions can be replaced with the new wrapper MPI functions packMPI\_Alltoall and packMPI\_Sendrecv at any point in the application where one wants to compress the volume of transferred data. Figure 4.4 shows how the packing algorithm works in a software implementation. If streaming hardware is considered, the implementation of the packing algorithm is straightforward.

It stores the words that are sent to the NIC in an input buffer and activates appropriate bit-lines corresponding to the chosen compression rate. Therefore, only a few cycles of latency will be added, which can be considered negligible.

# 4.3.2 Case Study: Alya

The problems that we selected in our investigation use the conjugate gradient (CG) method of Alya application as the main kernel. The execution of the CG kernel consists of (i) one MPI point-to-point communication and (ii) two MPI group communications. Significant amounts of data are transferred in the MPI\_Sendrecv point-to-point communication where local parts of the search vector are exchanged in order to obtain the final matrix-vector multiplication result. Group communication is employed for the final dot-product summation of vectors in the algorithm but only one double per MPI call is exchanged at this stage.

Table 4.1: Average size of MPI messages (kB)

| N proc | Alya CG | Alya CG | Gromacs PME | Gromacs PME |

|--------|---------|---------|-------------|-------------|

|        | Input A | Input B | Input A     | Input B     |

| 4      | I4.4    | 47.8    | 559.8       | 4144.2      |

| 8      | 15.4    | 47.7    | 139.9       | 1036.0      |

| 16     | 7.9     | 25.8    | 147.8       | 259.0       |

| 32     | 3.9     | 17.4    | 55.4        | 350.4       |

| 64     | 2.2     | 9.2     | 18.4        | 135.5       |

| 128    | I.4     | 5.0     | 8.0         | 53.2        |

| 256    | 0.8     | 2.9     | 2.6         | 16          |

For the Alya CG evaluations we have used two input data sets which we call Input A and Input B. The Input A has size of  $5 \times 10^5$  while Input B is larger and has  $4 \times 10^6$  nodes. The exchanged mes-

Table 4.2: Average compression rates achieved on MPI messages in the SMVM part of CG kernel

|   | Alya CG | GZIP | FPC   | MAF  |

|---|---------|------|-------|------|

|   | Input A | 1.03 | 1.007 | 1.05 |

| ĺ | Input B | 1.12 | 1.086 | 1.02 |

Figure 4.5: Normalized error of solution X for Input A as a function of size of mantissa in SMVM communication

Figure 4.6: Normalized error of solution X for Input B as a function of size of mantissa in SMVM communication

sages are compressed before sending. After reception, decompression is performed. Table 4.2 shows the compression rates achieved by using two compression algorithms specifically designed for floating point data (FPC and MAF) and one general purpose, dictionary-based compression algorithm (GZIP). As can be seen, none of these algorithms is able to truly understand the data exchanged across nodes. Thus, the compression rates that we obtained are very poor (larger rate than 1.0 means the compressed size is smaller than uncompressed size). In addition, as execution proceeds over multiple iterations, compressibility of the data does not change significantly. Based on the obtained results,

Figure 4.7: Iterations Required as size of mantissa in SMVM communication

Figure 4.8: Iterations Required as size of mantissa in SMVM communication

only lossy compression is meaningful to achieve higher compression rates. In order to apply lossy compression in scientific simulation a criteria of accuracy has to be established. For this test case, the application developers determined a 1% deviation in the final result to be acceptable. The tests of accuracy have been done in order to determine how many low-order bits of every double can be discarded. Our tests show that keeping only 3 bytes of the original double-precision floating point value does still produce an acceptable result. Figure 4.5 and Figure 4.6 show how the normalized error of the resulting array changes with the precision of the mantissa. The results are obtained by using the

GNU Multiple Precision Floating-Point Reliably (MPFR) library 6 to emulate different precisions in floating point data. MPFR applies rounding when reducing the precision, meaning that these results are not based on a simple mantissa cut. When reducing the precision we need to be careful with the effects on the latency of the CG kernel. It is known that reducing precision can result in an increase of the number of iterations necessary for algorithm convergence. This increase in the number of iterations can easily offset the gains obtained thanks to compression. As we can see in Figure 4.7 and Figure 4.8 for our test cases the number of iterations until convergence increases by only 1% even when precision of mantissa is low. Another interesting effect that can be observed is that as more processors are added, more bits of mantissa are required so that the final solution of the system converges and satisfies the criteria of accuracy (1% normalized error - maximum error compared to double precision). This happens because the number of frontiers exchanged between processes increases and, therefore, discarding bits of the mantissa has more influence on the final result.

#### Performance result using lossy compression with 1 process per node configuration

Figure 4.9: Profile of Alya CG Input A kernel with 1 process per node

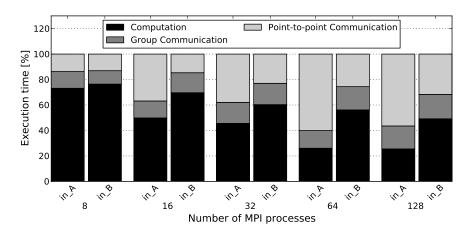

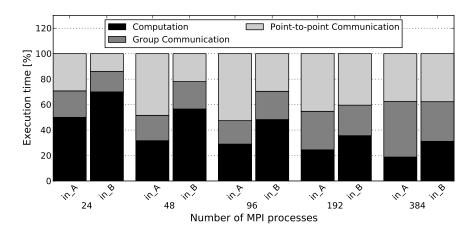

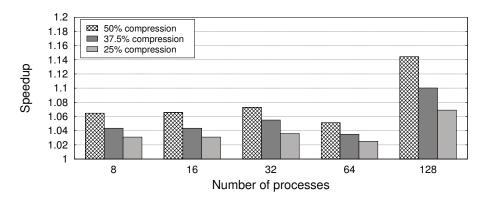

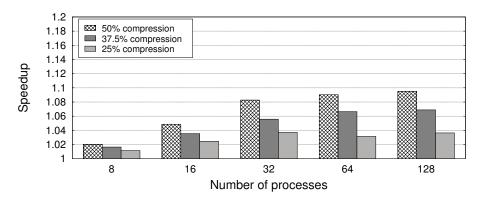

Figure 4.10: Profile of Alya CG Input B kernel with 1 process per node