# DEVELOPMENT OF LOW-COST AND HIGH-EFFICIENCY COMMERCIAL SIZE N-TYPE SILICON SOLAR CELLS

A Dissertation Presented to The Academic Faculty

by

Kyung Sun Ryu

In Partial Fulfillment

of the Requirements for the Degree

Doctor of Philosophy in the

School of Electrical and Computer Engineering

Georgia Institute of Technology August 2015

Copyright © 2015 by Kyung Sun Ryu

# DEVELOPMENT OF LOW-COST AND HIGH-EFFICIENCY COMMERCIAL SIZE N-TYPE SILICON SOLAR CELLS

#### Approved by:

Dr. Ajeet Rohatgi, Advisor School of Electrical and Computer Engineering Georgia Institute of Technology

Dr. Thomas K. Gaylord School of Electrical and Computer Engineering Georgia Institute of Technology

Dr. Miroslav M. Begovic Department of Electrical and Computer Engineering Texas A&M University Dr. Gee-Kung Chang School of Electrical and Computer Engineering Georgia Institute of Technology

Dr. Shreyes N. Melkote School of Mechanical Engineering Georgia Institute of Technology

Date Approved: May 4th, 2015

| This thesis work is dedicated to my parents Jae Man Ryu and Sun Ja Yeon, my brother                                                                        |

|------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Joong Sun Ryu, my wife Aekyung Jung, and my daughter Claire Dain Ryu. This work would have been incomplete without their encouragement, support, and love. |

|                                                                                                                                                            |

|                                                                                                                                                            |

|                                                                                                                                                            |

#### **ACKNOWLEDGEMENTS**

I would like to express my sincere gratitude to my advisor Dr. Ajeet Rohatgi for supervising my Ph.D. study and giving me the opportunity to conduct this study in the School of Electrical and Computer Engineering at Georgia Institute of Technology. I really appreciate his valuable advising and mentoring on my research. He has also spent much time in helping me to improve writing and presentation skills and to grow as a scientist.

I also would like to thank to Dr. Thomas K. Gaylord, Dr. Miroslav M. Begovic, Dr. Gee-Kung Chang, and Dr. Shreyes Melkote for serving as my thesis reading committee and giving advice on my thesis.

I acknowledge the gratitude to former and current colleagues at University Center of Excellence for Photovoltaics Research and Education (UCEP). Special thanks to Dr. Young-Woo Ok and Ajay Upadhyaya for their guidance, support, and valuable discussions. I am also grateful to James Keane, and Francesco Zimbardi for their extensive and professional assistance with equipment maintenance, to Carla East for providing an excellent administrative support and motherly affection, to Vijay Upadhyaya, Brian Rounsaville, and Elizabeth Lori Chang for their active support and cooperation and discussions in research. Thanks to Dr. Abasifreke Ebong, Dr. Ian Cooper, Dr. Rishi Ramanathan, Dr. Moon-Hee Kang, Dr. John Renshaw, Dr. Jiun-Hong Lai, Chia-Wei (Ricky) Chen, Eunhwan Cho, and Keeya Madani for their true relationship and generous support. Special thanks to Keith Tate, Dr. Manav Sheoran, and Dr. Arnab Das for their training and valuable discussions during early year of my Ph.D.

I would also like to thank to Suniva members (Dr. Atul Gupta, Dr. Adam Payne, Dr. Vijay Yelunder, Vinodh Chandrasekaran, Preston Davis, Liladhar Dahal) for their generous support and cooperation in my research.

#### **TABLE OF CONTENTS**

|                                                            | Page  |

|------------------------------------------------------------|-------|

| ACKNOWLEDGEMENTS                                           | iv    |

| LIST OF TABLES                                             | xii   |

| LIST OF FIGURES                                            | xiv   |

| LIST OF SYMBOLS AND ABBREVIATIONS                          | xix   |

| SUMMARY                                                    | xxii  |

| CHAPTER 1: INTRODUCTION                                    | 1     |

| 1.1 Statement of the Problem                               | 1     |

| 1.2 Motivation                                             | 4     |

| 1.3 Thesis Objectives                                      | 7     |

| CHAPTER 2: BASIC OPERATION AND FUNDAMENTAL PHYSICS OF      | SOLAR |

| CFELLS                                                     | 13    |

| 2.1 Basic Operation and Equivalent Circuit of a Solar Cell | 13    |

| 2.2 Solar Cell Parameters                                  | 15    |

| 2.3 Losses in Si Solar Cells                               | 19    |

| 2.3.1 Reflection Loss                                      | 20    |

| 2.3.2 Shading Loss                                         | 22    |

| 2.3.3 Incomplete Absorption                                | 22    |

| 2.3.4 Resistive Losses                                     | 23    |

| 2.3.5 Recombination Loss                                   | 25    |

| CHAPTER 3: LITERATURE REVIEW OF N-TYPE SOLAR CELLS 31                                                  |

|--------------------------------------------------------------------------------------------------------|

| 3.1 History of N-type Silicon Solar Cells                                                              |

| 3.2 Investigation of Promising Technologies for Boron Emitter Formation                                |

| 3.2.1 Boron Tribromide (BBr <sub>3</sub> ) Diffusion                                                   |

| 3.2.2 Boron Diffusion by Spin Coating of Boric Acid Source                                             |

| 3.2.3 Ion implantation                                                                                 |

| 3.2.4 Boron Emitter Formation by Inkjet and Screen Printing                                            |

| 3.2.5. Atmospheric Pressure Chemical Vapor Deposition (APCVD)                                          |

| 3.3 Understanding of Boron Rich Layer (BRL)                                                            |

| 3.4 Review of Dielectric Layers for Passivating Boron Emitter Surfaces                                 |

| 3.5 A Review of Various Promising N-type Silicon Solar Cell Structures                                 |

| 3.5.1 N-type Si Solar Cell with Screen-printed Aluminum-alloyed Rear Emitter 41                        |

| 3.5.2 N-type Front Junction Si Solar Cells with Al <sub>2</sub> O <sub>3</sub> Passivated B Emitter 42 |

| 3.5.3 Interdigitated back Contact Silicon Solar Cell                                                   |

| 3.5.4 Rationale of Selecting PERT Cell Structure in This Thesis                                        |

| CHAPTER 4: INVESTIGATION AND DEVELOPMENT OF A NOVEL BORON-                                             |

| DOPED EMITTER FORMED BY INKJET PRINTING AND ITS SURFACE                                                |

| PASSIVATION PROPERTIES46                                                                               |

| 4.1 Modeling of N-type PERET Solar Cell to Establish Material and Device Parameters                    |

| for Attaining ≥21% Efficiency                                                                          |

| 4.2 Formation and Analysis of Doping Profiles of Inkjet Printed Boron Emitters 48                      |

| 4.3 J <sub>0e</sub> Study of Boron-doped Inkjet Emitters Passivated by SiN <sub>x</sub> Antireflection Coatin |

|---------------------------------------------------------------------------------------------------------------|

|                                                                                                               |

| 4.4 The Impact of BRL on J <sub>0e</sub> .                                                                    |

| 4.5 Summary                                                                                                   |

| CHAPTER 5: INVESTIGATION AND UNDERSTANDING OF PROCESS                                                         |

| INDUCED BULK LIFETIME IN N-TYPE SILICON WAFERS 5                                                              |

| 5.1 Solar Cell Modeling to Establish Bulk Lifetime and Resistivity Requirements for                           |

| Achieving 21% Efficiency5                                                                                     |

| 5.2 Effect of Inkjet Boron Diffusion Process on Bulk Lifetime of N-type Si Wafer 5                            |

| 5.3 Effect of BRL Removal by Oxidation on Bulk Lifetime                                                       |

| 5.4 Summary                                                                                                   |

| CHAPTER 6: DEVELOPMENT OF A RAPID CHEMICAL ETCHING PROCES                                                     |

| FOR BRL REMOVAL AND SUBSEQUENT SURFACE PASSIVATION FOR                                                        |

| HIGH BULK LIFETIME, LOW Joe, AND HIGH EFFICIENCY 6                                                            |

| 6.1 Impact of BRL Removal by Chemical Etching and Subsequent Passivation on Jo                                |

| Bulk Lifetime, and Cell Efficiency                                                                            |

| 6.2 Internal Quantum Efficiency (IQE) Analysis to Validate the J <sub>0e</sub> and Cell Efficience            |

| for Various Passivation Schemes                                                                               |

| 6.3 Detailed Understanding of the BRL and the Si Interface by Transmission Electron                           |

| Microscopy (TEM)                                                                                              |

| 6.4 Investigation of the BRL at the Si Interface by Auger Electron Spectroscopy (AES                          |

| 7                                                                                                             |

| 6.5 Analysis of the 19.0% N-type PERT Solar Cell                                                              |

| 6.6 Summary                                                                                |

|--------------------------------------------------------------------------------------------|

| CHAPTER 7: TECHNOLOGY DEVELOPMENT AND FABRICATION OF HIGH                                  |

| EFFICIENCY N-TYPE COMMERCIAL SIZE SILICON SOLAR CELLS WITH                                 |

| FOUR PROMISING B EMITTER TECHNOLOGIES79                                                    |

| 7.1 Four Promising Technologies for Boron Emitter Formation                                |

| 7.2 Advanced Process Development for N-type PERT Solar Cell for Higher Efficiency          |

|                                                                                            |

| 7.3 Advantages of the Above Advanced Manufacturing Process for N-type PERT Cell            |

| 84                                                                                         |

| 7.4 ≥20% N-type PERT Solar Cells with Different B Emitter Technologies                     |

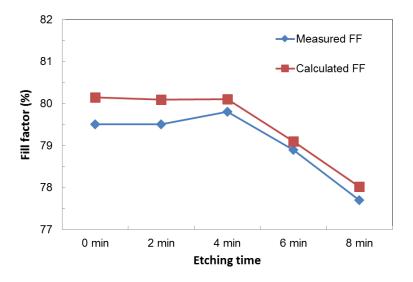

| 7.5 The Optimization of Chemical Etching Process for BRL Removal for Each B                |

| Diffusion Technology87                                                                     |

| 7.6 The Impact of Chemical Etching of BRL on the IQE of N-type PERT Solar Cell. 89         |

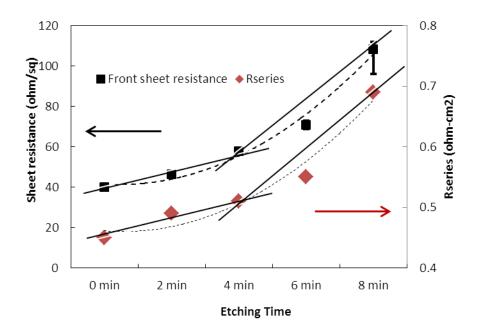

| 7.7 The Impact of Over Etching of BRL on N-type Solar Cell Parameters                      |

| $7.8$ Quantitative Impact of Increased $R_s$ and n-factor on FF due to BRL over Etching.93 |

| 7.9 Optimization of Chemical Etching Time for Each Boron Technology                        |

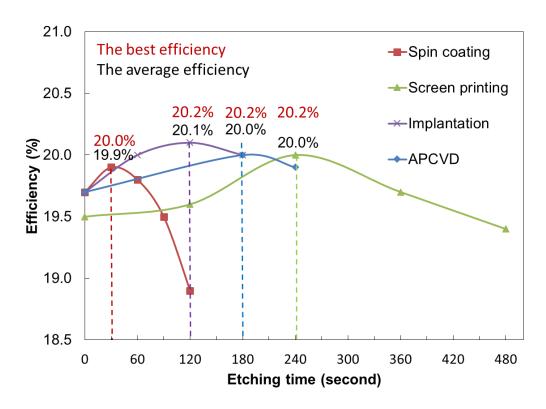

| $7.10$ Investigation of $J_{0e}$ and Bulk Lifetime of the N-type PERT Solar Cells with     |

| Different B Emitter Technologies                                                           |

| 7.11 Summary                                                                               |

| CHAPTER 8: TECHNOLOGY DEVELOPMENT AND OPTIMIZATION OF                                      |

| METALLIZATION FOR ACHIEVING ~21% EFFICIENT N-TYPE PERT CELL                                |

|                                                                                            |

| 8.1 Analytical Model for Optimizing the Front Gird Design to Reduce $R_s$ and Increase              |

|-----------------------------------------------------------------------------------------------------|

| Fill Factor                                                                                         |

| 8.1.1 Series Resistance (R <sub>s</sub> ) Optimization                                              |

| $8.1.2$ Calculation of the Impact of Number of Busbars and Fingers on $J_{sc}$ , $V_{oc}$ , FF, and |

| Efficiency. 106                                                                                     |

| 8.1.3 Application of the Optimized Front Grid Design with Five Busbars to Achieve                   |

| 20.4% N-type PERT Cell                                                                              |

| 8.2 Formation of Rear Point Contacts Formed by Laser Opening and Physical Vapor                     |

| Deposition of Al to Reduce Contact Recombination                                                    |

| 8.2.1 Fabrication of N-type PERT Cell with Rear Contacts Formed by Laser Opening                    |

| and PVD Al112                                                                                       |

| 8.3 Application of Floating Busbar to Improve V <sub>oc</sub>                                       |

| 8.4 Summary                                                                                         |

| CHAPTER 9: QUANTITATIVE UNDERSTANDING AND IMPACT OF EACH                                            |

| TECHNOLOGY ENHANCEMENT ON CELL PARAMETERS AND                                                       |

| EFFICIENCY THROUGH DETAILED MODELING AND                                                            |

| CHARACTERIZATION 122                                                                                |

| 9.1 Summary of Technology Enhancements that Raised the N-PERT Cell Efficiency                       |

| from 17.4% to ~21%                                                                                  |

| 9.2 Characterization Modeling and Analysis of 17.4% to 21% N-PERT Cells Fabricated                  |

| in This Thesis                                                                                      |

| 9.3 Summary                                                                                         |

| CHAPTER 10: FUTURE WORK                                                                             |

| 10.1 Implementation of Selective Emitters                            | 131            |

|----------------------------------------------------------------------|----------------|

| 10.2 Boron Emitter Surface Passivation by a Negatively Charged Alumi | num Oxide Film |

|                                                                      | 134            |

| REFERENCES                                                           | 137            |

| PUBLICATIONS FROM THIS WORK                                          | 145            |

| VITA                                                                 | 147            |

### LIST OF TABLES

| Page                                                                                                     |

|----------------------------------------------------------------------------------------------------------|

| Table 4.1 Input parameters of n-type PERT cells for PC1D modeling                                        |

| Table 5.1 Input parameters of n-type Si solar cells for PC1D simulation                                  |

| Table 6.1 $J_{0e}$ values and cell efficiencies with different passivation scheme                        |

| Table 7.1 Efficiencies of n-type solar cells formed by different B technologies                          |

| Table 7.2 <i>I-V</i> of n-type PERT solar cells with B emitter formed by different technologies.         |

|                                                                                                          |

| Table 7.3 Summary of I-V results of screen-printed B n-type solar cells with different                   |

| chemical etching time                                                                                    |

| Table 7.4 Comparison of key parameters of the implanted 20.1% cell and the 21%                           |

| simulated cell. 98                                                                                       |

| Table 8.1 Expression of six series resistance components for a ion-implanted n-type PERT                 |

| cell                                                                                                     |

| Table 8.2 Experimentally measured parameters of the 20.1% ion-implanted n-type PERT                      |

| cell                                                                                                     |

| Table 8.3 Calculated $R_s$ and its $R_s$ components for different number of busbars and fingers.         |

|                                                                                                          |

| Table 8.4 Calculated $J_0$ , $J_{sc}$ , $V_{oc}$ , FF, and efficiency for different number of busbar and |

| finger based on the 20.1% reference cell                                                                 |

| Table 8.5 <i>I-V</i> results of n-type PERT solar cells with 3 busbars and 5 busbars                     |

| Table 8.6 Summary of <i>I-V</i> results for n-type PERT cell with laser opening and PVD Al on            |

| the rear metal contacts                                                                                  |

| Table 8.7 List of commercial grade large area n-type silicon solar cells fal           | oricated using |

|----------------------------------------------------------------------------------------|----------------|

| various processing techniques                                                          | 115            |

| Table 8.8 Summary of <i>I-V</i> results for nPERT with floating busbars                | 120            |

| Table 9.1 PC1D modeling of the nPERT cells from baseline to 5 <sup>th</sup> generation | n 128          |

### LIST OF FIGURES

| Page                                                                                        |

|---------------------------------------------------------------------------------------------|

| Figure 1.1 Fossil fuel consumption and carbon dioxide ( $CO_2$ ) concentration in the air 1 |

| Figure 1.2 United States energy consumption in 2013                                         |

| Figure 1.3 LCOE contour plot for Atlanta area as a function of module cost and module       |

| efficiency with a BOS cost of \$2/W. Assumption for the chart :25 year lifetime:            |

| 20% derated: 7.69% WACC, No ITC, 50% debt fraction, 7% loan rate, and 5                     |

| year loan term                                                                              |

| Figure 1.4 Predicted increase in the market share of n-type mono-Si solar cells 5           |

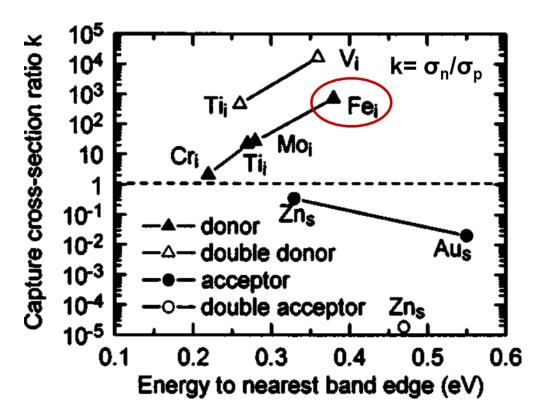

| Figure 1.5 Capture cross-section of metal impurities. 6                                     |

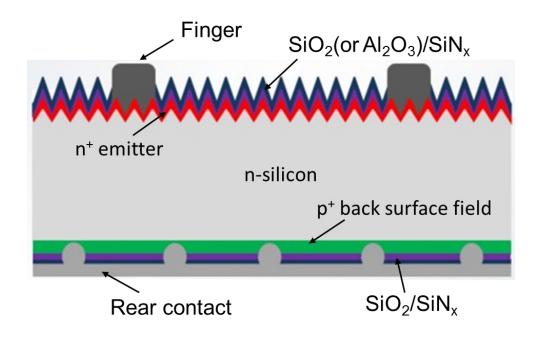

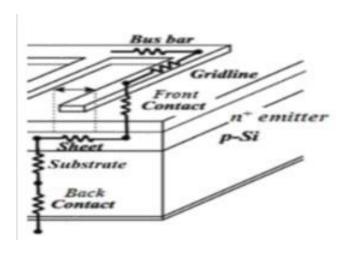

| Figure 1.6 Structure of a screen-printed PERT n-type Si solar cell                          |

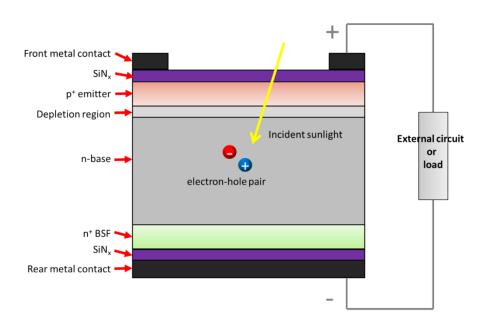

| Figure 2.1 A structure of a simple n-type Si solar cell and its basic operation             |

| Figure 2.2 Equivalent circuit of a p-n junction solar cell                                  |

| Figure 2.3 I-V characteristics of a solar cell. 16                                          |

| Figure 2.4 Losses in a Si solar cell                                                        |

| Figure 2.5 Anti-reflection coating to reduce the surface reflection                         |

| Figure 2.6 Incident light on flat Si surface and textured Si surface                        |

| Figure 2.7 Light trapping in solar cell to increase the optical path length                 |

| Figure 2.8 Series resistance components in a Si solar cell                                  |

| Figure 2.9 Energy band diagram of radiative recombination                                   |

| Figure 2.10 Energy band diagram of auger recombination                                      |

| Figure 2.11 Energy band diagram of SRH recombination                                        |

| Figure 2.12 Schematic of recombination at Si surface. 28                                    |

| Figure 2.13 Schematic of chemical passivated Si surface.                                    |

| Figure 2.14 Schematic of band diagrams for (a) a positively charged dielectric on n-type          |

|---------------------------------------------------------------------------------------------------|

| Si and (b) a negatively charged dielectric on p-type Si                                           |

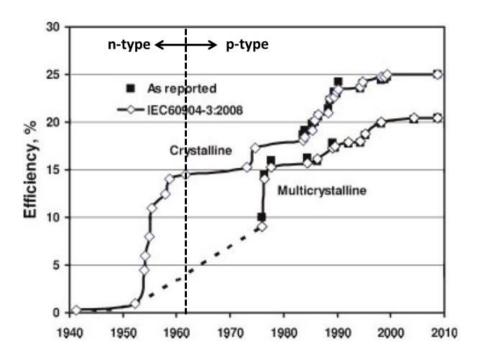

| Figure 3.1 Evolution of crystalline and multicrystalline silicon solar cell efficiency 31         |

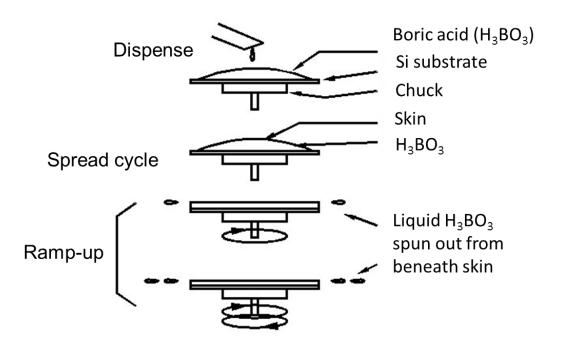

| Figure 3.2 Schematic of spin coating process for boron diffusion                                  |

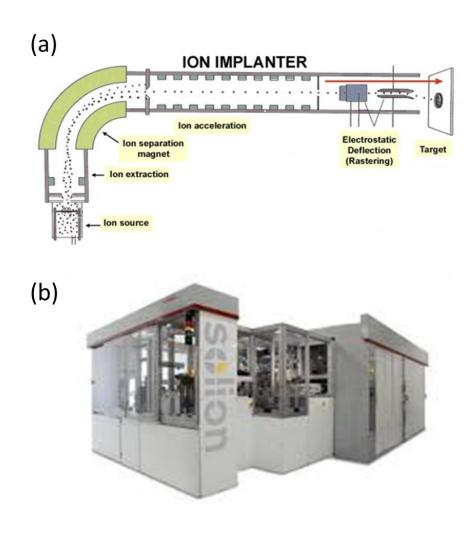

| Figure 3.3 (a) Schematic diagram of ion implant system and (b) Varian Solion implanter.           |

|                                                                                                   |

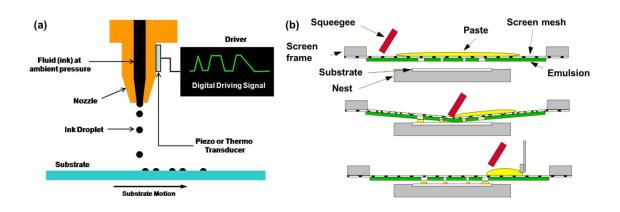

| Figure 3.4 Schematic diagram of boron source deposition by (a) Inkjet printer and (b)             |

| Screen printer                                                                                    |

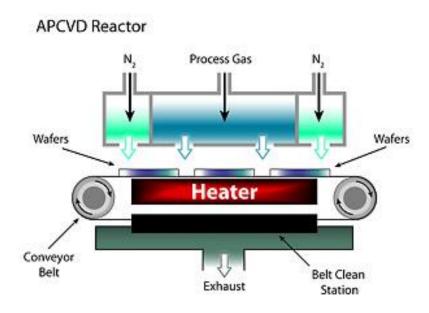

| Figure 3.5 Schematic diagram of APCVD system for B-doped film deposition 38                       |

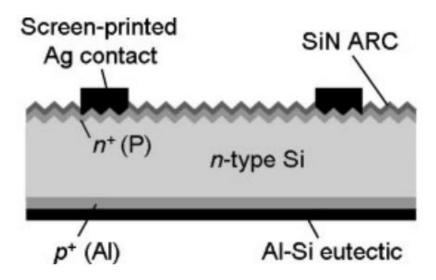

| Figure 3.6 Schematic of n+np+ solar cell with screen-printed aluminum-alloyed rear                |

| junction                                                                                          |

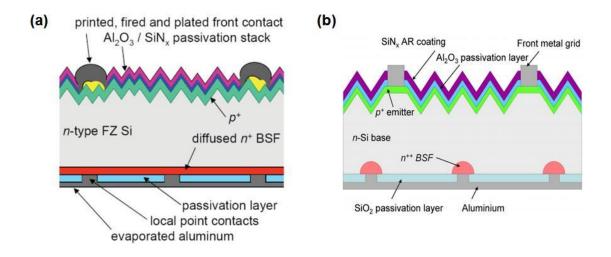

| Figure 3.7 Schematic diagram of n-type (a) PERT and (b) PERL Si solar cell                        |

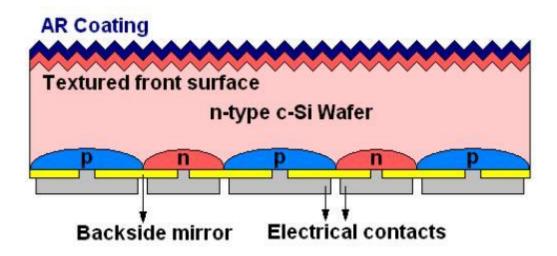

| Figure 3.8 Schematic diagram of interdigitated back contact n-type solar cell 44                  |

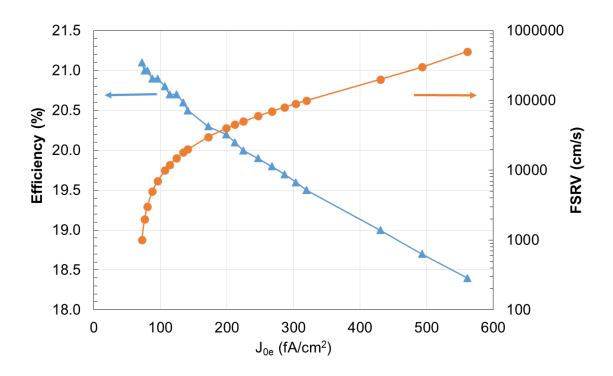

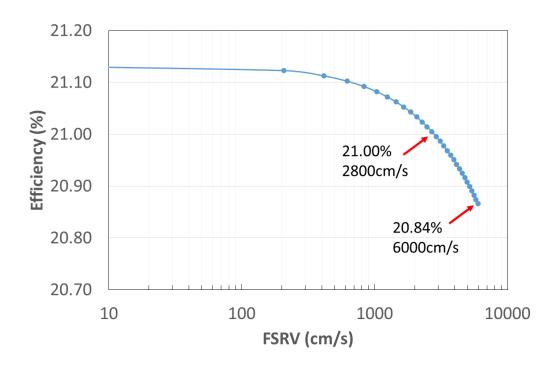

| Figure 4.1 PC1D modeling of n-type solar cell efficiency as a function of $J_{0e}$ and FSRV.      |

| 48                                                                                                |

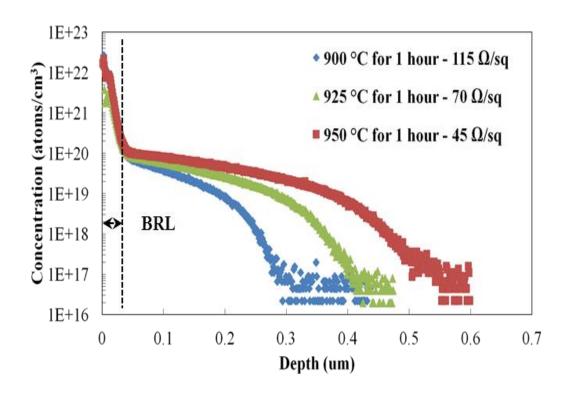

| Figure 4.2 Sheet resistance and SIMS data for boron concentration profiles annealed at            |

| different temperature                                                                             |

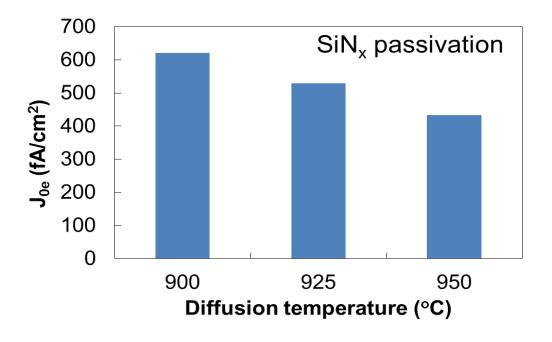

| Figure 4.3 Schematic diagram of J <sub>0e</sub> sample structure                                  |

| Figure 4.4 $J_{0e}$ values of $SiN_x$ capped inkjet B emitter annealed at different temperatures. |

|                                                                                                   |

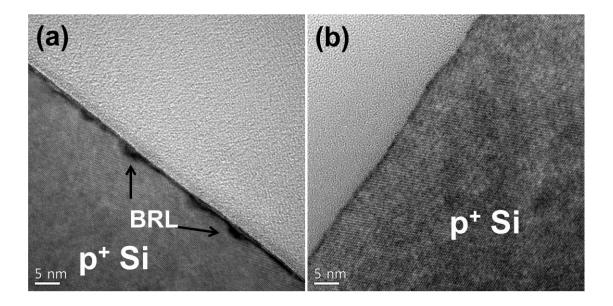

| Figure 4.5 TEM images of cross-section of inkjet-printed boron emitter (a) Before                 |

| oxidation and (b) After oxidation53                                                               |

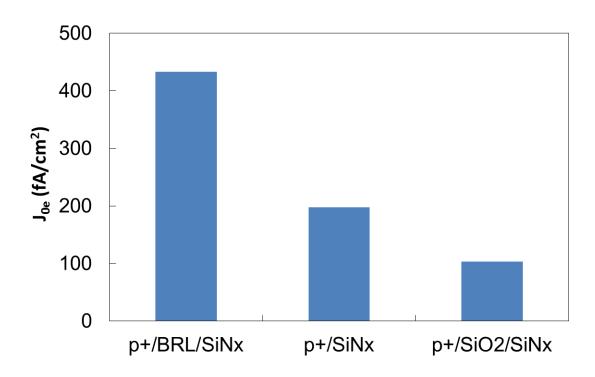

| Figure 4.6 $J_{0e}$ values of B emitter (p <sup>+</sup> ) capped with BRL/SiN <sub>x</sub> , SiN <sub>x</sub> only, and SiO <sub>2</sub> /SiN <sub>x</sub> |

|------------------------------------------------------------------------------------------------------------------------------------------------------------|

| layer                                                                                                                                                      |

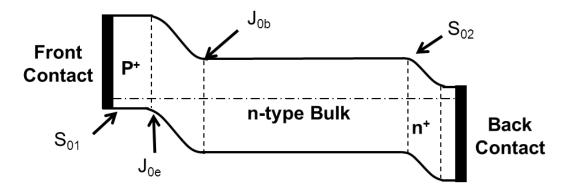

| Figure 5.1 Energy band diagram of a n-type solar cell                                                                                                      |

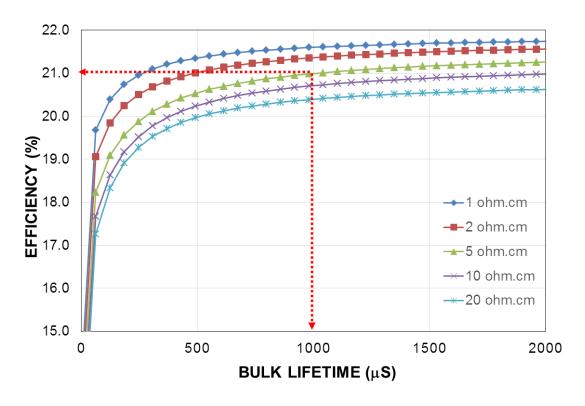

| Figure 5.2 PC1D modeling of n-type solar cell efficiency as a function of bulk lifetime and                                                                |

| resistivity59                                                                                                                                              |

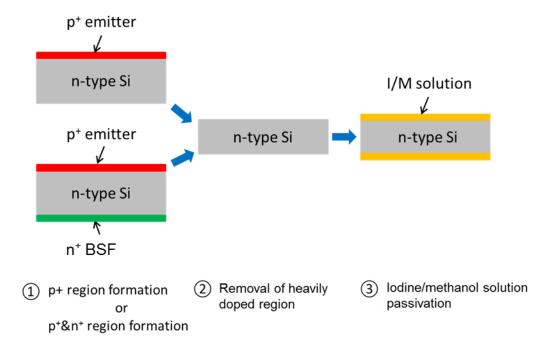

| Figure 5.3 Process sequence of sample preparation for process-induced bulk lifetime                                                                        |

| measurements61                                                                                                                                             |

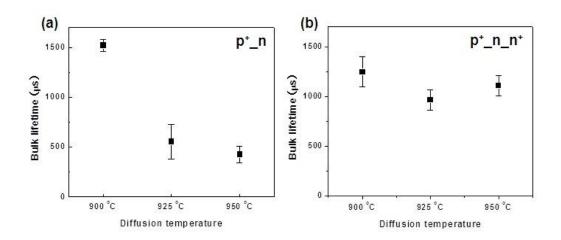

| Figure 5.4 Bulk lifetime in (a) $p+/n$ and (b) $p^+/n/n^+$ structures formed by annealing in the                                                           |

| temperature range of 900 °C to 950 °C                                                                                                                      |

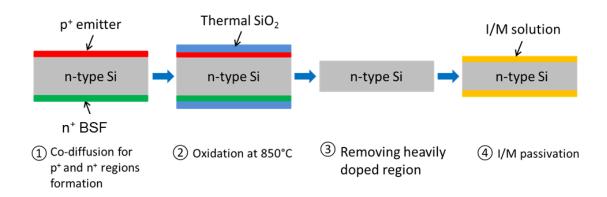

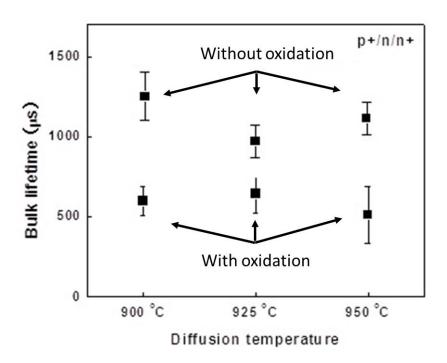

| Figure 5.5 Process sequence studying for post-diffusion oxidation induced lifetime 63                                                                      |

| Figure 5.6 Bulk lifetime of $p^+/n/n^+$ structures before and after a thermal oxidation step after                                                         |

| co-diffusion. 64                                                                                                                                           |

| Figure 6.1 (a) Schematic diagram (a) experimental plan and (b) structure of $J_{0e}$ sample. 68                                                            |

| Figure 6.2 Schematic diagram of (a) experimental plan and (b) structure of n-type solar                                                                    |

| cell69                                                                                                                                                     |

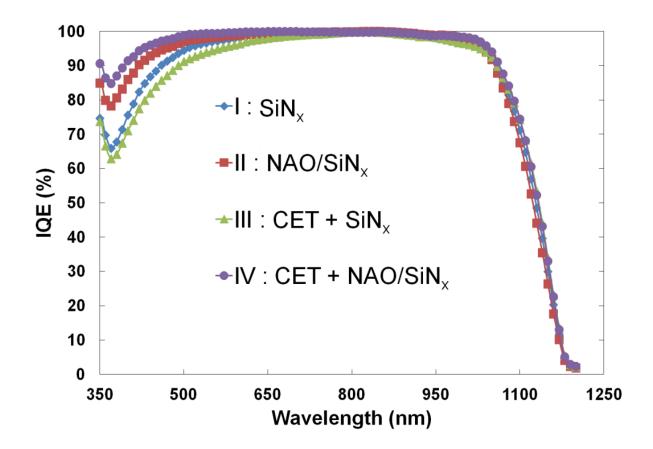

| Figure 6.3 IQE data of the n-type Si solar cell by using different passivation process of                                                                  |

| group I – IV                                                                                                                                               |

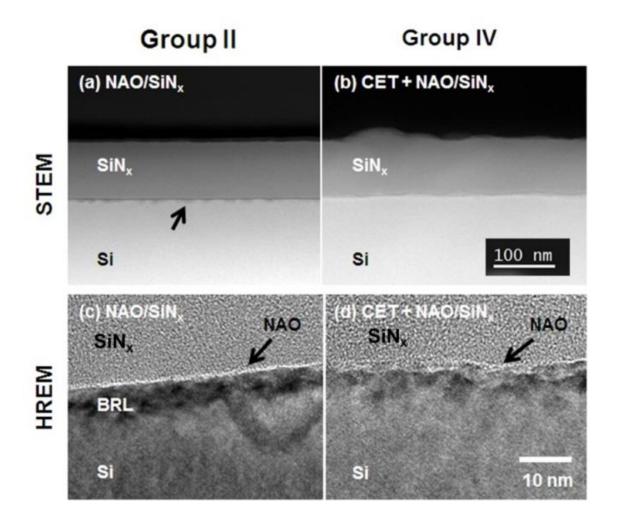

| Figure 6.4 STEM and HREM images obtained from the symmetric NAO/SiNx passivated                                                                            |

| boron emitter (SiNx-NAO-p+-n-p+-NAO-SiNx) structure : (a) STEM of                                                                                          |

| NAO/SINx passivated p+ emitter with BRL, (b) STEM of NAO/SiNx                                                                                              |

| passivated p+ emitter with BRL removed, (c) HREM of NAO/SiNx passivated                                                                                    |

| p+ emitter with BRL, and (d) HREM of NAO/SiNx passivated p+ emitter with                                                                                   |

| BRI removed 74                                                                                                                                             |

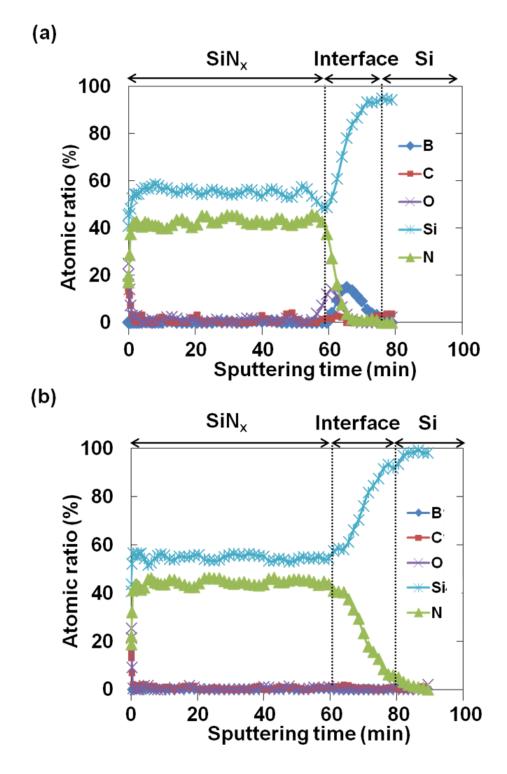

| Figure 6.5 AES depth profiling analysis measured from the symmetric structure sample in                        |

|----------------------------------------------------------------------------------------------------------------|

| (a) group II and (b) group IV76                                                                                |

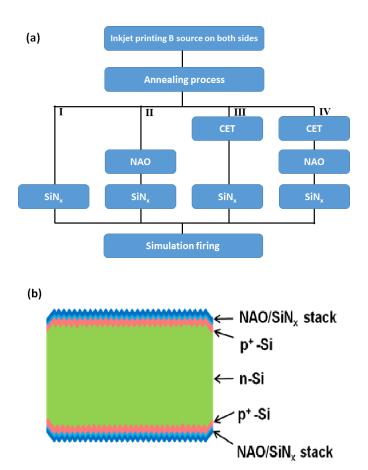

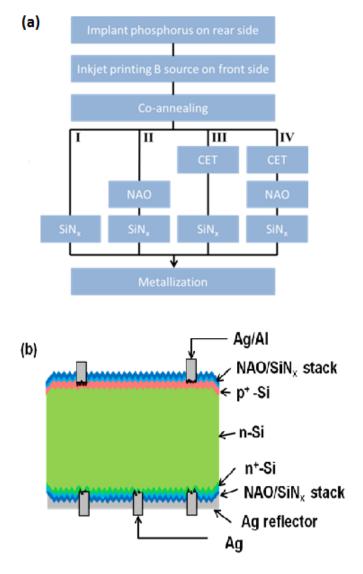

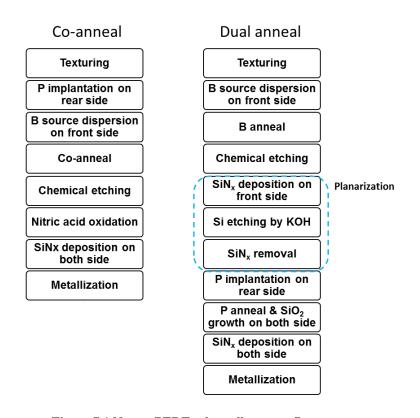

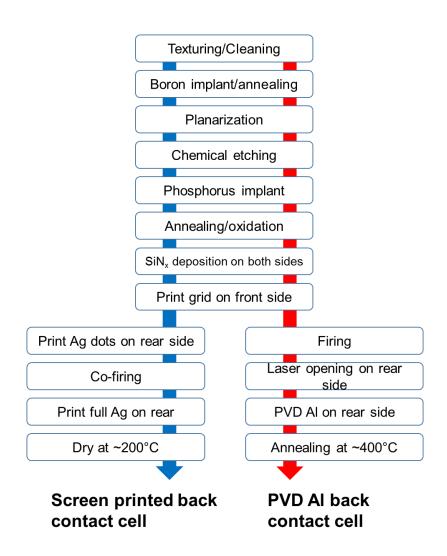

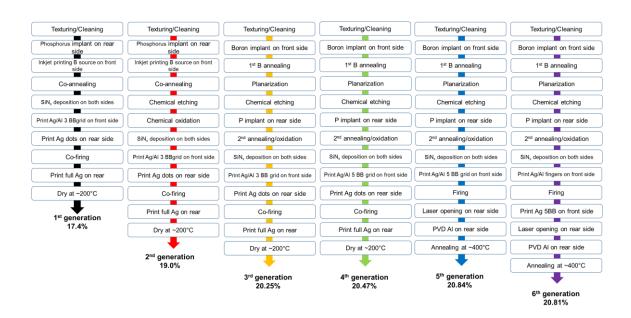

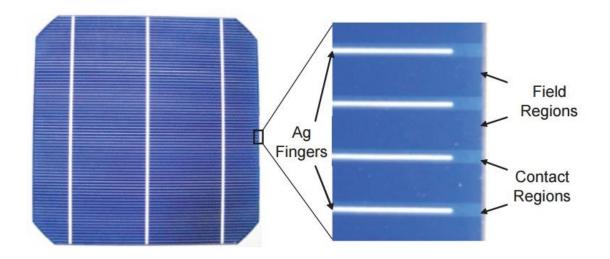

| Figure 7.1 N-type PERT solar cell process flows.                                                               |

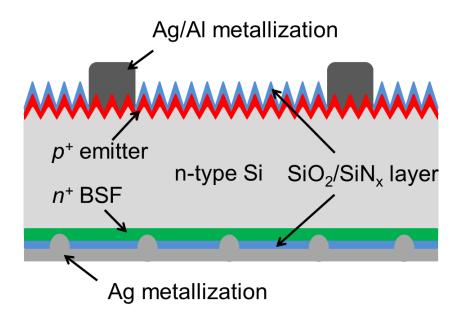

| Figure 7.2 Schematics of n-type PERT solar cell structure.                                                     |

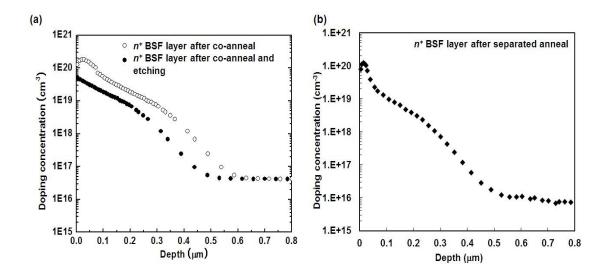

| Figure 7.3 Phosphorus doping concentration after (a) co-anneal and (b) dual anneal process                     |

| 85                                                                                                             |

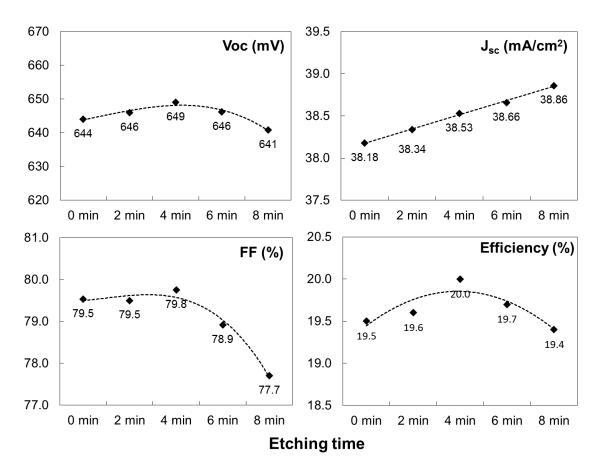

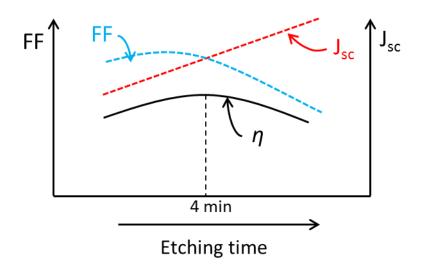

| Figure 7.4 <i>I-V</i> results of n-type cells with screen-printed B emitter as a function of etching           |

| time                                                                                                           |

| Figure 7.5 Diagram of changes in cell performance with the increased etching time 89                           |

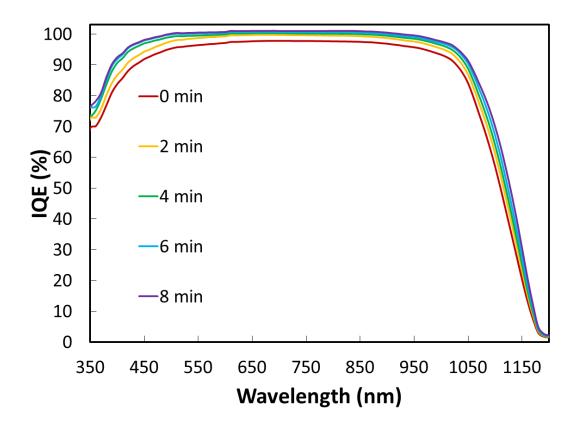

| Figure 7.6 IQE response of n-type solar cell with the increased etching time 90                                |

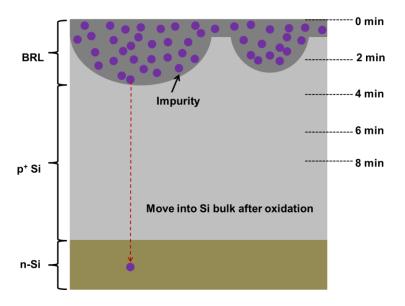

| Figure 7.7 The chemical etching of BRL and B emitter formed by the screen printing                             |

| technique91                                                                                                    |

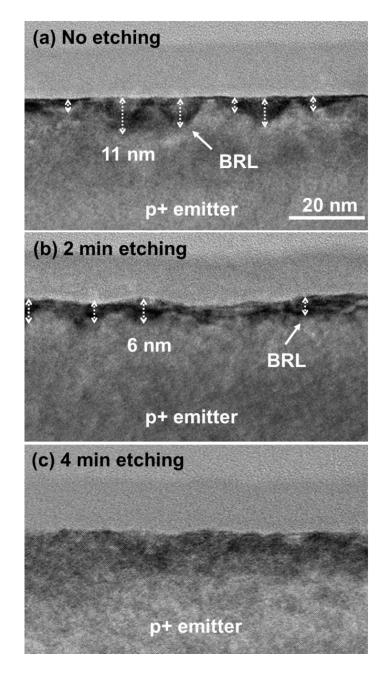

| Figure 7.8 TEM images of cross section of boron diffused Si with different etching times                       |

| for (a) 0 min, (b) 2min, and (c) 4min                                                                          |

| Figure 7.9 B emitter sheet resistance and $R_{\text{s}}$ of n-type solar cells as a function of etching        |

| time                                                                                                           |

| Figure 7.10 Comparison between the measured and calculated fill factor                                         |

| Figure 7.11 Efficiency trends of four different B technologies as a function of etching time.                  |

| 96                                                                                                             |

| Figure 7.12 (a) $J_{0e\text{-pass}}$ of each B emitter passivated by $SiO_2/SiN_x$ stack and (b) bulk lifetime |

| of n-type Si wafer with $1^{st}$ anneal for each B diffusion, $2^{nd}$ anneal, and $\text{SiN}_x$              |

| passivation, and simulation firing                                                                             |

| Figure 8.1 Components of series resistance of solar cell                                                       |

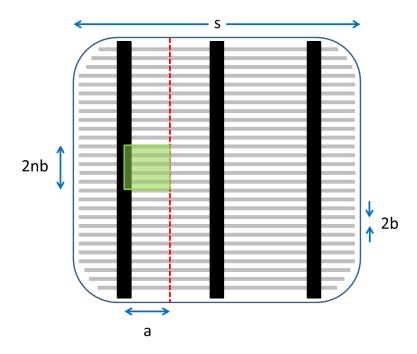

| Figure 8.2 Diagram of an industrial solar cell with three busbar. Green square represents                                    |

|------------------------------------------------------------------------------------------------------------------------------|

| the unit cell for the analysis.                                                                                              |

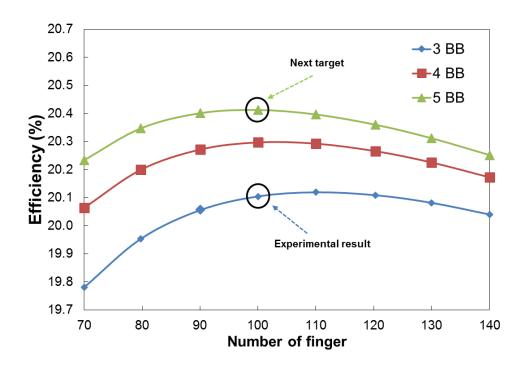

| Figure 8.3 Calculated cell efficiencies with different number of busbars and fingers 110                                     |

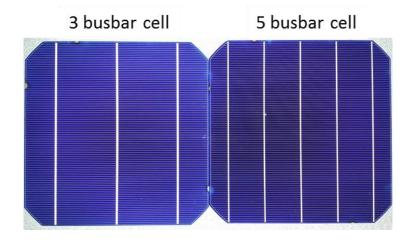

| Figure 8.4 The front grid patterns with (left) 1.5mm wide 3 busbars and (right) 0.9mm wide                                   |

| 5 busbars                                                                                                                    |

| Figure 8.5 Comparison of process flow for the rear contacts formed by screen-printing and                                    |

| physical vapor deposition (PVD) Al                                                                                           |

| Figure 8.6 Schematic structure of (a)Fire-through busbars and (b)Floating busbars 117                                        |

| Figure 8.7 Calculation of V <sub>oc</sub> as a function of total J <sub>0</sub>                                              |

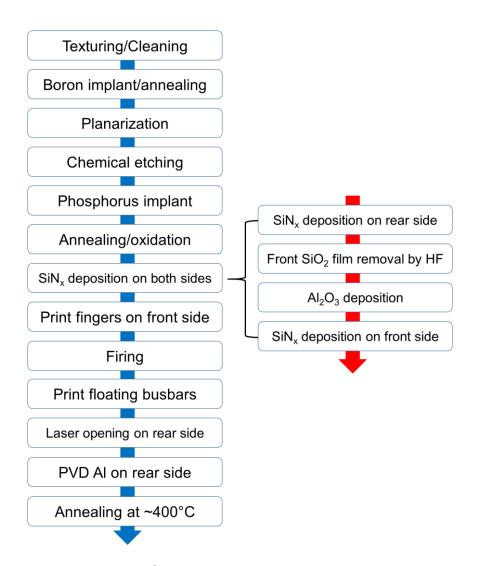

| Figure 8.8 Process flow of nPERT cell with floating busbars                                                                  |

| Figure 9.1 Process flow for nPERT cells of 1 <sup>st</sup> to 6 <sup>th</sup> generation                                     |

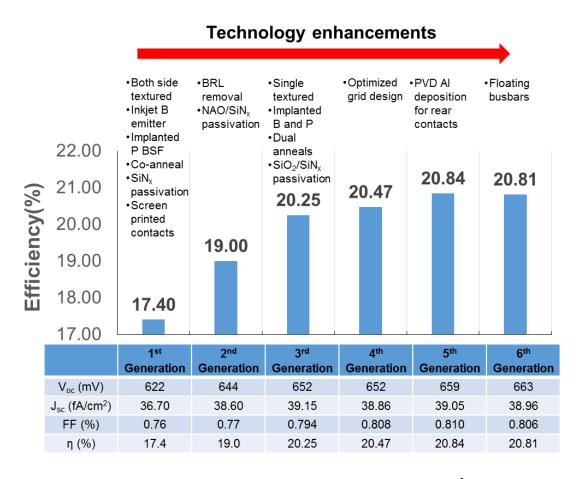

| Figure 9.2 Efficiency roadmap toward ~21% on commercial grade 239 cm <sup>2</sup> Cz Si wafers.                              |

|                                                                                                                              |

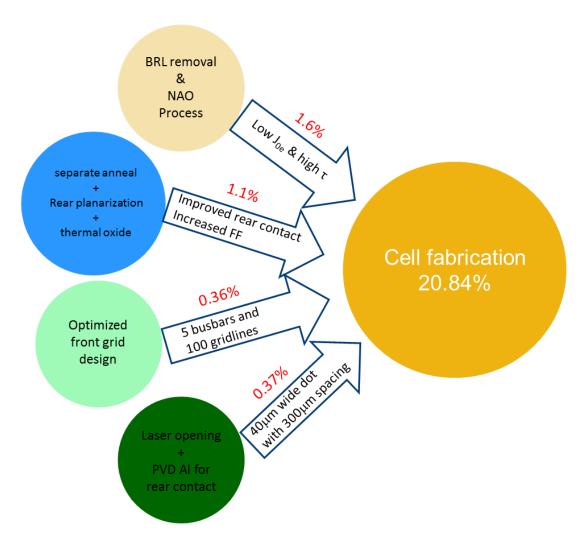

| Figure 9.3 The contribution of each technology enhancement leading to 20.84% efficiency                                      |

| in this thesis                                                                                                               |

| Figure 10.1 Structure of a n-type PERT cell with selective emitters                                                          |

| Figure 10.2 Optical micrograph of an ion-implanted selective emitter solar cell 133                                          |

| Figure 10.3 Modeling of n-type PERT cell efficiency as a function of BSRV 134                                                |

| Figure 10.4 Processing flow of 6 <sup>th</sup> generation cell with Al <sub>2</sub> O <sub>3</sub> /SiNx stack for B emitter |

| surface passivation                                                                                                          |

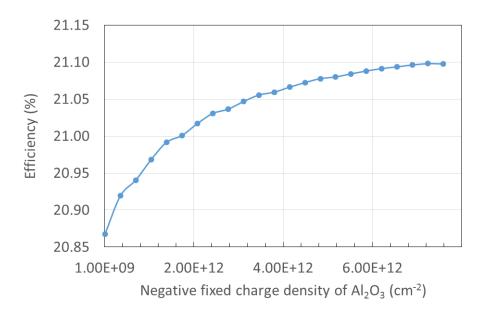

| Figure 10.5 Cell efficiency as a function of negative fixed charge density of Al <sub>2</sub> O <sub>3</sub> 136             |

#### LIST OF SYMBOLS AND ABBREVIATIONS

AES Auger electron spectroscopy

Al<sub>2</sub>O<sub>3</sub> Aluminum oxide

APCVD Atmospheric pressure chemical vapor deposition

ARC Anti-reflection coating

B Boron

BBr<sub>3</sub> Boron tribromide

BOS Balance of system

BRL Boron-rich layer

BSF Back surface field

BSG Borosilicate glass

BSRV Back surface recombination velocity

CET Chemical etching treatment

Cz Czochralski

D<sub>it</sub> Interface state density

EQE External quantum efficiency

FF Fill factor

FSRV Front surface recombination velocity

H<sub>3</sub>BO<sub>3</sub> Boric acid

HIT Heterojunction with Intrinsic Thin layer

HREM High resolution electron microscopy

IBC Interdigitated back contact

IQE Internal quantum efficiency

*I-V* Current-voltage

J<sub>0b</sub> Base saturation current density

$J_{0b\text{-metal}}$   $J_{0b}$  in the metalized emitter surface

$J_{0b\text{-pass}}$   $J_{0b}$  in the passivated emitter area

J<sub>0e</sub> Emitter saturation current density

$J_{0e-metal}$   $J_{0e}$  in the metalized emitter surface

$J_{0e-pass}$   $J_{0e}$  in the passivated emitter area

J<sub>sc</sub> Short-circuit current density

LCOE Levelized cost of electricity

LID Light induced degradation

n<sup>+</sup> Heavily phosphorus doped

n<sub>i</sub> Intrinsic carrier concentration

NAO Nitric acid grown oxide

P Phosphorus

p<sup>+</sup> Heavily boron doped

PC1D Name of one-dimensional device simulation program

PECVD Plasma enhanced chemical vapor deposition

PERL Passivated emitter and rear locally-diffused

PERT Passivated emitter, rear totally-diffused

PV Photovoltaics

PVD Physical vapor deposition

QSSPC Quasi-steady state photoconductance

R<sub>s</sub> Series resistance

R<sub>sh</sub> Shunt resistance

S Surface recombination velocity

Si Silicon

SIMS Secondary ion mass spectroscopy

SiN<sub>x</sub> Silicon nitride

SiO<sub>2</sub> Silicon oxide

SRH Shockley-Read-Hall

STEM Scanning transmission electron microscopy

TEM Transmission electron microscopy

UV Utraviolet

$\Delta n$  Injection level

η Energy conversion efficiency

τ<sub>bulk</sub> Bulk lifetime

$\tau_{eff}$  Effective minority carrier lifetime

#### **SUMMARY**

Photovoltaics (PV) is one of the most promising candidate for sustainable energy source because sunlight is free, essentially unlimited, and not localized in any part of the world. In addition, PV is environmentally friendly and a non-polluting energy source. Even though levelized cost of electricity (LCOE) from PV has come down by a factor of five since 1998, PV accounts for only less than 0.2% of total energy consumed in United States due to a higher LCOE (~\$0.15/kWh) compared to fossil fuel (≤\$0.1/kWh). Therefore, it is necessary to further reduce the cost of modules as well as balance of system (BOS) to attain grid parity for mass adoption of PV.

The PV module price can be reduced by reducing module material and manufacturing cost and by increasing solar cell efficiency. Solar cell efficiency is the most effective way to reduce the PV system cost because higher efficiency not only reduces the amount of material and the number of cells or modules required to produce a given power but also it reduces the BOS cost by shrinking the footprint of the PV system. Since n-type Si has the potential for higher stabilized efficiency, the overall objective of this thesis is to produce ~ 21% n-type manufacturable PERT (passivated emitter, rear totally-diffused) Si solar cells at low-cost. However, there are several challenges that need to be overcome in order to accomplish this goal. The challenges provided the motivation to explore various B diffusion technologies in this thesis and develop process and dielectric stack combination to passivate its surface to minimize boron emitter recombination. In addition, a detailed study of the BRL layer is conducted to understand its role and mitigate or eliminate its negative impact on surface passivation and bulk lifetime. Finally, optimization of cell design and technology development is carried out using production tools to achieve

commercial ready cell efficiencies approaching 21% on large area (239 cm²) commercial grade n-type Cz Si wafers.

Chapter 2 deals with the fundamental physics and the optical/electrical loss mechanisms of the solar cells. In chapter 3, the various technologies used for cell processing were reviewed. Also, various n-type Si solar cell concepts in the literature were reviewed. This research focused on development of low-cost and high-efficiency n-type PERT cells using commercially viable technologies.

In chapter 4, at the start of this research,  $J_{0e}$  of the inkjet-printed B emitter was studied by a combination of simulation and measurement. The boron-doped emitters with sheet resistance in the range of  $60\text{-}120\Omega/\text{sq}$  were formed by inkjet printing of liquid boron source followed by annealing in the temperature range of  $900\,^{\circ}\text{C}$  to  $950\,^{\circ}\text{C}$ . All the doping profiles showed very high near surface doping concentration of  $\geq 1\times 10^{21}\,\text{cm}^{-3}$  due to the formation of undesirable BRL.  $SiN_x$  passivated inkjet-printed B emitters with the BRL gave very high  $J_{0e}$  values (>  $400\text{fA/cm}^2$ ). However, when the BRL was completely removed by a thermal oxidation process followed by HF dip,  $J_{0e}$  value decreased by a factor of two to ~  $198\text{fA/cm}^2$  but was still short of the  $J_{0e}$  target of  $\leq 80\text{fA/cm}^2$ . It was found that  $SiO_2/SiN_x$  stack passivation after the BRL removal reduced the  $J_{0e}$  value to ~ $100\text{fA/cm}^2$  which is close to the target value of  $80\text{fA/cm}^2$  for 21% efficient n-type PERT cells.

In chapter 5, process-induced bulk lifetime in n-type Si wafers was studied, because the bulk lifetime in finished device is very important for solar cell efficiency. Model calculations were performed to establish base resistivity and bulk lifetime requirements to achieve 21% cells. A  $5\Omega$ •cm n-type Cz Si material was selected in this thesis and the model calculations showed that at least 1ms bulk lifetime should be maintained in the finished

device for achieving  $\geq 21\%$  PERT cells. Process-induced lifetime study using p<sup>+</sup>/n/n<sup>+</sup> structures on this material showed high bulk lifetime (>1ms) after the B and P co-diffusion in the temperature range of 900 °C to 950 °C due to phosphorus diffusion-induced effective gettering of impurities. However, a 850 °C thermal oxidation after the co-diffusion, used for BRL removal, degraded the bulk lifetime significantly to lower than 500 $\mu$ s. This negates the benefit of good surface passivation or low  $J_{0e}$  due to BRL removal. Therefore, an alternative method to the thermal oxidation is developed in the next chapter to remove the BRL which not only gives lower  $J_{0e}$ , but also preserves bulk lifetime.

In chapter 6, a chemical etching process was developed to remove the harmful BRL as an alternative to the thermal oxidation which leads to unwanted bulk lifetime degradation. In addition, this chapter showed a positive synergistic effect of passivating the BRL-free boron emitter surface with nitric acid-grown oxide (NAO) capped with PECVD SiN<sub>x</sub>. The combination of chemical etching and NAO/SiN<sub>x</sub> passivation resulted in low J<sub>0e-pass</sub> of 100fA/cm<sup>2</sup> without the degradation in bulk lifetime. This resulted in a large area (239 cm<sup>2</sup>) n-type Cz Si solar cell with 19.0% conversion efficiency, compared to the 17.4% cells at the start of this research with the BRL and SiN<sub>x</sub> passivation. Remainder of the thesis will focus on fundamental research and technology innovation to achieve the efficiency target of 21%.

In chapter 7, By developing technologies and optimizing solar cell fabrication process involving dual annealing for B and P dopants, rear surface planarization, and chemical etching for BRL removal, greater than 20% efficient n-type PERT cells with screen-printed contacts were achieved on commercial grade 239 cm<sup>2</sup> n-type Cz Si wafers. This represents over 1% (absolute) efficiency enhancement over the single anneal process

developed in chapter 6 which resulted in 19% efficiency. In addition, for B emitter formation, spin coating, screen printing, ion-implantation, and APCVD technologies were utilized and compared in this chapter. The etching process for the BRL removal was optimized for each technology. It was found that the maximum cell efficiency is achieved when only the BRL is etched away. Under etching the BRL results in inferior surface passivation, V<sub>oc</sub> and J<sub>sc</sub> while over etching degrades cell efficiency due to increase in R<sub>s</sub> and n-factor. Due to different BRL thickness, the optimized etching times for spin coating, screen printing, implantation, and APCVD were 30s, 240s, 120s, and 180s, respectively. The corresponding best efficiencies were 20.0%, 20.2%, 20.2%, and 20.2%. This chapter also shows nearly the same efficiency potential of the four B diffusion technologies for high efficiency commercial-ready n-type PERT solar cells up to the efficiency of 20%. However, more research needs to be done to drive this efficiency toward 21%. Ion-implanted cell technology is selected in the next chapter to achieve 21% efficiency through device modeling and further technology enhancements.

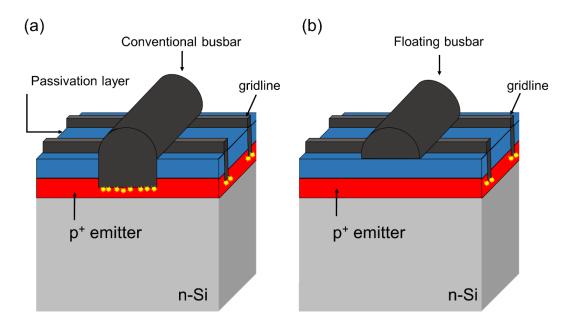

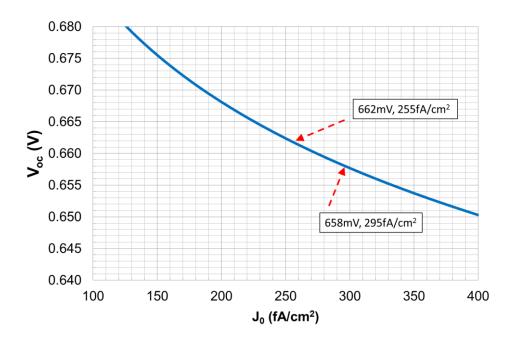

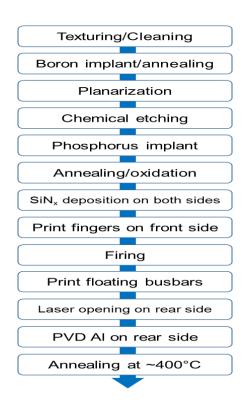

Chapter 8 focused on advanced metallization on the front and back through technology development and design optimization for higher efficiency cells. Advanced metallization involved three enhancements: i) optimization of front grid design with five busbars to increase FF, ii) laser opening and PVD Al to reduce rear contact recombination, and iii) introduction of floating busbars. The front grid pattern was optimized using an analytical model, which revealed 5 busbars with 100 gridlines can provide 0.33% increase in absolute efficiency. Fabrication of 5 busbar cells raised the efficiency from 20.1% to 20.4%. Second technology enhancement involved replacing the 120µm wide 500µm apart screen printed metal dots on the rear surface with laser opening of a 40µm dot pattern with

300 $\mu$ m spacing followed by PVD Al metallization. This reduced the back metal/Si contact area from 4.5% to 1.4%, resulting in higher  $V_{oc}$  and another 0.36% increase in efficiency. Best cell efficiency with this technology enhancement was 20.86%. Finally, floating busbars were applied on the front to reduce the front metal/Si contact area from 7.5% to 4.5%. This did give another 4mV increase in  $V_{oc}$  but the cell efficiency did not increase because of the slightly lower FF due to the inferior busbar/gird contact resistance. Improved floating busbar paste can overcome this and provide ~21% cells.

In chapter 9, by developing and integrating several efficiency enhancement features, 20.84% efficient nPERT cell was achieved on commercial grade 239 cm $^2$  n-type Cz Si wafers. The technology developments involved chemical etching of BRL to improve emitter surface passivation and bulk lifetime, separate annealing of B emitter and PBSF to optimize diffused regions for lower  $J_0$ , rear side planarization for lower surface recombination and higher back reflectance, optimized grid pattern with 5 busbars for lower series resistance and higher fill factor, laser opening and PVD Al for rear contact metallization to reduce metal coverage and improve  $J_{0b}$  and  $V_{oc}$ . Floating busbar technology showed ~4mV increase in  $V_{oc}$ , but efficiency enhancement was not seen due to high bus and grid contact resistance. All these technology enhancements provided a 3.44% absolute increase in efficiency over the 17.4% efficient nPERT cell at the start of this research, resulting in 20.84% efficiency.

Lastly, chapter 10 suggests research directions to improve cell efficiency further and attain ≥21% efficient n-type PERT solar cells which involve two additional technology developments including the use of selective emitters and negatively charged aluminum

oxide ( $Al_2O_3$ ) film for boron emitter surface passivation. These innovative technologies will raise cell efficiency further from 20.8 to 21.1%.

#### **Chapter 1: INTRODUCTION**

#### 1.1 Statement of the Problem

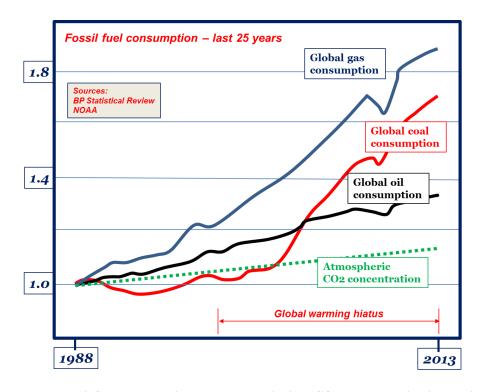

Historically, the fossil fuels such as gas, coal, oil have been the dominant resource for world energy supply. The consumption of the fossil fuels has been increasing steadily to satisfy growing world energy demand as shown in Figure 1.1. During the last 25 years, gas consumption has increased by over 80%, coal consumption by over 70%, and oil consumption by over 30%. However, this balance could change in the coming decades because fossil fuels are not only limited in supply but also cause detrimental impact on the environment through the emission of global warming gases (Figure 1.1).

Figure 1.1 Fossil fuel consumption and carbon dioxide (CO<sub>2</sub>) concentration in the air.

Nuclear energy has also attracted considerable interest as a substitute for the fossil fuels due to lower cost and clean production of electricity. However, nuclear energy raises concerns about safety and radioactive waste disposal. In addition, it takes long time to build a nuclear plant, so it cannot fulfill the rapidly rising demand for energy. Therefore, a clean energy source needs to be developed to reduce the dependence on fossil fuels and nuclear energy.

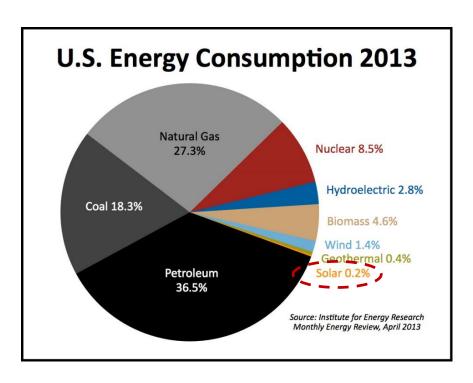

Photovoltaics (PV) is one of the most promising candidate for sustainable energy source because sunlight is free, essentially unlimited, and not localized in any part of the world. In addition, PV is environmentally friendly and a non-polluting energy source. Even though levelized cost of electricity (LCOE) from PV has come down by a factor of five since 1998, PV accounts for only less than 0.2% of total energy consumed in United States as shown in Figure 1.2 [1] due to a higher LCOE (~\$0.15/kWh) compared to fossil fuel (≤\$0.1/kWh). Therefore, it is necessary to further reduce the cost of modules as well as balance of system (BOS) to attain grid parity for mass adoption of PV.

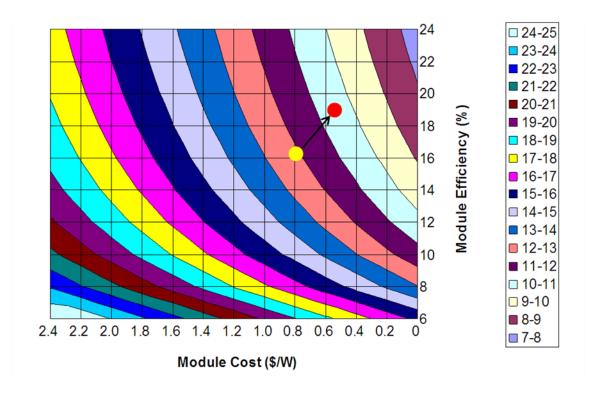

Figure 1.2 United States energy consumption in 2013

The PV module price can be reduced by reducing module material and manufacturing cost and by increasing solar cell efficiency. Solar cell efficiency is the most effective way to reduce the PV system cost because higher efficiency not only reduces the amount of material and the number of cells or modules required to produce a given power but also it reduces the BOS cost by shrinking the footprint of the PV system. LCOE contours in Figure 1.3, calculated by using the reasonable technical and financial inputs, reveal that the grid parity at ~ \$0.1/kWh, which is average retail price of electricity in U.S., can be reached by increasing current Si PV module efficiencies from 15.0-16.5% to ≥19.0% while simultaneously reducing the current module cost from ~\$0.80/W to < \$0.50/W. Since cell-to-module conversion results in an efficiency loss of about 10-15% relative (2.0-2.5%) absolute) [2], the corresponding cell efficiency needs to be ≥21%. This requirement established the overall goal for this thesis. It is important to note that Figure 1.3 assumed a total BOS cost of \$2/W, which is close to the current situation in the U.S. for residential commercial PV system. However, if the BOS drops to \$0.75/W, which is the DOE target, then  $\geq 21\%$  cells at  $\leq \$0.50$ /W can reach the global grid parity at  $\not\in 10$ /kWh.

Figure 1.3 LCOE contour plot for Atlanta area as a function of module cost and module efficiency with a BOS cost of \$2/W. Assumption for the chart :25 year lifetime: 20% derated: 7.69% WACC, No ITC, 50% debt fraction, 7% loan rate, and 5 year loan term.

#### 1.2 Motivation

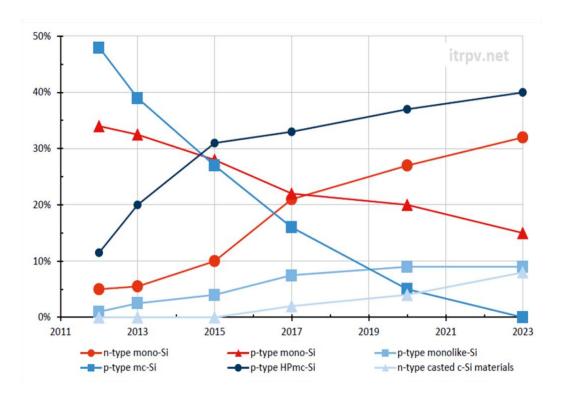

Silicon (Si) solar cells have been the workhorse of PV industry since their inception in 1956 at Bell laboratory. Si accounts for almost 90% of the PV modules shipped today. About 84% of PV module production is currently based on p-type crystalline silicon, while the n-type crystalline Si has a market share of only 4% as shown in Figure 1.4 [3].

Figure 1.4 Predicted increase in the market share of n-type mono-Si solar cells.

This is because, until 1980s, PV was mostly used for space applications where p-type Si is more durable because it is more tolerant to high energy particle radiation in space. However, since then, many researchers have studied n-type Si for PV and confirmed its superior electrical properties compared to the p-type Si. The first positive attribute of n-type Si is that it is less sensitive to the harmful metallic impurities, such as interstitial Fe (Fe<sub>i</sub>), which are usually present in the feedstock Si or introduced during cell manufacturing. These impurities can degrade bulk lifetime and cell performance by forming Shockley-Read-Hall (SRH) recombination centers. Note that the minority carriers in n-type Si are holes instead of electrons. Figure 1.5 shows that harmful impurities have higher capture cross section for electron than hole ( $\sigma_n/\sigma_p > 1$ ). Therefore, they hurt the bulk lifetime in p-type Si more than n-type Si [4].

Figure 1.5 Capture cross-section of metal impurities.

Therefore, n-type Si generally has higher bulk lifetime than p-type Si for the same impurity concentration which provides opportunity for achieving higher cell efficiency. Secondly, due to absence of boron, n-type Si does not suffer from light induced degradation (LID) which can cause reduction in 0.5~1% absolute cell efficiency [5-7]. The LID is ascribed to boron-oxygen (B-O) defects which are formed by prolonged light exposure (≥24 hours) of boron-doped p-type Si.

As a consequence of above attributes and the need for higher efficiency cells for low-cost PV, n-type Si has recently attracted considerable attention for high efficiency solar cells, including the development of industrial tools and technologies for commercializing n-type Si cells. Therefore, it is not surprising that the international PV

roadmap in Figure 1.4 predicts that the n-type monocrystalline Si market share may reach 30% by 2015 and over 60% by 2020, compared to 6% in 2012 [8]. This potential of n-type Si for high efficiency without LID provided the motivation in this thesis to develop low-cost high-efficiency commercial ready n-type Si solar cells with efficiency  $\geq$  21% in an attempt to approach grid parity.

#### 1.3 Thesis Objectives

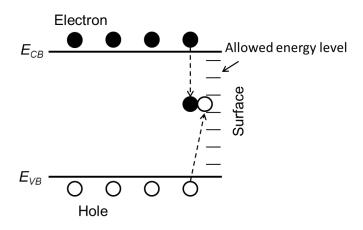

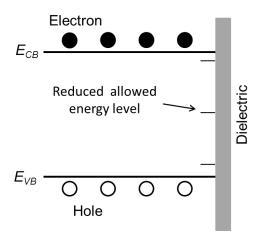

Low-cost high efficiency is the key to reducing cost of PV system. Since n-type Si has the potential for higher stabilized efficiency, the overall objective of this thesis is to produce ~ 21% n-type manufacturable PERT (passivated emitter, rear totally-diffused) Si solar cells at low-cost. However, there are several challenges that need to be overcome in order to accomplish this goal. Most essential process for n-type solar cells is the formation of single-side boron emitter with low-cost, high throughput, and high quality. In addition, it is challenging to attain high quality boron (B) emitter surface passivation and maintain high bulk lifetime due to the formation of boron-rich layer (BRL) on top of the boron emitter after the boron diffusion. The BRL interferes with surface passivation and can cause lifetime degradation because of inactive boron, segregated metal impurities, and structural defects in the BRL. Furthermore, widely used PECVD SiN<sub>x</sub> layer for anti-reflection coating and passivation of phosphorus doped n<sup>+</sup> emitter in p-base devices does not work well for boron emitters.

The above challenges provided the motivation to explore various B diffusion technologies in this thesis and develop process and dielectric stack combination to passivate its surface to minimize boron emitter recombination. In addition, a detailed study

of the BRL layer is conducted to understand its role and mitigate or eliminate its negative impact on surface passivation and bulk lifetime. Finally, optimization of cell design and technology development is carried out using production tools to achieve commercial ready cell efficiencies approaching 21% on large area (239 cm²) commercial grade n-type Cz Si wafers.

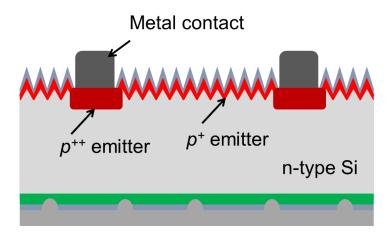

The overall goal of fabricating commercial ready low-cost high-efficiency (~21%) n-type PERT Si solar cells, shown in Figure 1.6, will be achieved through following 6 tasks in this thesis.

Figure 1.6 Structure of a screen-printed PERT n-type Si solar cell.

## Task 1: Investigation and Development of a Novel Boron-doped Emitter Formed by Inkjet Printing and its Surface Passivation Properties.

The formation of high quality boron emitter is required for achieving high efficiency n-type solar cells. In this section, a novel inkjet printing technology is used at

the beginning to form B emitter because of its potential for low cost and suitability in photovoltaic manufacturing. Technology development involves formation of inkjet boron emitters using appropriate B doping pastes and optimized annealing condition. Doping profiles and reverse saturation current density ( $J_{0e}$ ) are determined for various inkjet-printed B emitters to select the optimized B emitter for high efficiency n-type cells. In addition, various emitter surface passivating dielectrics are evaluated to minimize  $J_{0e}$ , while maintaining appropriate sheet resistance and antireflection coating. Finally, formation of BRL in the inkjet B emitters and its impact on surface passivation are studied.

## Task 2: Investigation and Understanding of Process-induced Bulk Lifetime in N-type Silicon Wafers.

Since bulk lifetime ( $\tau_{bulk}$ ) in n-type Si is key to achieving high efficiency n-type Si solar cells, process-induced bulk lifetime of n-type Si wafer is investigated prior to cell fabrication. This study includes development of boron diffusion, phosphorus diffusion, and thermal oxidation processes to attain bulk lifetime in excess of 1 ms, required for high efficiency n-type cells. In addition, process conditions are tailored to maintain manufacturability of PERT devices.

## Task 3: Development of a Rapid Chemical Etching Process for BRL Removal and Subsequent Surface Passivation for High Bulk Lifetime, Low $J_{0e}$ , and High Efficiency.

Most of the processes currently used in industry for the B emitter formation result in an unintentional supersaturated boron-rich layer (BRL) on top of the B emitter. It has been conjectured that the BRL acts as high recombination site due to inactive boron,

segregated metal impurities, and structural defects. It can also interfere with the emitter surface passivation. For this reason, either BRL formation needs to be prevented or the BRL needs to be removed during cell processing to achieve high efficiency. Therefore, in this task, first a fundamental understanding of the formation and impact of BRL is established. Then methods for BRL removal are explored, without hurting the emitter, to attain low  $J_{0e}$  and high  $\tau_{bulk}$ . These techniques are integrated in the cell process sequence to fabricate manufacturable high efficient n-type PERT solar cells. Finally, the effectiveness of the BRL removal process is validated by transmission electron microscopy (TEM) and auger electron spectroscopy (AES), and  $J_{0e}$  measurement.

# Task 4: Technology Development and Fabrication of High Efficiency N-type Commercial Size Silicon Solar Cells with Four Promising B Emitter Technologies.

Four commercially viable B diffusion techniques are investigated in this task as an alternative to the conventionally-used BBr<sub>3</sub> tube diffusion and the novel inkjet printed B emitter. The proposed techniques will involve spin coating, screen printing, ion-implantation, and atmospheric pressure chemical vapor deposition (APCVD) of B source. First, the impact of each boron technology on cell efficiency is explored by fabricating n-type PERT solar cells using the same process sequence. Then, the process sequence is optimized for each B diffusion technology to attain highest efficiency n-type PERT cell.

Task 5: Technology Development and Optimization of Metallization for Achieving ~21% Efficient N-type PERT Cell.

Fill factor (FF) is one of key parameters to achieve high cell efficiency. The FF is affected by total series resistance (R<sub>s</sub>) of the cell which consists of several components. These components are first analyzed for ion-implanted n-type PERT solar cell for the reference. The various components of R<sub>s</sub> are calculated for different spacing and number of fingers and busbars using the analytical modeling. Using these predetermined R<sub>s</sub> values from the modeling, optimized front grid design for producing a maximum cell efficiency is selected. In addition, sputtering of aluminum by physical vapor deposition (PVD) in combination with laser opening of dielectric stack is used on the rear side for metal contacts to reduce the contact area. This concept replaces the existing rear contacts formed by screen-printed and fire-through silver (Ag) dots followed by screen-printing low temperature cured Ag paste. Compared to the screen-printed rear contacts, the PVD Al metallization provides less metal contact fraction on the rear side and narrower point contact pitch. This lowers metal-induced recombination as well as lateral resistance from the rear side. These optimizations and improvements in metallization are implemented in full cell and benefits on  $J_{0e}$  and FF are quantified. Finally, the floating busbar is applied for a further improvement. The floating busbars make no direct contact with Si emitter and reside just on top of the anti-reflection coating. Therefore, this reduces the recombination further and hence give an added boost in V<sub>oc</sub>.

# Task 6: Quantitative Understanding of Impact of Each Technology Enhancement on Cell Parameters and Efficiency through Detailed Modeling and Characterization.

In this task, all the above fundamental understanding, cell design, and technology developments are integrated into a process sequence to achieve ~21% efficient large area

PERT solar cells on commercial size 239 cm<sup>2</sup> n-type Cz Si wafers. Screen-printed contacts to the boron emitter. Detailed device modeling and cell characterization are used to explain each of the five technology enhancements that led to the increase in PERT cell efficiency from  $\sim$ 17.4% to  $\sim$ 21% in this research. Device modeling is performed using PC1D model and cells are characterized by light and dark *I-V*, IQE, reflectance, J<sub>0e</sub>, and bulk lifetime measurements.

# Chapter 2 : BASIC OPERATION AND FUNDAMENTAL PHYSICS OF SOLAR CFELLS

## 2.1 Basic Operation and Equivalent Circuit of a Solar Cell

A solar cell is a power generating device which directly converts sunlight into electricity using the photovoltaic effect. The process of converting sunlight into electrical energy consists of the following three essential steps:

- (1) Absorption of incident photons generates a large number of electron-hole pairs.

- (2) Separation of electron-hole pairs by electric field inside the p-n junction.

- (3) Transport of separated charge carriers to an external circuit or load.

The electrons then dissipate its energy in the external circuit or load and return to the solar cell.

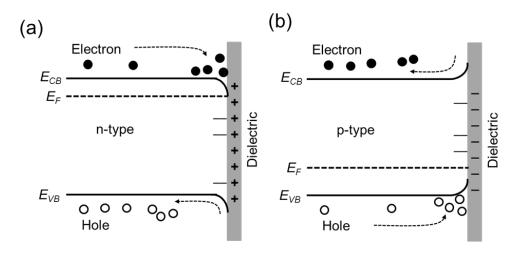

Figure 2.1 illustrates a structure of a simple n-type Si solar cell and its basic operation. The n-type Si solar cell involves the formation of a boron-doped ( $p^+$ ) emitter on the front side (p-n junction), diffusion of phosphorus-doped ( $n^+$ ) back surface field (BSF) on the rear side, deposition of a silicon nitride (SiN<sub>x</sub>) film on front and back for passivation and anti-reflection coating (ARC) on the emitter and passivation of the BSF surface, and screen-printed metallization for contacts. The boron emitter forms a p-n junction creating internal electric field in the depletion region. The light-generated electrons and holes are separated and swept across the junction by the internal electric field. The back surface filed (BSF) consists of a heavily phosphorus-doped ( $n^+$ ) region on the rear surface of the n-type solar cell. The high-low region (n+/n) generates an electric field at the interface that serves as a barrier for minority carrier flow to the rear contact [9]. The BSF reduces back surface recombination by reflecting the holes back into the base. The SiN<sub>x</sub> is frequently used for

Si surface passivation as well as ARC in PV industry. The  $SiN_x$  lowers surface recombination by reducing the number of dangling bonds at the Si surface and by providing field induced passivation via its built-in positive charge. In addition, it reduces the reflection from the front cell surface which raises the absorption of the incident light into the cell. Lastly, the front and back contacts on most commercial solar cells are formed by screen-printing technology because of its simplicity, high throughput, and low manufacturing cost. The cell efficiency can be improved significantly by avoiding the recombination of the generated carriers at the front and back surfaces, in the heavily doped emitter and BSF regions, and in the bulk. The importance of surface, emitter and bulk recombination will be quantified by device modeling to provide guidelines for technology development and optimized cell design.

Figure 2.1 A structure of a simple n-type Si solar cell and its basic operation.

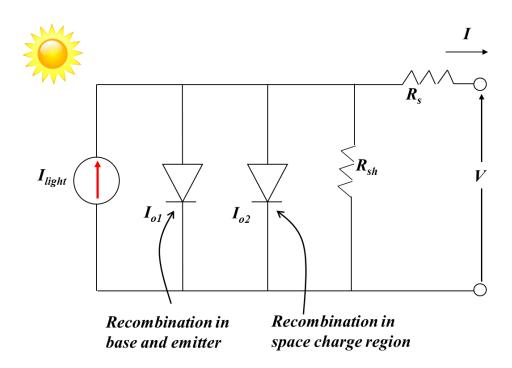

The basic structure of a Si solar cell can be modeled by a circuit with a current source ( $I_{light}$ ) connected in parallel with two diodes ( $I_{01} \& I_{02}$ ), series resistance ( $R_s$ ), and shunt resistance ( $R_{sh}$ ) as illustrated in Figure 2.2. These diodes are characterized by their reverse saturation current  $I_{01}$  and  $I_{02}$ .  $I_{01}$  represents the recombination in the base and emitter of the solar cell, and  $I_{02}$  represents the recombination in the space charge region of the solar cell. The series resistance is composed of bulk, sheet, contact, grid, and busbar resistances. The shunt resistance is the leakage path of the current through a solar cells via parasitic shunting.

Figure 2.2 Equivalent circuit of a p-n junction solar cell.

# 2.2 Solar Cell Parameters

As explained in Chapter 2.1, a solar cell is a device which converts the incident sunlight into electrical energy. The conversion efficiency is the most important parameter

to characterize the performance of a solar cell. The cell efficiency is defined as the ratio of electrical power output ( $P_{out}$ ) to the incident photon power ( $P_{in}$ ) as shown in Figure 2.3 [10].

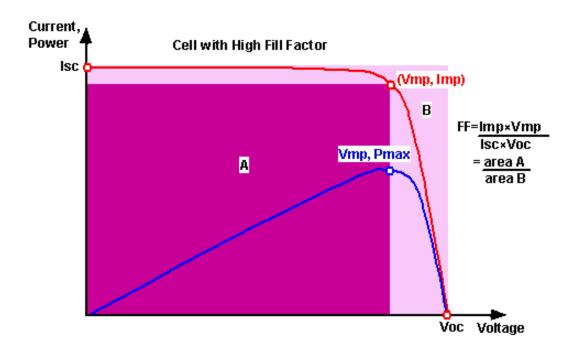

Figure 2.3 I-V characteristics of a solar cell.

The conversion efficiency  $(\eta)$  is expressed as [11]

$$E_{ff}(\eta) = \frac{P_{out}}{P_{in}} = \frac{V_{mp} \cdot I_{mp}}{P_{in}} = \frac{V_{oc} \cdot I_{sc} \cdot FF}{P_{in}}$$

(2.1)

where  $V_{mp}$  and  $I_{mp}$  are the voltage and current at maximum power point ( $P_{max}$ ) and  $P_{in}$  is  $100 \text{mW/cm}^2$  for standard test conditions (STC).

**Fill factor** (FF) is a measure of "squareness" of the I-V curve as illustrated in Figure 2.3. It is defined as the ratio of the maximum power output of a solar cell (area A) to the product of  $V_{oc}$  and  $I_{sc}$  (area B). The FF is expressed as

$$FF = \frac{V_{mp} \cdot I_{mp}}{V_{oc} \cdot I_{sc}} = \frac{area\_A}{area\_B}$$

(2.2)

FF can be also expressed by an empirical equation below:

$$FF = \frac{v_{oc} - \ln(v_{oc} + 0.72)}{v_{oc} + 1}$$

(2.3)

where the  $v_{oc}$  is the "normalized  $V_{oc}$ " is defined as a following equation

$$v_{oc} = \frac{q}{nkT}V_{oc} \tag{2.4}$$

where q is the electronic charge, n is the ideality factor, k is Boltzmann constant, and T is temperature.

Open circuit voltage ( $V_{oc}$ ) is the maximum voltage that the solar cell can generate.  $V_{oc}$  is expressed as

$$V_{oc} = \frac{kT}{q} \ln \left( \frac{I_{sc}}{I_o} + 1 \right) \tag{2.5}$$

The  $I_o$  is a reverse saturation current of a finite dimension p-n junction diode and is expressed by following equations [11, 12]

$$I_{o} = I_{oe} + I_{ob} = A \left( \frac{qD_{e}n_{i}^{2}}{L_{e}N_{A}} \cdot F_{P} + \frac{qD_{h}n_{i}^{2}}{L_{h}N_{D}} \cdot F_{N} \right) = A \left( \frac{qn_{i}^{2}}{N_{A}} \cdot S_{eje} + \frac{qn_{i}^{2}}{N_{D}} \cdot S_{ejb} \right)$$

(2.6)

$$F_{p} = \frac{S_{e} \cosh(W_{p}/L_{e}) + D_{e}/L_{e} \sinh(W_{p}/L_{e})}{D_{e}/L_{e} \cosh(W_{p}/L_{e}) + S_{e} \sinh(W_{p}/L_{e})}$$

(2.7)

$$F_{N} = \frac{S_{h} \cosh(W_{N} / L_{h}) + D_{h} / L_{h} \sinh(W_{N} / L_{h})}{D_{h} / L_{h} \cosh(W_{N} / L_{h}) + S_{h} \sinh(W_{N} / L_{h})}$$

(2.8)

where  $S_h$  and  $S_e$  are hole and electron surface recombination velocities, respectively;  $W_P$  and  $W_N$  are the thickness of the emitter and the base, respectively.  $F_N$  and  $F_P$  are called

geometry factors. It is interesting note that if front and back surfaces have high recombination velocity ( $S_h$  and  $S_e \approx \infty$ ),  $F_N$  and  $F_P$  can be expressed as:

$$F_N = \coth\left(\frac{W_N}{L_h}\right), \ F_P = \coth\left(\frac{W_P}{L_e}\right)$$

(2.8)

On the other hand, if front and back surfaces have very low recombination velocity ( $S_h$  and  $S_e \approx 0$ ),  $F_N$  and  $F_P$  can be reduced to :

$$F_N = \tanh\left(\frac{W_N}{L_h}\right), \ F_P = \tanh\left(\frac{W_P}{L_e}\right)$$

(2.9)

The emitter saturation current ( $I_{0e}$ ) is the recombination current at the junction edge on the emitter side and accounts for the recombination at the front surface and in the bulk of the emitter. The base saturation current ( $I_{0b}$ ) is the recombination current at the depletion edge on the base side which accounts for bulk and rear surface recombination.

As defined in Equation (2.5), the  $V_{oc}$  depends on the short circuit current ( $I_{sc}$ ) and reverse saturation current ( $I_0=I_{0e}+I_{0b}$ ) of the solar cell. Thus,  $V_{oc}$  is a measure of the amount of recombination in a solar cell.  $I_{sc}$  typically has a small variation, the  $I_o$  may vary by orders of magnitude.

**Shor circuit current** ( $I_{sc}$ ) is expressed as

$$I_{sc} = \int_{E_{c}}^{\infty} q \cdot N_{ph}(\lambda) \cdot EQE(\lambda) d\lambda$$

(2.6)

Where  $E_g$  (1.1eV) is the bandgap of silicon,  $N_{ph}$  is the number of incident photons,  $\lambda$  is the wavelength, and EQE is the external quantum efficiency. The EQE is the ratio of the number of charge carriers collected by the solar cell to the number of photons of a given wavelength incident on the solar cell. EQE can be written as following equation

$$EQE(\lambda) = [1 - R(\lambda)] \cdot IQE(\lambda)$$

(2.7)

where reflectance (R) is the percentage of the light reflected from the solar cell and IQE is the internal quantum efficiency. The IQE is the ratio of the number of carriers collected by the solar cell to the number of photons of a given wavelength entering the solar cell.

#### 2.3 Losses in Si Solar Cells

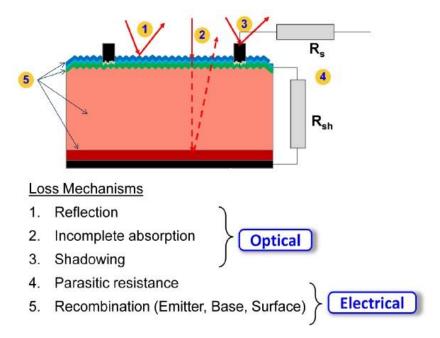

The theoretical efficiency for Si solar cells under one sun operation is about 29.3% [13]. However, the maximum cell efficiencies fabricated by Sunpower, Panasonic, and UNSW are currently 25.0~25.5% [14-16]. The difference between the theoretical and the measured efficiency is due to optical and electrical losses as shown in Figure 2.4 [17]. The optical loss is due to the loss of photons which could not generate electron-hole pairs. This loss is due to the front surface reflection, shading, and incomplete absorption. The electrical loss is due to the generated e-h pairs that do not contribute to the cell output power. This loss is attributed to resistances and recombination.

Figure 2.4 Losses in a Si solar cell.

#### 2.3.1 Reflection Loss

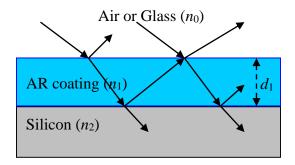

The reflection loss is attributed to incident photons that are reflected from the solar cell surfaces. The reflection can be minimized by **anti-reflection coating** (ARC) and **surface texturing**.

(1) Anti-reflection coating (ARC): ARC is formed by a thin dielectric material on the Si surface to reduce the reflection of incident light via destructive interference of the waves reflected from the top and bottom surfaces of the dielectric (Figure 2.5). Proper selection of thickness  $d_I$  and refractive index  $n_I$  of the ARC can reduce reflection significantly.

Figure 2.5 Anti-reflection coating to reduce the surface reflection.

For a single layer ARC, the reflectance (R) can be expressed by Fresnel's equation [11, 18].

$$R = \frac{r_1^2 + r_2^2 + 2r_1r_2\cos\theta}{1 + r_1^2r_2^2 + 2r_1r_2\cos\theta}, \ \theta = \frac{2\pi n_1 d_1}{\lambda}, \ r_1 = \frac{n_0 - n_1}{n_0 + n_1}, \qquad r_2 = \frac{n_1 - n_2}{n_1 + n_2}$$

(2.8)

where n is the refractive index of a layer. The reflectance has minimum  $R_{\min}$  when  $n_1d_1 = \lambda/4$  [18] (quarter-wavelength AR coating) and is obtained by :

$$R_{\min} = \frac{(n_0 n_2 - n_1^2)^2}{(n_0 n_2 + n_1^2)^2}$$

(2.15)

If  $n_1 = \sqrt{n_0 n_2}$ ,  $R_{\rm min}$  becomes zero at the desired wavelength  $\lambda = 4n_1d_1$  which can be selected by tailoring the ARC thickness  $d_1$ . Since solar spectrum has maximum photon energy at a wavelength ( $\lambda$ ) of 630 nm [19], ARC is typically designed to minimize the reflection at 630 nm.

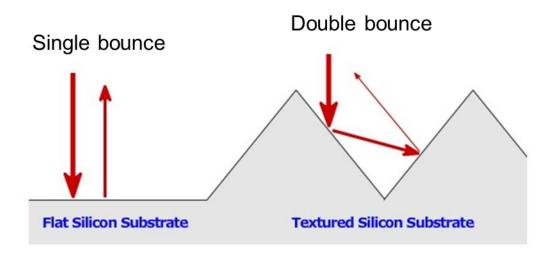

(2) Surface texturing: surface texturing is another effective technique for minimizing reflection. Any roughening of the surface reduces the reflection by increasing the number of bounces as illustrated in Figure 2.6 [20]. Surface texturing can be accomplished by etching along the surfaces of the Si crystal planes <100>. With the surface texturing, the weighted average reflection of the Si surface can be reduced from ~30% to about 11%. The ARC deposition on the textured Si surfaces can reduce this further to within 3%.

Figure 2.6 Incident light on flat Si surface and textured Si surface.

#### 2.3.2 Shading Loss

A finished solar cell needs to be contacted at the front and back side in order to extract power from the solar cell. However, the front metal contact inhibits the light to enter into the solar cell which reduces  $I_{light}$ . This is referred to as the shading loss. Thus, the front contact including fingers and gridlines should cover as small at the front as possible. However, this results in increased resistive losses because carriers have to travel longer distance to be collected by the metal contact. Therefore, grid design has to be optimized in order to balance the shading and resistive losses.

# 2.3.3 Incomplete Absorption

The loss due to incomplete absorption refers to the loss of photons with energy E>E<sub>g</sub> which do not get absorbed in the solar cell due to smaller cell thickness or insufficient optical path length through the cell. This can be minimized by appropriate light trapping that enhances the absorption of long wavelength photons by reflecting them back into the cell from the surfaces.

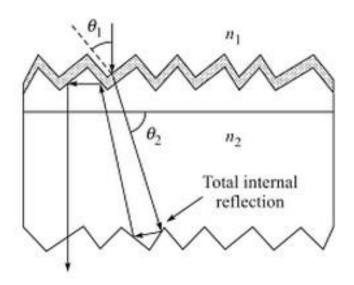

**Light trapping**: the light trapping is achieved by changing the angle of incident light so that the rays can travel at certain angle, rather than perpendicular to the surface. This results in increased optical path length as shown in Figure 2.7 [21]. Therefore, the front surface should be textured in order for the rays to meet the surface at an angle. According to Snell's law:

$$n_1 Sin \theta_1 = n_2 Sin \theta_2 \tag{2.16}$$

the total internal reflection can occur at the rear surface if the incident angle is greater than the critical angle. Consequently, the path length can be increased by a combination of front textured surface and rear reflector design. However, the textured surface leads to increased surface recombination in the cell because of increased interface trap density. Thus, to mitigate the surface recombination, the light trapping should be achieved with a planar rear surface, while keeping the front surface textured, to form a dielectric mirror that reflects light back not the silicon.

Figure 2.7 Light trapping in solar cell to increase the optical path length.

#### 2.3.4 Resistive Losses

The resistive losses are the result of series ( $R_s$ ) and shunt resistances ( $R_{sh}$ ) of a solar cell. These two resistances affect the final FF of solar cell. The following equations show the effect of series and shunt resistances on FF.

$$FF = FF_S[1 - \frac{(v_{oc} + 0.7)}{v_{oc}} \cdot \frac{FF_S}{r_{SH}}]$$

(2.17)

$$FF_S = FF_o(1 - r_S) \tag{2.18}$$

$$r_S = \frac{R_{sh}}{R_{CH}}, \ R_{CH} = \frac{V_{OC}}{I_{SC}}, \ r_{SH} = \frac{R_{sh}}{R_{CH}}$$

(2.19)

where  $FF_o$  is the ideal FF without  $R_s$  and  $R_{sh}$  terms as defined in Equation (2.3). Consequently,  $R_s$  of a solar cell should be as low as possible and  $R_{sh}$  should be as large as possible in order to obtain high FF and efficiency.

The  $R_{sh}$  is generally due to process-induced defects that result in partial shunting of the p-n junction and lowering of shunt resistance. This low shunt resistance reduces the amount of photocurrent flowing through the p-n junction and reduces the voltage of the solar cell. Note that  $R_{sh}$  is not a design parameter, but the  $R_s$  is a design parameter that can be controlled.

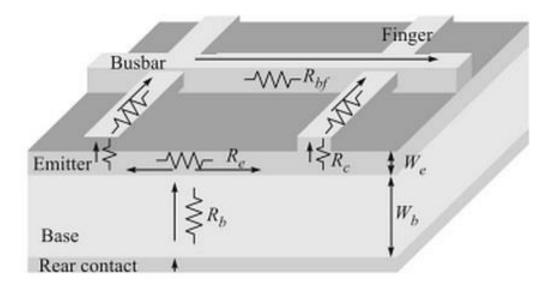

The series resistance  $R_s$  of a solar cell consists of several components as illustrated in Figure 2.8 [21]. These include resistance of base ( $R_b$ ), resistance of the emitter ( $R_e$ ), resistance of the metal-Si interface (contact resistance  $R_c$ ), and resistance  $R_b$  associated with busbars and fingers.

Figure 2.8 Series resistance components in a Si solar cell.

$$R_{S} = R_{b} + R_{e} + R_{c} + R_{bf} (2.20)$$

Thus, the proper grid and emitter design is very important for lowering  $R_s$  and increasing FF and cell efficiency.

# 2.3.5 Recombination Loss

When illuminated, the generation of electron-hole pair occurs throughout a Si solar cell. The excess carriers return back to reach a thermal equilibrium by recombination of excess electrons and holes. There are four types of recombination processes in a Si solar cell.

- 1. Radiative recombination

- 2. Auger recombination

- 3. Shockley-Read-Hall (SRH) recombination

- 4. Surface recombination

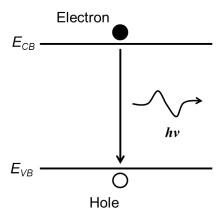

(1) Radiative (Band-to-Band) recombination: In radiative recombination, an excited electron from the conduction band falls directly back into the valence band. The excited electron releases the energy in the form of a photon (Figure 2.9). The rate of this recombination depends on the number of carriers in the conduction and the number of empty states in the valence band. This recombination process is dominant in direct bandgap semiconductors, but it is not important in indirect bandgap material like Si.

Figure 2.9 Energy band diagram of radiative recombination

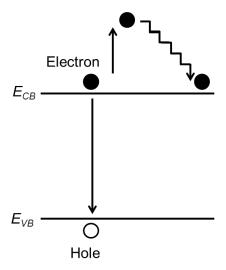

(2) Auger recombination: This occurs at high carrier concentrations (>  $10^{17}$  cm<sup>-3</sup>). As shown in Figure 2.10, when an electron and a hole recombine and give that energy to another electron in the conduction band instead of giving the energy as heat or a photon. The electron that receives the energy goes to a higher energy level and then thermalizes back to the conduction band via scattering.

Figure 2.10 Energy band diagram of auger recombination.

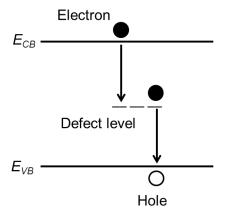

(3) Shockley-Read-Hall (SRH) recombination: The SRH recombination occurs in material with defects which give rise to energy levels within the band gap. The SRH recombination involves two step processe as illustrated in Figure 2.11. First, an electron (or hole) is trapped by an energy state in the energy level introduced by the defects. If a hole moves up to the same energy state before the electron is re-emitted into the conduction band, it then recombines. The recombination via mid-gap energy levels is very effective in reducing bulk lifetime.

Figure 2.11 Energy band diagram of SRH recombination.