**ADVERTIMENT**. La consulta d'aquesta tesi queda condicionada a l'acceptació de les següents condicions d'ús: La difusió d'aquesta tesi per mitjà del servei TDX (<a href="www.tesisenxarxa.net">www.tesisenxarxa.net</a>) ha estat autoritzada pels titulars dels drets de propietat intel·lectual únicament per a usos privats emmarcats en activitats d'investigació i docència. No s'autoritza la seva reproducció amb finalitats de lucre ni la seva difusió i posada a disposició des d'un lloc aliè al servei TDX. No s'autoritza la presentació del seu contingut en una finestra o marc aliè a TDX (framing). Aquesta reserva de drets afecta tant al resum de presentació de la tesi com als seus continguts. En la utilització o cita de parts de la tesi és obligat indicar el nom de la persona autora.

**ADVERTENCIA**. La consulta de esta tesis queda condicionada a la aceptación de las siguientes condiciones de uso: La difusión de esta tesis por medio del servicio TDR (<a href="www.tesisenred.net">www.tesisenred.net</a>) ha sido autorizada por los titulares de los derechos de propiedad intelectual únicamente para usos privados enmarcados en actividades de investigación y docencia. No se autoriza su reproducción con finalidades de lucro ni su difusión y puesta a disposición desde un sitio ajeno al servicio TDR. No se autoriza la presentación de su contenido en una ventana o marco ajeno a TDR (framing). Esta reserva de derechos afecta tanto al resumen de presentación de la tesis como a sus contenidos. En la utilización o cita de partes de la tesis es obligado indicar el nombre de la persona autora.

**WARNING**. On having consulted this thesis you're accepting the following use conditions: Spreading this thesis by the TDX (<a href="www.tesisenxarxa.net">www.tesisenxarxa.net</a>) service has been authorized by the titular of the intellectual property rights only for private uses placed in investigation and teaching activities. Reproduction with lucrative aims is not authorized neither its spreading and availability from a site foreign to the TDX service. Introducing its content in a window or frame foreign to the TDX service is not authorized (framing). This rights affect to the presentation summary of the thesis as well as to its contents. In the using or citation of parts of the thesis it's obliged to indicate the name of the author

## UNIVERSITAT POLITÈCNICA DE CATALUNYA Departament d'Arquitectura de Computadors

# Low-Cost And Efficient Fault Detection And Diagnosis Schemes for Modern Cores

A thesis submitted in fulfillment of the requirements for the degree of DOCTOR OF PHILOSOPHY / DOCTOR PER LA UPC by

## Javier Sebastián Carretero Casado Barcelona, 2015

Advisor: **Xavier Vera Rivera** (Intel Corporation) Tutor: **Antonio González Colás** (UPC) Mientras iba de tu mano hacia la montaña, unos días eran fuego y otros eran llamas. Dentro del espejo donde no me reflejaba, la promesa que en la cima nos aguardaba. Pero una vez allí las nubes no nos dejaban ver el suelo y una sensación que tuve fue miedo.

El camino de bajada era más estrecho, se podría decir una bajada a los infiernos. Te pedí que me guiaras cuando estaba ciego, la montaña fue quien respondió con eco, un eco que reproducía exactamente mis lamentos, los sueños que una vez tenía y ya no tengo.

San Juan de la Cruz - Los Planetas

All these saints that I move without

I lose without in vain

All these saints, they move without

They moved without again

Well, all these places will lose without

They lose without a name

St. Apollonia - Beirut

## Abstract

Continuous improvements in transistor scaling together with microarchitectural advances have made possible the widespread adoption of high-performance processors across all market segments. However, the growing reliability threats induced by technology scaling and by the complexity of designs are challenging the production of cheap yet robust systems.

Soft error trends are haunting, especially for combinational logic, and parity and ECC codes are therefore becoming insufficient as combinational logic turns into the dominant source of soft errors. Furthermore, experts are warning about the need to also address intermittent and permanent faults during processor runtime, as increasing temperatures and device variations will accelerate inherent aging phenomena.

These challenges specially threaten the commodity segments, which impose requirements that existing fault tolerance mechanisms cannot offer. Current techniques based on redundant execution were devised in a time when high penalties were assumed for the sake of high reliability levels. Novel light-weight techniques are therefore needed to enable fault protection in the mass market segments.

The complexity of designs is making post-silicon validation extremely expensive. Validation costs exceed design costs, and the number of discovered bugs is growing, both during validation and once products hit the market. Fault localization and diagnosis are the biggest bottlenecks, magnified by huge detection latencies, limited internal observability, and costly server farms to generate test outputs.

This thesis explores two directions to address some of the critical challenges introduced by unreliable technologies and by the limitations of current validation approaches.

We first explore mechanisms for comprehensively detecting multiple sources of failures in modern processors during their lifetime (including transient, intermittent, permanent and also design bugs). Our solutions embrace a paradigm where fault tolerance is built based on exploiting high-level microarchitectural invariants that are reusable across designs, rather than relying on re-execution or ad-hoc block-

level protection. To do so, we decompose the basic functionalities of processors into high-level tasks and propose three novel runtime verification solutions that combined enable global error detection: a computation/register dataflow checker, a memory dataflow checker, and a control flow checker. The techniques use the concept of endto-end signatures and allow designers to adjust the fault coverage to their needs, by trading-off area, power and performance. Our fault injection studies reveal that our methods provide high coverage levels while causing significantly lower performance, power and area costs than existing techniques.

Then, this thesis extends the applicability of the proposed error detection schemes to the validation phases. We present a fault localization and diagnosis solution for the memory dataflow by combining our error detection mechanism, a new low-cost logging mechanism and a diagnosis program. Selected internal activity is continuously traced and kept in a memory-resident log whose capacity can be expanded to suite validation needs. The solution can catch undiscovered bugs, reducing the dependence on simulation farms that compute golden outputs. Upon error detection, the diagnosis algorithm analyzes the log to automatically locate the bug, and also to determine its root cause. Our evaluations show that very high localization coverage and diagnosis accuracy can be obtained at very low performance and area costs. The net result is a simplification of current debugging practices, which are extremely manual, time consuming and cumbersome.

Altogether, the integrated solutions proposed in this thesis capacitate the industry to deliver more reliable and correct processors as technology evolves into more complex designs and more vulnerable transistors.

# Acknowledgements

Esta tesis no hubiera visto la luz sin la ayuda y el apoyo constante de varias personas.

Quiero empezar estos agradecimientos con Xavier Vera: director de tesis, jefe y amigo. Xavi es quien me ha iniciado en el mundo de la investigación, me ha enseñado, guíado, aconsejado y quien me ha discutido ideas con una paciencia inacabable. De él he aprendido la importancia de desarrollar el pensamiento crítico, la autoconfianza y el espíritu de luchador. Gràcies!

Junto con Xavi, Jaume Abella ha sido como un segundo director. Gran parte de lo que sé se lo debo a él. Ojalá algún día tenga su capacidad de saber plantear las preguntas adecuadas, de saber esquivar y meter goles con argumentos, o de perseguir la simplicidad y la novedad en las soluciones. Aquesta tesi és teva també.

A Antonio González tengo que agradecerle la confianza que tuvo en mí, desde el día que me contrató en Intel, así como cuando me sugirió la posibilidad de realizar esta tesis. Gracias por estas oportunidades.

Mil gracias también a los compañeros de Intel y UPC por las risas, coñas, viajes y buenos momentos compartidos. En especial a los 'Rancis', a Matteo, Rakesh R., Demos, Juan F., Kyriakos, Gaurang U., Qiong, Pepe y a Pedro M., entre otros.

Fuera del laboratorio, quiero dar las gracias a mis amigos/as de Barcelona y de Barahona. Me habéis ayudado a desconectar de las dificultades de la tesis y del trabajo. Sois una parte importante de mi vida, y con vosotros he podido respirar aire fresco y ver las cosas con una perspectiva más amplia. Ya no hay más excusas para no veros más a menudo.

Para acabar, me gustaría dedicar unas palabras a mi familia. A todos ellos, gracias por hacerme sentir querido y tener fe en mí. En especial, a mis hermanos (Charo, María José y Patxi) por su apoyo constante. A mis cuñados y a los bichejos por hacer al clan aún más divertido. Y sobre todo a mis padres, a quien va dedicada esta tesis: nunca podré apreciar ni llegar al nivel de vuestra dedicación.

# Contents

| $\mathbf{A}$ | bstra                  | ct          |                                                                 | $\mathbf{v}$ |

|--------------|------------------------|-------------|-----------------------------------------------------------------|--------------|

| $\mathbf{A}$ | ckno                   | wledge      | ments                                                           | vii          |

| C            | onter                  | $_{ m nts}$ |                                                                 | ix           |

| Li           | $\operatorname{st}$ of | Figure      | es es                                                           | xiii         |

| Li           | $\operatorname{st}$ of | Tables      | i                                                               | xvii         |

| G            | lossa                  | ry of A     | acronyms and Abbreviations                                      | xix          |

| 1            | Intr                   | oducti      | on                                                              | 1            |

|              | 1.1                    | Motiva      | ation: Reliability Challenges                                   | 2            |

|              |                        | 1.1.1       | Impact of Transistor Scaling on Lifetime Reliability            | 2            |

|              |                        | 1.1.2       | Growing Design Complexity and Validation Costs                  | 6            |

|              | 1.2                    | Proble      | m Statement                                                     | 7            |

|              |                        | 1.2.1       | Lifetime Reliability Mechanisms for Multiple Sources of Failure | s 7          |

|              |                        | 1.2.2       | Overheads of Error Detection Solutions                          | 8            |

|              |                        | 1.2.3       | Tackling Observability and Reproducibility During Post-Silicon  |              |

|              |                        |             | Validation                                                      | 9            |

|              |                        | 1.2.4       | System-Level Simulation for Error Discovery and Diagnosis       | 10           |

|              | 1.3                    | Thesis      | Approach                                                        | 11           |

|              | 1.4                    | Thesis      | Contributions                                                   | 12           |

|              | 1.5                    | Thesis      | Organization                                                    | 14           |

| 2            | Bac                    | kgroun      | nd                                                              | 17           |

|              | 2.1                    | Econor      | mic Costs of Hardware Reliability                               | 17           |

|              | 2.2                    | Reliab      | ility Concepts and Metrics                                      | 18           |

|              |                        | 221         | Basic Terminology and Classification of Errors                  | 18           |

#### x · CONTENTS

|   |     | 2.2.2    | Fault Tolerance Metrics                      |

|---|-----|----------|----------------------------------------------|

|   | 2.3 | Hardw    | rare Failure Phenomena: How Electronics Fail |

|   | 2.4 | Aspect   | ts of Fault Tolerance                        |

|   | 2.5 | Valida   | tion and Debugging: Background               |

|   |     | 2.5.1    | Pre-Silicon Validation                       |

|   |     | 2.5.2    | Post-Silicon Validation                      |

|   |     | 2.5.3    | Runtime Validation                           |

| 3 | Rel | ated W   | Vork 2                                       |

|   | 3.1 | Re-exe   | ecution- Based Hardware Techniques           |

|   | 3.2 | Error    | Coding Techniques                            |

|   | 3.3 | Circui   | t-Level Techniques                           |

|   | 3.4 | Softwa   | re-Level and Hybrid Techniques               |

|   | 3.5 | Indust   | rial Validation Techniques                   |

| 4 | Eva | luatior  | r Framework                                  |

|   | 4.1 | Bench    | marks, Tools and Simulators                  |

|   |     | 4.1.1    | Benchmarks                                   |

|   |     | 4.1.2    | Timing Simulator                             |

|   |     | 4.1.3    | Fault Coverage Evaluation Methodology        |

|   |     | 4.1.4    | Area, Power and Delay Evaluation Methodology |

|   | 4.2 | RAS I    | Seatures in the Baseline Processor           |

| 5 | Reg | gister I | Dataflow Validation                          |

|   | 5.1 | Introd   | uction                                       |

|   | 5.2 | Regist   | er Dataflow Failures                         |

|   | 5.3 | End-to   | p-End Dataflow Validation                    |

|   |     | 5.3.1    | Signature-Based Protection: General Idea     |

|   |     | 5.3.2    | Failure Recovery                             |

|   |     | 5.3.3    | Microarchitectural Changes                   |

|   | 5.4 | End-to   | p-End Register Value and Dataflow Validation |

|   |     | 5.4.1    | Implementing End-to-End Residue Checking     |

|   |     | 5.4.2    | Integrating Signatures with Residues         |

|   |     | 5.4.3    | Microarchitectural Changes                   |

|   |     | 5.4.4    | Examples                                     |

|   | 5.5 | Signat   | ure Generation Policies                      |

|   |     | 5.5.1    | Round-Robin Policies                         |

|   |     |         | CON                                                 | TENTS | • | xi  |

|---|-----|---------|-----------------------------------------------------|-------|---|-----|

|   |     | 5.5.2   | Minimum In-Flight Use Policy                        |       |   | 83  |

|   |     | 5.5.3   | Physical Register Policy                            |       |   | 83  |

|   |     | 5.5.4   | Static Policy                                       |       |   | 84  |

|   |     | 5.5.5   | Enhanced Static Policy                              |       |   | 86  |

|   | 5.6 | Evalua  | ation                                               |       |   | 90  |

|   |     | 5.6.1   | Coverage Results                                    |       |   | 91  |

|   |     | 5.6.2   | Overheads                                           |       |   | 95  |

|   | 5.7 | Relate  | ed Work                                             |       |   | 101 |

|   | 5.8 | Conclu  | asions                                              |       |   | 105 |

| 6 | Con | ntrol F | low Recovery Validation                             |       |   | 107 |

|   | 6.1 | Introd  | uction                                              |       |   | 107 |

|   | 6.2 | Contro  | ol Flow Recovery in Modern OoO Processors: Overvio  | ew    |   | 108 |

|   | 6.3 | Contro  | ol Flow Recovery Failures                           |       |   | 110 |

|   | 6.4 | End-T   | o-End Validation of RAT State Recovery              |       |   | 113 |

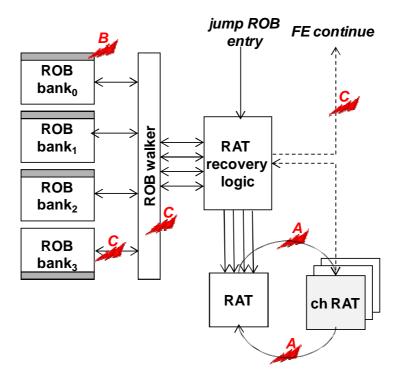

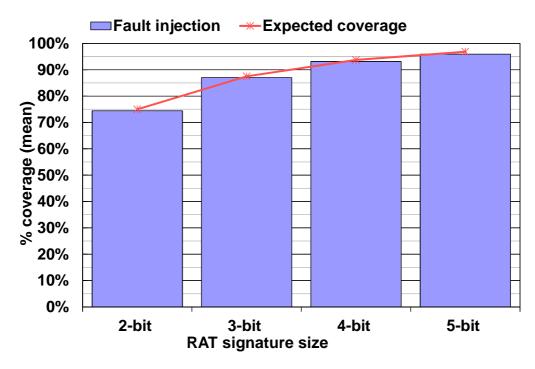

|   |     | 6.4.1   | RAT State Signature Tracking                        |       |   | 113 |

|   |     | 6.4.2   | RAT State Signature Validation                      |       |   | 118 |

|   |     | 6.4.3   | Microarchitectural Changes                          |       |   | 119 |

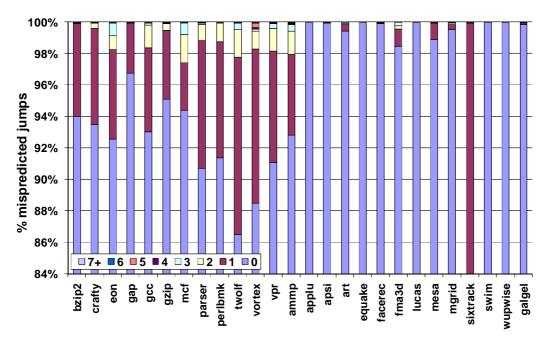

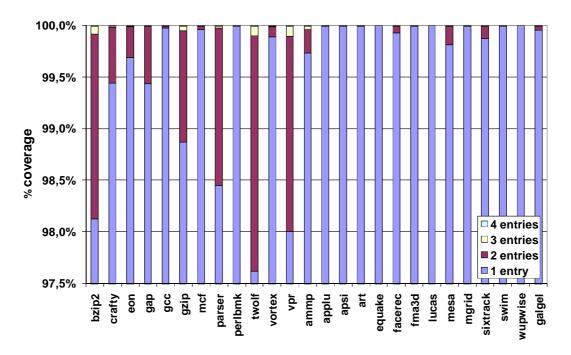

|   | 6.5 | End-T   | o-End Validation of Instruction Squashing           |       |   | 120 |

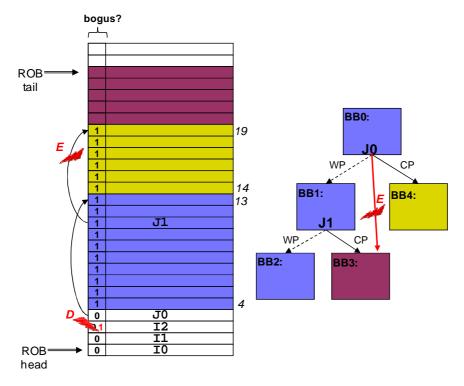

|   |     | 6.5.1   | Bogus Region Tracking                               |       |   | 120 |

|   |     | 6.5.2   | Bogus Region Validation                             |       |   | 122 |

|   |     | 6.5.3   | Microarchitectural Changes                          |       |   | 124 |

|   | 6.6 | Evalua  | ation                                               |       |   | 124 |

|   |     | 6.6.1   | Coverage Results                                    |       |   | 124 |

|   |     | 6.6.2   | Overheads                                           |       |   | 128 |

|   | 6.7 | Conclu  | asions                                              |       |   | 132 |

| 7 | Mei | mory I  | Flow Validation                                     |       |   | 135 |

|   | 7.1 | Introd  | uction                                              |       |   | 135 |

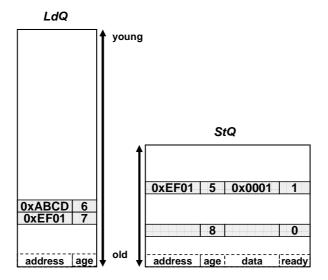

|   | 7.2 | Load-S  | Store Queue: Overview                               |       |   | 136 |

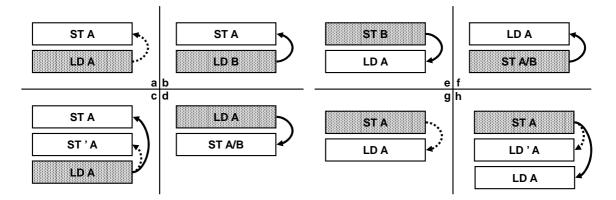

|   | 7.3 | Load-S  | Store Queue Failures                                |       |   | 138 |

|   | 7.4 | LSQ N   | Memory Ordering Tracking and Validation: General Id | dea   |   | 140 |

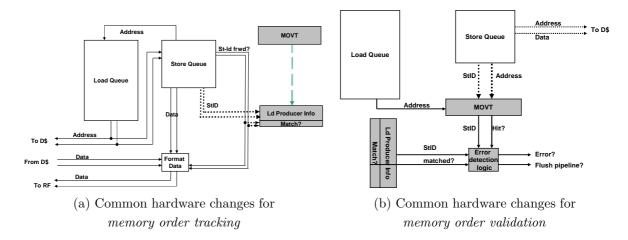

|   |     | 7.4.1   | Microarchitectural Changes                          |       |   | 141 |

|   |     | 7.4.2   | LSQ Memory Ordering Tracking                        |       |   | 142 |

|   |     | 7.4.3   | LSQ Memory Order Validation                         |       |   | 143 |

|   |     | 7.4.4   | Failure Recovery                                    |       |   | 145 |

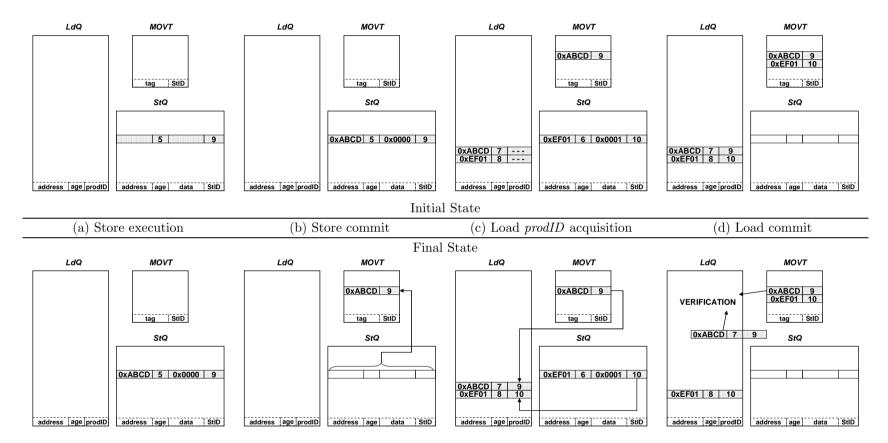

|   | 7.5 | Design  | n #1: MOVT Access at Execute                        |       |   | 145 |

|   |     |         |                                                     |       |   |     |

|     | _ | CONTENTS |

|-----|---|----------|

| XII | • |          |

|                  | 7.6    | Design #2: Minimal prodID Acquisition                                | 148 |  |  |  |

|------------------|--------|----------------------------------------------------------------------|-----|--|--|--|

|                  | 7.7    | Design #3: $MOVT$ Access at Allocate                                 | 150 |  |  |  |

|                  | 7.8    | Evaluation                                                           | 153 |  |  |  |

|                  |        | 7.8.1 Fault Coverage Methodology                                     | 153 |  |  |  |

|                  |        | 7.8.2 Area Overheads                                                 | 154 |  |  |  |

|                  |        | 7.8.3 Evaluation of Design #1: $MOVT$ Access at Execute              | 155 |  |  |  |

|                  |        | 7.8.4 Evaluation of Design #2: Minimal $prodID$ Acquisition          | 158 |  |  |  |

|                  |        | 7.8.5 Evaluation of Design #3: $MOVT$ Access at Allocate             | 159 |  |  |  |

|                  | 7.9    | Conclusions                                                          | 163 |  |  |  |

| 8                | Aut    | comated Fault Localization and Diagnosis                             | 165 |  |  |  |

|                  | 8.1    | Introduction                                                         |     |  |  |  |

|                  | 8.2    | Automated Fault Localization and Diagnosis: Proposed System Overview |     |  |  |  |

|                  | 8.3    | Event Generation                                                     |     |  |  |  |

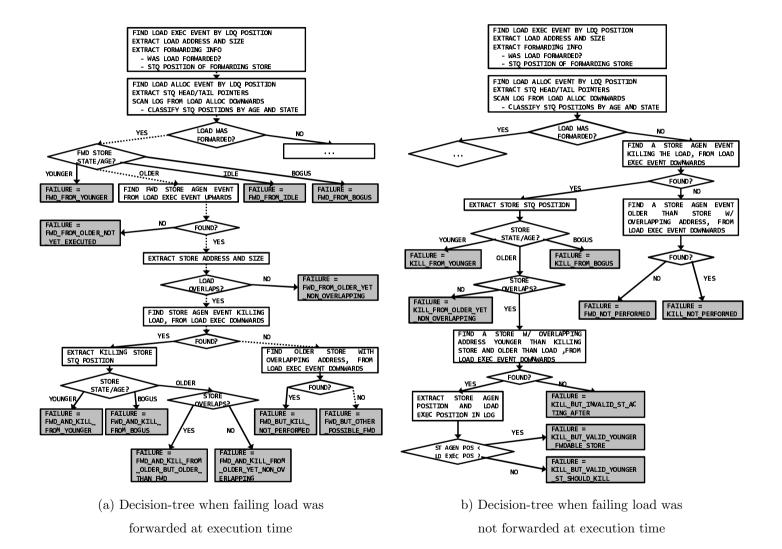

|                  | 8.4    | Diagnosis Algorithm                                                  | 170 |  |  |  |

|                  | 8.5    | Logging System Implementation                                        | 176 |  |  |  |

|                  |        | 8.5.1 Microarchitectural Changes                                     | 177 |  |  |  |

|                  |        | 8.5.2 System-Level Interaction                                       | 180 |  |  |  |

|                  | 8.6    | Evaluation                                                           | 182 |  |  |  |

|                  |        | 8.6.1 Diagnosis Coverage Results                                     | 182 |  |  |  |

|                  |        | 8.6.2 Overheads                                                      | 186 |  |  |  |

|                  | 8.7    | Related Work                                                         | 188 |  |  |  |

|                  | 8.8    | Conclusions                                                          | 191 |  |  |  |

| 9                | Con    | Conclusions                                                          |     |  |  |  |

|                  | 9.1    | Publications                                                         | 194 |  |  |  |

|                  | 9.2    | Open Research Directions                                             | 195 |  |  |  |

| $\mathbf{A}_{]}$ | ppen   | dix:                                                                 |     |  |  |  |

| A                | Bas    | eline Processor Microarchitecture                                    | 197 |  |  |  |

|                  | A.1    | Processor Frontend                                                   | 197 |  |  |  |

|                  | A.2    | Processor Backend                                                    | 199 |  |  |  |

| Bi               | ibliog | graphy                                                               | 209 |  |  |  |

# List of Figures

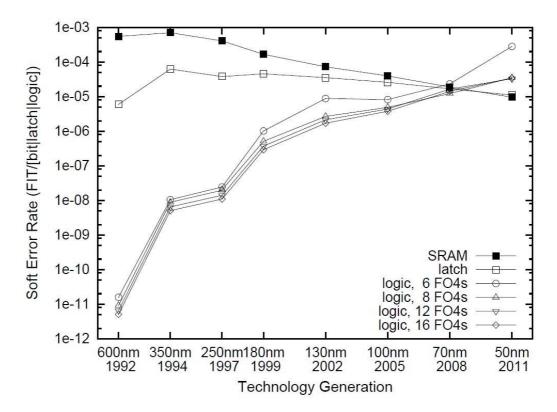

| 1.1  | SER trends for SRAM cells, latches and combinational logic                  | 3  |

|------|-----------------------------------------------------------------------------|----|

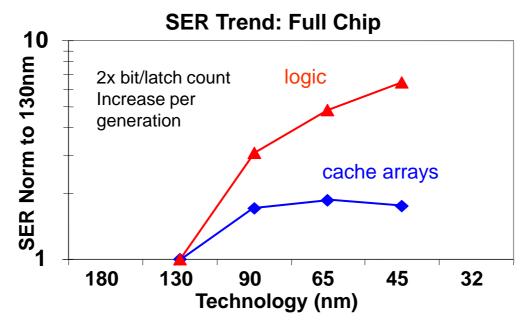

| 1.2  | Chip-level SER trends for caches and logic                                  | 4  |

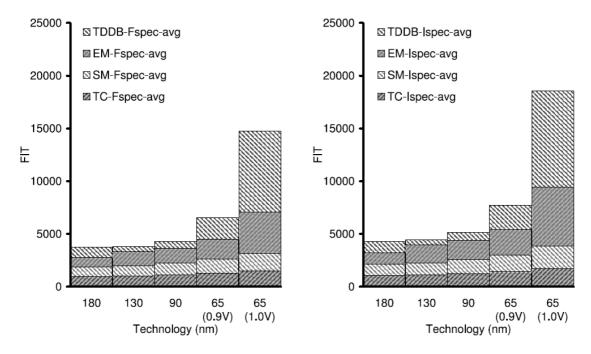

| 1.3  | Wear-out failure phenomena FIT contribution breakdown                       | 6  |

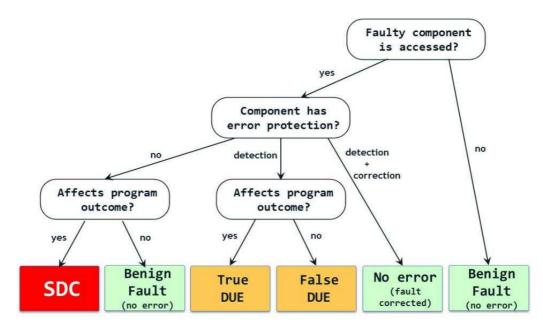

| 2.1  | Classification of faults effects                                            | 19 |

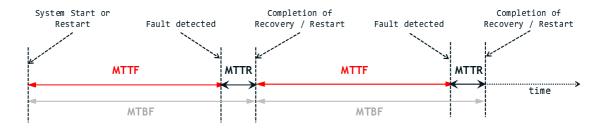

| 2.2  | Vendors fault tolerance metrics                                             | 21 |

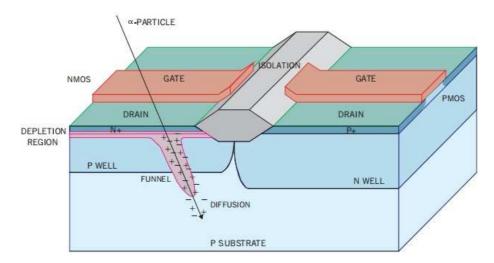

| 2.3  | Particle strike causing current disturbance                                 | 22 |

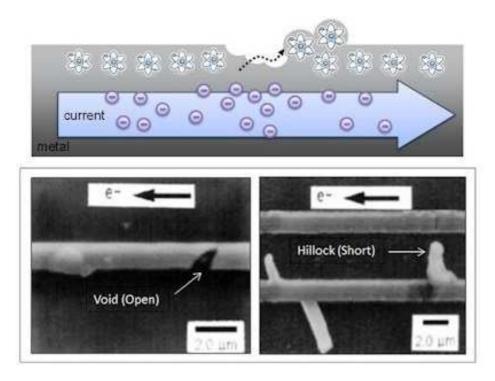

| 2.4  | Physical wear-out phenomena, open and short creation                        | 23 |

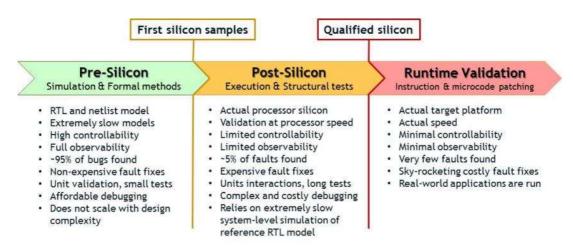

| 2.5  | Validation domains and characteristics                                      | 25 |

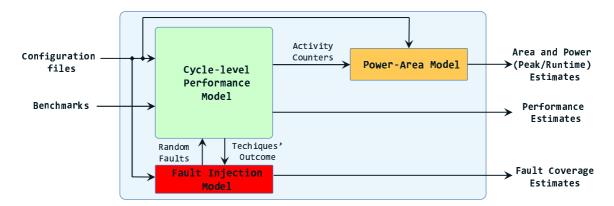

| 4.1  | Global structure of our evaluation framework                                | 48 |

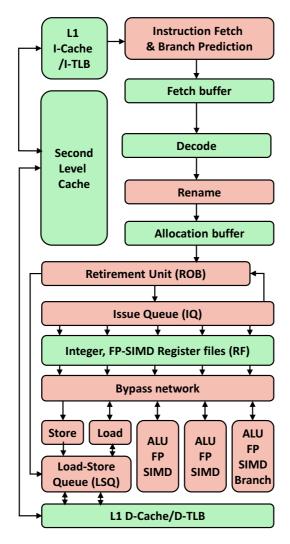

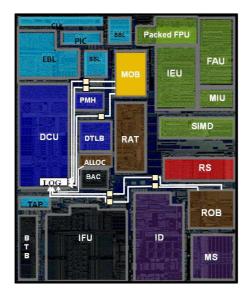

| 4.2  | Baseline processor microarchitecture                                        | 50 |

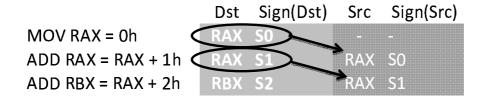

| 5.1  | Register signature assignment among dependent instructions: an ex-          |    |

|      | ample                                                                       | 64 |

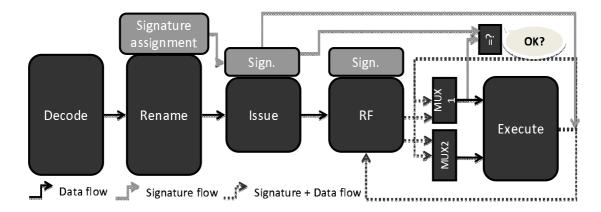

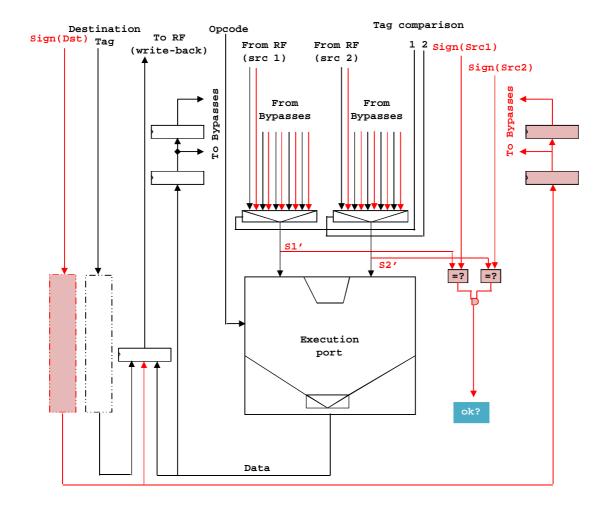

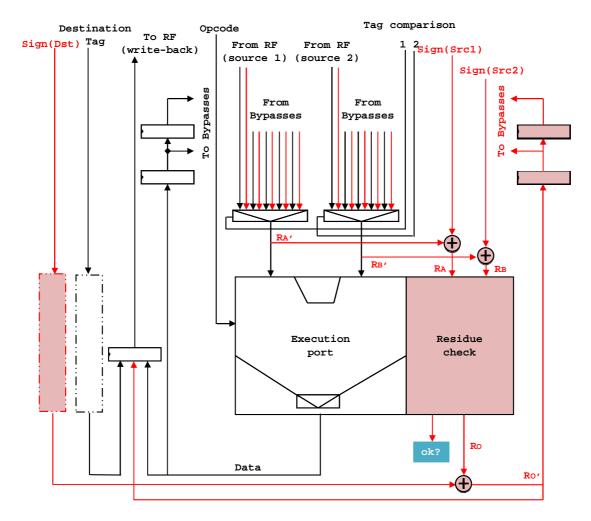

| 5.2  | End-to-end signature checking: extensions in the core data<br>flow          | 65 |

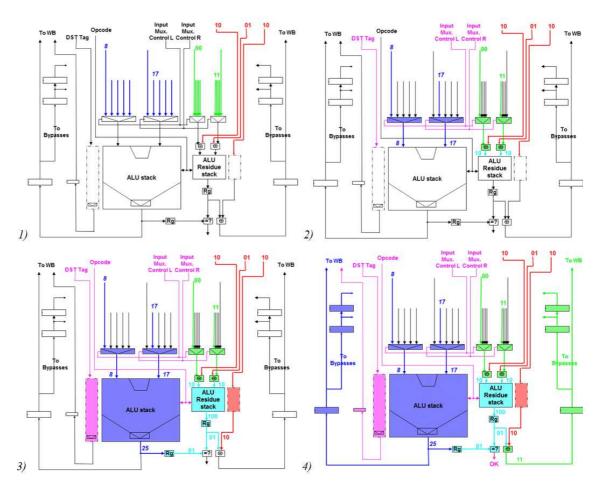

| 5.3  | End-to-end signature checking: extensions in the backend logic              | 66 |

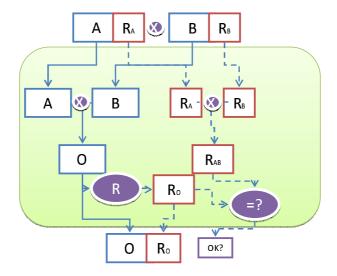

| 5.4  | Concurrent error detection with residue codes                               | 71 |

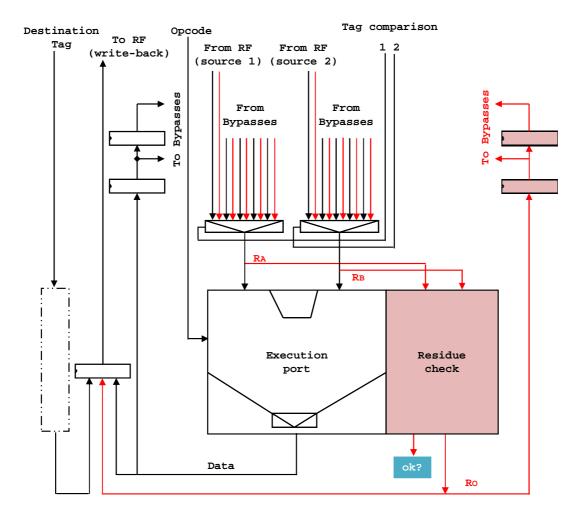

| 5.5  | End-to-end residue checking: extensions in the backend logic                | 72 |

| 5.6  | Combined end-to-end signature and residue checking scheme: exten-           |    |

|      | sions in the backend logic                                                  | 74 |

| 5.7  | End-to-end signatures and residues operation: fault-free scenario ex-       |    |

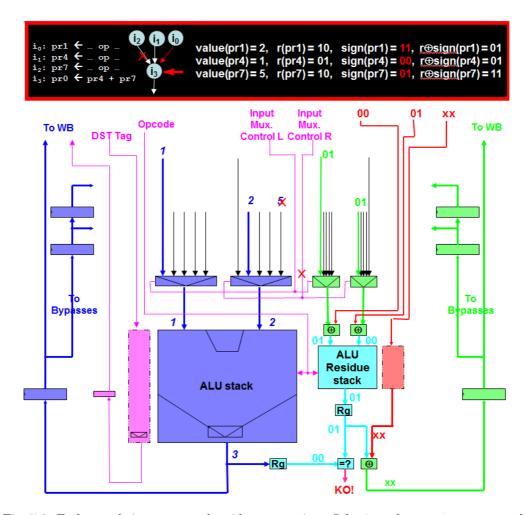

|      | ample                                                                       | 77 |

| 5.8  | End-to-end signatures and residues operation: Selection of wrong in-        |    |

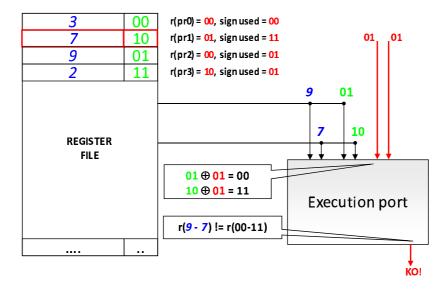

|      | puts example                                                                | 79 |

| 5.9  | End-to-end signatures and residues operation: Wrong Register File           |    |

|      | Access example                                                              | 80 |

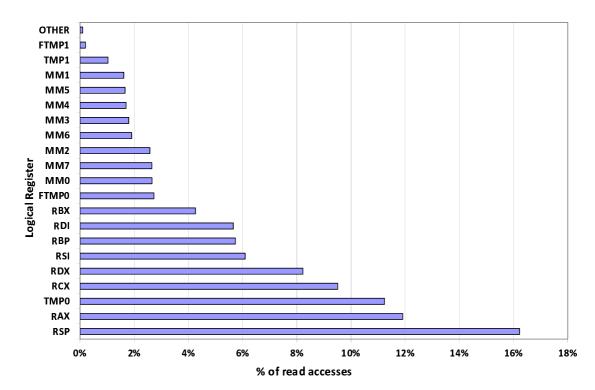

| 5.10 | Distribution of usage for the different logical registers across all bench- |    |

|      | marks                                                                       | 85 |

#### xiv · LIST OF FIGURES

| 5.11 | Signature masking enhancement to boost coverage for 'Selection of wrong inputs' case: extensions in the backend logic | 88  |

|------|-----------------------------------------------------------------------------------------------------------------------|-----|

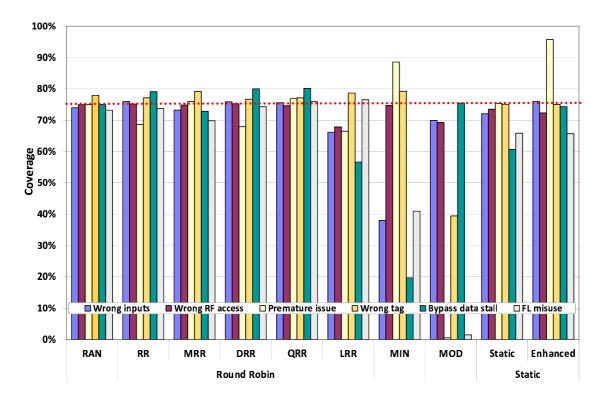

| 5.12 | Coverage results for all policies and error scenarios for 2-bit signatures                                            | 92  |

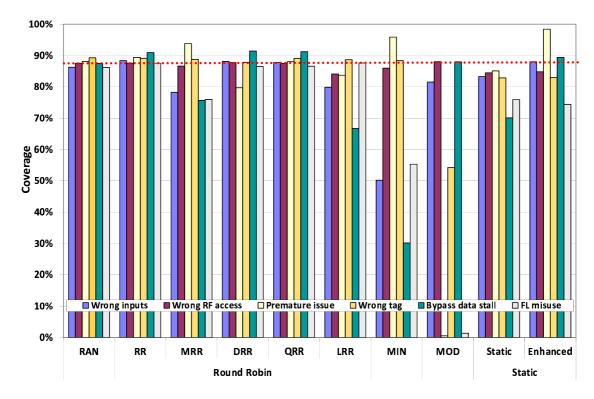

| 5.13 | Coverage results for all policies and error scenarios for 3-bit signatures                                            | 94  |

| 6.1  | Failure scenarios related to RAT state history reconstruction                                                         | 111 |

| 6.2  | Failure scenarios related to identification of control-flow dependent in-                                             |     |

|      | structions                                                                                                            | 112 |

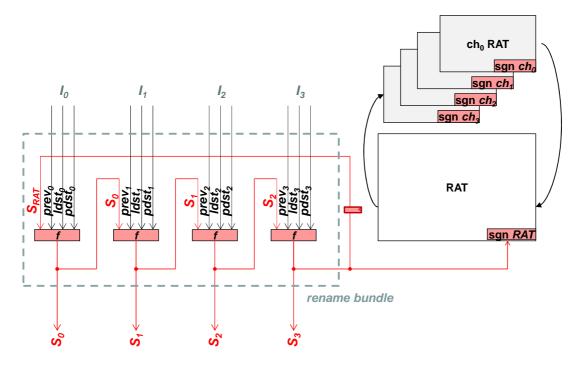

| 6.3  | RAT state signature generation: extensions in the rename logic                                                        | 114 |

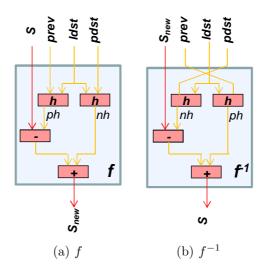

| 6.4  | $f$ and $f^{-1}$ blocks implementation                                                                                | 117 |

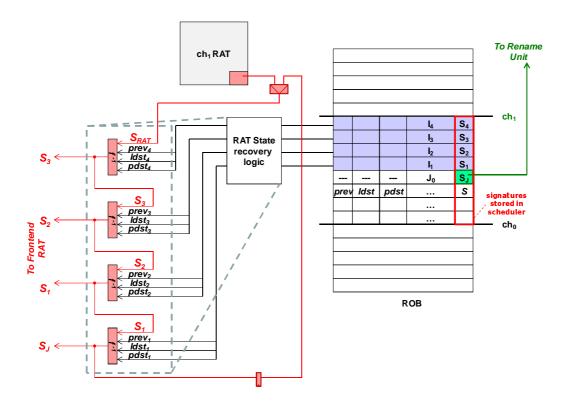

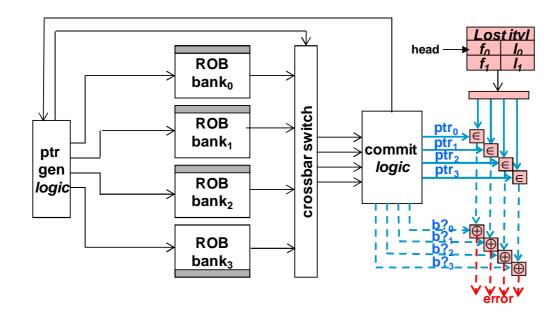

| 6.5  | RAT state signature reconstruction: extensions in the commit logic .                                                  | 118 |

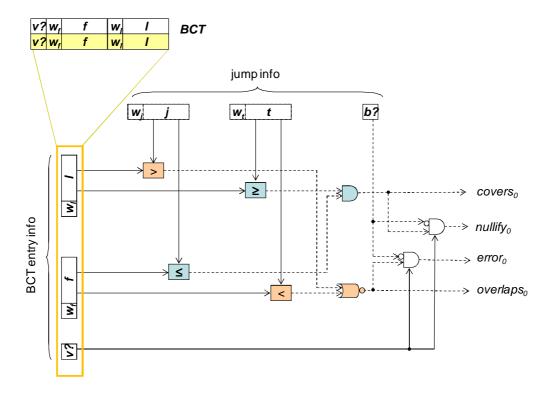

| 6.6  | BCT mechanism: extensions for bogus region tracking and validation .                                                  | 121 |

| 6.7  | BCT mechanism: extensions in the commit logic                                                                         | 123 |

| 6.8  | Coverage for end-to-end RAT state signatures                                                                          | 125 |

| 6.9  | Breakdown of number of younger resolved bogus regions for each mispredicted branch                                    | 126 |

| 6.10 | Coverage for identification of control-flow dependent instructions (1 to                                              |     |

|      | 4 BCT entries)                                                                                                        | 127 |

| 7.1  | A typical LSQ configuration                                                                                           | 136 |

| 7.2  | Failure scenarios related to LSQ operation                                                                            | 138 |

| 7.3  | MOVT hardware template                                                                                                | 141 |

| 7.4  | Memory ordering tracking and validation: an example                                                                   | 144 |

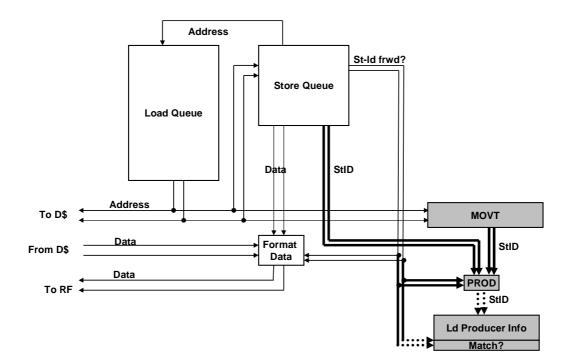

| 7.5  | MOVT hardware for design #1: prodID $acquisition$ at execute time .                                                   | 146 |

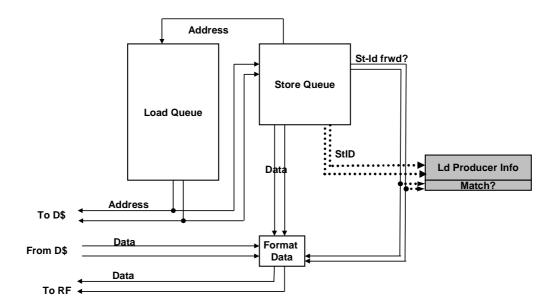

| 7.6  | MOVT hardware for design #2: minimal prodID $acquisition$                                                             | 149 |

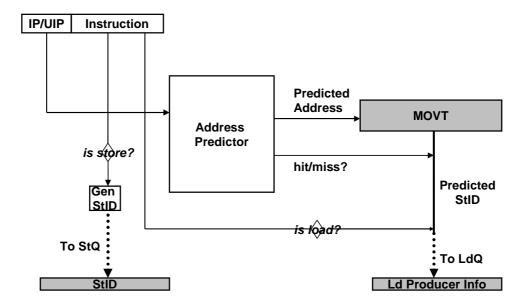

| 7.7  | MOVT hardware for design #3: prodID $acquisition$ at allocate time .                                                  | 151 |

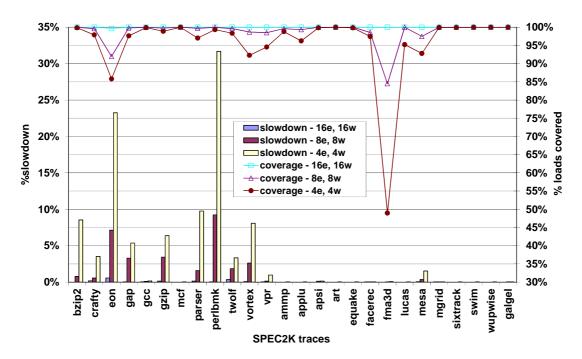

| 7.8  | Coverage and slowdown for different fully-associative $MOVTs$ based                                                   |     |

|      | on <i>prodID</i> acquisition at execute time                                                                          | 156 |

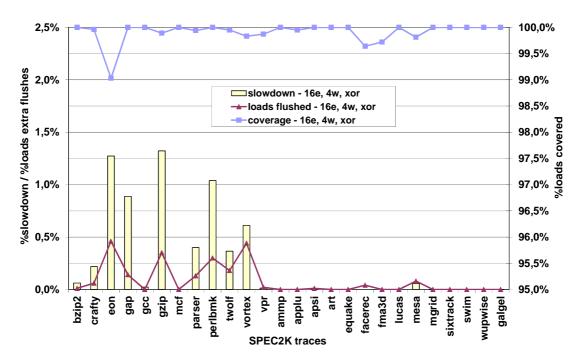

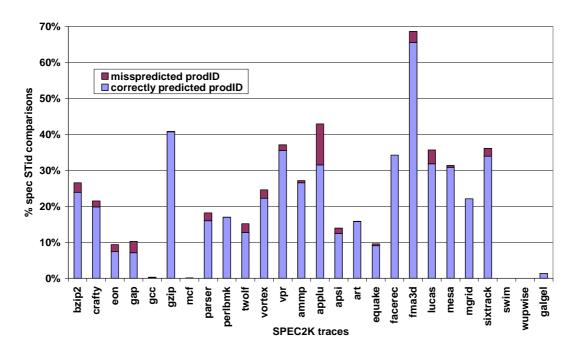

| 7.9  | Detailed evaluation of a 16 entries, 4-way MOVT based on prodID                                                       |     |

|      | acquisition at execute time                                                                                           | 157 |

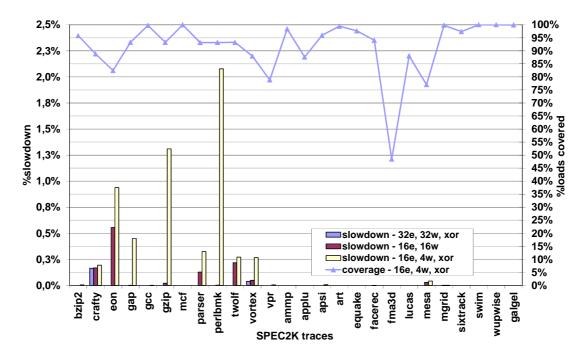

| 7.10 | Coverage and slowdown for different $minimalist\ MOVTs$ configurations                                                | 159 |

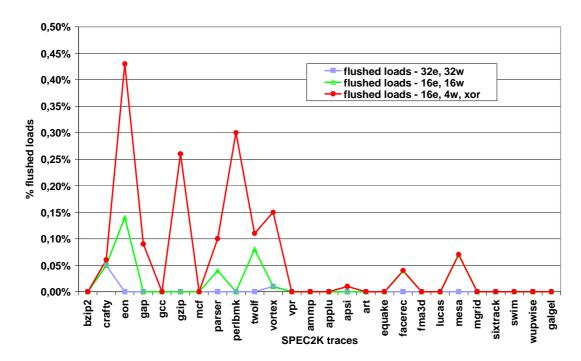

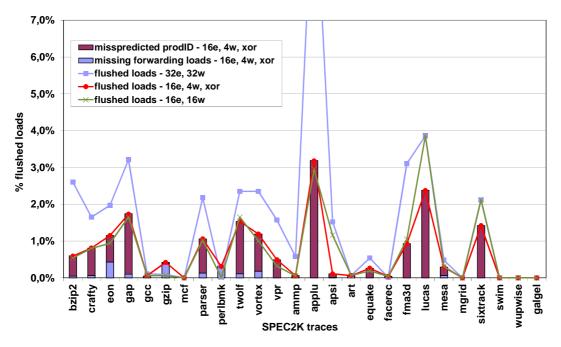

| 7.11 | Flushed loads for different $minimalist\ MOVTs$ configurations                                                        | 160 |

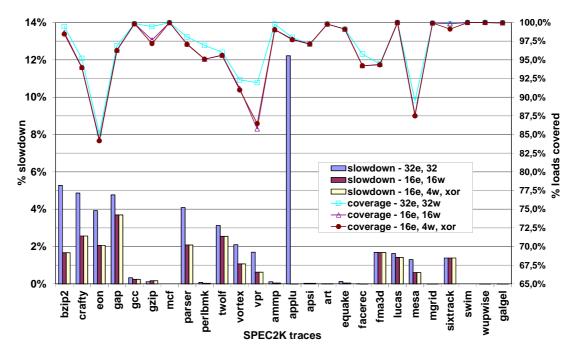

| 7.12 | Coverage and slowdown for different $MOVT$ s based on prodID $acqui$                                                  |     |

|      | sition at allocate time                                                                                               | 161 |

| 7.13 | Breakdown of speculative prodID comparisons for a 32-entries fully-                                                   |     |

|      | associative $MOVT$ based on prodID $acquisition$ at allocate time                                                     | 162 |

#### LIST OF FIGURES · xv

| 7.14 | Breakdown of pipeline flushes for different $MOVTs$ based on prodID               |     |

|------|-----------------------------------------------------------------------------------|-----|

|      | acquisition at allocate time                                                      | 162 |

| 8.1  | Event driving latches: extensions in the processor                                | 167 |

| 8.2  | Diagnosis algorithm showing failure type determination: high-level code           | 173 |

| 8.3  | Log of a LSQ failure: an example                                                  | 174 |

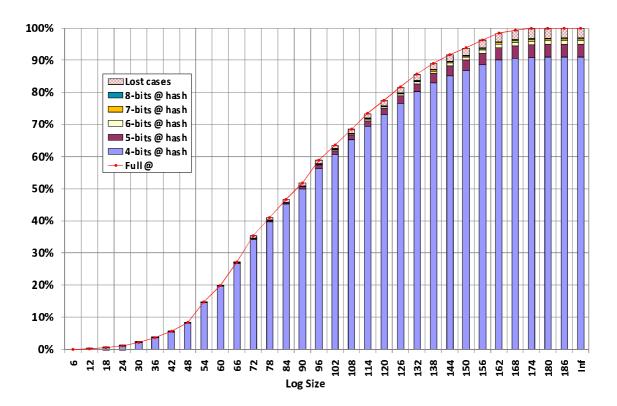

| 8.4  | Accumulated diagnosis coverage versus log size                                    | 175 |

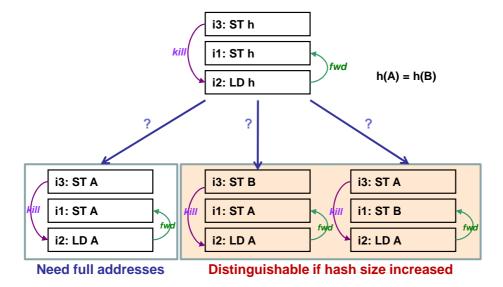

| 8.5  | Address hashing undistinguishable failure scenarios: an example $\ . \ . \ .$     | 176 |

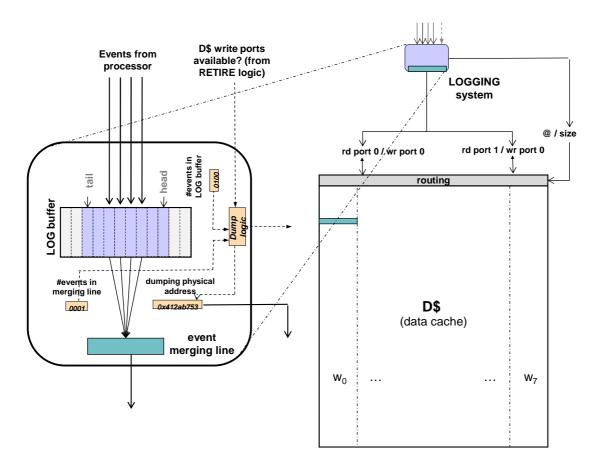

| 8.6  | Activity logging mechanism: hardware design and integration                       | 178 |

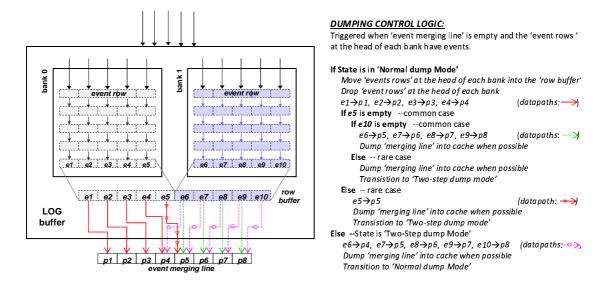

| 8.7  | Log buffer: hardware organization                                                 | 179 |

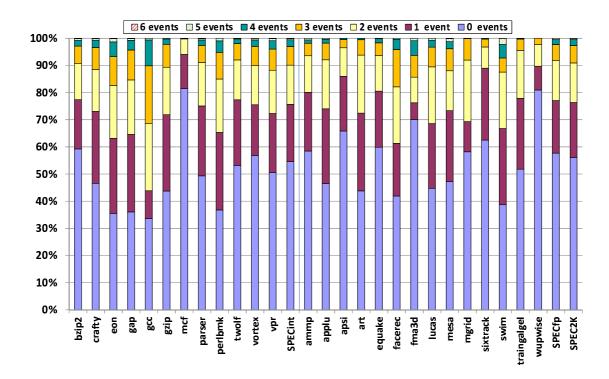

| 8.8  | Breakdown of number of LSQ log events generated per cycle                         | 183 |

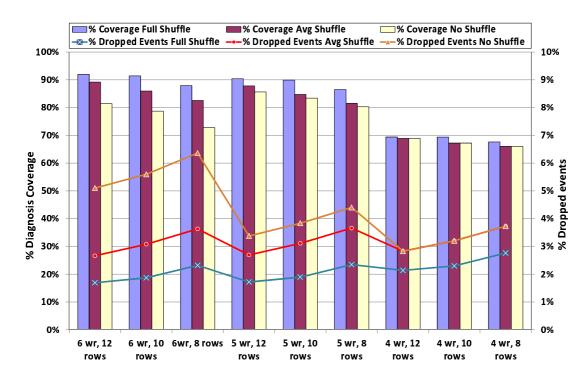

| 8.9  | Diagnosis coverage and dropped events for different ${}^{\circ}LOG\ buffer"$ con- |     |

|      | figurations. 'Xwr, Yrows' stands for number of writable events per cy-            |     |

|      | cle, total number of 'event rows'                                                 | 184 |

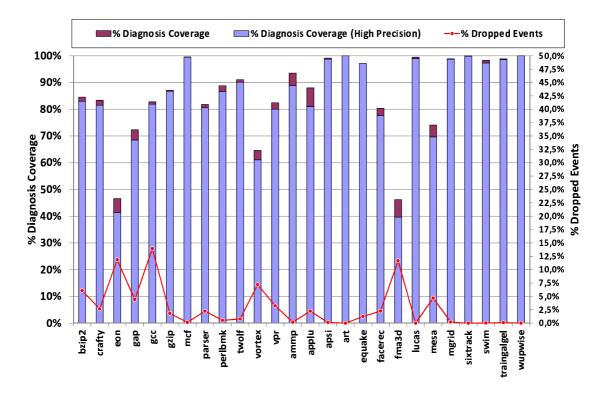

| 8.10 | Diagnosis coverage for a '5wr,12rows $LOG\ buffer$ ' configuration                | 185 |

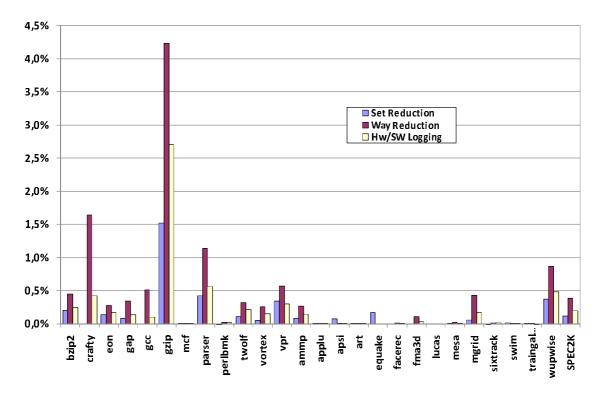

| 8.11 | Slowdown induced by a '5wr,12rows $LOG\ buffer$ ' configuration                   | 187 |

# List of Tables

| 3.1 | Comparison of hardware-level global re-execution techniques                      | 32  |

|-----|----------------------------------------------------------------------------------|-----|

| 3.2 | Comparison of error coding techniques                                            | 36  |

| 3.3 | Comparison of circuit-level techniques                                           | 40  |

| 3.4 | Comparison of software and hybrid techniques                                     | 41  |

| 4.1 | Benchmarks used to evaluate our solutions                                        | 49  |

| 4.2 | Simulator configuration                                                          | 52  |

| 5.1 | Register signature mismatches corresponding to real register dataflow            |     |

|     | errors                                                                           | 68  |

| 5.2 | Values, residues, signatures and combined residues-signatures for fault-         |     |

|     | free example                                                                     | 78  |

| 5.3 | Mask table for a processor with two execution ports $(P0 \text{ and } P1)$ , two |     |

|     | by<br>pass levels (BL0 and BL1) and the write-back port (WB)                     | 89  |

| 5.4 | Values of the masks set up at every bypass level and execution port $$ .         | 89  |

| 5.5 | Area and power overheads for the different signature generation poli-            |     |

|     | cies when end-to-end residue is absent                                           | 97  |

| 5.6 | Area and power overheads for the different signature generation poli-            |     |

|     | cies when end-to-end residue is implemented                                      | 99  |

| 5.7 | Overheads summary of implementing end-to-end signature checking                  |     |

|     | and end-to-end residue checking                                                  | 100 |

| 5.8 | Comparative table of techniques that detect errors in the register               |     |

|     | dataflow                                                                         | 101 |

| 5.9 | Blocks and logic protection for register dataflow validation techniques          | 103 |

| 6.1 | Commit time assertion checks for instruction squashing verification .            | 123 |

| 6.2 | Area and power overheads. $nb$ SGN stands for $n$ -bits RAT state sig-           |     |

|     | natures                                                                          | 129 |

| 6.3 | Area and power overheads. ne BCT stands for n BCT entries                        | 130 |

#### xviii · LIST OF TABLES

| 6.4 | Area and power overheads. nb SGN stands for n-bits RAT state sig-          |     |

|-----|----------------------------------------------------------------------------|-----|

|     | natures and ne BCT for n BCT entries                                       | 131 |

| 7.1 | Protocol when loads hit the $MOVT$ at commit time (Design #1)              | 147 |

| 7.2 | Protocol when loads miss the $MOVT$ at commit time (Design $\#1$ )         | 147 |

| 7.3 | Protocol when loads hit the $MOVT$ at commit time (Design $\#2$ )          | 149 |

| 7.4 | Protocol when loads miss the $MOVT$ at commit time (Design $\#2$ )         | 150 |

| 7.5 | Protocol when loads hit the $MOVT$ at commit time (Design #3)              | 152 |

| 7.6 | Protocol when loads miss the $MOVT$ at commit time (Design #3)             | 152 |

| 7.7 | Area overhead w.r.t. the LSQ, for different $MOVT$ sizes $\dots$           | 155 |

| 7.8 | Coverage, slowdown and area cost for different $MOVT$ configurations       | 155 |

| 8.1 | Diagnosable LSQ failure scenarios: descriptions and required analysis      |     |

|     | window size                                                                | 172 |

| 8.2 | Area, peak dynamic power and cycle time overhead for different ' $LOG$ -   |     |

|     | GING systems'                                                              | 188 |

| 8.3 | Comparative table for fault localization, logging and diagnosis techniques | 190 |

# Glossary of Acronyms and Abbreviations

ACE Architecturally Correct Execution.

AGEN Address Generation.

AGU Address Generation Unit.

**ALLOC** Allocation.

**ALU** Arithmetic and Logic Unit.

AR-SMT Active and Redundant Simultaneous Multi-Threading.

ATE Automatic Test Equipment.

ATPG Automatic Test Pattern Generation.

AVF Architecture Vulnerability Factor.

BCS Beta Core Solution.

BCT Bogus Check Table.

BER Backward Error Recovery.BICS Built-In Current Sensor.

BIST Built-In Self Test.

BTB Branch Target Buffer.

**CAM** Content Addressable Memory.

**CFCSS** Control Flow Checking by Software Signatures.

CFG Control Flow Graph.

ch RAT Checkpoint RAT.

CMOS Complementary Metal-Oxide Semiconductor.

CMP Chip Multiprocessor.CPU Central Processing Unit.

**CRAFT** CompileR Assisted Fault Tolerance.

**CRC** Cyclic Redundancy Code.

**CRT** Chip-level Redundant Threading.

**CRTR** Chip-level Redundant Threading with Recovery.

**CSM** Continuous Signature Monitoring.

**D**\$ Data Cache.

**DDFV** Dynamic DataFlow Verification.

**DDR3 SDRAM** Double Data Rate type three Synchronous Dynamic Random-Access Memories.

**DEC-TED** Double Error Correction Triple Error Detection.

#### xx · GLOSSARY

**DFCM** Differential Finite Context Method.

DFG Data Flow Graph.DFT Design for Testability.

**DIVA** Dynamic Implementation Verification Architecture.

**DMR** Dual Modular Redundancy.

**DRAM** Dynamic Random-Access Memory.

**DRR** Double Round Robin signature generation policy.

**DUE** Detected Unrecoverable Error.

**DVFS** Dynamic Voltage and Frequency Scaling.

**ECC** Error Correcting Code.

**EDDI** Error Detection by Duplicated Instructions.

**EM** Electromigration.

**FER** Forward Error Recovery.

FIFO First In First Out.FIT Failure In Time.

FL Free List.FO4 Fan-out of 4.FP Floating Point.

**FRITS** Functional Random Instruction Testing at Speed.

**FWD** Forwarding.

**GDXC** Generic Debug eXternal Connection.

**HCI** Hot Carrier Injection.

**HPC** High-Performance Computing.

I\$ Instruction Cache.IC Integrated Circuit.

**IFRA** Instruction Footprint Recording and Analysis.

**INT** Integer.

I/O Input/Output.IQ Issue Queue.

**ISA** Instruction Set Architecture.

JEU Jump Execution Unit.L2\$ Second Level Cache.

LD Load.

LDEXEC Load Execution.LdQ Load Queue.

$\begin{tabular}{ll} \textbf{LEA} & Load Effective Address.} \end{tabular}$

**LLC** Last Level Cache.

LRR Logical Round Robin signature generation policy.

LRU Least Recently Used.LSQ Load/Store Queue.

MCA Machine Check Architecture.

MIN Minimum signature generation policy.

MOB Memory Order Buffer.

MOD Modulo signature generation policy.

MOVT Memory Order Validation Table.

MRR Minimum Round Robin signature generation policy.

MSHRMiss Status Holding Register.MTBFMean Time Between Failures.

MTTF Mean Time To Failure.MTTR Mean Time To Repair.

MUX Multiplexor.

NBTI Negative Bias Temperature Instability.NMOS N-type Metal Oxide Semiconductor.

**OS** Operating System.

**PBTI** Positive Bias Temperature Instability.

PC Program Counter.

pdst Physical Register Destination.

**PHT** Pattern History Table.

PLA Programmable Logic Arrays.

**PMOS** P-type Metal Oxide Semiconductor.

PRF Physical Register File.PSA Path Signature Analysis.

**PSMI** Periodic State Management Interrupt.

**QRR** Quad Round Robin signature generation policy.

RAN Random signature generation policy.RAS Reliability-Availability-Serviceability.

**RAT** Register Alias Table.

**RF** Register File.

RMT Redundant Multi Threading.RNA Register Name Authentication.

**ROB** Re-Order Buffer.

**RR** Round Robing signature generation policy.

**RTL** Register Transfer Language.

SBU Single Bit Upset.

**SDC** Silent Data Corruption.

**SEC-DED** Single Error Correction Double Error Detection.

SelRSelective Replication.SERSoft Error Rate.SEUSingle Event Upset.

**SGN** Signature.

SHREC SHared REsource Checker.

SIMD Single-Instruction Multiple Data.

SIS Signatured Instruction Streams.

Slick Slice-Based Locality Exploitation for Efficient Redundant Multithreading.

SMT Simultaneous Multi Threading.

SpecIV Speculative Instruction Validation.

SRAM Static Random-Access Memory.

**SRMT** Software-based Redundant Multithreading.

#### xxii · GLOSSARY

**SRT** Simultaneously and Redundantly Threading.

**SRTR** Simultaneously and Redundantly Threaded with Recovery.

Store.

StQ Store Queue.SW Software.

SWIFT Software Implemented Fault Tolerance.TAC Timestamp-based Assertion Checking.

**TBFD** Trace-Based Fault Diagnosis.

**TDDB** Time Dependent Dielectric Breakdown.

**TDP** Thermal Design Power.

TLB Translation Lookaside Buffer.TMR Triple Modular Redundancy.

${\bf TRUMP} \quad {\bf Triple \ Redundancy \ Multiplication \ Protection}.$

**TTF** Time To Failure.

TVF Time Vulnerability Factor.VLIW Very Long Instruction Word.

**XOR** Exclusive Or.

## CHAPTER 1

# **INTRODUCTION**

Historically, fault tolerant designs have been applied to niche safety-critical and mission-critical segments to provide high reliability levels against hardware faults.

However, the increasing transistor miniaturization and subsequent supply voltage reductions, together with growing design complexities are amplifying the susceptibility of all computing systems to runtime errors: reliability is becoming a concern for products ranging from mobile devices up to mainstream computers.

Depending on the target market segments, processors are designed considering certain error rate specifications. However, whereas these specifications stay constant across product generations, the inherent error rates due to transient, permanent and design errors do increase. Meeting error rate specifications requires trading off performance, power or cost to implement fault tolerance techniques or to improve the validation phases.

Traditional fault tolerance solutions based on re-execution were devised in a time when high performance and power penalties were assumed for the sake of high reliability levels. However, commodity segments are extremely customer-sensitive and impose requirements that existing approaches cannot offer. Resorting to error detection-correction codes to protect memory arrays in commodity segments will soon not suffice, as combinational logic turns into the dominant source of failures. In the absence of new fault tolerance solutions, traditional online error detection methods would counteract the benefits of technology scaling and would offset the actual growth of the microprocessor industry.

At the same time, the increasing design complexity together with shortening timeto-market schedules are imposing important challenges in guaranteeing that processors are error-free before shipment. The costs of post-silicon validation currently

#### 2 · Chapter 1. Introduction

overpass the costs of the design phases, and the number of bugs found in the validation phases and once products hit the market is projected to rapidly increase.

In this thesis we focus on the error detection, error localization and diagnosis aspects of fault tolerance. Error detection is a pre-requisite to support other aspects of fault tolerance, whereas bug localization and debugging dominate validation efforts.

This thesis explores two directions to address some of the critical challenges introduced by unreliable technologies and by the limitations of current validation approaches. We first explore low-cost effective solutions to detect multiple sources of failures in commodity processors during their lifetime. Then, we explore post-silicon approaches that target the problems of bug detection, localization and diagnosis by relying on the features of our error detection mechanisms.

This chapter is organized as follows. Section 1.1 provides a detailed motivation for this work by presenting the main reliability challenges and trends targeted in this thesis. In Section 1.2 we state the research problems and the main objectives targeted in this thesis. Section 1.3 describes the new approaches that thesis proposes to effectively address the research objectives. Section 1.4 enumerates the main contributions of our work, and finally we describe the organization of this document in Section 1.5.

#### 1.1 Motivation: Reliability Challenges

There are several reliability challenges brought by technology scaling and by the complexity of designs that have driven the research of this thesis. We describe them in the following two sections.

#### 1.1.1 Impact of Transistor Scaling on Lifetime Reliability

The everlasting transistor miniaturization is radicalizing the error rates caused by particle strikes, also known as soft errors [129]. Furthermore, other sources of failure that were considered as a manufacturing problem in the past, are now emerging as a threat to processor lifetime reliability. We describe for these failure mechanisms the error rate trends introduced by technology scaling.

#### Increasing Cell and Control Logic Susceptibility to Soft Errors

Prediction of soft errors scaling trends for CMOS are haunting. On one hand, as SRAM cells shrink their soft error rate (SER) is expected to decrease due to a reduction in the susceptible area. On the other hand, SRAM cells will operate with

Fig. 1.1: SER trends for SRAM cells, latches and combinational logic [175]

lower charges and the  $Q_{crit}$  will decrease, amplifying the range of harmful particles. The former factor has dominated and offset the latter one in the past. However, this fact no longer seems to persists for SRAM cells. Alan Wood et al. [51] have reported that Oracle's technology scaling from 180nm to 65nm in the past caused a significant reduction in the SER error rates per bit, but from 40nm onwards to 28nm there was a reversal of this trend. Intel and Oracle [51, 133] indicated that the SER/bit for SRAM cells was slightly reducing after 45nm, and becoming almost constant.

The vulnerability for control logic has been traditionally lower than for SRAM cells or latches due to logical, electrical and timing masking effects [174]. However, Shivakumar et al. [175] estimated that the SER from logic would rise exponentially. Their study indicated that the effect of latching-window masking would be reduced drastically as transistors would shrink in size or frequency would increase (or pipe stages would decrease in length) [174, 175].

Figure 1.1 shows the soft error rate estimations for SRAM cells, latches and combinational logic for different pipeline depths and technologies<sup>1</sup>. It can be observed that the error rate trends for combinational logic was projected to increase at an

<sup>&</sup>lt;sup>1</sup>Error rates are expressed in FITs, that stands for Failures In Time. One FIT corresponds to one failure in one billion  $(10^9)$  hours.

#### 4 · Chapter 1. Introduction

Fig. 1.2: Chip-level SER trends for caches and logic [133]

exponential rate for all pipeline depths. Also, from 50nm onwards the SER of a 6/8/12/16 FO4 logic and the SER per latch were projected to be higher than the SER per SRAM cell. The study also estimated that logic would become the dominant source of soft errors and the SER contribution of unprotected SRAM cells would stay relatively constant (in absolute terms) [175].

This SER trend for combinational logic has been confirmed to be true nowadays [15]. In 2014, Intel has reported [133] that the contribution of caches to the chip SER is becoming flat, while at the same time the SER for chip logic continues to increase because the SER per latch is not decreasing fast enough with respect to Moore's Law (Figure 1.2).

Moreover, Wood has observed for 40nm and 28nm technologies that the SER of combinational logic approximately doubles when dropping voltage from 1.25V to 0.7V, and doubles again when reducing from 0.7V to 0.5V [51]. Therefore, designs will be limited in core-count and performance due to voltage limitations, unless efficient fault tolerance techniques (specially for logic) are found.

These results are game-changing: solutions like ECC or parity to reduce the SRAM SER will quickly become insufficient as logic becomes the dominant source of soft errors. Therefore, new efficient methods for protecting combinational logic are becoming essential to construct reliable systems.

#### New Sources of Failures Affecting Lifetime Reliability

Wear-out vulnerability, permanent faults and variations have traditionally been exclusively dealt by circuit and process engineers, because it has been considered as pure manufacturing problems, and not problems to be handled during runtime (i.e. not lifetime reliability problems). However, supply voltages are not scaling accordingly to transistor scaling<sup>2</sup>, resulting in increasing power densities, which at the same time is accelerating the problems of aging phenomena<sup>3</sup> and affecting processor lifetime reliability at a higher pace for new technologies.

Srinivasan et. al [191] have determined that the failure rate of a 65nm POWER4-like processor is 300% higher than the 180nm version of the processor. Time-dependent dielectric breakdown (TDDB) and electromigration (EM) represent the most damaging failure mechanisms, as Figure 1.3 shows. Failure rates caused by these phenomena will become more frequent and will radicalize due to their exponential dependence on temperature and because of decreasing interconnect dimensions.

With shrinking geometries, interconnects and transistors are becoming more vulnerable to the impact of variations introducing during the fabrication process. The thickness of the layers varies over the die area and as a consequence wear-out phenomena like electromigration will produce more frequent opens in the narrower portions, or shorts between neighboring or crossing conductors [42]. High-frequency circuits with minimal frequency guardband will be more prone to suffer from delay faults because of increased resistance induced by wearout, or because of the static variations of transistors parameters [23]. Similarly, bridging faults will appear due to short-circuit scenarios caused by electromigration.

Current testing approaches based on screening out processor infant mortality through temperature and voltage induce aging are therefore becoming obsolete and inadequate [23, 204]. As a consequence, an increasing number of faults due to weaker, variable transistors or due to latent manufacturing defects will manifest once the processor has been shipped and will cause failures before the target lifetime.

These facts call for new runtime solutions that are able to expand their error detection capabilities beyond soft errors, as new failure phenomena are becoming a problem for lifetime reliability.

<sup>&</sup>lt;sup>2</sup>Due to cell stability issues, leakage power hazards, etc.

<sup>&</sup>lt;sup>3</sup>Aging phenomena includes electromigration, stress migration, gate oxide or time dependent dielectric breakdown, thermal cycling [192], negative-bias temperature instability [6], among others.

#### 6 · Chapter 1. Introduction

Fig. 1.3: Wear-out failure phenomena FIT contribution breakdown [192]

#### 1.1.2 Growing Design Complexity and Validation Costs

Technology scaling has enabled performance breakthroughs through increasing transistor densities. On the other hand, a system FIT rate is rapidly increasing due to Moore's Law exponential pace: there is a higher probability that at least one of them suffers from faults during their lifetime or during fabrication. Therefore, the cost and complexity to keep current reliability levels for future technology where billions of devices are guaranteed to work during several years with a low failure rate is going to be huge.

However, growing transistor density is also materializing as an increasing processor design complexity, which directly puts a tremendous pressure in the processor validation phases. This growing complexity has fueled the importance of post-Silicon validation and debug phases during the production cycle of a processor [87, 121]. The validation phases currently overpass in cost the design phases. Around 35% of the product cost are spent on them, and it has been reported [148] that microprocessor companies staff their teams with three verification engineers per designer. At the same time, Intel has reported that the number of bugs found in the validation phases is increasing at a 3x to 4x rate for each generation, and this trend is proportional to the number of lines of structural RTL [88, 201]. The growing design complexity and the shrinking timelines for product delivery are aggravating these facts.

Even though post-silicon validation can leverage real silicon speeds to achieve high

coverage for subtle component interactions, it poses problems to error detection and diagnosis.

Sometimes bugs elude the validation phases and end up in the market, potentially causing massive financial and reputation impacts. The number of escaped bugs is increasing at a high pace: as an example, for Core 2 Duo designs researchers have reported a discovery rate that is 3 times larger than that of the Pentium 4 [43]. Under this scenario, the number of bugs debbugged in the validation phases is projected to rapidly increase, as well as the speed in which they are discovered once products hit the market (affecting millions of purchases).

These facts are calling for research advances in novel techniques and tools to improve the post-silicon validation phases, as well as in runtime verification approaches that provide processor lifetime correctness under undiscovered bugs. According to the ITRS [80, 81, 82], "without major breakthroughs, verification will be a non-scalable, show-stopping barrier for further progress in the semiconductor industry".

#### 1.2 Problem Statement

The described challenges brought by the increasing vulnerability of silicon technologies and by the inefficiency of existing post-silicon validation methods, introduce several problems that we address in this thesis. In the following subsections we discuss them, we critically analyze the short-comings of some existing work, and we state the high-level research objectives that this thesis addresses to alleviate these problems.

#### 1.2.1 Lifetime Reliability Mechanisms for Multiple Sources of Failures

Reliability trends show that multiple wear-out and permanent sources of failure are emerging as important contributors to microprocessors failure rates, rendering soft errors not the only reliability concern to be taken care of during product lifetime. At the same time, design complexity is causing an increase in design bugs eluding the post-silicon validation phases and impacting processor lifetime reliability.

As it will be thoroughly analyzed in Chapter 3 (Related Work), most state-of-art error detection solutions are designed for a specific error type, or for a few of them. For pure hardware reexecution-based techniques (Section 3.1), permanent faults cannot be targeted by solutions relying on temporal redundancy [64, 93, 143, 157, 162, 183, 196, 205, 207], whereas design bugs cannot be detected by solutions based on spatial (and design) redundancy [63, 127, 182, 197, 198]. Software-implemented redundant execution approaches (Section 3.4) also fail to detect multiple sources of failures

#### 8 · Chapter 1. Introduction

for the same reasons: they can either detect soft errors [138, 158, 160] or cannot comprehensively detect design bugs [34, 211]. Circuit-level techniques (Section 3.3) are limited to soft error mitigation [61], soft error detection detection [161, 202], or cannot detect permanent fault or design bugs in a cost-effective manner [47, 203]. On the other hand, built-in self-test circuits [2] cannot detect soft errors. Traditional error coding techniques like parity, ECC or CRC (Section 3.2), can detect soft and hard errors but just target data protection [70, 90, 210] and not combinational logic (an important contributor to processors failure rates).

Therefore, one major goal of this thesis is to:

• Explore and evaluate novel on-line mechanisms for comprehensively detecting multiple sources of failures in modern microprocessor cores during their lifetime (including transient, intermittent, permanent faults and design bugs). We look for unified mechanisms that can deal with all these sources of failure at the same time.

#### 1.2.2 Overheads of Error Detection Solutions

The radical increase in raw error rates will pervade and threaten all commodity market segments. These segments impose challenging requirements to fault tolerance mechanisms that existing ones do not offer. Most of the error detection mechanism were devised for high-end segments where extreme reliability levels were targeted, in spite of severely weighing down global performance. However, reliability is not a primary design goal in commodity systems and some amount of fault coverage can be traded-off as long as processor performance, power and area are not severely impacted by runtime error detection solutions.

As it is described in Chapter 3, state-of-art error detection solutions are generally not suitable from a performance, power or area perspective when dealing with multiple sources of failures. Reexecution-based techniques covering soft and hard errors [63, 127, 198] suffer extreme power and power performance overheads because they redo at every microarchitectural block all the state and internal activity that constitute a computation. Reexecution-based techniques exploiting loose synchronization [182] or ineffectual instruction removal [197] to minimize performance slowdowns, still incur high power overheads and sacrifice a hardware thread context from another core to execute redundant computations. Advanced solutions exploiting both spatial redundancy and design heterogeneity [10] protect against soft errors, hard errors and design bugs. However, their power overheads and area costs are not affordable.

Software-implemented redundant execution approaches targeting soft and hard errors [34, 211] suffer from the same performance and power problems, even though

they require minimal area overheads. Compiler support has also been exploited by hybrid software-hardware solutions to avoid re-execution and to compute the expected microarchitectural activity to be observed during an error-free execution [131, 171, 219]. However, these techniques can only detect failures for the fetch and decode logic, and require extending the processor instruction set. Finally, error coding techniques implemented as self-checking circuits [12, 17, 136, 152] can detect soft errors, hard errors and design bugs with tolerable power and area overheads while causing no slowdown, though they are designed to detect errors in data and functional units.

Globally, existing solutions based on re-execution cannot strategically protect selected critical blocks or functionalities in a cost-effective and targeted way: they are global all-or-nothing approaches. Furthermore, these solutions do not offer flexibility to processor designers who may prefer modulating error coverage and power, performance and area overheads.

Hence, this thesis also aims at:

- Satisfying the needs for efficient reliability solutions with minimal costs in performance, power and area, while at the same time reaching similar reliability levels of traditional defect tolerance techniques.

- Exploring alternatives to reexecution-based techniques that can provide a more flexible trade-off between coverage and overheads, and that are also designed to be more modular for targeting specific blocks or functionalities.

#### 1.2.3 Tackling Observability and Reproducibility During Post-Silicon Validation

The increasing design complexity and transistor integration is posing critical problems to error detection, localization and diagnosis during the post-silicon validation phases.

Processor are like black boxes where observing internal state or activity is extremely difficult. Common techniques like scan chains [2], hold-scan flip-flops [94] and cycle breakpoints [18] allow high-speed state inspection at a given execution moment. However, these techniques are prone-to error and require long iterative non-automated trial-and-error processes to hunt down the moment when the fault is exercised (as their use is extremely dependent on the experience of validators). Modern solutions based on on-chip embedded trace buffers [1, 103, 220] can continuously sample the internal state for a given time period, by storing traced data into dedicated memory. They are however limited by the limited capacity of on-chip storage buffers and the pin I/O bandwidth to extract them. On-chip trace buffering have fixed and limited capacity: these solutions fail at capturing the internal activity for common scenarios where errors manifest thousands of cycles after faults are exercised. In case

of a failure, the log may have been overflown with traces without information about the real cause. Furthermore, on-chip trace buffers [1, 103] require important area overheads. Hardware features added for post-silicon validation purposes are costly and useless to the user once a product goes into production. Therefore, companies normally rely on scan-based techniques to increase the internal observability.

A big problem found during post-silicon validation are non-reproducible errors, which are important contributors to the high cost of current post-silicon approaches [84]. Existing tracing solutions aggravate the reproducibility problem: when attempting to reproduce an error, frequent and time-consuming scan chain and external logic analyzer operations can introduce interferences and non-determinism into the normal program timing, potentially hiding the error. Independently of the interference caused by current state acquisition methods, many bugs are non-reproducible in nature because of the unique conditions that are needed for them to manifest (such as temperature, voltage fluctuations, etc).

To enhance the post-silicon validation phases, in this thesis we also:

- Pursue advancements in system observability through microarchitectural logging technologies that can enable bigger and more flexible buffering capacities, while at the same time have a very low area impact (hardware cost).

- Look for new validation approaches that can extend coverage to non-reproducible errors and that minimally interfere with system performance and operation.

#### 1.2.4 System-Level Simulation for Error Discovery and Diagnosis

The limited internal observability is drifting validation towards methodologies based on rooting errors once an architectural state mismatch is found. Post-silicon validation is principally driven by software tests that are run during a massive number of cycles on real silicon samples. These software tests are generated by specific applications [146], whereas RTL processor models are used to compute the expected error-free architectural results. As a consequence, big server farms are needed to keep in pace with the validation flow. The biggest issue of these approaches is that catching errors by means of architectural state mismatches incurs huge detection latencies, which ultimately leads to extremely time consuming and complex debugging processes to narrow down the time interval when the fault is exercised.

Once a reproducible error is discovered, methods to transfer and synchronize the silicon state to the RTL simulator [178] are used as a means to debug it. The objective is to help validators to understand the wrong system behavior, to reason about the error-free behavior and to locate the fault. System-level simulation of RTL models is an inestimable and powerful tool, but it comes at a high price: it is generally 7-8 orders of magnitude slower than actual silicon [16]. Furthermore, when facing design bugs, RTL system-level simulation cannot help much because the bug may probably be present in the models. In addition, debugging the location and root cause behinds errors is a complex and manual step that requires a deep understanding of the microarchitecture.

These facts indicate several research objectives. In this thesis we also aim to:

- Explore alternatives to error discovery methods that rely on golden state generation and slow architectural-state mismatch sighting.

- Enrich the debugging practices with new methods to automatize the error localization and error diagnosis steps. We specially want to minimize the dependence on costly system-level failure simulations. Given the increasing design complexity, we also want to provide tools to help rooting the cause of errors (wrong system behavior and the expected error-free one).

#### 1.3 Thesis Approach

This thesis explores several approaches to address the mentioned research objectives.

We embrace a paradigm shift where error detection is built based on dynamically checking microarchitectural invariants, rather than relying on performance-oppressive redundant execution, or limited fine-grain circuit-level approaches.

Our solutions are end-to-end in nature: instead of individually checking low-level microarchitectural blocks, end-to-end approaches allow verifying high-level functionalities whose implementation is scattered across many components, in a uniform and implementation-independent manner. An end-to-end scheme involves generating a protection code at a source point, and checking for errors only at the end of the path, where information is ultimately consumed.

This thesis approaches the problem by first decomposing the functionalities of a modern processor into high-level tasks that can be verifiable in a cost-effective manner and that when combined together can ensure the correctness of almost the whole core. Specifically, we propose three new approaches to detect errors during runtime, which encompass the following high-level functionalities of modern out-of-order cores: computation-register dataflow, control flow recovery and memory dataflow. This thesis proposes error detection mechanisms for these functionalities because of several reasons. First, the involved blocks are difficult to protect in a cost-effective manner. Second, these functionalities represent around 78.35% of the area of the baseline pro-

#### 12 · Chapter 1. Introduction

cessor described in Chapter 4 (excluding protected structures like caches, TLBs, and queues). And third, according to our previous studies [205], it contributes to around 94% of the SDC SER FIT <sup>4</sup> (excluding protected structures, too).

Then, this thesis addresses the problems of current validation methodologies. We begin by adding value to our error detection mechanisms by extending their applicability to the post-silicon validation phases. Since our error detection methods can catch design bugs (and transient, permanent and intermittent), we minimize the need for slow system-level simulation to perform bug discovery. We also advocate that new transparent continuous logging techniques combined with flexible on-chip buffer capacities allows debugging non-reproducible errors and reduces the dependence on costly external tools.

#### 1.4 Thesis Contributions

The main contributions of this dissertation span two different areas: targeted lightweight runtime error detection and cost-effective post-silicon fault localization and diagnosis.

The key results related to run-time fault detection are as follows:

1. Register dataflow logic runtime validation is first deeply studied. We propose a novel runtime technique to detect errors in the register dataflow logic. The solution introduces a novel concept called signature checking that detects errors by attaching a token to each produced register value and by matching consumed signatures against source signatures. We show through fault injection campaigns that the rename tables, wake-up logic, select logic, bypass control, operand read and write-back, register free list, register release, register allocation, and the load replay logic are protected with high coverage. The approach is shown to be very effective in detecting faults, and allows designers to choose the coverage ratio by amplifying the signature size.

We also propose nine different signature allocation policies with different area and power requirements. We show that in-flight signature distribution can be controlled to increase coverage for different register dataflow failure scenarios.

2. We introduce a new microarchitecture that combines register dataflow checking and register value checking. We particularly show how to improve our register dataflow checking technique by integrating it with an end-to-end residue checking scheme. Our evaluations show that a significant amount of power and area

<sup>&</sup>lt;sup>4</sup>Silent Data Corruption failure rate caused by soft errors, as described in Chapter 2.

- can be amortized by combining both solutions, while at the same time protection is extended to the functional units, load-store queue data and addresses, bypass values and register file values.

- 3. Efficient control flow logic runtime validation is then studied. Even though a myriad of targeted solutions exist to detect faults in the instruction sequencing (fetch, decode and allocate logic), none of them can check the complex logic involved in implementing efficient control flow recovery. We propose two techniques to validate the rename state recovery and the squashing functionalities of high-performance out-of-order cores. The proposal uses end-to-end rename state signature checking and tracking of squashed regions to detect faults in the ROB, the rename state recovery logic, the checkpoint rename tables, and in the instruction squashing mechanism. Our evaluations demonstrate the effectiveness of our approach: very high failure reduction rates are achieved with minor power and area overheads.

- 4. Finally, we target the runtime validation of the memory dataflow logic implemented by the load-store queue. Our proposed solution (MOVT), relies on a tiny cache-like structure that keeps the last producer id's for tracked addresses. At commit time, loads are checked to have obtained the data from the youngest older producing store. We have shown that by exploiting the fact that most forwarding store-load pairs are close to each other, coverage can be increased for small set-associative MOVTs by conservatively flushing the pipeline and restarting execution under some scenarios. Three different implementations of the technique with different trade-offs are proposed and evaluated. The solution presents very high fault coverage with attractive area and performance overheads. Moreover, MOVT can be used to solve the vulnerability hole inherent to redundant multi-threading designs where the load-store queue activity is not replicated across threads.

The key results related to cost-effective fault localization and automated diagnosis are the following:

5. Existing tracing solutions are constrained by the capacity and area of on-chip logs. A new software-hardware logging system to increase the internal observability is proposed to alleviate these issues. First, we show that by sequestering physical memory pages from the application being run and re-purposing them to store activity logs we can increase observability by means of logs that can be sized to suite validation needs and without requiring big hardware structures. We then propose a hardware structure that temporally buffers internal activity

### 14 · Chapter 1. Introduction

at full speed and connects with the data cache to access the log pages. We study its efficiency and show that by offloading the buffer during idle cache cycles and by letting the application allocate lines as needed, performance is not critically impacted.

- 6. We show how to combine our error detection mechanisms together with the described logging system to construct a novel post-silicon validation methodology. As a practical example, we particularly focus on the memory dataflow logic implemented by the load-store queue. By using our runtime bug-detection mechanisms together with the proposed non-intrusive logging system, we eliminate the simulation steps required to generate golden outputs for test programs and we extend coverage to non-reproducible errors without any intervention to orchestrate the activity logging.

- 7. Current debugging practices are manual and cumbersome. We present a diagnosis algorithm that analyzes the log produced by our validation system and automatically localizes and diagnoses errors in the load-store queue. Not only the fault location is determined, but also the wrong behavior and the failure-free expected one. We evaluate its efficiency and show that a very high percentage of errors can be automatically diagnosed for different precision levels.

# 1.5 Thesis Organization

The rest of this thesis is organized as follows:

Chapter 2 presents basic background information and the basic concepts necessary for proper understanding of this document. Chapter 3 contains a survey and a critical analysis of related work in the area of fault tolerance and post-silicon validation. Chapter 4 describes the evaluation framework. This chapter details the processor performance simulator, the benchmarks, and the area/power/delay/error coverage models that have been used in this thesis. We also describe the baseline error detection mechanisms that our processor model incorporates.

We distribute the main contributions of this thesis in the next four chapters:

- In Chapter 5 we present a runtime solution to detect errors in the register dataflow logic, register data values and computation. Several implementations with different coverage, area and power trade-offs are also studied.

- In Chapter 6 we detail two runtime solutions to detect errors in the control flow recovery logic of modern out-of-order processors. The first one implements an

end-to-end validation of the rename state recovery, whereas the second one is an end-to-end solution for validating the instruction squashing.

- In Chapter 7 we describe a proposal that targets the runtime validation of the memory dataflow logic implemented by the load-store queue. We present three different implementations, with varying degrees of error detection coverage, performance costs and design complexity.

- In Chapter 8 we detail a novel hardware-software solution to discover, locate and diagnose errors during post-silicon validation. To show the potential of our approach, we focus on how to apply it to the memory dataflow logic implemented by the load-store queue.

Finally, Chapter 9 draws the main conclusions of this dissertation and points out some ideas for future work. The microarchitecture description of our baseline processor is found in Appendix A.

# CHAPTER 2

# **BACKGROUND**

The scope of this Chapter is to present some basic concepts that are relevant to the general topic of this thesis. In Section 2.1 we describe the economic impact of hardware vulnerability in computing systems. Section 2.2 defines some basic concepts related to faults, errors and metrics. Hardware failure mechanisms are categorized in Section 2.3. Some relevant fault tolerance fields are introduced in Section 2.4. We finally include in Section 2.5 an overview of the different processor validation phases.

# 2.1 Economic Costs of Hardware Reliability

Technology reliability problems are already making an impact in the industry across all sectors that rely on information systems. Despite being a sensitive problem for microprocessor companies, several reliability issues have been notoriously public.

Sun Microsystems was one of the first affected companies affected by technology scaling issues. In 2000 it was reported that their UltraSparc II servers were crashing at an alarming rate. After arduous works to understand the reason behind this behavior and significant dissatisfaction from their clients, Sun found that the problem was caused by bit flips in their insufficiently protected cache memories [3, 14]. In 2004, Cyprus reported an incident where soft errors brought down an automotive factory every month [129]. In 2005, HP revealed that a CPU farm in Los Alamos National Laboratory crashed frequently due to particle striking several cache tag arrays [117].

Other examples of reliability hazards related to design bugs have also hit the microprocessor industry. In 1994 it was discovered that the Intel Pentium microprocessor made occasional errors in floating point divisions [150]. Intel ended up offering to replace all flawed Pentium processors, and despite a small fraction of consumers

# 18 · Chapter 2. Background

requested a replacement, a cost of 475 million dollars was incurred. In 1997, it was found a bug affecting the 6x86 Cyrix microprocessors series. The bug allowed to build unprivileged programs that would halt the system in an infinite loop. Fortunately, a workaround at the OS level allowed avoiding the recall of all products [218]. In 2007, a flaw was discovered in the TLB of several AMD Phenom processors series that could cause a system lock-up in rare circumstances. Initial BIOS and software workarounds disabled the buggy TLB, incurring in performance degradations of 10%-15% on average. The bug put a temporary stop to the production and severely harmed AMD reputation [180].

Regarding degradation errors, Intel announced in 2011 a problem in the 3Gbps SATA ports of its Cougar Point chipset familily. The problem was located in a faulty and leaky transistor that caused the degradation of the IO link over time. Despite Intel performed stress burn-in tests before releasing the product, the problem was detected by OEMs. Intel halted the shipment of affected products, recalled the faulty ones and incurred an estimated cost of 700 million dollars [95].