# **Solid-state Memory on Flexible Silicon for Future Electronic Applications**

Dissertation by

Mohamed Tarek Ghoneim

In Partial Fulfillment of the Requirements

For the Degree of

Doctor of Philosophy

King Abdullah University of Science and Technology

Thuwal, Kingdom of Saudi Arabia

November, 2016

### **EXAMINATION COMMITTEE PAGE**

The dissertation of Mohamed Tarek Ghoneim is approved by the examination committee.

Committee Chairperson: Muhammad Mustafa Hussain- Associate Professor

Committee Members: Aurelien Manchon - Associate Professor, Jasmeen Merzaban - Assistant Professor, David Clarke - Extended Tarr Family Professor (Harvard)

# COPYRIGHT PAGE

© November 2016

Mohamed Tarek Ghoneim

All Rights Reserved

#### **ABSTRACT**

Solid-state Memory on Flexible Silicon for Future Electronic Applications

### Mohamed Tarek Ghoneim

Advancements in electronics research triggered a vision of a more connected world, touching new unprecedented fields to improve the quality of our lives. This vision has been fueled by electronic giants showcasing flexible displays for the first time in consumer electronics symposiums. Since then, the scientific and research communities partook on exploring possibilities for making flexible electronics. Decades of research have revealed many routes to flexible electronics, lots of opportunities and challenges. In this work, we focus on our contributions towards realizing a complimentary approach to flexible inorganic high performance electronic memories on silicon. This approach provides a straight forward method for capitalizing on the existing well-established semiconductor infrastructure, standard processes and procedures, and collective knowledge. Ultimately, we focus on understanding the reliability and functionality anomalies in flexible electronics and flexible solid state memory built using the flexible silicon platform. The results of the presented studies show that: (i) flexible devices fabricated using etch-protect-release approach (with trenches included in the active area) exhibit ~19% lower safe operating voltage compared to their bulk counterparts, (ii) they can withstand prolonged bending duration (static stress) but are prone to failure under dynamic stress as in repeated bending and re-flattening, (iii) flexible 3D FinFETs exhibit ~10% variation in key properties when exposed to out-of-plane bending stress and out-ofplane stress does not resemble the well-studied in-plane stress used in strain engineering,

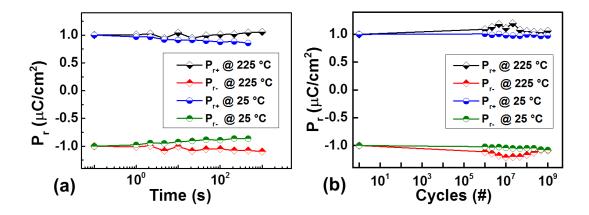

(iv) resistive memories can be achieved on flexible silicon and their basic resistive property is preserved but other memory functionalities (retention, endurance, speed, memory window) requires further investigations, (v) flexible silicon based PZT ferroelectric capacitors exhibit record polarization, capacitance, and endurance (1 billion write-erase cycles) values for flexible FeRAMs, uncompromised retention ability under varying dynamic stress, and a minimum bending radius of 5 mm, and (vi) the combined effect of 225 °C, 260 MPa tensile stress, 55% humidity under ambient conditions (21% oxygen), led to 48% reduction in switching coercive fields, 45% reduction in remnant polarization, an expected increase of 22% in relative permittivity and normalized capacitance, and reduced memory window (20% difference between switching and non-switching currents at 225 °C).

#### **ACKNOWLEDGEMENTS**

I thank and express my deep appreciation to Prof. Muhammad Hussain for his active mentorship, sincere advice, guidance and supervision throughout the past five years (MSc. and PhD). I have learnt a lot from him on both technical and personal grounds. I also thank Prof. Talal Al-Attar, Prof. Mohab Anis, and Prof. Slim Alouini for all the support and encouragement, Prof. Tso-Ping Ma for the opportunity to spend the last few months of my PhD with his group at Yale University, and Prof. Aurelien Manchon, Prof. Jasmeen Merzaban, and Prof. David Clarke for dedicating the time and energy to review my work and active participation in the evaluation committee. I am deeply indebted to Teta Kareema, Amal Ghoneim, Uncle Khaled Ghoneim, Aunt Labiba Ghozlan, Waleed Mohsin, Noha Hashish, and Mohamed Hashish for the much needed support welcoming Mariam in Saudi Arabia. I express my gratitude to all friends and colleagues in our group for the wonderful camaraderie, especially, Dr. Jhonathan Rojas for teaching me how to build my first flexible silicon devices, Aftab Hussain for all the wonderful scientific/non-scientific/philosophical discussions, tea breaks, family activities, amazing friendship, and the short lived Friday games, and KAUST Nanofab staff for their much appreciated help and cooperation. I also thank Dr. Mohammed Zidan and Dr. Mohammed Alnassar for their extra-ordinary help with my memory work, Dr. Gennadi Bersuker and Prof. Chadwin Young for the help and advice on the reliability work, and Prof. Muhammad Ashraful Alam for the teaching advice and insightful discussion on the heat dissipation paper.

Last and definitely not least, I am grateful and deeply indebted to my wife Asmaa Hashish, for whom words cannot even come close to accurately express my feelings, for going above and beyond duty and making KAUST feel like a real home, and little Mariam for the joy and happiness she brought to the family at large. I am forever grateful to my parents, Azza Ghozlan and Tarek Ghoneim, Aunt Labiba Ghozlan and Uncle Mohamed Ghoneim for their unconditional love and support throughout, before, during, and after my PhD journey. All thanks and praise to God for providing the strength to move forward and all the blessings we enjoy and should forever be thankful and express our sincere gratitude.

# TABLE OF CONTENTS

| EXAMINATION COMMITTEE PAGE2                                                    |

|--------------------------------------------------------------------------------|

| COPYRIGHT PAGE                                                                 |

| ABSTRACT4                                                                      |

| ACKNOWLEDGEMENTS6                                                              |

| TABLE OF CONTENTS                                                              |

| LIST OF ABBREVIATIONS                                                          |

| LIST OF FIGURES                                                                |

| LIST OF TABLES                                                                 |

| Chapter 1 Introduction and Review on Physically Flexible Nonvolatile Memory 17 |

| 1.1. NVM Operating Principles                                                  |

| 1.2. NVM Architectures 24                                                      |

| 1.3. Literature Review                                                         |

| 1.3.1. All Organic Systems                                                     |

| 1.3.2. Hybrid Systems                                                          |

| 1.3.3. Flexible Silicon Systems                                                |

| 1.4. References                                                                |

| Chapter 2 Reliability of Flexible High-k/Metal Gate Devices                    |

| 2.1. Device Fabrication                                                        |

| 2.2.    | Electrical Characterization                                              |

|---------|--------------------------------------------------------------------------|

| 2.3.    | Electrical Reliability Analysis                                          |

| 2.4.    | Mechanical Reliability Analysis                                          |

| 2.5.    | Conclusion                                                               |

| 2.6.    | References                                                               |

| Chapter | 3 Performance Analysis of High Performance Flexible Non-planar 3D FinFET |

| CMOS.   | 80                                                                       |

| 3.1.    | Device Fabrication and Characterization                                  |

| 3.2.    | Silicon's Bending Ability and Limitations                                |

| 3.3.    | Effect of Bending Axis Orientation, Stress Type, Carrier Type on FinFET  |

| Perfo   | rmance85                                                                 |

| 3.4.    | Residual Stress vs. Effective Stress                                     |

| 3.5.    | Conclusion                                                               |

| 3.6.    | References102                                                            |

| Chapter | 4 Flexible Memristor                                                     |

| 4.1.    | Device Fabrication                                                       |

| 4.2.    | Device Characterization                                                  |

| 4.3.    | Conclusion                                                               |

| 4.4.    | References                                                               |

| Chapter | 5 Flexible FeRAM 115                                                     |

| 5.1.    | Device Fabrication                                                       |

| 5.2.    | Device Characterization    | 120 |

|---------|----------------------------|-----|

| 5.3.    | Harsh Environment Analysis | 136 |

| 5.4.    | Conclusion                 | 147 |

| 5.5.    | References                 | 148 |

| Chapter | 6 Conclusion               | 156 |

| 6.1.    | Status Quo                 | 156 |

| 6.2.    | Future Directions          | 158 |

| 6.3.    | References                 | 162 |

#### LIST OF ABBREVIATIONS

IoTInternet of ThingsIoEInternet of EverythingSSSubthreshold SwingNVMNonvolatile MemoryRAMRandom Access Memory

ReRAM Resistive Memory

FeRAM Ferroelectric Memory

PCRAM Phase Change Memory

MRAM Magnetic Memory

AFM Atomic Force Microscopy

NEM Nanoelectromechnical

RIE Reactive Ion Etching

DRIE Deep Reactive Ion Etching

FET Field Effect Transistor

SONOS Silicon-Oxide-Nitride-Oxide-Silicon

TANOS Tantalum Nitride-Alumina-Nitride-Oxide-Silicon

1T One Transistor

1T1R One Transistor-One Resistor

1T1C One Transistor-One Capacitor

2T2C Two Transistors-Two Capacitors

SOI Silicon on Insulator SSD Solid State Drive

ULSI Ultra Large Scale Integration

CNTs Carbon Nanotubes

ZnO Zinc Oxide

GI-XRD Grazing Incidence X-Ray Diffraction

OLED Organic Light Emitting Diode CES Consumer Electronics Show

M2M Machine to Machine

PP-SSS Privacy Protection Solid State Storage

PVDF-TrFE Poly[vinylidenefluoride-co-trifluoroethylene]

FOX Field Oxide

ITRS International Technology Roadmap for Semiconductors

CMOS Complementary Metal-Oxide-Semiconductor

MOSCAP Metal-Oxide-Semiconductor Capacitor

Vramp Ramping Voltage

TDDB Time Dependent Dielectric Breakdown

DIBL Drain Induced Barrier Lowering

ILD Interlayer Dielectric

Dit Interfacial Defects Density

BOX Buffered Oxide

CVS Constant Voltage Stress

PZT Lead Zirconium Titanate

FG Floating Gate

CT Charge Trap QDs Quantum Dots

# LIST OF FIGURES

| Figure 1.2.1: Architectures of NVM                                                                       |

|----------------------------------------------------------------------------------------------------------|

| Figure 1.3.1: Chart highlighting the focus of the review.                                                |

| Figure 1.3.1.1: a) Schematic representation of the devices and molecular structure of the                |

| organic semiconductor QQT(CN)4 and the ferroelectric PVDF-TrFE. Reprinted by                             |

| permission from Macmillan Publishers Ltd: Nature Communications [35], copyright                          |

| (2014), b) schematic of an all-inkjet-printed inverter using two p -type OTFTs (top) and                 |

| diagrams of the PS brush treatment procedure on the PVP gate dielectric and Ag S/D                       |

| electrodes (bottom). Reprinted with permission from [43]. Copyright © 2013 WILEY-                        |

| VCH Verlag GmbH & Co                                                                                     |

| Figure 1.3.2.1: a) Schematic illustrations of three basic modes for transfer printing.                   |

| Reprinted with permission from [45]. Copyright © 2012 WILEY-VCH Verlag GmbH &                            |

| Co., b) schematic diagram of the fabrication procedures for the freestanding OFETs using                 |

| modified water-floatation method. Reprinted with permission from [52]. Copyright ©                       |

| 2013 WILEY-VCH Verlag GmbH & Co., c) schematic illustrations of the process for                          |

| fabricating flexible crossbar-structured memory on a plastic substrate via the laser lift-off            |

| transfer method. Reprinted with permission from [54]. Copyright © 2014 WILEY-VCH                         |

| Verlag GmbH & Co., d) schematic illustration of the cells in the conducting-interlayer                   |

| SiOx memory device sputtered at room temperature. Reprinted with permission from                         |

| [55]. Copyright © 2014 WILEY-VCH Verlag GmbH & Co                                                        |

| Figure 1.3.2.2: Schematic illustration of the controlled spalling process used for removing              |

| the prefabricated devices and circuits from the rigid silicon handle wafer. The inset                    |

| schematically shows the device architecture for the ultra-thin body transistors with raised              |

| source/drain regions. Reprinted with permission from [59]. Copyright (2012) American                     |

| Chemical Society                                                                                         |

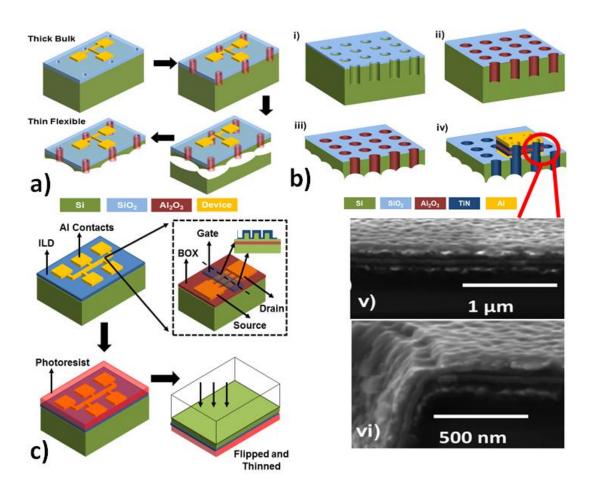

| Figure 1.3.3.1: a) Device first approach illustration where the devices are fabricated in a              |

| traditional fashion, then, protected using photoresist (PR). The PR is then patterned and                |

| the pattern is transferred to the field oxide (FOX) layer then to the Si substrate. Using the            |

| spacer technique, a highly conformal atomic layer deposition (ALD) spacer is deposited                   |

| for sidewalls. Finally, the dies are put in a reactive chamber containing XeF2 gas for                   |

| isotropic Si when the etching regions merge, the top flexible portion of Si (100)                        |

| containing the devices can be safely released, b) device last approach illustration where                |

| flexible silicon fabric is first released then devices are built. Adapted with permission                |

| from [129]. Copyright $\ensuremath{\mathbb{G}}$ 2014 WILEY-VCH Verlag GmbH & Co., c) illustration of the |

| soft-etch back approach where the traditional dies containing devices are covered with                   |

| PR for protection, then, the die is flipped upside down and etched using DRIE to the                     |

| desired thickness. Adapted with permission from [67]. Copyright (2014) American                          |

| Chemical Society                                                                                         |

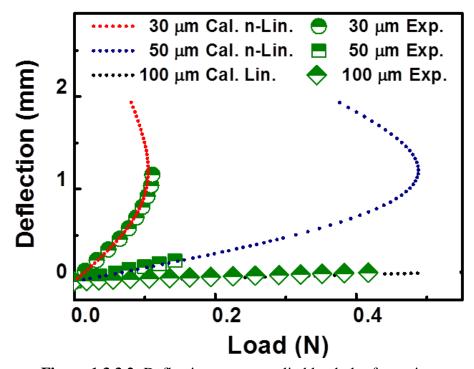

| Figure 1.3.3.2: Deflection versus applied load plot for various thicknesses of flexible                  |

| substrates, dotted lines showing non-linear analytical solution for 30 and 40 $\mu m$ thick              |

| substrates and linear analytical solution for 100 µm thick substrates. Adapted courtesy of      |

|-------------------------------------------------------------------------------------------------|

| Prof. YongAn Huang, Huazhong University of Science and Technology, China                        |

| Figure 2.1.1: Main fabrication steps of MOSCAPs on flexible silicon                             |

| Figure 2.1.2: Digital photo of the actual fabricated MOSCAPs on flexible ultra-thin Si          |

| fabric. 59                                                                                      |

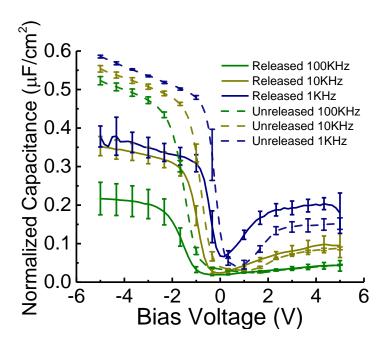

| Figure 2.2.1: Normalized C-V curves for flexible and inflexible MOSCAPs at different            |

| frequencies                                                                                     |

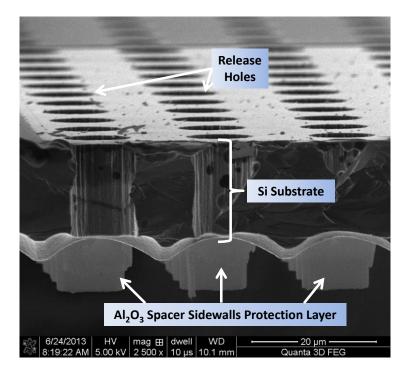

| Figure 2.2.2: The scanning electron microscope image of the thin silicon fabric showing         |

| the scallops at the bottom of the structures, which might be caused by the release              |

| processing step                                                                                 |

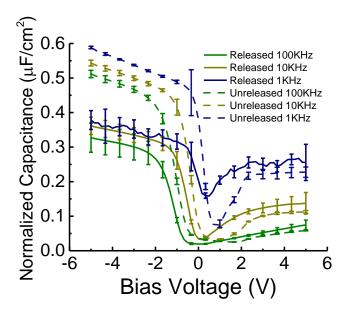

| Figure 2.2.3: Normalized C-V curves for flexible and inflexible devices corrected for           |

| series resistance                                                                               |

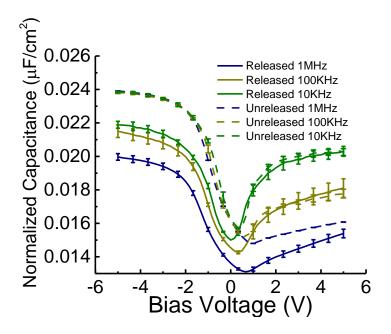

| Figure 2.2.4: Normalized C-V curves for flexible and inflexible dummy MOSCAPs at                |

| different frequencies. 65                                                                       |

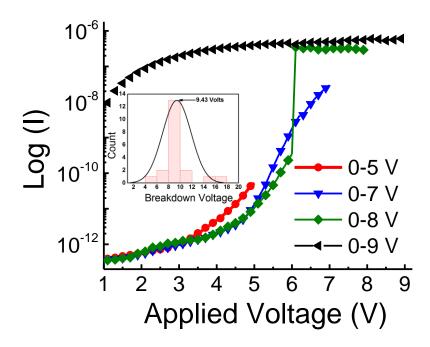

| Figure 2.3.1: The current-voltage dependencies for the subsequent applied vramp                 |

| measurements with a $1V$ increment. Inset: the histogram of $V_{bd}$ values obtained on tested  |

| devices                                                                                         |

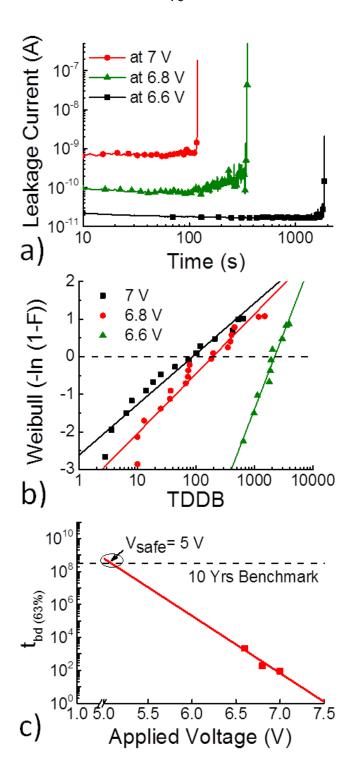

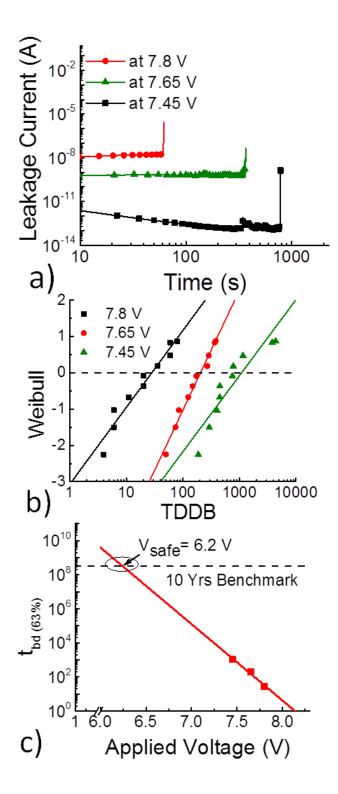

| Figure 2.3.2: a) Sample constant stress voltages (CVS) measurements performed on                |

| flexible devices, b) corresponding Weibull distributions, and c) lifetime projection plot.      |

|                                                                                                 |

| Figure 2.3.3: a) Constant stress voltages (CVS) measurements on unreleased inflexible           |

| devices, b) corresponding Weibull distributions, and C) lifetime projections plot 71            |

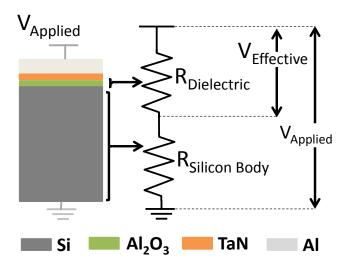

| Figure 2.3.4: Modelling of back gated MOSCAPs in terms of series resistances                    |

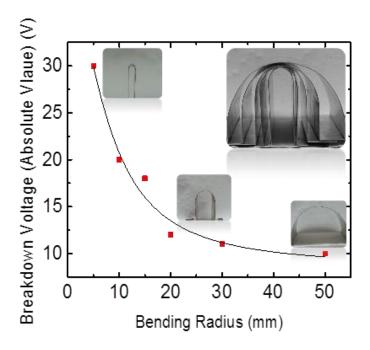

| Figure 2.4.1: Change of average breakdown voltage of MOSCAPs versus bending radius.             |

| 75                                                                                              |

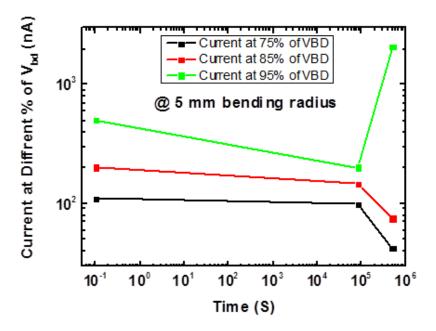

| Figure 2.4.2: Leakage current versus time corresponding to different values of constant         |

| stress voltages. 76                                                                             |

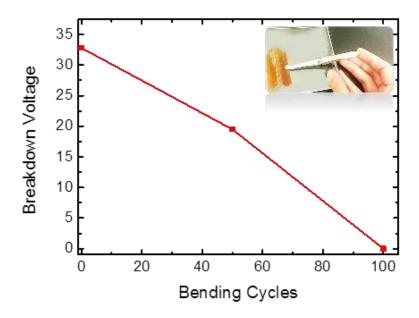

| Figure 2.4.3: Breakdown voltage as a function of bending cycles. Inset: the samples are         |

| extended using the Kapton tape from both edges to enable manual bending of the sample           |

| at the center of the bending structure.                                                         |

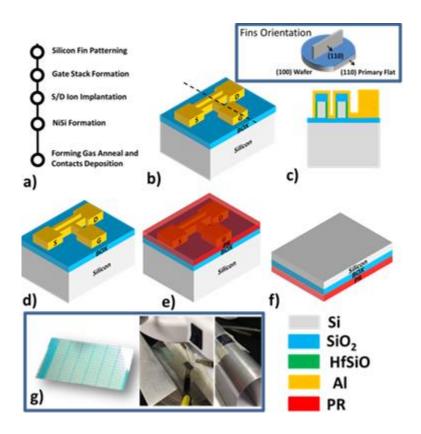

| Figure 3.1.1: Fabrication flow (a-f) and characterization setup (g) of flexible FinFET 82       |

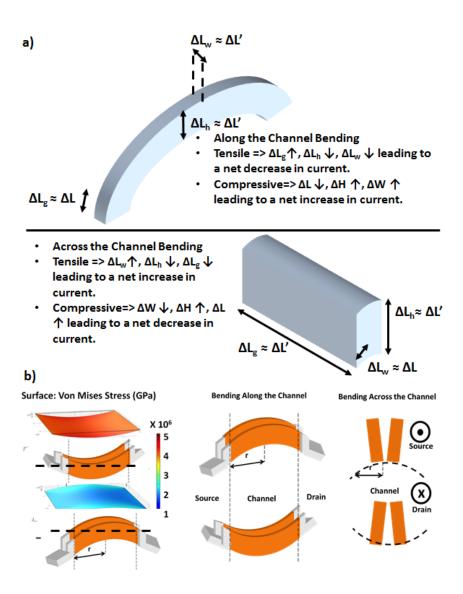

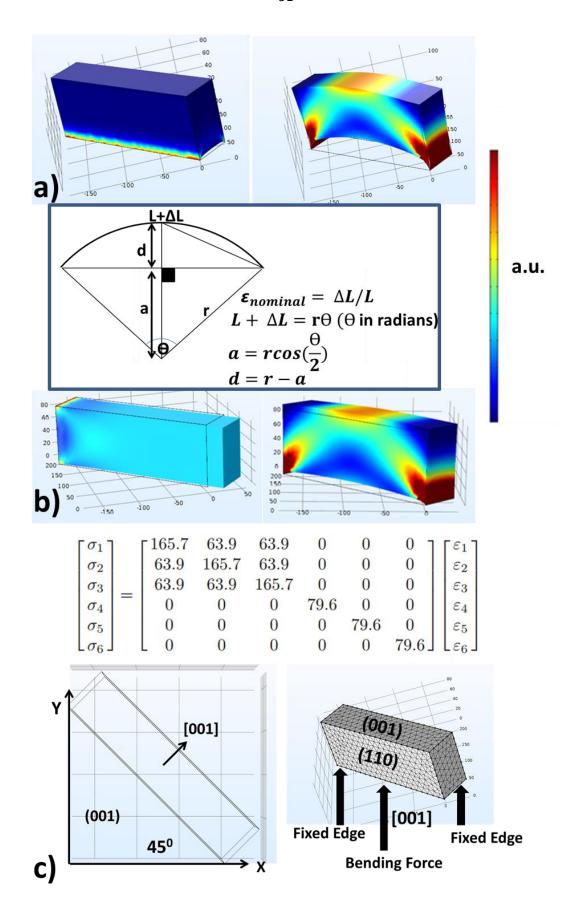

| Figure 3.3.1: Illustrations on changes in fin dimensions (a), and FEM simulations for Von       |

| Mises stress distribution (b).                                                                  |

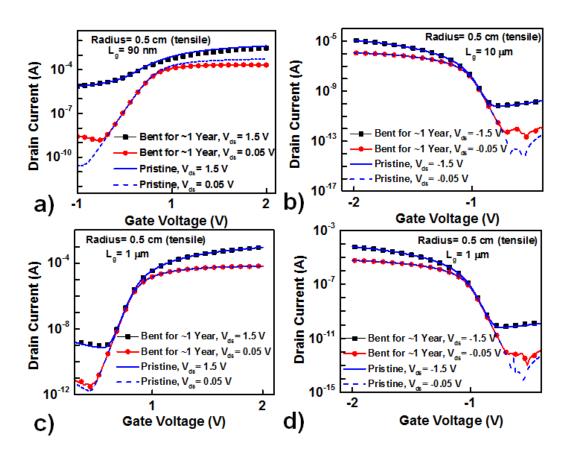

| Figure 3.3.2: Transfer (a-d) and output (e-f) plots of FinFETs of various dimensions            |

| under varied stress conditions and bending axes                                                 |

| Figure 3.3.3: FEM stress profile for along and across the channel bending (a) and in-           |

| plane/out-of- plane stress (b)                                                                  |

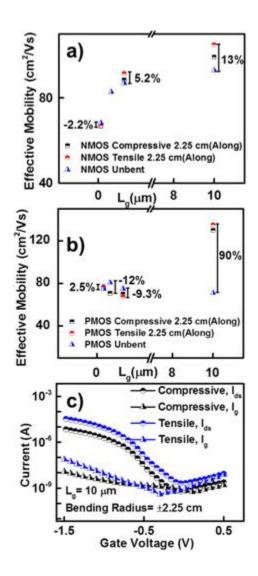

| Figure 3.3.4: Mobility vs. gate length (a-b) and functional device with 90% mobility change (c) |

| Unange (C)94                                                                                    |

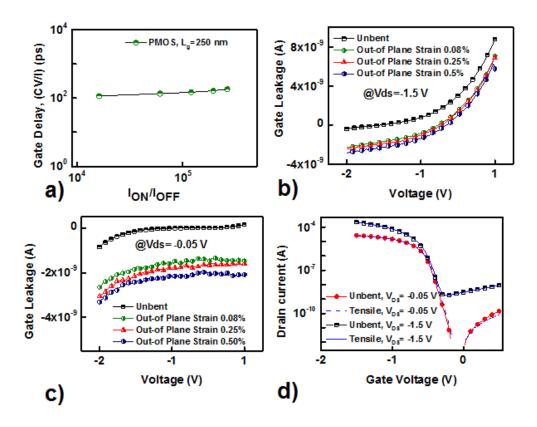

| Figure 3.3.5: Gate delay (a) and leakage trends (b-c) for a 250 nm p-type FinFET with the transfer plot shown in (d)                                                                                                                                                                                                                                                                                        |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Figure 3.3.6: Transfer plots for short and long channel FinFETs bent for 12 months at 0.5                                                                                                                                                                                                                                                                                                                   |

| cm bending radius (a-d).                                                                                                                                                                                                                                                                                                                                                                                    |

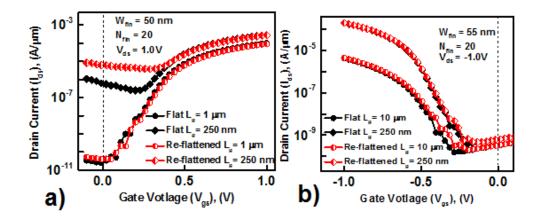

| Figure 3.4.1: Transfer plots for re-flattened n-type (a) and p-type (b) FinFETs 101                                                                                                                                                                                                                                                                                                                         |

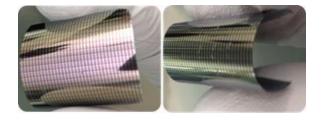

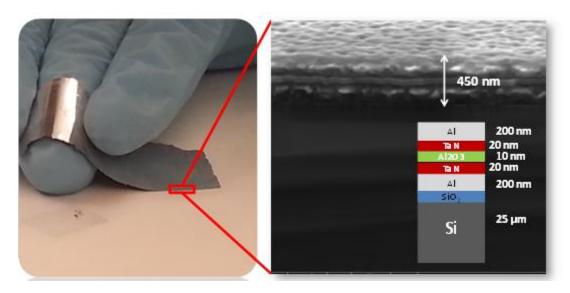

| Figure 4.1.1: Peeling off a thin flexible Si fabric from bulk Si (100); a) thermal oxidation to grow 300 nm SiO <sub>2</sub> on Si, b) patterning and etching deep trenches in SiO <sub>2</sub> and Si bulk (~25 um deep) followed by a spacer formation step to protect trenches sidewalls (not shown), c) peeling thin Si (100) sheet using XeF <sub>2</sub> isotropic etch at the bottom of the trenches |

| Acetone (b)                                                                                                                                                                                                                                                                                                                                                                                                 |

| Figure 4.1.3: Digital image of actual fabricated memristors on flexible Si fabric (25 μm thick)(left). It is to be noted there is no support platform to hold or to handle the released silicon fabric. Scanning electron microscope image of device and platform stack (right)                                                                                                                             |

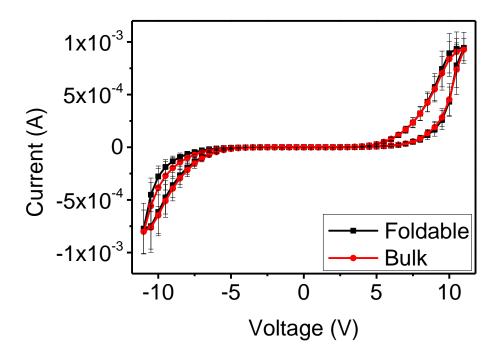

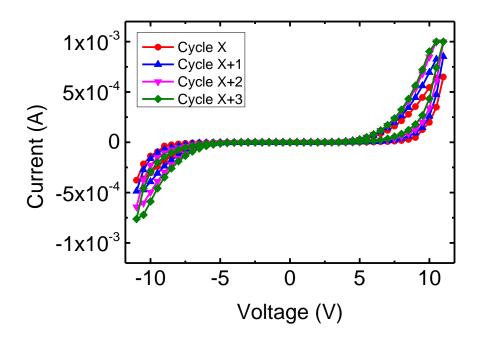

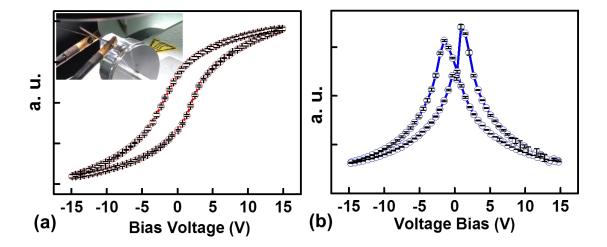

| Figure 4.2.1: Basic IV hysteresis properties of foldable vs. bulk memristors                                                                                                                                                                                                                                                                                                                                |

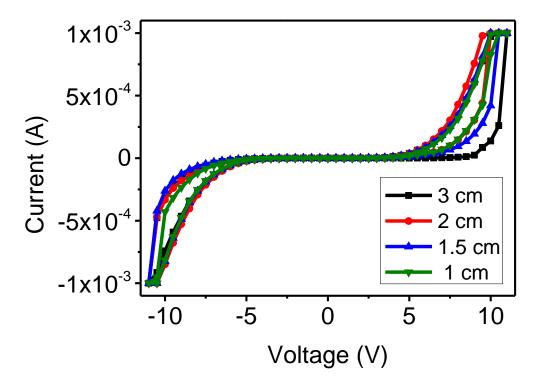

| Figure 4.2.2: IV hysteresis loops for memristive devices at different bending radii 111                                                                                                                                                                                                                                                                                                                     |

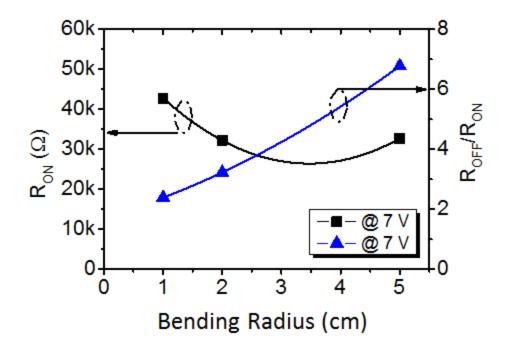

| Figure 4.2.3: Variation of $R_{ON}$ (left) and $R_{OFF}/R_{ON}$ ratio (right) as a function of bending radius                                                                                                                                                                                                                                                                                               |

| Figure 4.2.4: Overlapping cycles for a representative device                                                                                                                                                                                                                                                                                                                                                |

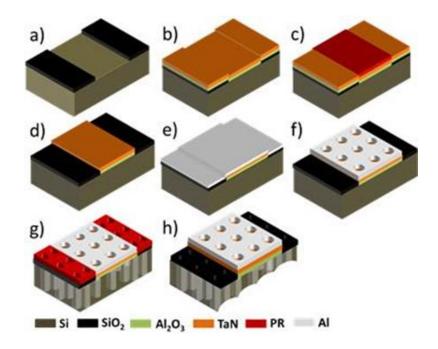

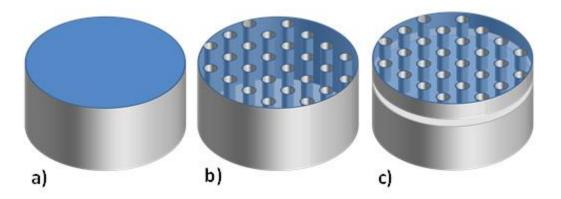

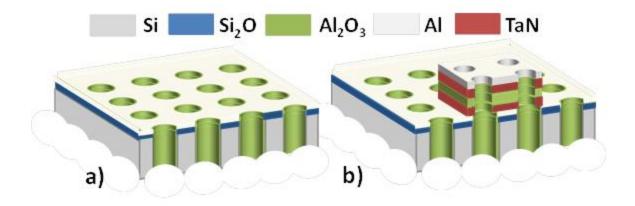

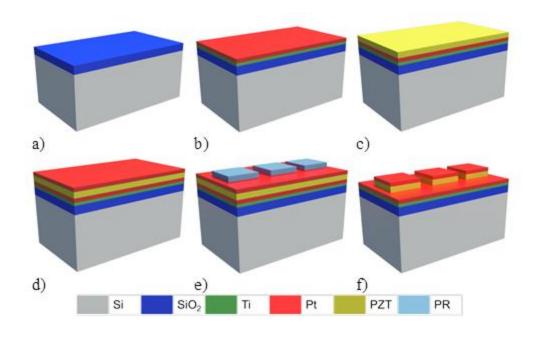

| Figure 5.1.1 Fabrication process flow of bulk FeRAM                                                                                                                                                                                                                                                                                                                                                         |

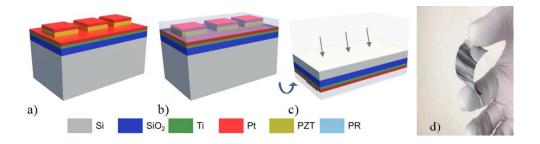

| Figure 5.1.2: Fabrication process flow for flexing the silicon substrate. (a-c): silicon                                                                                                                                                                                                                                                                                                                    |

| substrate with pre-fabricated FeRAM devices undergoes soft etch back process (upside                                                                                                                                                                                                                                                                                                                        |

| down) to thin down the substrate to achieve an ultra-thin version of flexible silicon with pre-fabricated devices (d)                                                                                                                                                                                                                                                                                       |

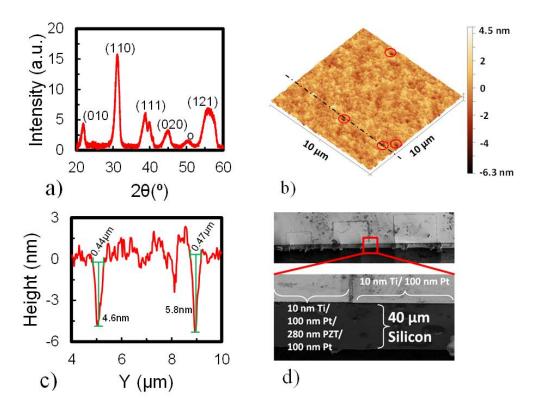

| Figure 5.2.1: a) Grazing incidence X-ray diffraction (GI-XRD) of as deposited PZT thin                                                                                                                                                                                                                                                                                                                      |

| film, b) atomic force microscopy (AFM) measurement, c) height profile of the dotted line                                                                                                                                                                                                                                                                                                                    |

| in part (b), and d) scanning electron microscope (SEM) cross-section image depicting the                                                                                                                                                                                                                                                                                                                    |

| thickness of the final fabric                                                                                                                                                                                                                                                                                                                                                                               |

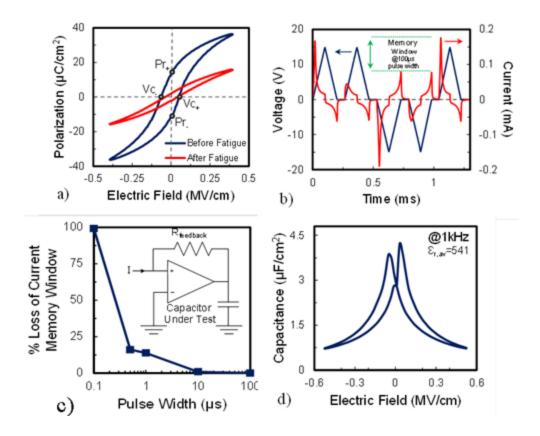

| Figure 5.2.2: Representative plots for various ferroelectric memory properties; a) Basic                                                                                                                                                                                                                                                                                                                    |

| polarization-electric field plot, b) current-voltage plot vs. time for memory window                                                                                                                                                                                                                                                                                                                        |

| extraction, c) percentage loss of current memory window versus pulse width, inser-                                                                                                                                                                                                                                                                                                                          |

| showing the schematic of the virtual ground feedback method used for eliminating                                                                                                                                                                                                                                                                                                                            |

| connection parasitics from actual device measurements, d) capacitance-electric field plot     |

|-----------------------------------------------------------------------------------------------|

| of ferroelectric memory                                                                       |

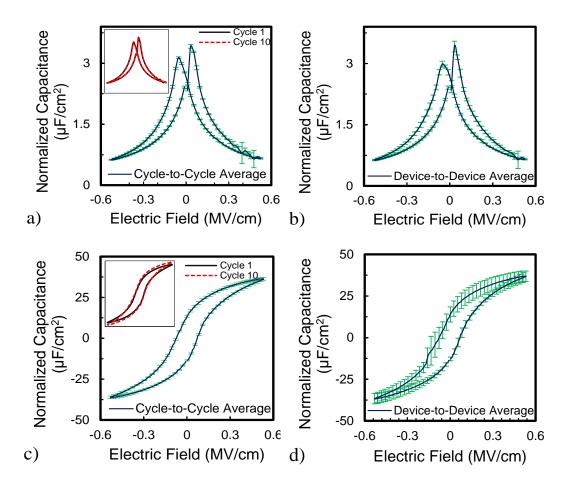

| Figure 5.2.3: a) Cycle-to-cycle capacitance variation of ferroelectric memory, inset          |

| showing 1st and 10th cycles, b) device-to-device capacitance variation for 10 devices, c)     |

| cycle-to-cycle polarization variation, inset showing first and tenth cycles, d) device-to-    |

| device polarization variation for 10 devices                                                  |

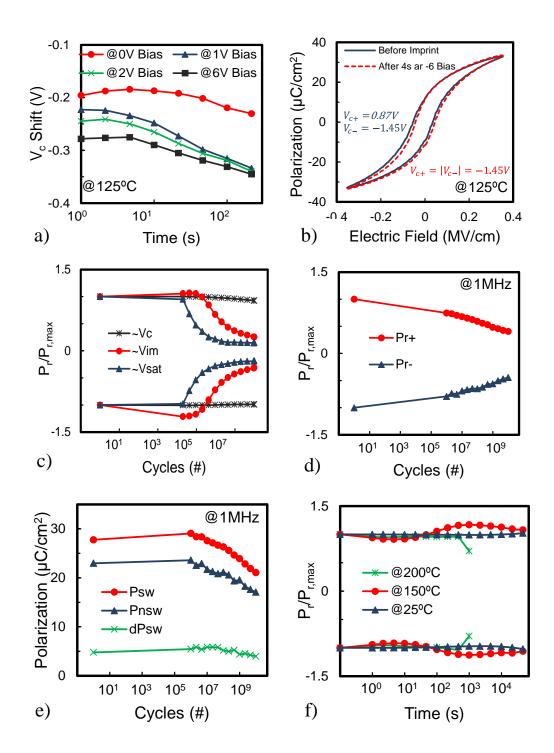

| Figure 5.2.4: a) Fatigue test for ferroelectric capacitors at different disturbance signal's  |

| amplitudes, b) fatigue test results at 1 MHz, c) non-volatile charges stability assessment    |

| as a function of switching cycles, d) retention measuremet at various temperatures, e)        |

| imprint test of ferroelectric capacitors at different bias voltages at 125°C, and f) restored |

| symmetric behavior after applying a constant bias voltage to counteract the imprint           |

| effect                                                                                        |

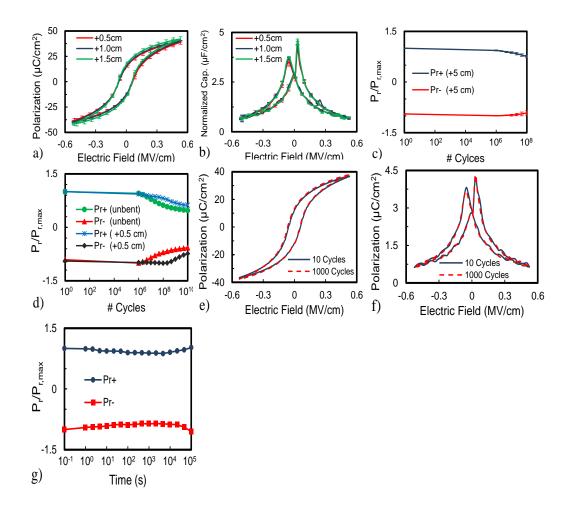

| Figure 5.2.5: a) Polarization, b) capacitance, and c) fatigue behavior variation at different |

| bending radii (lines represent averages of 7 devices with error bars representing standard    |

| deviation), d) fatigue enhancement at minimum bending radius, e) basic hysteresis plot        |

| for polarization versus applied voltage after 1000 bending cycles at minimum radius (5        |

| mm), f) capacitance-voltage plot after 1000 bending cycles at minimum radius, and g)          |

| representative retention polarization plot of a device after 1300 bending cycles at           |

| minimum bending radius                                                                        |

| Figure 5.3.1: Cycle-to-cycle variation in polarization of the memory devices (a), inset       |

| showing the physical set-up utilizing a 2.5 cm diameter metallic stub, and capacitance (b)    |

| behavior of flexible ferroelectric PZT memory capacitors                                      |

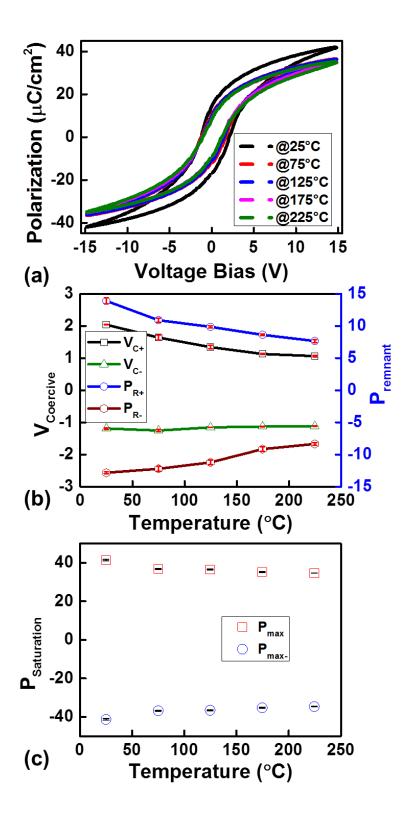

| Figure 5.3.2: Polarization hysteresis plots vs. voltage bias (a), change in coercive voltage  |

| and remnant polarization (b), and decrease in saturation polarization (c) at wide range of    |

| temperatures                                                                                  |

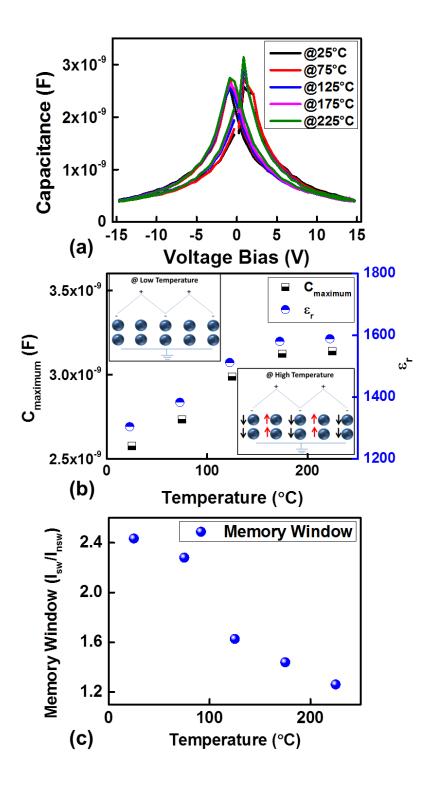

| Figure 5.3.3: Capacitance-voltage plot (a), maximum capacitance and relative                  |

| permittivity (b), and memory window plotted as a function of temperature (c) 144              |

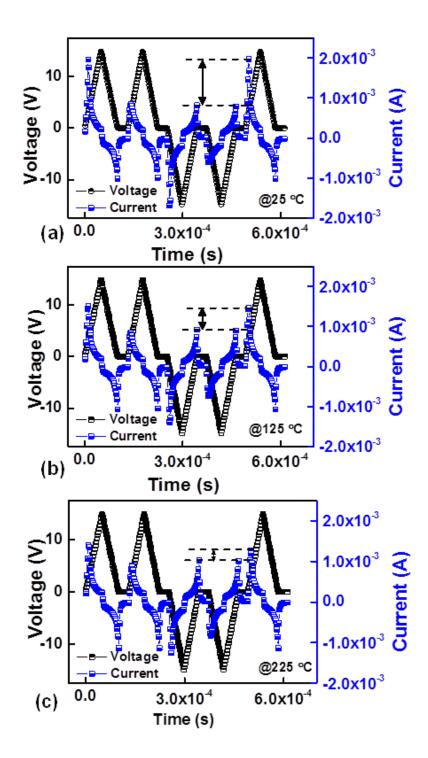

| Figure 5.3.4: Memory window calculations from voltage-current vs. time plots at               |

| different temperatures (a-c)                                                                  |

| Figure 5.3.5: Retention (a) and fatigue (b) tests of flexible bent ferroelectric PZT memory   |

| at room temperature and 225 $^{\circ}$ C.                                                     |

# LIST OF TABLES

| Table 1.1.1: Operation Principles of Common NVM                                   | 20       |

|-----------------------------------------------------------------------------------|----------|

| Table 2.2.1: Series resistance values for released and bulk devices at different  | t small  |

| signal excitation frequencies                                                     | 63       |

| Table 3.3.1: Key switching properties of FinFETs under out-of-plane stress        | 88       |

| Table 5.2.1: Summary of research progress in flexible ferroelectric memory device | es over  |

| the past few years                                                                | 134      |

| Table 5.3.1: Percentage change in ferroelectric properties of PZT memory under    | er harsh |

| conditions                                                                        | 146      |

### **Chapter 1** Introduction and Review on Physically Flexible Nonvolatile Memory

Solid-state memory is an essential component of the digital age. With advancements in healthcare technology and the Internet of Things (IoT), the demand for ultra-dense, ultra-low-power memory is increasing. In this chapter, we present a comprehensive perspective on the most notable approaches to the fabrication of physically flexible memory devices. With the future goal of replacing traditional mechanical hard disks with solid-state storage devices, a fully flexible electronic system will need two basic devices: transistors and nonvolatile memory. Transistors are used for logic operations and gating memory arrays, while nonvolatile memory (NVM) devices are required for storing information in the main memory and cache storage. Since the highest density of transistors and storage structures is manifested in memories, the focus of this chapter is flexible NVM. Flexible NVM components are discussed in terms of their functionality, performance metrics, and reliability aspects, all of which are critical components for NVM technology to be part of mainstream consumer electronics, IoT, and advanced healthcare devices.

This Chapter briefly outlines the operating principles, common nonvolatile memory architectures of different NVM cells and technologies, and a literature review of the flexible NVM research area and highlights the most common approaches for making flexible NVM. The material presented is published as:

• Ghoneim, M.T.; Hussain, M.M. Review on Physically Flexible Nonvolatile Memory for Internet of Everything Electronics. *Electronics* **2015**, 4, 424-479.

Chapter 2 and 3 demonstrate the reliability studies of flexible high-κ/metal gate devices, including flexible MOSCAPs and flexible FinFETs on silicon. These chapters represent our contribution in showing the first key element in NVM cells which is the select/access transistor. We first study the electrical and mechanical reliability aspects of a flexible version of a simple metal-oxide-semiconductor structure then move forward to undertake the performance analysis of high performance flexible non-planar 3D FinFET CMOS. These two chapters are published as:

- Ghoneim, M.T.; Rojas, J.P.; Young, C.D.; Bersuker, G.; Hussain, M.M. Electrical Analysis of High Dielectric Constant Insulator and Metal Gate Metal Oxide Semiconductor Capacitors on Flexible Bulk Mono-Crystalline Silicon. *IEEE Trans. Rel.* 2015, 64, 579-585.

- Ghoneim, M.T.; Kutbee, A.; Nasseri, F.G.; Bersuker, G.; Hussain, M.M. Mechanical anomaly impact on metal-oxide-semiconductor capacitors on flexible silicon fabric. *Appl. Phys. Lett.* 2014, 104, 234104.

- Ghoneim, M.T.; Alfaraj, N.; Torres-Sevilla, G.A.; Fahad, H.M.; Hussain, M.M. Outof-Plane Strain Effects on Physically Flexible FinFET CMOS. *IEEE Trans. Electron Devices*, 2016, 1-8.

- Torres-Sevilla, G.A.;\* Ghoneim, M.T.;\* Fahad, H.;\* Rojas, J.P.; Hussain, A.M.;

Hussain, M.M. Flexible nanoscale high-performance FinFETs. ACS Nano 2014, 8,

9850-9856. [\* Equal Contributions]

Chapters 4 and 5 represent the second main component of NVM which is the storage elements. Chapter 4 demonstrates a flexible resistive memory device (memristor—storage element in ReRAM) on flexible silicon and chapter 5 demonstrates

flexible ferroelectric capacitors (storage element in FeRAM) on silicon. The presented work in these two chapters has been published as:

- Ghoneim, M.T.; Zidan, M.A.; Salama, K.N.; Hussain, M.M. Towards neuromorphic electronics: Memristors on foldable silicon fabric. *Microelectron*. *J.* 2014, 45, 1392-1395.

- Ghoneim, M.T.; Zidan, M.A.; Alnassar, M.Y.; Hanna, A.N.; Kosel, J.; Salama, K.N.; Hussain, M.M. Thin PZT-Based Ferroelectric Capacitors on Flexible Silicon for Nonvolatile Memory Applications. *Adv. Electron. Mater.* 2015, 1, 1500045.

- Ghoneim, M.T.; Hussain, M.M., 2015. Study of harsh environment operation of flexible ferroelectric memory integrated with PZT and silicon fabric. *Appl. Phys. Lett.* 2015, 107, 052904.

Finally, chapter 6 provides useful insights based on the learnt lessons from our research pursuits and outlines future directions towards achieving fully flexible NVM modules and systems for IoT and wearable electronic applications.

### 1.1. NVM Operating Principles

Similar to how we define the human brain's ability to memorize as the ability to remember useful information over long- and short-term durations, electronic memories have the ability to retain stored information over various durations. An electronic memory that is able to retain information over short periods of time (milliseconds) is identified as a volatile memory. In this case, when the power goes off, information stored in the volatile memory is lost. On the contrary, an electronic memory that is able to store information over long periods of time (~10 years is the industry standard) is called a

nonvolatile memory (NVM). NVMs can retain information even when no power is supplied. There are five major classes of NVMs [1]: resistive random access memory (ReRAM) also referred to as memristor [2-5], ferroelectric RAM (FeRAM), [6] magnetic RAM (MRAM) [7, 8], phase change RAM (PCRAM) [9, 10], and flash memory (floating gate (FG) and charge trapping (CT)) [11, 12, 13]. Other technologies, such as nanoelectromechanical (NEM) NVMs [14, 15] and molecular based NVMs [16] exist but they are not mainstream. Table 1.1.1 summarizes the principles of operation of the leading NVM technologies and indicates which technologies have already been demonstrated in a flexible form. Note that the terms 'floating gate' and 'charge-trapping flash' are used interchangeably in recent literature. In Table 1.1.1, the distinguishing property is whether the charge-trapping layer is a conductor or an insulator, although both conducting and insulating layers (with or without embedded NPs and QDs) trap charges; nanoparticles (NP) embedded in an insulator for charge trapping are also considered FG-Flash.

**Table 1.1.1: Operation Principles of Common NVM**

| NVM Type                           | Operation Principle                                                                                                                                                                                                                       | Flexed |

|------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|

| ReRAM (Memristor)  Conductive Path | A resistive oxide is sandwiched between two metallic layers. The resistance of the oxide changes with applied "set" and "reset" voltage pulses. A high-resistance state corresponds to "0" and a low-resistance state corresponds to "1." | Yes    |

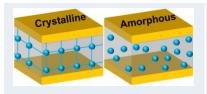

# A ferroelectric material has two possible **FeRAM** polarization states inherent from its crystalline structure. Applying write/erase E<sub>external</sub> Yes voltage pulse switches for positive to negative polarization states, corresponding to "0" or "1." Spintronic devices such as magnetic tunneling junctions are composed of a fixed ("pinned") magnetic moment layer, a tunneling barrier (oxide), and a free layer. Current flowing in nearby lines is expected **MRAM** to magnetize the free layer. If the free layer Free Magnetic Laver magnetic moment is parallel to that of the No pinned layer, the device is "ON" and the Pinned Magnetic Layer resistance across the structure is low. If the free layer is magnetized such that its magnetic moment is anti-parallel to the pinned layer, the device is "OFF" and the structure will be in high-resistance state. Current or laser pulses are applied to change Yes **PCRAM** the phase of a material from crystalline (low

resistance) to amorphous (high resistance) and vice versa at a localized space, which changes the material's electrical and optical properties. Short pulses above the melting temperature are needed to make the change from the crystalline to the amorphous phase, while longer pulses below the melting temperature are required to restore the crystalline order of the material.

Flash

FG flash has the same structure as a field effect transistor (FET) except that its gate dielectric is split into three layers. The first is tunneling oxide, the second is an embedded conductor layer (i.e., doped polysilicon or embedded quantum dots (QDs) or metallic nanoparticles (NPs)) floating gate, and the third is a blocking oxide. When a programming voltage is applied, carriers tunnel from the channel to the floating gate. This results in a shift of the threshold

Yes

|                  | CT                                                                                                                                                                                                                                                                                                 | voltage of the transistor corresponding to "1." A reverse bias is applied during the erase operation to move the charges back into the channel.  The charge trap flash replaces the floating gate with a conductor layer that has an insulting layer (i.e., silicon nitride). The most common structures are the SONOS (Polysilicon-oxide- nitride-oxide-silicon) and the TANOS (titanium-alumina-nitride-oxide- silicon). | Yes |

|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| NEM-NVM  Current | A nano-electromechanical switch is fabricated such that (i) upon applying a programming electrical signal, its pull-in voltage shifts when operated at a designed switching voltage or (ii) it has a free moving cantilever that has bistable physical states affecting its electrical properties. |                                                                                                                                                                                                                                                                                                                                                                                                                            | No  |

A bistable molecule can be switched from a low-conductance state ("0") to a high-conductance state "1" by applying brief bias voltage pulses to switch the state through oxidation and translation of the molecular structure between the two stable states.

No

#### 1.2. NVM Architectures

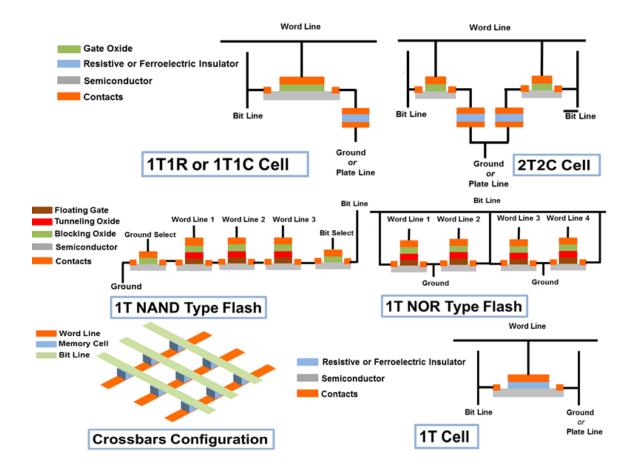

NVM architectures are an important element in memory design that can be classified into three main categories: the 1T, where the memory cell is composed of a single transistor ('T' stands for transistor); the 1T1C or 1T1R, where the memory cell is composed of an access/select transistor and a nonvolatile storage structure ('C' stands for capacitor and 'R' stands for resistor); and the 2T2C (two transistors and two capacitors per memory bit) [1, 17, 18]. Other variations of these main architectures [17, 19] and different arrangements, such as the 1T2C, have also been reported [20-22]. Furthermore, there are differences in the way memory cells are connected to each other. For instance, NOR-type flash and NAND-type flash memories both have a 1T architecture but different cell connections [23]. Also, there is the crossbars configuration in which each memory cell is connected to four neighboring cells [6]. Figure 1.2.1 shows the schematic arrangements of the three main architectures, NOR and NAND flash arrangements, and the crossbars configuration.

Figure 1.2.1: Architectures of NVM

### 1.3. Literature Review

Recent advancements in flexible electronics research will enable novel applications ranging from stylish flexible gadgets for real-time monitoring of health-related vital signs to novel biological applications such as electronic skin [23-33]. Critical advances have been made in recent years that rely on organic materials as active elements because of their inherent flexibility. Mainstream approaches to capitalize on naturally flexible substrates like polymers can be categorized into (i) all-organic systems, where both devices (specifically active materials) and substrates are made up of organic materials [34-40] or inkjet- and screen-printed in thin layers onto paper and organic

substrates [41-44] and (ii) hybrid systems, where inorganic electronic devices are transferred onto an organic substrate using transfer printing and other transfer techniques [45-53], laser lift-off transfer [54], and low-temperature direct deposition of inorganic devices on plastic organic substrates [55-58]. Other approaches use silicon-on-insulator (SOI) substrates, and controlled spalling technology to peel-off thin semiconductor layers [59-61]. In addition, a complementary transfer-free approach has recently been introduced, where thinning down the inorganic substrate through traditional, standard fabrication processes improves the flexibility of the substrate [62-67].

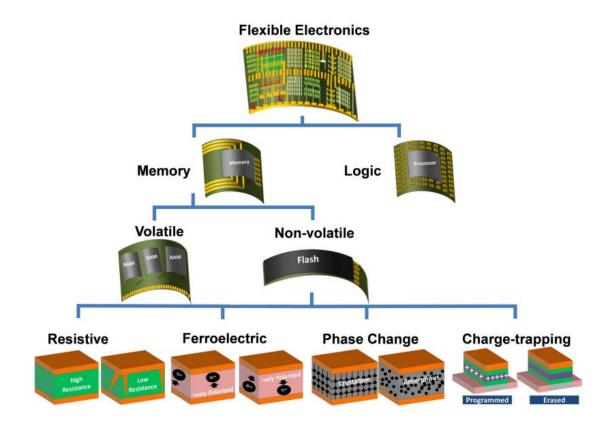

These approaches are all geared towards achieving fully flexible electronic systems. The three main components in any electronic system are (1) processing units, (2) the main memory, and (3) storage. Processing units perform logic operations through transistor logic, while the main memory performs temporary short-term storage (cache) with a quick access feature, also known as primary storage or random access memory (RAM), through access transistors and capacitors that store charges. Storage refers to the long-term retention of information, traditionally implemented using hard disks. However, at present, a shift towards other NVM types in a solid-state drive (SSD) format for supporting faster performance and higher integration densities within strict area constraints is taking place. Hence, the main electronic devices required to build an electronic system are transistors, capacitors, and NVM devices. Emerging NVM such as resistive random access memory (ReRAM), flash memory, phase change RAM (PCRAM), and ferroelectric random access memories (FeRAMs) have the benefits of fast switching, low-operation voltage, and ultra-large-scale-integration (ULSI) densities. These attractive qualities not only make them a favorable option for replacing magnetic hard disks but also for replacing quick access, volatile, and dynamic RAM. This means that future electronic systems will require combinations of only two essential devices: transistors and NVM devices.

An objective assessment of the discussed mainstream and complementary approaches to flexible electronics must focus on their ability to provide high-performance, reliable NVM devices with ULSI density transistors. In this section, we present the mainstream NVM architectures and technologies with a special focus on most up-to-date techniques for producing flexible NVM devices.

Every memory cell consists of a gating device for access/select that is usually implemented using a transistor. Hence, memory arrays are where the largest number of transistors exist in an electronic system, a consequence of their ULSI density and low cost/bit (\$/bit). Furthermore, with the continuous reduction in \$/bit of NVMs and the higher switching speeds between memory states ('0' to '1' or vice versa) of emerging NVM technologies, replacing volatile random access memory and magnetic hard disks with faster SSDs made up of transistors and NVM structures becomes feasible. Here, the progress made over the past few years in three prominent types of flexible NVM technologies is discussed: (i) resistive, (ii) ferroelectric, (iii) phase change, and (iv) charge-trapping NVMs. In addition, the reliability aspects of the devices reported are discussed and an assessment for emerging technologies that provides useful insights towards their potential for commercialization is also provided. Figure 1.3.1 briefly positions the focus of this review in context of flexible electronics research.

Figure 1.3.1: Chart highlighting the focus of the review.

As of today variety of materials have been used to build NVM devices. For example, NMVs based on; (i) embedded 0-dimensional gold nanoparticles (NPs) [68-72], black phosphorous quantum dots (QDs) [73], and silicon QDs [74], (ii) 1-dimensional zinc oxide (ZnO) nanowires [75], silicon (Si) nanowires [76], and carbon nanotubes (CNTs) [77-79], and (iii) 2-dimensional graphene [80-82], graphene oxide [83-89], molybdenum disulfide (MoS<sub>2</sub>) [90, 91], zinc oxide (ZnO) [75], and hydrated tungsten trioxide (WO<sub>3</sub>.H<sub>2</sub>O) nano-sheet [51] have already been reported.

Although, these and other similar reports have focused on discrete memory devices or cells, academic researchers and semiconductor industries have reported macroelectronics (large area electronics) focusing on mainly artificial skin [92-94] and display technology where memory has not been an integrated built-in module. Sony

reported a rollable organic light emitting diode (OLED) based display in 2010 [95]. Samsung in the consumer electronics show (CES) 2011 and, later, LG and Nokia demonstrated a flexible display prototype [96]. However, the futuristic vision of the IoT where everything is connected, communicating, and making real-time decisions with artificial intelligence, with the associated emerging markets of big data analysis and machine-to-machine (M2M) technologies, would require more than flexible displays. The steep increase in the number of sensors from few millions in 2007 to billions of devices in 2013 is expected to persist, reaching the trillion sensor devices mark by 2023 due to the impact of IoT [97]. These sensors will be integrated in smart cards and RFIDs, vehicular technologies, buildings, infrastructures, healthcare, smart energy, factories, and supply chain management [97-99], as well as on humans for improving regular day to day experience [100]. To achieve such functionalities and fulfill the futuristic vision, IoT devices will require: (i) increased intra-node processing for real-time decision making, (ii) robustness to environmental variations (reliability), (iii) ultra-low power operation, (iv) ultra-high density integrated NVM and (v) smart antennas for wireless communications [101-105]. In addition, IoT devices should be physically flexible to enable wider adaptation in wearable forms and conforming to curvilinear structures in various forms.

To this end, integrated device manufacturers (IDMs) have already demonstrated devices designed to meet the IoT requirements. In 2014, Aitken et al. identified the 65 nm CMOS technology as the most suitable IoT chip process based on wafer cost and die area analysis [106]. In 2015, Yamamoto et al. demonstrated a novel gate stack in 65 nm CMOS technology for ultra-low leakage devices [102], Ueki et al. from Renesas

Electronics Corporation developed a low power 2 Mb ReRAM macro in 90 nm CMOS technology [107], Whatmough et al. implemented a 0.6 volts transceiver in 65 nm CMOS technology [108], and Yamauchi et al. developed an embedded flash memory in vehicle control systems for IoT applications [99]. Furthermore, Hitachi researchers have studied how to profit from IoT for 10 years and used big data analysis to introduce the wearable happiness meter to unravel the link between physical motion and happiness [100]. Tanakamaru et al. introduced privacy protection solid state storage (PP-SSS) for what they called, "the right to be forgotten," where data is physically and automatically broken hardware-wise to co-op with anticipated security and privacy issues in the IoT era [109]. These are all great milestones in providing useful insights of what the future holds with the IoT revolution.

Based on the existing progress and current status, it is evident that while IoT devices are required to attain physical flexibility, they still have to rely on CMOS technology while pushing for ultra-low power consumption, ultra-low leakage currents, improved reliability, and ultra large scale co-integration of NVMs, CPUs, and antennas. Flexible antennas have been studied for decades and will not be discussed in this section [110-115]. As aforementioned, NVM modules require information storage elements and select access transistors; therefore, a NVM perspective of the flexible electronics arena provides a comprehensive overview of the basic elements needed for implementing all electronic systems, including systems suitable for IoT applications.

### 1.3.1. All Organic Systems

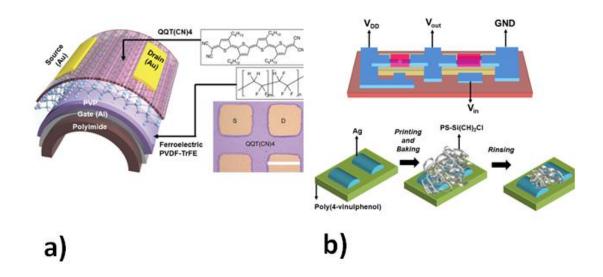

Most organic electronics use a variety of polymeric semiconductors as channel materials, polymeric ferroelectrics for nonvolatile storage, and thick, durable insulating polymers to support the flexible substrate. Figure 1.3.1.1a shows a representative structure for an all-organic deposited NVM that uses a quinoidal oligothiophene derivative (QQT(CN)<sub>4</sub>) as the organic channel material and a polyvinilidene-cotrifluoroethylene (PVDF-TrFE) as the ferroelectric material; Figure 1.3.1.1b shows an inkjet-printed organic inverter on a plastic substrate. Compared to inorganic silicon electronics, the all-organic approach is more challenging with respect to the performance of organic materials, especially as transistor channel materials. The highest reported mobility for most organic channel materials is more than 20 times lower than silicon [116-119], with the exception of 43 cm<sup>2</sup>/V.s peak hole saturation mobility reported by Yongbo Yuan et al. in 2014 [120]: this translates into lower performance. Furthermore, organic electronics have yet to match the reliability of inorganic electronics nor can they compare in thermal stability [121]. To capitalize on the low-cost benefits of an allorganic system, there is a need to integrate polymeric dielectrics because they typically have low dielectric constants compared to the semiconductor industry's high-κ dielectrics and, in most cases, are even lower than that of SiO<sub>2</sub> [122]. Although it is a challenge to achieve the high capacitance values required for high-performance electronic devices using all-organic materials, there are also benefits from their use such as extremely high flexibility and conformal abilities. Currently, flexible organic electronic research has already gained solid grounds in commercial applications like active-matrix organic lightemitting diode (AMOLED) displays [123]. Therefore, organic electronics show true potential for further expansion and enhanced maturity in macroelectronics.

**Figure 1.3.1.1:** a) Schematic representation of the devices and molecular structure of the organic semiconductor QQT(CN)4 and the ferroelectric PVDF-TrFE. Reprinted by permission from Macmillan Publishers Ltd: Nature Communications [35], copyright (2014), b) schematic of an all-inkjet-printed inverter using two p -type OTFTs (top) and diagrams of the PS brush treatment procedure on the PVP gate dielectric and Ag S/D electrodes (bottom). Reprinted with permission from [43]. Copyright © 2013 WILEY-VCH Verlag GmbH & Co.

### 1.3.2. Hybrid Systems

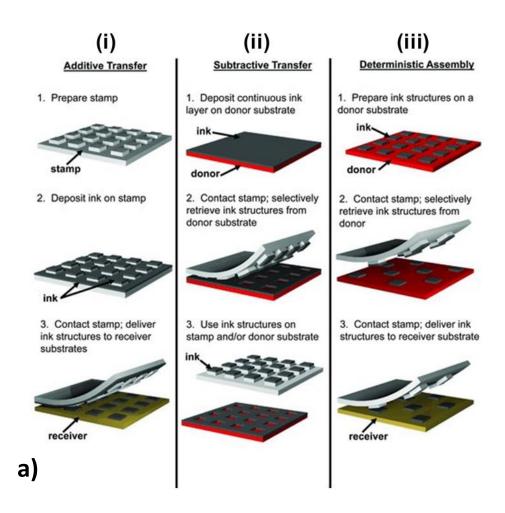

Hybrid systems use both organic and inorganic materials, making them conducive to a wider spectrum of techniques with greater versatility. Figure 1.3.2.1 is an illustrative summary of available flexible hybrid techniques. In transfer printing, a molded polymer is used as a stamp that can be functionalized with desired materials and then printed onto a different substrate. Figure 1.3.2.1aa shows the three modes of transfer printing by John Rogers's group at the University of Illinois at Urbana-Champaign [45]. Figure 1.3.2.1bb shows a representative generic transfer technique, where devices are fabricated on a specific rigid substrate and then transferred to one that is flexible (a banknote in this

case). A specific type of transfer is the laser lift-off by Keon Jae Lee's group at the Korea Advanced Institute of Science and Technology (KAIST), where a laser shot is used to etch a sacrificial layer to release the device for transfer (Figure 1.3.2.1c) [54]. Figure 1.3.2.1d shows a resistive memory structure made up of room-temperature-sputtered and e-beam-evaporated materials on a flexible substrate [55]. The mainstream hybrid transfer approach achieves high performance by transferring high-performance inorganic devices onto an organic substrate for flexibility; however, it adds extra nonconventional transfer steps and suffers low yields. Although this is mitigated by the direct-deposition-on-plastic-substrates approach, using plastic adds temperature restrictions to the fabrication process. As a result, it is a challenge to produce high-quality films such as atomic-layer-deposited high-κ dielectrics that usually require temperatures above 300°C. And finally, because the different solvents used for patterning and photolithography should not affect the flexible organic substrate, there are limitations to suitable plastic material choices.

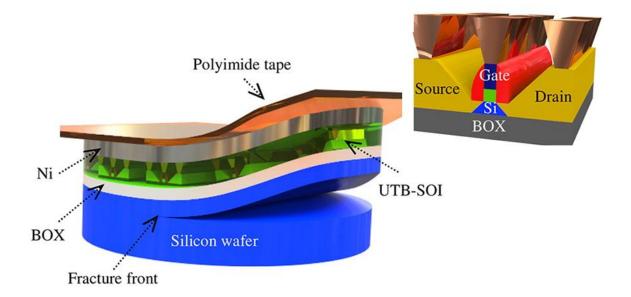

The spalling technique uses stressor layers to initiate fracture-modes in SOI and semiconductor substrates. In 2012, Banarjee *et al.* reported on the exfoliation of thin-film transistors from prefabricated bulk wafers using the spalling technique [124]. In the same year, Shahrejerdi *et al.* reported having performed, at room temperature, controlled spalling of full SOI wafer circuitry and successfully transferred the surface layer to a flexible plastic substrate [59, 125]. The authors deposited a nickel (Ni) stressor layer that abruptly discontinued near one edge of the wafer where a crack in the mono-crystalline silicon (Si) was initiated by an applied force [126, 127]. However, before the force is applied, polyimide tape is added to support the flexible peeled fabric-bearing ultra-thin

body devices (Figure 1.3.2.2). This approach has also been reported for single crystals of germanium (Ge) and gallium arsenide (GaAs) [60, 128]. Another spalling approach was used by Bellanger and Serra where Si (100) foils were peeled off from the bulk substrate [61]. The challenges faced by the spalling technique are two fold: first, extra deposition and complex tuning of a stressor material with a specific thickness followed by etching are required and second, once the crack has been initiated, the peeling-off process requires high dexterity that is not suitable for mass production.

Figure 1.3.2.1: a) Schematic illustrations of three basic modes for transfer printing. Reprinted with permission from [45]. Copyright © 2012 WILEY-VCH Verlag GmbH & Co., b) schematic diagram of the fabrication procedures for the freestanding OFETs using modified water-floatation method. Reprinted with permission from [52]. Copyright © 2013 WILEY-VCH Verlag GmbH & Co., c) schematic illustrations of the process for fabricating flexible crossbar-structured memory on a plastic substrate via the laser lift-off transfer method. Reprinted with permission from [54]. Copyright © 2014 WILEY-VCH Verlag GmbH & Co., d) schematic illustration of the cells in the conducting-interlayer SiOx memory device sputtered at room temperature. Reprinted with permission from [55]. Copyright © 2014 WILEY-VCH Verlag GmbH

**Figure 1.3.2.2:** Schematic illustration of the controlled spalling process used for removing the prefabricated devices and circuits from the rigid silicon handle wafer. The inset schematically shows the device architecture for the ultra-thin body transistors with raised source/drain regions. Reprinted with permission from [59]. Copyright (2012) American Chemical Society.

### 1.3.3. Flexible Silicon Systems

The complementary transfer-free approach uses a fundamental inverse proportionality between the material's thickness (t) and its flexibility. Equation 1 shows the relation between the deflection ' $\delta$ ' occurring in a material, with flexural modulus " $E_{Flexural}$ ", thickness 't,' length 'L' and width 'w,' due to an applied force 'F.'  $E_{Flexural}$  is a material property. Therefore, for specific 'L' and 'w,' a material with lower thickness 't' would experience larger deflections ' $\delta$ ' due to the same applied force 'F' (i.e. it becomes more flexible). Hence, we transform traditional, rigid electronic devices on economical Si (100) wafers into new, flexible devices by sufficiently reducing the thickness of the host's substrate.

$$\delta = \frac{FL^3}{4E_{Flexural} wt^3} \tag{1}$$

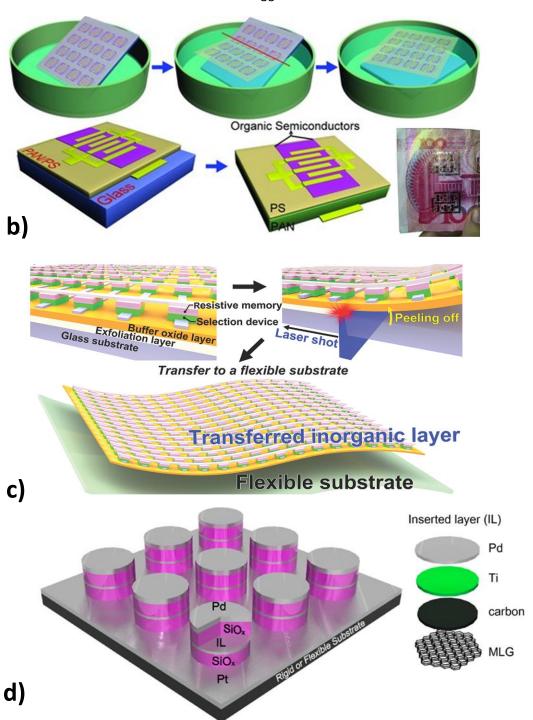

This approach provides a pragmatic solution to the aforementioned critical challenges by copying the associated perks of high performance, reliability, ULSI density, and the low cost of inorganic silicon-based electronics to the flexible arena via a transformed version of traditional devices. Moreover, the silicon industry has capitalized on monolithic integration over the past few decades and because of its core competitive advantages, it has grown into a huge market. Hence, preserving monolithic integration by using Si as a flexible substrate further improves this flexing approach. Figure 1.3.3.1 lists the different silicon-flexing techniques [62, 66, 67]. The scanning electron microscope image in Figure 1.3.3.1b illustrates the added advantage of extra device active area, which may be available in the form of conformal deposition of device layers through release trenches (holes) [129]. The etch-protect-release approach incurs some lost area, which is compensated by the potential reliability associated with the relatively novel air-gap shallow trench isolation (STI) technology [130]. On the other hand, remaining portions of the wafer can be recycled after chemical mechanical polishing and the holes network has a self-cooling effect, acting as air cooling channels for heat dissipation [131].

Although, conceptually the soft back-etching process (Figure 1.3.3.1c) is similar to the traditional back-grinding technique, there are considerable differences. For example, the soft back etch is a simple and delicate process compared to the complex and abrasive nature associated with the induced scratches, crystal defects, and the formation of stresses that take place during back grinding [132]. Furthermore, using the soft back etch requires no chemical mechanical polishing and leaves no residual stress on the substrate unlike the machining stress caused during back grinding [133-135]. Finally,

back grinding to thinner substrates causes subsurface damage [135] and shallow surface cracks [134].

Figure 1.3.3.1: a) Device first approach illustration where the devices are fabricated in a traditional fashion, then, protected using photoresist (PR). The PR is then patterned and the pattern is transferred to the field oxide (FOX) layer then to the Si substrate. Using the spacer technique, a highly conformal atomic layer deposition (ALD) spacer is deposited for sidewalls. Finally, the dies are put in a reactive chamber containing XeF2 gas for isotropic Si when the etching regions merge, the top flexible portion of Si (100) containing the devices can be safely released, b) device last approach illustration where flexible silicon fabric is first released then devices are built. Adapted with permission from [129]. Copyright © 2014 WILEY-VCH Verlag GmbH & Co., c) illustration of the soft-etch back approach where the traditional dies containing devices are covered with PR for protection, then, the die is flipped upside down and etched using DRIE to the desired thickness. Adapted with permission from [67]. Copyright (2014) American Chemical Society.

Fracture strength is a property that applies to all techniques because it determines the overall mechanical stability of an ultra-thin flexible electronic system [136]. To assess the fracture strength of a substrate, the most common method is the three-point bending test [137]. For Si thicknesses greater than 100 µm, the linear elastic bending beam theory provides an accurate estimation of fracture strength [138,139]; however, thinner substrates produce a nonlinear deflection-load relationship that is used to estimate fracture strength (Figure 1.3.3.2). This is caused by the large deflection of the thin silicon substrate resulting from horizontal forces at the supporting bearings; to account for this nonlinearity, in 2015 Liu et al. introduced the large deflection theory of beam [137]. This relationship provides important insights for theoretical limitations of flexible silicon thinner than 100 µm. Furthermore, based on the application's required bending radius, the thickness of the flexible silicon substrate must be adjusted such that the applied stress (stress=Young's modulus x strain  $(\varepsilon)$ , where nominal strain is defined as  $\varepsilon_{\text{nominal}}$ =(thickness (t))/((2 x bending radius (r))) is lower than the fracture stress (fracture stress of thin Si substrates is higher than that of thicker substrates). For instance, [137] shows that for a 50-um thick silicon substrate, the fracture stress is ~ 1.1 GPa. At the lowest estimate for Si (100), the Young's modulus is 128 GPa [140]; hence, the minimum bending radius that would cause fracture stress for a 50-µm thick flexible silicon substrate is ~ 3 mm and decreases with decreasing thicknesses. Therefore, a vanilla flexible silicon substrate that is 50-um thick or less with a bending radius of > 3 mm will safely operate below the fracture stress level. We would like to point out that these results are for a bare silicon (100) substrate with no additive layers or patterns for devices. Therefore, based on the properties of the material, thickness of the substrate, and the bending radius necessary

for a specific application, the most suitable approach and material system can be determined. Noteworthy, the nominal strain is only a nominal value; whereas, the actual stress value depends on the modulus of elasticity of specific constituent material stacks.

**Figure 1.3.3.2:** Deflection versus applied load plot for various thicknesses of flexible substrates, dotted lines showing non-linear analytical solution for 30 and 40 μm thick substrates and linear analytical solution for 100 μm thick substrates. Adapted courtesy of Prof. YongAn Huang, Huazhong University of Science and Technology, China.

As identified by the International Technology Roadmap for Semiconductors (ITRS) 2013 Emerging Research Devices report, the main challenge will be to identify replacement technologies for static RAM and flash as they approach their physical limits [141]. Replacements must provide electrically accessible, high-speed, high-density, low-power NVMs that meet the reliability requirements for the desired devices including surviving high temperatures. It will be important to identify and address other reliability

issues early in the development process. The temperature requirement for flexible, inorganic silicon-based NVM devices is a given because the materials used will have already survived the high thermal budgets required for the deposition of high-quality thin films used in complementary metal oxide semiconductor (CMOS) technology and subsequent front-end-of-line processing anneals. Due to the advancements in lithography, properties of a flexible inorganic NVM also rely on high integration density.

Challenges common to both organic and inorganic material systems toward their application in future electronics, including IoT devices include (i) attaining high speeds, (ii) being suitable for low-power devices, and (iii) identifying and assessing the reliability issues that arise when devices are flexed beyond the standard studied stresses in planar substrates. In addition, organic electronics must also achieve temperature stability and satisfactory integration density. The forthcoming sections of the dissertation focus on our contributions in advancing the status quo of the flexible silicon system approach as a feasible solution for future flexible IoT and wearable memories and electronic systems.

### 1.4. References

- [1] Han, S.-T.; Zhou, Y.; Roy, V.A.L. Towards the Development of Flexible Non-Volatile Memories. *Adv. Mater.* 2013, 25, 5425-5449.

- [2] Govoreanu, B.; Kar, G.; Chen, Y.; Paraschiv, V.; Kubicek, S.; Fantini, A.; Radu, I.; Goux, L.; Clima, S.; Degraeve, R.  $10 \times 10 \text{nm}^2$  Hf/HfOx crossbar resistive RAM with excellent performance, reliability and low-energy operation. In IEEE International Electron Device Meeting, Washington, DC, USA, 5-7 December 2011, pp. 31.6.1-31.6.4.

- [3] Jo, S.H.; Chang, T.; Ebong, I.; Bhadviya, B.B.; Mazumder, P.; Lu, W. Nanoscale memristor device as synapse in neuromorphic systems. *Nano Lett.* 2010, 10, 1297-1301.

- [4] Strukov, D.B.; Snider, G.S.; Stewart, D.R.; Williams, R.S. The missing memristor found. *Nature* 2008, 453, 80-83.

- [5] Chua, L.O. Memristor-the missing circuit element. *IEEE Trans. Circuit Theory* 1971, 18, 507-519.

- [6] Shannigrahi, S.R.; Jang, H.M. Fatigue-free lead zirconate titanate-based capacitors for nonvolatile memories. *Appl. Phys. Lett.* 2001, 79, 1051-1053.

- [7] Parkin, S.; Xin, J.; Kaiser, C.; Panchula, A.; Roche, K.; Samant, M. Magnetically engineered spintronic sensors and memory. *Proc. IEEE* 2003, 91, 661-680.

- [8] Gupta, M.K.; Hasan, M. Robust High Speed Ternary Magnetic Content Addressable Memory. *IEEE Trans. Electron Devices* 2015, 62, 1163-1169.

- [9] Lencer, D.; Salinga, M.; Wuttig, M. Design Rules for Phase-Change Materials in Data Storage Applications. *Adv. Mater.* 2011, 23, 2030-2058.

- [10] Yoon, J.M.; Shin, D.O.; Yin, Y.; Seo, H.K.; Kim, D.; Kim, Y.I.; Jin, J.H.; Kim, Y.T.; Bae, B.-S.; Kim, S.O. Fabrication of high-density In<sub>3</sub>Sb<sub>1</sub>Te<sub>2</sub> phase change nanoarray on glass-fabric reinforced flexible substrate. *Nanotechnology* 2012, 23, 255301.

- [11] Jeon, Y.; Lee, M.; Moon, T.; Kim, S. Flexible Nano-Floating-Gate Memory With Channels of Enhancement-Mode Si Nanowires. *IEEE Trans. Electron Devices* 2012, 59, 2939-2942.

- [12] Yoon, K.; Il Han, P.; Seongjae, C.; Jang-Gn, Y.; Jung Hoon, L.; Doo-Hyun, K.; Gil Sung, L.; Se-Hwan, P.; Dong Hua, L.; Won Bo, S.; Wandong, K.; Hyungcheol, S.; Jong-Duk, L.; Park, B.-G. A Vertical 4-Bit SONOS Flash Memory and a Unique 3-D Vertical Array Structure. *IEEE Trans. Nanotechnol.* 2010, 9, 70-77.

- [13] Lee, J.S.; Kim, Y.M.; Kwon, J.H.; Shin, H.; Sohn, B.H.; Lee, J. Tunable memory characteristics of nanostructured, nonvolatile charge trap memory devices based on a binary mixture of metal nanoparticles as a charge trapping layer. *Adv. Mater.* 2009, 21, 178-183.

- [14] Pott, V.; Vaddi, R.; Geng Li, C.; Lin, J.T.M.; Kim, T.T. Design Optimization of Pulsed-Mode Electromechanical Nonvolatile Memory. *IEEE Electron Device Lett.* 2012, 33, 1207-1209.

- [15] Young Choi, W.; Hei, K.; Lee, D.; Lai, J.; Tsu-Jae King, L. Compact Nano-Electro-Mechanical Non-Volatile Memory (NEMory) for 3D Integration. In IEEE International Electron Devices Meeting, Washington, DC, USA, 10-12 December 2007, pp. 603-606.

- [16] Green, J.E.; Choi, J.W.; Boukai, A.; Bunimovich, Y.; Johnston-Halperin, E.; DeIonno, E.; Luo, Y.; Sheriff, B.A.; Xu, K.; Shin, Y.S. A 160-kilobit molecular electronic memory patterned at 1011 bits per square centimetre. *Nature* 2007, 445, 414-417.

- [17] Joachim, H.O.; Jacob, M.; Rehm, N. 2T2C signal margin test mode using a defined charge exchange between BL and/BL. U.S. Patents US6876590 B2, 5 April 2005.

- [18] Wang, X.P.; Fang, Z.; Li, X.; Chen, B.; Gao, B.; Kang, J.F.; Chen, Z.X.; Kamath, A.; Shen, N.S.; Singh, N.; Lo, G.Q.; Kwong, D.L. Highly compact 1T-1R architecture (4F<sup>2</sup> footprint) involving fully CMOS compatible vertical GAA nano-pillar transistors and oxide-based RRAM cells exhibiting excellent NVM properties and ultra-low power operation. In IEEE International Electron Devices Meeting, Washington, DC, USA, 10-12 December 2007, San Francisco, CA, USA, 10-13 December 2012, pp. 20.6.1-20.6.4.

- [19] Joachim, H.O.; Jacob, M.; Rehm, N. 2T2C signal margin test mode using a defined charge exchange between BL and/BL. U.S. Patents US20040095821 A1, 20 May 2004.

- [20] Ogasawara, S.; Ishiwara, H. Fabrication and characterization of 1T2C-type ferroelectric memory cell with local interconnections. *Jpn. J. Appl. Phys.* 2002, 41, 6895.

- [21] Hyun-Soo, K.; Shuu'ichirou, Y.; Toru, I.; Takaaki, F.; Hiroshi, O.; Hiroshi, I. Fabrication and Characterization of 1 k-bit 1T2C-Type Ferroelectric Memory Cell Array. *Jpn. J. Appl. Phys.* 2005, 44, 2715.

- [22] Hyun-Soo, K.; Shuu'ichirou, Y.; Hiroshi, I. Improved Data Disturbance Effects in 1T2C-Type Ferroelectric Memory Array. *Jpn. J. Appl. Phys.* 2004, 43, 2558.

- [23] Zhou, H.; Seo, J.-H.; Paskiewicz, D.M.; Zhu, Y.; Celler, G.K.; Voyles, P.M.; Zhou, W.; Lagally, M.G.; Ma, Z. Fast flexible electronics with strained silicon nanomembranes. *Sci. Rep.* 2013, 3, 1291.

- [24] Des Etangs-Levallois, A.L.; Lesecq, M.; Danneville, F.; Tagro, Y.; Lepilliet, S.; Hoel, V.; Troadec, D.; Gloria, D.; Raynaud, C.; Dubois, E. Radio-frequency and low noise characteristics of SOI technology on plastic for flexible electronics. *Solid-State Electron.* 2013, 90, 73-78.

- [25] Nasr, B.; Wang, D.; Kruk, R.; Rösner, H.; Hahn, H.; Dasgupta, S. Flexible Electronics: High-Speed, Low-Voltage, and Environmentally Stable Operation of Electrochemically Gated Zinc Oxide Nanowire Field-Effect Transistors. *Adv. Funct. Mater.* 2013, 23, 1729-1729.

- [26] Han, S.T.; Zhou, Y.; Wang, C.; He, L.; Zhang, W.; Roy, V. Flexible Electronics: Layer-by-Layer-Assembled Reduced Graphene Oxide/Gold Nanoparticle Hybrid Double-Floating-Gate Structure for Low-Voltage Flexible Flash Memory. *Adv. Mater.* 2013, 25, 793-793.

- [27] Farsinezhad, S.; Mohammadpour, A.; Dalrymple, A.N.; Geisinger, J.; Kar, P.; Brett, M.J.; Shankar, K. Transparent anodic TiO<sub>2</sub> nanotube arrays on plastic substrates for disposable biosensors and flexible electronics. *J. Nanosci. Nanotechnol.* 2013, 13, 2885-2891.

- [28] Majewski, L.; Grell, M.; Ogier, S.; Veres, J. A novel gate insulator for flexible electronics. *Org. Electron.* 2003, 4, 27-32.

- [29] McAlpine, M.C.; Friedman, R.S.; Lieber, C.M. High-performance nanowire electronics and photonics and nanoscale patterning on flexible plastic substrates. *Proc. IEEE* 2005, 93, 1357-1363.

- [30] Sun, Y.; Rogers, J.A. Inorganic semiconductors for flexible electronics. *Adv. Mater.* 2007, 19, 1897-1916.

- [31] Rogers, J.A.; Someya, T.; Huang, Y. Materials and Mechanics for Stretchable Electronics. *Science* 2010, 327, 1603-1607.

- [32] Sokolov, A.N.; Tee, B.C.K.; Bettinger, C.J.; Tok, J.B.H.; Bao, Z. Chemical and Engineering Approaches To Enable Organic Field-Effect Transistors for Electronic Skin Applications. *Acc. Chem. Res.* 2012, 45, 361-371.

- [33] Wang, C.; Hwang, D.; Yu, Z.; Takei, K.; Park, J.; Chen, T.; Ma, B.; Javey, A. User-interactive electronic skin for instantaneous pressure visualization. *Nat. Mater.* 2013, 12, 899-904.

- [34] Mei, Y.; Loth, M.A.; Payne, M.; Zhang, W.; Smith, J.; Day, C.S.; Parkin, S.R.; Heeney, M.; McCulloch, I.; Anthopoulos, T.D. High Mobility Field-Effect Transistors with Versatile Processing from a Small-Molecule Organic Semiconductor. *Adv. Mater.* 2013, 25, 4352-4357.

- [35] Kim, R.H.; Kim, H.J.; Bae, I.; Hwang, S.K.; Velusamy, D.B.; Cho, S.M.; Takaishi, K.; Muto, T.; Hashizume, D.; Uchiyama, M. Non-volatile organic memory with sub-millimetre bending radius. *Nat. Commun.* 2014, 5, 3583.

- [36] Liu, X.; Guo, Y.; Ma, Y.; Chen, H.; Mao, Z.; Wang, H.; Yu, G.; Liu, Y. Organic Electronics: Flexible, Low-Voltage and High-Performance Polymer Thin-Film Transistors and Their Application in Photo/Thermal Detectors . *Adv. Mater.* 2014, 26, 3569-3569.

- [37] Lai, Y.-C.; Huang, Y.-C.; Lin, T.-Y.; Wang, Y.-X.; Chang, C.-Y.; Li, Y.; Lin, T.-Y.; Ye, B.-W.; Hsieh, Y.-P.; Su, W.-F. Stretchable organic memory: toward learnable and digitized stretchable electronic applications. *NPG Asia Mater.* 2014, 6, e87.

- [38] Tiwari, J.N.; Meena, J.S.; Wu, C.S.; Tiwari, R.N.; Chu, M.C.; Chang, F.C.; Ko, F.H. Thin-Film Composite Materials as a Dielectric Layer for Flexible Metal–Insulator–Metal Capacitors. *ChemSusChem* 2010, 3, 1051-1056.