# Field-effect transistors based on solution processed zinc tin oxide

Feldeffekttransistoren basierend auf flüssigprozessiertem Zink-Zinn-Oxid

Zur Erlangung des akademischen Grades Doktor-Ingenieur (Dr.-Ing.)

genehmigte Dissertation von M.Sc. Reinhold Benedikt Sykora aus Augsburg

Tag der Einreichung: 09.10.2017, Tag der Prüfung: 15.01.2018

Darmstadt — D 17

1. Gutachten: Prof. Dr.-Ing. Heinz von Seggern

2. Gutachten: Prof. Dr.-Ing. Horst Hahn

Darmstadt 2018

Fachbereich Material- und Geowissenschaften

Elektronische Materialeigenschaften Field-effect transistors based on solution processed zinc tin oxide Feldeffekttransistoren basierend auf flüssigprozessiertem Zink-Zinn-Oxid

Genehmigte Dissertation von M.Sc. Reinhold Benedikt Sykora aus Augsburg

1. Gutachten: Prof. Dr.-Ing. Heinz von Seggern

2. Gutachten: Prof. Dr.-Ing. Horst Hahn

Darmstadt 2018

Tag der Einreichung: 09.10.2017

Tag der Prüfung: 15.01.2018

Darmstadt — D 17

Bitte zitieren Sie dieses Dokument als:

URN: urn:nbn:de:tuda-tuprints-72097

URL: http://tuprints.ulb.tu-darmstadt.de/7209

Dieses Dokument wird bereitgestellt von tuprints,

E-Publishing-Service der TU Darmstadt

http://tuprints.ulb.tu-darmstadt.de

tuprints@ulb.tu-darmstadt.de

Die Veröffentlichung steht unter folgender Creative Commons Lizenz: Namensnennung – Keine kommerzielle Nutzung – Keine Bearbeitung 4.0 Deutschland http://creativecommons.org/licenses/by-nc-nd/4.0/de/

## Erklärung zur Dissertation

Hiermit versichere ich, die vorliegende Dissertation ohne Hilfe Dritter nur mit den angegebenen Quellen und Hilfsmitteln angefertigt zu haben. Alle Stellen, die aus Quellen entnommen wurden, sind als solche kenntlich gemacht. Diese Arbeit hat in gleicher oder ähnlicher Form noch keiner Prüfungsbehörde vorgelegen.

| Darmstadt, den 09.1 | 10.2017 |

|---------------------|---------|

|                     |         |

|                     |         |

|                     |         |

(M.Sc. Reinhold Benedikt Sykora)

## Zusammenfassung

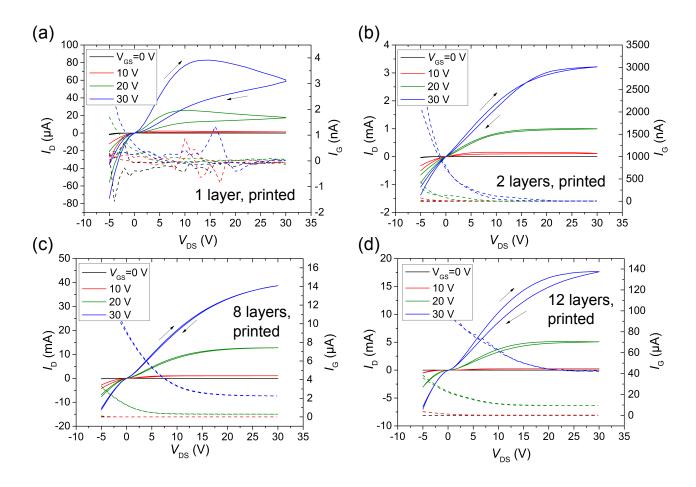

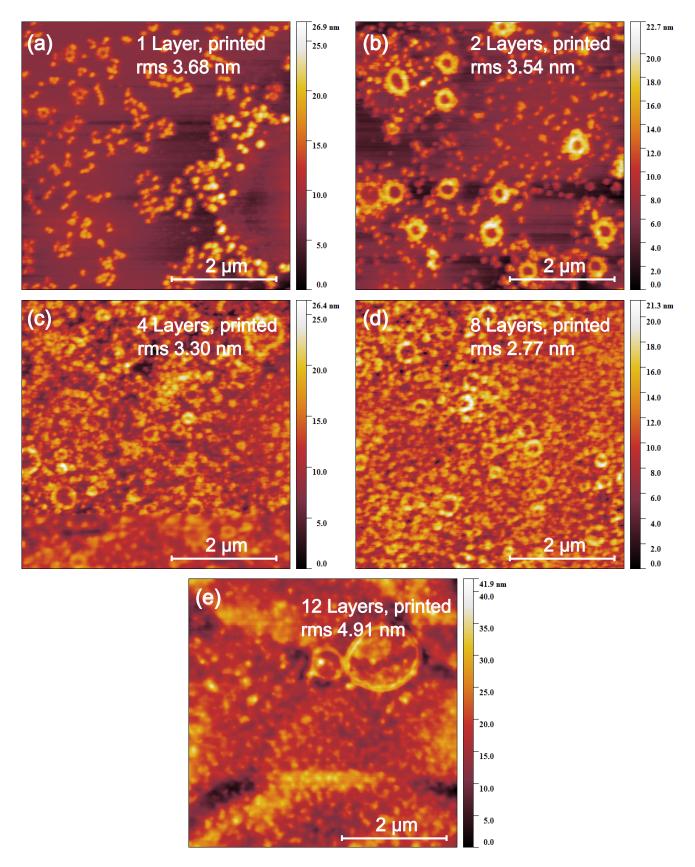

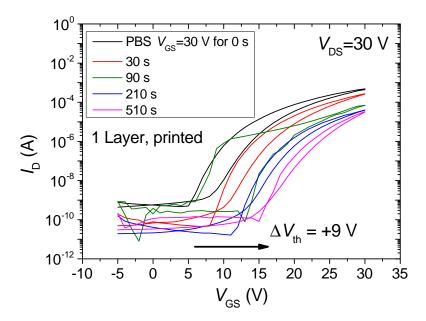

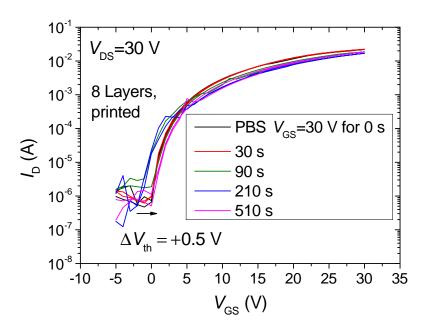

vielfälitger Verwendung besitzt es auch einige Nachteile. Erstens muss die kristalline Reinheit sehr hoch sein, um gute Bauteileigenschaften zu erhalten. Um dies erreichen zu können sind teure und aufwändige Herstellungsmethoden nötig. Für spezielle Anwendungen wie zum Beispiel radio-frequency identification (RFID)-Systeme sind dessen hohe Herstellungskosten nicht geeignet. Auf der anderen Seite besitzt Zink-Zinn-Oxid (ZTO), als ein amorpher Metalloxid Halbleiter (AOS), welcher aus der Flüssigphase hergestellt wird, trotz seines amorphen Charakters gute Transistorkennwerte. Im Gegensatz zum umfassend untersuchten Indium-Gallium-Zink-Oxid (IGZO) enthält es nicht das teure Indium. In dieser Arbeit wurde eine Prekursorenroute entwickelt, die nicht auf dem gängigen, aber giftigen Methylglycol basiert. Als Hauptlösungsmittel diente Ethanol, mit Ethylenglycol als optionalem Zweitlösungsmittel. Mit Hilfe dieser Prekursorlösungen konnten dünne ZTO-Schichten entweder mittels Aufschleudern oder Drucken hergestellt werden. Untersuchungen ergaben, dass die erhaltenen Filme eine geringe Oberflächenrauigkeit haben und hauptsächlich eine amorphe Struktur zeigen, in der Zinkoxid Nanokristallite enthalten sind. Die prozessierten ZTO-Schichten sind transparent und zeigen eine n-Dotierung. Anhand Untersuchungen von Bottom-Gate-Transistoren konnte herausgefunden werden, dass ein Verhältnis von Zink zu Zinn von 7:3 die besten Transistorkennwerte erzielte. Ferner wurde gezeigt, dass ein Ersatz von 40 % Ethanol durch Ethylenglycol die Bauteilkennwerte verbessern konnte und dass Salzsäure, welche als Stabilisator in der Prekursorenlösung dient, Elektronenfallen erzeugen kann. Mit Hilfe eines Multischichtenansatzes von gedruckten ZTO-Schichten war es möglich, die Transistorkennwerte zu verbessern. Die höchste je berichtete Elektronenmobilität von  $7.8\,\mathrm{cm}^2\mathrm{V}^{-1}\mathrm{s}^{-1}$  für gedruckte ZTO-Transistoren wurde bei acht prozessierten Schichten erhalten. Es konnte des weiteren gezeigt werden, dass ein Transistor, der aus mehr als vier ZTO-Schichten aufgebaut ist, eine höhere Widerstandsfähigkeit gegenüber positivem Gate Spannungsstresstest (PBS) und gegenüber Wasser als Elektronendonator und Sauerstoff als Elektronenakzeptor im ZTO-System zeigt. Transistoren, welche mehr als vier ZTO-Schichten besitzen, zeigen gute Kennwerte, obwohl sie bei 350 °C anstatt der Standardeinstellung von 500 °C ausgeheizt wurden. Der Grund für die besseren Transistor-Kennwerte und die höhere Widerstandsfähigkeit gegenüber Gasen in der Atmosphäre mittels Multischichtenansatzes konnte auf eine verbesserte Oberflächenbedeckung und eine höhere Filmqualität zurückgeführt werden. Des weiteren war es möglich einen Aufbau für zeitabhängige Transistormessungen zu realisieren und die ersten Ergebnisse zeigten, dass die schnellsten Einschaltzeiten gemessen werden konnten, wenn der

Fast alle Transistoren basieren auf anorganischen Halbleitern, wie zum Beispiel Silizium. Trotz dessen

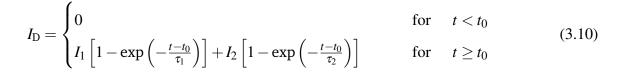

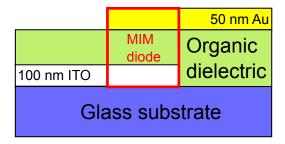

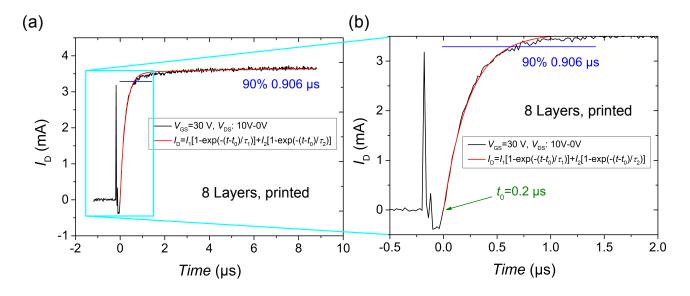

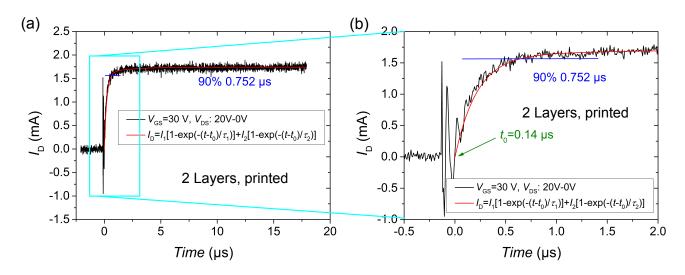

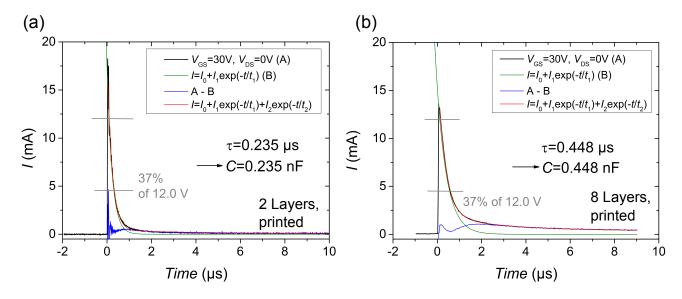

Transistor im linearen Bereich betrieben wird. Die höchste Schaltfrequenz eines Transistors wurde mit 1.33 MHz gemessen. Es konnte gezeigt werden, dass der Einschaltvorgang anhand von zwei Zeitkonstanten beschrieben werden kann. Es ist anzunehmen, dass die kurze Zeitkonstante den Transport der injezierten Ladungsträger repräsentiert, während die lange Zeitkonstante den Transport der gefangenen Ladungsträger darstellt.

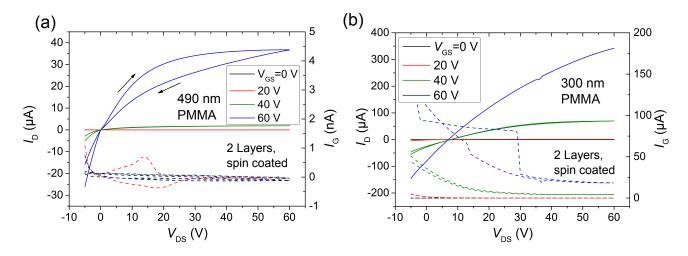

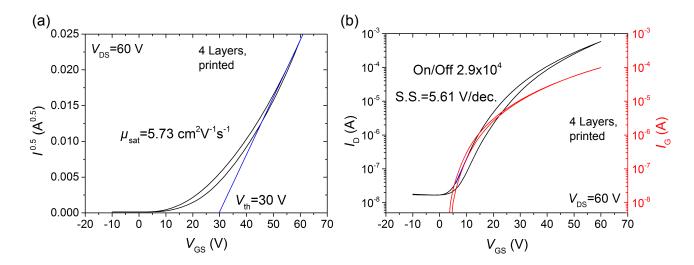

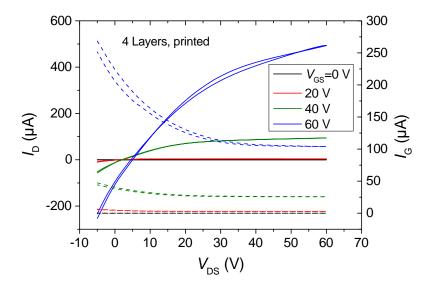

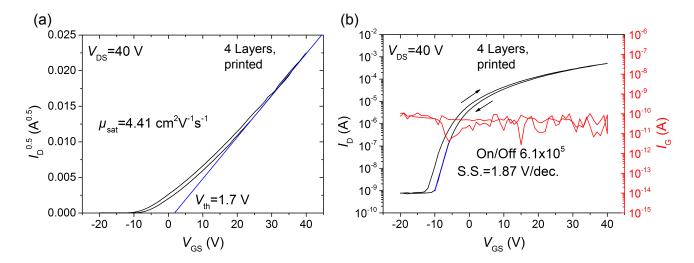

Außerdem konnten funktionale ZTO Top-Gate-Transistoren mit den organischen Dielektrika Polymethylmethacrylat (PMMA), Polystyrol (PS) und ein vernetzbares Copolymer (PAZ) realisiert werden. Es konnte gezeigt werden, dass eine Dicke des Dielektrikums PMMA von mindestens 490 nm nötig ist, um gute Transistor-Kennwerte bei niedrigen Leckströmen zu erhalten. Die besten Top-Gate-Transistoren konnten durch eine veränderte Elektrodenstruktur realisiert werden, die eine Überlappung zwischen Source/Drain und Gate-Elektode reduziert. Der beste gedruckte ZTO Top-Gate Transistor, der diese Elektrodenanordnung in Verbindung mit PMMA benutzt, zeigte eine Elektronenbeweglichkeit von bis zu 4.4 cm<sup>2</sup>V<sup>-1</sup>s<sup>-1</sup>. Dieser Wert ist der höchste je berichtete Wert für einen gedruckten ZTO/PMMA Top-Gate-Transistor. Im Vergleich dazu zeigten die Top-Gate-Transistoren mit PS und PAZ deutlich geringere Transistorkennwerte. Diese Messergebnisse konnten mit einer besseren Benetzung des polareren PMMA auf dem eher hydrophilen ZTO begründet werden.

Die in dieser Arbeit präsentierten Ergebnisse könnten zur Prozessierung von kosteneffizienten, umweltfreundlichen, gedruckten und leistungsfähigen Dünnschichttransistoren beitragen.

## **Abstract**

Most of the transistors are based on inorganic semiconductors such as the ubiquitous silicon (Si). Nevertheless they have some problematic issues. First, their crystalline quality must be very high to guarantee good device properties. Second, in order to achieve the first point costly and demanding processing methods are necessary. For certain application like radio-frequency identification (RFID) tags these processing cost are too high. On the other hand zinc tin oxide (ZTO) as an amorphous oxide semiconductor (AOS) can be processed out of solution and ensures good device characteristics even in the amorphous phase. In contrast to the widely studied indium gallium zinc oxide (IGZO) it does not contain the costly indium. In this thesis a precursor route for ZTO was developed that does not use the common but toxic 2-methoxyethanol as a solvent. It applied ethanol (EtOH) and ethylene glycol (EG) as an optional co-solvent. By applying this precursor solution thin ZTO films could be processed either by spin coating or ink-jet printing. Investigations revealed their smoothness, and predominant amorphous phase with small embedded zinc oxide (ZnO) nanocrystallites. The obtained transparent films exhibited an n-doped character. By building bottom-gate transistors using these ZTO films it could be shown that a Zn:Sn ratio of 7:3 produces the best transistor results, the replacement of 40% of EtOH by EG could improve the thin film transistor (TFT) performance, and the stabilizer hydrochloric acid (HCl) led to the creation of electronic trap states. A multiple layer approach led to the improvements of all transistor parameters. The highest ever reported mobility of up to 7.8 cm<sup>2</sup>V<sup>-1</sup>s<sup>-1</sup> for an ink-jet printed bottom-gate ZTO transistor was obtained by processing eight layers. It could also be shown that a transistor composed of more than four layers had better resistance against positive bias stress (PBS) and water (H<sub>2</sub>O) or oxygen (O<sub>2</sub>) in the atmosphere. While H<sub>2</sub>O acts as an electron donor in the ZTO system, O<sub>2</sub> leads to electron accumulation at the oxide surface. Devices composed of multiple layers showed acceptable performance even if annealed at a reduced temperature of 350 °C compared to the standard setting of 500 °C. The reason for the multiple-layer enhancements was identified as an improved surface coverage and film quality. A setup for time dependent transistor measurements was realized and the first results revealed, that the fastest switching of the ZTO transistors took place in the linear regime. The highest switching frequency of a transistor was measured to be 1.33 MHz. The investigated on-switching behavior can be described by two time constants. It is very likely that the small time constant represents the transport of the injected charge carriers while the long time constant is a measure for the transport of trapped charge carriers. Functional hybrid top-gate transistors using ZTO and the organic dielectric materials poly(methyl methacrylate) (PMMA), polystyrene (PS), and a benzyl azide containing copolymer (PAZ) could be processed. It was shown that a minimal thickness of 490 nm of the organic dielectric PMMA was necessary to ensure good device performance and small leakage currents. The best performance could be achieved if new electrode masks were applied in order to reduce the overlap between the source/drain and gate electrode. The best working printed ZTO top-gate transistor using these masks and a PMMA layer showed a mobility of up to  $4.4\,\mathrm{cm^2V^{-1}s^{-1}}$ . To the best of the author's knowledge this is the highest reported mobility of an ink-jet printed ZTO/PMMA top-gate transistor. The top-gate transistors using PS and PAZ as dielectrics exhibited inferior device performance. This result could be explained by a better adhesion of the polar PMMA to the quite hydrophilic ZTO surface. The results presented in this thesis could contribute to realizing easily processable, cost efficient, environmental friendly, printable, and good performing TFTs.

# **Contents**

| 1  | Intr    | oduction                                                           | 1    |

|----|---------|--------------------------------------------------------------------|------|

| 2  | The     | ory                                                                | 5    |

|    | 2.1     | Basics of inorganic semiconductors                                 | . 5  |

|    | 2.2     | Theory of field-effect transistors                                 | 10   |

|    | 2.3     | Basics of amorphous oxide semiconductors                           | 17   |

|    | 2.4     | Zinc tin oxide as semiconductor                                    | 21   |

| 3  | Exp     | periment                                                           | 23   |

|    | 3.1     | Precursor route                                                    | 23   |

|    | 3.2     | Processing methods                                                 | 24   |

|    | 3.3     | Transistor layouts                                                 | . 27 |

|    | 3.4     | Thin film characterization techniques                              | 33   |

|    | 3.5     | Electrical characterization                                        | 41   |

| 4  | Res     | ults and discussion                                                | 47   |

|    | 4.1     | Results of thin film characterization                              | 47   |

|    | 4.2     | Effects of precursor route on bottom-gate transistors              | 57   |

|    | 4.3     | Multiple-layer approach of printed bottom-gate transistors         | 67   |

|    | 4.4     | Time dependent measurements of printed bottom-gate transistors     | 74   |

|    | 4.5     | Impact of reduced annealing temperature on bottom-gate transistors | 79   |

|    | 4.6     | Atmospheric effects on bottom-gate transistors                     | 83   |

|    | 4.7     | Top-gate transistors based on different organic dielectrics        | 90   |

| 5  | Con     | nclusion and outlook                                               | 105  |

|    | 5.1     | Conclusion                                                         | 105  |

|    | 5.2     | Outlook                                                            | 107  |

| Li | st of ] | Figures                                                            | 109  |

| Li | st of ' | Tables                                                             | 113  |

| List of abbreviations                   | 115 |

|-----------------------------------------|-----|

| Nomenclature                            | 119 |

| Bibliography                            | 123 |

| Curriculum Vitae                        | 137 |

| Publications & Conference contributions | 139 |

| Acknowledgments                         | 141 |

VIII Contents

## 1 Introduction

We are living in the electronic age. Almost everyone naturally uses smartphones, computers, and other smart devices. But only very few people know how these devices work or that most of them contain millions and millions of transistors. But what are these transistors and how did they evolve? They were first realized 70 years ago at Bell Laboratories. One year later Jon Bardeen and Walter Brattain first reported a point contact transistor using germanium (Ge) as the active material [1]. With this three terminal device it was possible to amplify current signals. Their advisor William Shockley published soon after a work explaining the principle behind this new device [2]. Bardeen and Brattain already reported that their new device also worked using silicon (Si) as the active material. The major benefit of this material is the quality of the interface between its perfectly ordered single crystalline phase with electron mobility values of up to  $1500\,\mathrm{cm}^2\mathrm{V}^{-1}\mathrm{s}^{-1}$  [3] and its amorphous oxide state silicon dioxide (SiO<sub>2</sub>). Due to this fact most electronic devices continue to be based on this material combination. A big drawback of this material system is that its electronic properties suffer greatly if impurities are introduced or if the polycrystalline or even the amorphous phase is used for the production of transistors. Therefore great effort has to be taken to process single crystalline Si with very few defects. These processes are very complex and costly. For certain low demanding products like RFID devices or membranes other materials came into consideration for research groups all over the world. These materials include small organic molecules and polymers first reported by Chiang et al. in 1977 [4]. The benefits of these organic semiconductors are that most of them especially the polymers can be processed out of solution at low temperatures, making them feasible for flexible substrates [5]. Their two main problems are that they are very sensitive to oxygen (O<sub>2</sub>) and water (H<sub>2</sub>O) in the atmosphere and that they normally exhibit small charge carrier mobility values in the range of 1 cm<sup>2</sup>V<sup>-1</sup>s<sup>-1</sup> or smaller. In 2004 amorphous oxide semiconductor (AOS)s evolved as another kind of material since Nomura et al. [6] reported on indium gallium zinc oxide (IGZO) which they processed at room temperature making it possible to realize electronic devices on flexible substrates. Since then many research groups worked on crystalline zinc oxide (ZnO) as a promizing transparent conductive oxide (TCO) material [7, 8, 9]. Due to the introduction of additional elements into the ZnO system amorphous phases can be realized and the scattering of charge carriers at grain boundaries can be avoided [10]. The main benefits of this kind of materials are that most of them can be processed out of solution, they form transparent thin films, they exhibit large mobility values of up to  $100 \, \mathrm{cm}^2 \mathrm{V}^{-1} \mathrm{s}^{-1}$ , and they are normally not sensitive to atmospheric H<sub>2</sub>O and O<sub>2</sub> [11]. As Nomura et al. several research groups work on AOS materials containing indium. Unfortunately, this rare earth element is not so abundant [12] with a concentration of  $10^{-7}$  in the crust of the earth [13]. In addition, it has to be taken into account that most research groups use the toxic solvent 2-methoxyethanol which is not suitable for industrial production.

Recently the first industrial products based on printed electronics like the membrane switches produced by the company Metafas displayed in **Figure 1.1** has been realized [14].

**Figure 1.1:** Different printed membrane switches distributed by the company Metafas from the Netherlands [14].

An important building block of such membranes are transistors. For this electronic devices different layout configurations exist. The two main layouts can differ in the position of the gate electrode. In comparison to the widely processed bottom-gate configuration the use of the top-gate layout has certain advantages. For instance organic dielectric materials can not be processed in the bottom-gate approach since the decomposition of the precursor normally requires high temperature which would severely affect them [15]. Furthermore the dielectric layer can act as a protective layer of the semiconductor against any interaction with gaseous species [16]. The benefits of organic dielectric materials in particular are their transparency, flexibility, and processing simplicity [17, 18].

The aim of this PhD project was to develop a cost efficient and environmental friendly precursor solution route. A route based on ethanol has been realized to achieve indium free zinc tin oxide (ZTO) films. Using this precursor solution ZTO thin films and field-effect transistors were first produced and characterized on purchased prestructured bottom-gate, bottom-contact thin film transistor (TFT) substrates. Then ZTO top-gate transistors based on different solution processed organic dielectrics could be processed and characterized.

This thesis is separated into six chapters. Following the introduction the thesis continues with a chapter about the basics of inorganic semiconductors and field-effect transistors with a focus on transparent conductive oxides and the investigated material ZTO. The experimental part dealing with the precursor route, processing methods, different transistor layouts, and the thin film as well as the electrical

2 1 Introduction

characterization is introduced in chapter 3. Chapter 4 presents and discusses the main results of the research. First the outcome of the thin film characterization is presented followed by a section of how different factors of the precursor route influence the transistor performance. In the next section the effect of multiple-layers on printed transistors is investigated. Then the results of transistors processed at a reduced annealing temperature are introduced. Chapter 4 closes with the analysis of organic dielectrics and the results of hybrid top-gate transistors using ZTO as the semiconductor and organic polymers as the dielectric. The conclusion and outlook is presented in chapter 5.

## 2 Theory

In this chapter the basic principles of inorganic semiconductors with a focus on amorphous semiconductors will be presented. The differences to other materials such as metals and dielectric materials are introduced. Then the theory of field-effect transistors is reported followed by a section about transparent conductive oxides. This chapter closes with a presentation of the main features of the semiconductor: zinc tin oxide (ZTO).

#### 2.1 Basics of inorganic semiconductors

In this section the basic concept of inorganic semiconductors such as its simplified band diagram, the Schottky effect, and current transport mechanisms will be introduced by referring to the books written by Kittel and Sze [19, 3].

#### Simplified band diagram

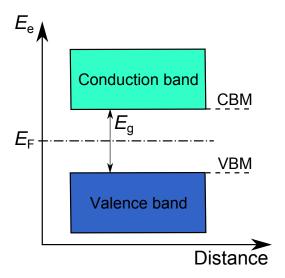

Band diagrams are a representation of Bloch functions that solve the Schrödinger equation for a one electron problem in a periodic lattice. They can be drawn in a Brillouin zone, which is an area in reciprocal space. A simplified band diagram of an ideal semiconductor at a temperature of 0 K can be seen in **Figure 2.1**.

Two important bands are drawn in this diagram with the ordinate being the energy of an electron  $E_e$  and the abscissa being the distance in the real space. On the one hand there is the completely filled valence band with the valence band maximum (VBM) and on the other hand the empty conduction band with the conduction band minimum (CBM). The energy spread between these two locations is called the band gap  $E_g$ . In the case of an undoped semiconductor the Fermi energy lies somewhere close to the middle of this band gap dependent on the density-of-states (DOS) of the two bands.

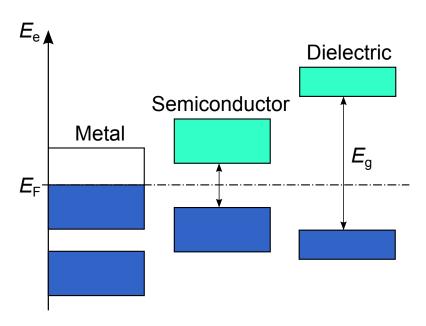

Using the definitions from **Figure 2.1** the simplified band diagram of a metal and a dielectric in comparison to a semiconductor can be drawn according to **Figure 2.2**. On the one hand in a metal the conduction band is not completely filled with electrons. The absence of a band gap is the reason why metals show electrical conductivity even at a very small temperature close to 0 K. Their resistivity is very low with typical values around  $10^{-6} \Omega cm$  [19]. On the other hand dielectrics such as SiO<sub>2</sub> ( $E_g = 9.3 \text{ eV}$  [20]) or

**Figure 2.1:** Simplified band diagram of an ideal semiconductor. The ordinate represents the energy of an electron  $E_e$  and the abscissa the location in the real space. The band lower in energy displayed in blue is the valence band with its maximum point the valence band maximum (VBM). The band higher in energy displayed in green is the conduction band with its lowest point the conduction band minimum (CBM). The energy difference between CBM and VBM is called the band gap  $E_g$ . At 0 K the Fermi energy  $E_F$  lies exactly in the middle of the band gap in the case of an ideal undoped semiconductor.

PMMA ( $E_g$  = 4.8 eV [21]) exhibit very large band gaps. The difficulty of optical excitation and charge carrier injection explains the high resistivity of these materials of up to  $10^{17} \,\Omega$ cm.

**Figure 2.2:** Comparison of the simplified band diagram of metals, semiconductors, and dielectrics. Displayed in blue are the valence bands and in green the conduction bands. Note that the band at  $E_{\rm F}$  is not completely filled in the case of a metal. The semiconductors exhibit a small and the dielectric a large band gap.

#### Important electronic levels

A material can be defined as a semiconductor if its electrical resistivity measured at room temperature lies between  $10^0$  and  $10^{11}\,\Omega$ cm. A perfect semiconductor shows zero conductivity at a temperature of 0 K. Typical and widely studied semiconductors are the element-semiconductors Si and Ge and the compound semiconductors, for example gallium arsenide (GaAs). Semiconductors exhibit small band gaps unlike insulators. For instance Ge exhibits a band gap of 0.66 eV and the band gap of GaAs has been measured at 300 K to be 1.43 eV. If energy is introduced into the system, which exceeds the value of the band gap, electrons can be excited from the fully occupied valence band to the empty conduction band. During this process a positively charged hole is created in the valence band. Both, the electrons and holes, can lead to an increase in conductivity after the application of a voltage.

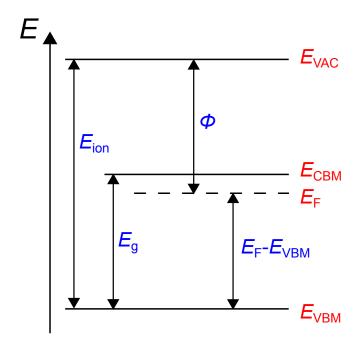

But the band gap is not the only important value to characterize a semiconductor. The difference in potential energy of an electron between the Fermi level  $E_{\rm F}$  and the vacuum level  $E_{\rm VAC}$  is defined as the work function  $\Phi$ . Typical values for the work function are 5.1 eV for gold (Au) [3] and 4.6 eV for indium tin oxide (ITO) [22]. Other fundamental parameters of a semiconductor are the valence band offset  $E_{\rm F} - E_{\rm VBM}$ , which is the difference between the Fermi level and the VBM. The ionization energy  $E_{\rm ion}$  is the energy that is necessary to extract an electron from the valence band to the vacuum level. **Figure** 2.3 displays these main parameters in an electronic scheme of an n-type semiconductor. The energy differences are displayed in blue and the energy levels are shown in red.

The free charge carriers within a semiconductor drift through the material under an applied voltage with the drift velocity  $v_D = \mu \mathcal{E}$  where  $\mathcal{E}$  is the electric field defined as  $\mathcal{E} = V/d$ . The unit of the mobility  $\mu$  is cm<sup>2</sup> V<sup>-1</sup>s<sup>-1</sup>. Both electrons and holes can contribute to the overall conductivity  $\sigma$  of a semiconductor according to the formula  $\sigma = (ne\mu_e) + (pe\mu_h)$ . In this formula n and p describe the concentration of electrons and holes, respectively, e the elementary charge, and  $\mu$  the mobility of electrons or holes.

#### Schottky effect and transport mechanisms

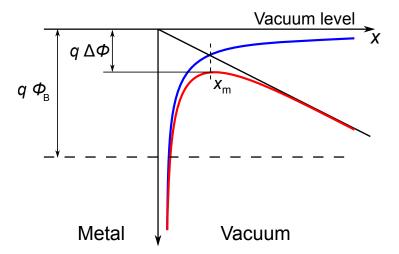

In a unipolar n-type field-effect transistor (FET) the electron injection from the metallic electrodes to the semiconducting material is important. There are two major different metal/semiconductor contact possibilities. The Ohmic contact and the Schottky contact. It is characteristic of an Ohmic contact that the space charge region becomes so small that the electrons can pass it via tunneling which leads to a current independent on the sign of the applied voltage. The Schottky contact will be introduced by referring to the book of Bergmann and Schäfer [23]. If an electric field is applied the potential energy for emission of electrons is reduced owing to the image force. **Figure 2.4** illustrates the Schottky effect that appears at a metal/vacuum interface.

**Figure 2.3:** Energy scheme of an n-type semiconductor showing the main parameters valence band offset  $E_{\rm F} - E_{\rm VBM}$ , band gap  $E_{\rm g}$ , work function  $\Phi$ , and ionization energy  $E_{\rm ion}$  displayed in blue. The main energetic levels  $E_{\rm CBM}$ , Fermi energy  $E_{\rm F}$ ,  $E_{\rm VBM}$ , and vacuum level  $E_{\rm VAC}$  are labeled in red.

**Figure 2.4:** Illustration of the Schottky effect at a metal/vacuum interface. The image force at the interface leads to a decrease of the initial work function  $\Phi_B$  by a value of  $\Delta\Phi$ .

The initial barrier height for thermionic emission of an electron out of the metal  $q\Phi_B$  is reduced by  $q\Delta\Phi$  due to the image force and the maximum is shifted to  $x_m$ . This image force is a result of the created positive elementary charge within the metal that is induced by the removed electron from the metal into the vacuum by the application of an external voltage. The total energy as a function of the distance x at the interface has consequently two contributions, the Coulomb energy from the image force, and the energy from the external applied field  $\mathcal{E}$  (Equation 2.1).

$$E(x) = \frac{q^2}{16\pi\varepsilon_0 x} + q\mathscr{E}x\tag{2.1}$$

In **Equation 2.1** q labels the electric charge and  $\varepsilon_0$  the vacuum permittivity. The changed work function  $\Delta \Phi = \sqrt{\frac{q\mathscr{E}}{4\pi\varepsilon_0}}$  and its position  $x_{\rm m} = \sqrt{\frac{q}{16\pi\varepsilon_0\mathscr{E}}}$  can be obtained if the derivative of (**Equation 2.1**) is set equal zero  $\frac{\mathrm{d}E(x)}{\mathrm{d}x} = 0$ .

If the metal is brought into contact with a semiconductor instead of the vacuum the relative permittivity of the semiconductor has to be taken into account. The electric field  $\mathcal{E}$  in the space charge region of the semiconductor can now be written as displayed in **Equation 2.2**.

$$\mathscr{E} = \sqrt{\frac{2qN_{\rm D}}{\varepsilon_0 \varepsilon_{\rm r}} \left( V - V_{\rm D} - \frac{k_{\rm B}T}{q} \right)} \tag{2.2}$$

$N_{\rm D}$  is the concentration of donors of the n-type semiconductor and  $V_{\rm D}$  is the diffusion voltage.  $V_{\rm D}$  in combination with the applied voltage V represents the factor for the activation energy  $\Delta E = q(V_{\rm D} + V)$ . This activation energy has to be overcome to inject electrons from the semiconductor into the metal since the current has to be proportional to  $n_0 \exp\left(-\frac{q(V_{\rm D}+V)}{k_{\rm B}T}\right)$ .  $n_0$  represents the equilibrium concentration of electrons within the bulk of the semiconductor. With the help of **Equation 2.2** the voltage dependent barrier height  $q\Phi_{\rm B}(V)$  within the space charge region of the semiconductor as a result of the Schottky effect can be determined using **Equation 2.3**

$$q\Phi_{\rm B}(V) = q\sqrt[4]{\frac{N_{\rm D}}{8\pi^2} \cdot \frac{q^3}{\varepsilon_0^3 \varepsilon_{\rm r}^3} \left( \left| V - V_{\rm D} - \frac{k_{\rm B}T}{q} \right| \right)}$$

(2.3)

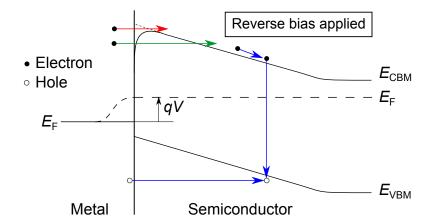

The next image visualizes the three main current transport mechanisms at an interface between a metal and an n-type semiconductor if a bias is applied in reverse direction (**Figure 2.5**). The thermionic emission over the barrier into the semiconductor is displayed in red. This mechanism normally occurs in medium doped semiconductors such as Si with  $N_{\rm D} \leq 10^{-17}$  cm<sup>-3</sup> and is typical for Schottky diodes. The tunneling through the barrier (green) is the standard process in an Ohmic contact with heavily doped semiconductors. The recombination of electrons with holes from the metal in the space charge region is displayed in blue. Other mechanisms like recombination in the neutral region, edge leakage, and interface currents because of traps at the interface will not be presented because their role is negligible in standard inorganic semiconductors.

**Figure 2.5:** Representation of the three main current transport mechanisms that are possible at a metal/semiconductor interface under reverse bias condition. They are the thermionic emission over the barrier displayed in red, the field-emission or tunneling through the barrier shown in green, and the recombination in the space charge region of the semiconductor shown in blue.

#### 2.2 Theory of field-effect transistors

In this section the basics of field-effect transistors will be presented since the properties of the semiconductor ZTO was analyzed using these electronic devices. First, the basic layout and electrical connection of a three terminal device is shown and discussed. Second, the Shockley equations, the most important equations defining a transistor, are discussed. Third, the various operation regimes and the two main *I-V*-characteristics transfer and output in a field-effect transistor, are analyzed. The section closes with a representation of how the most important transistor parameters were obtained graphically using the transfer characteristics.

#### TFT working principle

Transistors are, apart from diodes, detectors or photovoltaic cells, other devices relying on semiconductors. FETs are one part of the family of transistors. Their concept was first reported in the 1930's by Lilienfeld [24, 25, 26]. 30 years later the first TFT was realized by Weimer [27]. A few years later the first TFTs using tin dioxide (SnO<sub>2</sub>) as semiconductor were reported by Klasens and Koelmans [28] and Boesen and Jacobs [29] in the case of ZnO. In 2004 Nomura *et al.* revived the research in AOSs by reporting that IGZO exhibits good transistor properties even if processed at room temperature [6]. Here the basic principle of these electronic devices will be presented by referring to the book *Physics of Semiconductor Devices* written by S.M. Sze [3]. If only one type of charge carrier is employed in a device it is called unipolar. Since most of the AOSs such as ZTO are n-type semiconductors the mechanism of electrons as the majority charge carriers will be discussed. Before the basic principles of a FET are

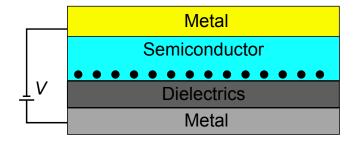

explained the field-effect shall be presented referring to a metal-insulator-semiconductor (MIS) diode as displayed in **Figure 2.6**.

**Figure 2.6:** Sketch showing the field-effect of a metal-insulator-semiconductor (MIS) diode. This diode could be represented as a plate capacitor where the semiconducting and the dielectric layer is placed between the metal plates. Due to the application of an external voltage between the metal plates, electrons, represented as black dots, are accumulated at the semiconductor/dielectric interface.

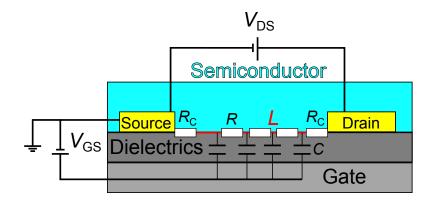

If a voltage V is applied to the metallic layers of a MIS diode, electrons, represented as black dots, can be injected from the top metal and can be accumulated at the semiconductor/dielectric interface. The amplitude of this voltage determines the amount of accumulated electrons. If the top-electrode of a MIS diode is separated into two parts, which define the channel, the three terminal arrangement of a FET shown in **Figure 2.7** can be obtained. A FET can be described as an arrangement of resistors R within the semiconducting layer connected with capacitors C in the dielectrics known in electrical engineering as transmission line [30]. A variable contact resistance  $R_C$  may appear between source and/or drain electrode and the semiconducting channel which could lead to an S-shape in the output characteristic which will be discussed later with the help of **Figure 2.12**.

**Figure 2.7:** Sketch showing the principle layout of a bottom-gate, bottom-contact transistor. It is composed of the three electrodes gate, source, and drain and the semiconductor which forms the conductive channel with length L highlighted in red. A FET can be described as an arrangement of resistors R within the semiconducting channel by capacitors C to the gate [30]. A contact resistance  $R_C$  could exist between the source and/or drain electrode and the semiconducting channel.

The source and drain electrodes are separated from the gate electrode by a dielectric layer of a certain thickness. This three terminal arrangement is called bottom-gate, bottom-contact. Another arrangement of the three electrodes would be the bottom-contact, top-gate configuration. Both arrangements will be discussed in **Figure 3.4**. There exist two possible operation modes in a unipolar transistor. First, there is the mostly desired accumulation mode. This mode occurs if 0 V is applied between the source and the gate electrode and only very low current can be measured between the source and drain electrode ( $I_D$ ). If a positive bias is now applied between the source and gate electrode ( $V_{GS}$ ) electrons which are injected by the source and the drain electrode accumulate due to the field-effect at the semiconductor/dielectric interface. After the application of a positive bias between the source and drain electrode  $(V_{DS})$  these accumulated electrons can be driven toward the drain electrode and an increase in the drain-current can be detected. The length L of this conductive channel between the source and the drain electrode is highlighted in red, but its width W is not displayed in **Figure 2.7**. Second, there is the depletion mode. In this mode a drain-current can be detected even though the gate-source voltage is 0 V. This could happen if the intrinsic semiconducting material already contains enough free charge carriers to contribute to a current flow. A negative  $V_{GS}$  bias has to be applied to turn such a device off. These devices can be called always-on devices. The threshold voltage  $V_{\rm th}$  can be used to differentiate between the two modes. It represents the  $V_{GS}$  at which a conductive layer within the channel is formed by the accumulation of electrons. If its value is positive the transistor works in enhancement mode and if it is negative the transistor works in depletion mode. In addition this parameter is a measure for the amount of electronic trap states. Therefore it should be close to 0 V to obtain an energy efficient device which can be operated at small driving voltages.

#### Operation modes

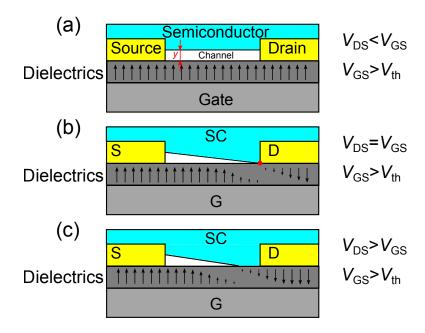

There are three main operation modes in a FET, which are illustrated in **Figure 2.8**. In all three modes the source-gate voltage  $V_{GS}$  is larger than the threshold voltage  $V_{th}$ . In the first mode the source-drain voltage is smaller than the source-gate voltage (a). In this case the electrons can travel through the conductive channel from the source to the drain electrode. This channel was created by the accumulation of charges at the dielectric/semiconductor interface. The constant field is indicated by black arrows within the dielectric. In this mode the transistor can be seen as a resistor showing Ohmic behavior. This mode is called the linear regime. If the source-drain voltage is equal to the gate-source voltage it leads to a contraction of the channel where its depth y is reduced to zero at the drain electrode. This point at the drain electrode is called the pinch-off point and is highlighted as a red dot in **Figure 2.8** (b). The arrows in the dielectrics illustrate the direction of the electric field and clarify the field free pinch-off point. If

the source-drain voltage is increased even further (c) the drain-current does not increase further but stays constant. The channel length L is hereby reduced. This mode is called the saturation regime.

**Figure 2.8:** Operation modes of a FET operating with a source-gate voltage  $V_{\rm GS}$  above the threshold voltage  $V_{\rm th}$ . It shows the linear regime if the source-drain voltage  $V_{\rm DS}$  is smaller than  $V_{\rm GS}$  (a), the pinch-off point in red if  $V_{\rm DS} = V_{\rm GS}$  (b), and the saturation regime if  $V_{\rm DS} > V_{\rm GS}$  (c). The direction of the electric field within the dielectric layer is indicated by black arrows.

#### Shockley equations and transistor parameters

The dependencies between the drain-current and the two characterisic voltages  $V_{\rm DS}$  and  $V_{\rm GS}$  can be extracted using the Shockley equations. For the linear regime **Equation 2.4** can be applied. This equation is a result of the linear model [31] if a small  $V_{\rm DS}$  is applied. In this case the transistor can be seen as a resistor, where its resistivity can be changed by the applied  $V_{\rm GS}$  bias. The equation can be derived if the velocity and the applied electric field are assumed to be constant. The drain current can be written as a product of the charge density times the velocity  $I_{\rm D} = -WQ_{\rm inv}v$  where the velocity is defined as  $v = \mu \mathscr{E}$ . Replacing the charge density by the expression  $Q_{\rm inv} = C'(V_{\rm GS} - V_{\rm y} - V_{\rm th})$  the drain current can be written as  $I_{\rm D} = -WC'(V_{\rm GS} - V_{\rm y} - V_{\rm th})\mu\mathscr{E}$ . By substituting the electric field by its definition  $\mathscr{E} = V_{\rm y}/y$  the drain current is  $I_{\rm D} = -WC'(V_{\rm GS} - V_{\rm y} - V_{\rm th})\mu\frac{dV}{dy}$ . This expression can be written as  $\int_{0}^{L} I_{\rm D} \mathrm{d}y = \mu WC' \int_{0}^{V_{\rm DS}} (V_{\rm GS} - V_{\rm y} - V_{\rm th}) \mathrm{d}V_{\rm y}$ . After the integration **Equation 2.4** can be obtained.

$$I_{\rm D} = \frac{WC'}{L} \cdot \mu \cdot \left( (V_{\rm GS} - V_{\rm th}) - \frac{1}{2} V_{\rm DS} \right) \cdot V_{\rm DS} \qquad \text{for} \qquad |V_{\rm DS}| \leq |V_{\rm GS} - V_{\rm th}| \qquad (2.4)$$

The greek symbol  $\mu$  represents the electron mobility and C' labels the areal capacitance. C' is calculated by  $C' = \varepsilon_0 \varepsilon_r d^{-1}$  where  $\varepsilon_0$  is the permittivity of vacuum,  $\varepsilon_r$  the dielectric dependent relative permittivity, and d is the thickness of the dielectric layer. Since transistors containing electronic trap states at the dielectric/semiconductor interface were characterized in this thesis, the threshold voltage  $(V_{th})$  has to be taken into account.

To obtain the equation for the saturation regime (**Equation 2.5**) the quadratic model has to be applied [31]. Here the same assumptions made for the linear model have to be used but this time the charge density may change between the source and drain electrode. First this equation describes a linear increase of the current but eventually peaks. This happens if the charge density at the drain electrode becomes zero as shown in **Figure 2.8** (b). After this pinch-off point holes are accumulated since the sign of the electric field changes. This effect leads to the creation of a depletion layer at the drain electrode where the in excess applied  $V_{\rm DS}$  bias is stored. **Equation 2.5** can be derived by applying **Equation 2.4**, which yields the following expression for the drain current for a small section of the channel with the width y:  $I_{\rm D} = C'\frac{W}{{\rm d}y}(V_{\rm G} - V_{\rm S} - V_{\rm C} - V_{\rm th}){\rm d}V_{\rm C}$ . In this equation the expressions  $V_{\rm G}$ ,  $V_{\rm S}$  and  $V_{\rm C}$  label the voltages at the gate, source, and within the channel, respectively. This equation can be integrated using the following limits  $0 \le y \le L$  and  $0 \le V_{\rm C} \le V_{\rm DS}$  yielding  $\int\limits_{0}^{L} I_{\rm D} {\rm d}y = \mu C'W \int\limits_{0}^{V_{\rm DS}} (V_{\rm G} - V_{\rm S} - V_{\rm C} - V_{\rm th}) {\rm d}V_{\rm C}$ . The result of the integration is  $I_{\rm D} = \mu C'\frac{W}{L}[(V_{\rm GS} - V_{\rm th})V_{\rm DS} - \frac{V_{\rm DS}^2}{2}]$  if  $|V_{\rm DS}| < |V_{\rm GS} - V_{\rm th}|$ . **Equation 2.5** for the saturation regime is obtained if  $|V_{\rm DS}| > |V_{\rm GS} - V_{\rm th}|$  is valid.

$$I_{\rm D} = \frac{WC'}{2L} \cdot \mu \cdot (V_{\rm GS} - V_{\rm th})^2$$

for  $|V_{\rm DS}| > |V_{\rm GS} - V_{\rm th}|$  (2.5)

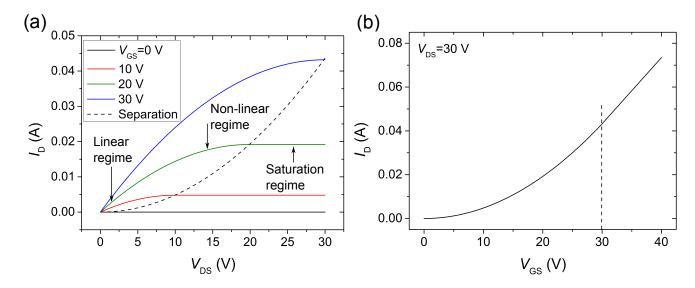

Since two voltage values can be changed in such a FET as introduced in **Figure 2.7**, two kinds of current voltage I-V-curves can be plotted (**Figure 2.9**). The output characteristic in which  $I_D$  is plotted against  $V_{DS}$  at constant  $V_{GS}$  voltages were obtained if **Equation 2.4** was applied as displayed in **Figure 2.9** a). First a linear increase of  $I_D$  as a function of  $V_{DS}$  can be seen (Linear regime). The non-linear regime is reached when  $V_{DS}$  becomes equal to  $V_{GS}$ , which is highlighted by a dashed black line. After that the drain-currents reach a steady state, which is called the saturation regime. The reason for this behavior was explained in **Figure 2.8** (c). **Subfigure 2.9** (b) displays the corresponding transfer characteristic where  $I_D$  is plotted against  $V_{GS}$  at a constant  $V_{DS}$  voltage using **Equation 2.5** and **Equation 2.4** for  $V_{GS} > V_{DS}$ .  $I_D$  increases in a quadratic dependency on  $V_{GS}$  until  $V_{DS}$  is equal to  $V_{GS}$  (dashed black line). Then  $I_D$  increases linearly with increasing  $V_{GS}$ . The transistor parameters for the plots were:  $W = 10,000 \,\mu\text{m}$ ,  $L = 20 \,\mu\text{m}$ ,  $C' = 38.4 \,\text{nF/cm}^2$  of a 90 nm thick SiO<sub>2</sub> layer,  $\mu = 5 \,\text{cm}^2 \,\text{V}^{-1} \,\text{s}^{-1}$ , and  $V_{\text{th}} = 0 \,\text{V}$ .

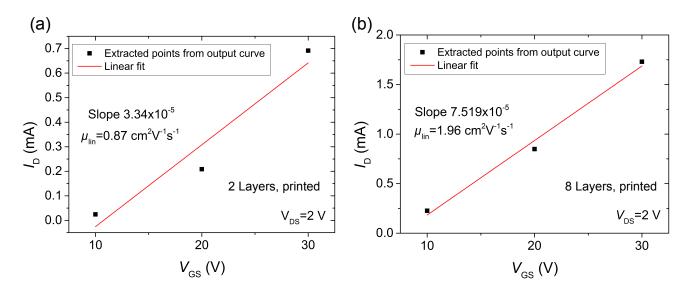

The most important transistor properties can be obtained by a graphical analysis of the transfer characteristic. The linear or field-effect mobility  $\mu_{lin}$  can be determined if the drain-current values in the linear

Figure 2.9: *I-V*-characteristics of an ideal n-type FET calculated using Equation 2.4 and Equation 2.5. Subfigure (a) shows the ideal output characteristics, where  $I_D$  is plotted against  $V_{DS}$  at constant  $V_{GS}$ . In subfigure (b) the corresponding ideal transfer characteristics is obtained if  $I_D$  is plotted against  $V_{GS}$  at a constant  $V_{DS}$ . The dashed lines represents the boarder between the non-saturation and saturation regime.

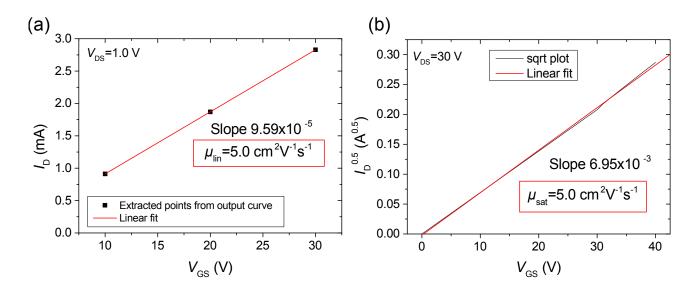

region of the output curves are plotted against the  $V_{GS}$  as displayed in **Figure 2.10** (a).  $\mu_{lin}$  can be calculated using the slope of the linear fit and **Equation 2.6**. This equation can be derived from **Equation 2.4**.

$$\mu_{\rm lin} = \frac{L}{V_{\rm DS}WC'} \left( \frac{\partial I_{\rm D}}{\partial V_{\rm GS}} \right) \tag{2.6}$$

The saturation mobility can be obtained if the transfer characteristics in the saturation regime is plotted in a square root (sqrt) fashion as shown in **Figure 2.10** (b). Using the slope of the linear fit and **Equation 2.7**  $\mu_{\text{sat}}$  can be calculated. The sqrt-plot helps to graphically determine  $\mu_{\text{sat}}$  due to the quadratic dependency of  $I_{\text{D}}$  to  $V_{\text{GS}}$  according to **Equation 2.5**. The threshold voltage can also be extracted from **Figure 2.10** (b) as the x-axis intercept of a linear fit. Both methods results in the same mobility of  $5.0 \,\text{cm}^2 \,\text{V}^{-1} \,\text{s}^{-1}$ .

$$\mu_{\text{sat}} = \frac{2L}{WC'} \left(\frac{\partial I_{\text{D}}^{0.5}}{\partial V_{\text{GS}}}\right)^2 \tag{2.7}$$

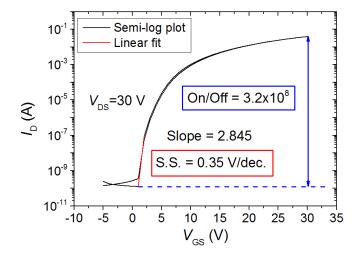

The on/off-current ratio can be determined if the drain-current is plotted semi-logarithmically as a function of  $V_{GS}$  in **Figure 2.11**. In this graph the subthreshold swing (S.S.), which is defined as S.S. =  $\left(\frac{d \log I_D}{d V_{GS}} \mid_{\max}\right)^{-1}$ , can be calculated as the inverse of the logarithmic slope of  $I_D$  highlighted in red.

Figure 2.10: Linear plot of a the drain-current as a function of  $V_{\rm GS}$  at a constant  $V_{\rm GS} = 1.0$  V. The point values are taken from the corresponding output characteristic which is not shown (a). The sqrt-plot of the drain-current as a function of  $V_{\rm GS}$  is displayed in subfigure (b). Using the slope of the linear fit of the left plot the linear mobility  $\mu_{\rm lin}$  can be obtained using **Equation 2.6** and the slope of  $I_{\rm D}$  of the right plot can be used to calculate the saturation mobility  $\mu_{\rm sat}$  according to **Equation 2.7**.

**Figure 2.11:** The on/off-current ratio as well as the subthreshold swing (S.S.) can be determined if the transfer characteristics is plotted semi-logarithmically.

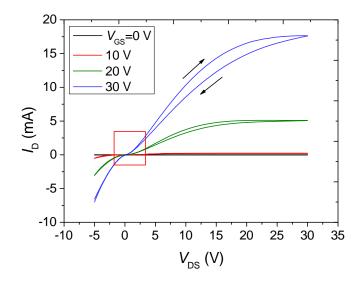

The output characteristic gives information on possible contact resistances between the semiconductor and the source and drain electrodes as introduced in **Figure 2.7**. These resistances can sometimes be seen by the S-shape of the drain-currents close to  $V_{\rm DS} = 0$  V. One example of an output characteristic with an enlarged section showing the contact resistance in the red box is displayed in **Figure 2.12**. This contact resistance occur if the curves do not show straight lines at this point meaning no Ohmic behavior. If the linear mobility is determined according to **Figure 2.10** (a) the appearance of this contact resistance

could lead to the extraction of false data points since the contact resistance appear in the linear regime of the output characteristic.

**Figure 2.12:** Example of an output characteristics that shows pronounced contact resistance. This S-shape of the drain-currents is highlighted by a red box. In addition, the hysteresis, meaning the difference between the forward and backward sweep of  $V_{DS}$ , is marked by black arrows.

Hysteresis as a difference between the forward and the backward sweep of the source-drain voltage can also be identified in an output characteristic. **Figure 2.12** displays such a hysteresis in the form of two black arrows. The reason for this hysteresis is the existence of electron trap states at the semiconductor/dielectric interface [32].

#### 2.3 Basics of amorphous oxide semiconductors

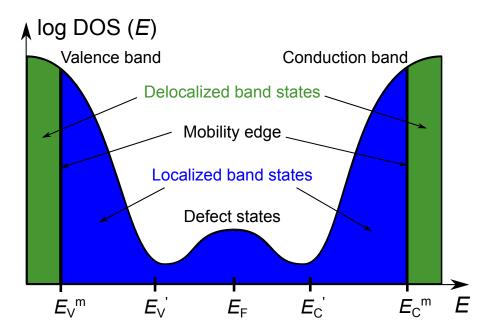

At this point the characteristics of amorphous semiconductors will be discussed referring to the books of Mott and Hunklinger [33, 34]. It is important to reveal the differences between these semiconductors and their crystalline counterparts since most AOSs and also zinc tin oxide (ZTO) are amorphous. In amorphous semiconductors similar to crystalline semiconductors there are bands and a band gap. In the amorphous phase there are differences in the binding length and binding angles between the neighboring atoms that define the band gap. These differences lead to the fact that the DOS show no clear edge but an exponentially phased out trend. This means that the states do not occur often and they are far apart. The electrons in these states are localized. **Figure 2.13** represent the DOS plot of an amorphous semiconductor. The delocalized states of the valence and conduction band are displayed in green and the localized states are displayed in blue. Both states are separated by the mobility edge. The mobility edge states of the valence and conduction band are labeled as  $E_{\rm V}^{\rm m}$  and  $E_{\rm C}^{\rm m}$ .  $E_{\rm V}$  and  $E_{\rm C}$  show the edges of the localized band states. Defect states could exist within the band gap of an amorphous semiconductor as

shown in **Figure 2.13**. These defect states could appear because of unsaturated chemical bonds [33] or adsorbates. Differences in light absorption occur between amorphous and crystalline semiconductors. Transitions can occur between localized states of the valence and the conduction band. This could result in smaller band gap values of amorphous semiconductors in comparison to their crystalline counterparts as for instance in the case of Si. Gap states close to the mobility edge of the conduction band could be responsible for the hysteresis in *I-V*-curves of transistors. Wide deep states close to the mobility edge of the valence band are reported to be the reason why AOSs normally show no p-type conductivity [35].

**Figure 2.13:** DOS with respect to energy in a logarithmic scale for an amorphous semiconductor. The delocalized states and the localized band states of the valence and conduction band are displayed in green and blue, respectively. The mobility edge of the valence and conduction band are labeled as  $E_{\rm V}^{\rm m}$  and  $E_{\rm C}^{\rm m}$ .  $E_{\rm V}$ ' and  $E_{\rm C}$ ' show the edges of the localized band states. Defect states can exist within the band gap. This scheme was inspired by images in the books of Mott [33] and Hunklinger [34]

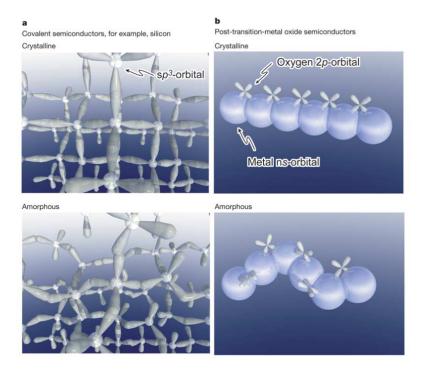

Amorphous oxide semiconductors can be divided into binary systems such as ZnO, SnO<sub>2</sub>, and In<sub>2</sub>O<sub>3</sub>, ternary systems such as ZTO, indium zinc oxide (IZO), and quaternary systems such as IGZO and hafnium zinc tin oxide (HZTO). ZnO is the most studied AOS material and ITO is the most studied material of all TCOs. O<sub>2</sub> vaccancies lead to highly n-type doping in these systems with mobilities ranging from 1 to  $100 \, \text{cm}^2 \, \text{V}^{-1} \text{s}^{-1}$  [11]. Almost all of the TCOs possess an amorphous structure, thus avoiding electron scattering at grain boundaries during charge transport and trap states that are normally observed in polycrystalline films [10]. In addition, they exhibit large band gap energies ranging from 2.8 to 3.7 eV, which makes them transparent in the visible region of the electromagnetic spectrum [36]. In contrast to the rigid  $sp^3$  orbital system of Si, where Hall mobility values deteriorate from the crystalline to the amorphous phase, transition metal oxides show comparable Hall mobilities in the crystalline and

the amorphous phase. This effect is due to the metal-oxygen-metal bonding between the large metal s-orbitals and the small oxygen (O) p-orbitals which is not extensively altered at the crystalline to amorphous transition [6]. **Figure 2.14** taken from the publication by Nomura  $et\ al$ . [6] illustrates this model in subfigure **b** and compares it with the rigid  $sp^3$  orbital system of a classical semiconductor with a covalent bonding system such as Si in subfigure **a**. Transition metal cations possessing an electronic configuration  $(n-1)d^{10}n$  s<sup>0</sup> with n being geater than or equal to 5 show the above described behavior between the crystalline and amorphous phase [37]. The widely studied materials IZO, IGZO, and ZTO fulfill this requirement. ZTO was evaluated in the framework of this thesis.

**Figure 2.14:** Illustration of the orbital arrangement in a classical  $sp^3$ -hybridized semiconductor as Si **a**, and in a TCO composed of big s-orbitals and small p-orbitals **b**. In the former case the overlapping between the orbitals and consequently the electron mobility detoriates by the crystalline to amorphous transistion, but in the latter case the overlapping of the big s-orbitals is not altered extensively. This image was taken from the publication of Nomura  $et\ al.\ [6]$ .

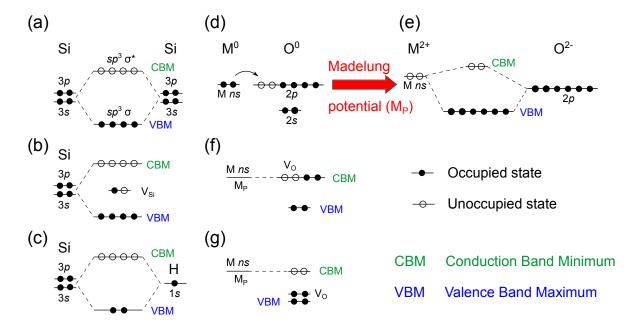

A detailed picture of the band structure of such a covalent semiconductor as Si in comparison to a more ionic like semiconductor such as a TCO will now be presented. A sketch of these two systems is illustrated in **Figure 2.15** referring to the review article of Kamiya and Hosono [10].

In Si the band gap  $E_g$  is defined as the gap between the VBM and CBM. The former is known to be the bonding  $sp^3$ -hybridized  $\sigma$ -orbitals and the latter is known to be the anti-bonding  $sp^3$ -hybridized  $\sigma^*$ -orbitals (a).  $E_g$  is formed because of the energetic splitting of the two states. If a Si vacancy  $V_{Si}$  is formed, a dangling bond state with one unpaired electron is created in the middle of the band gap (b). This state can act as a trap state for electrons and holes affecting the functionality of n- and p-type Si

**Figure 2.15:** Simplified band structure of Si and TCO. The band diagram of Si (a) is altered to (b) if a Si vacancy  $V_{Si}$  is created in the middle of the band gap. This unoccupied state can act as electron or hole trap state. This state can be negated by hydrogen treatment (c). The equilibrium band structure of a transition metal oxide (d) is changed by electron transfer from the metal to the O atom, which is indicated by an arrow. The created ionic states are stabilized by the Madelung potential  $M_P$  leading to a rise in the cationic level and a decrease in the anionic level (e). If an O vacancy  $V_O$  is created in the metal oxide, states will appear in or near the conduction band maximum which can act as donors (f). Normally these states are not stable and relax to occupied states near the VBM, which can not act as electronic trap centers (g). This image was inspired by the publication of Kamiya and Hosono [10].

devices. To avoid such dangling bonds the semiconductor is passivated using hydrogen in order to move this state into the valence band (c). The band diagram of a TCO is displayed in **Figure 2.15** (d). It is changed if two electrons are transferred from the metal to the O atoms. This leads to a reorganization of the band structure because the electronic level of the metallic cation is increased and the electronic level of the O anion is lowered according to the Madelung potential. In this case the VBM is formed by the O 2p-orbitals which are now fully filled while the CBM is formed by the unfilled metallic s-orbitals (e). If an O vacancy  $V_O$  is now created, states in or near the CBM states appear which can act as shallow donors, but not as trap centers for electrons (f). These states are not stable and relax to fully occupied states near the VBM that can no longer act as electron trap centers (g). For TCOs the Madelung potential is very important since it is the cause of their transparency, large band gap, and small amount of electron trap states in the band gap [35].

#### 2.4 Zinc tin oxide as semiconductor

Zinc tin oxide (ZTO) can be seen as a combination of ZnO and SnO<sub>2</sub>. It can be written as  $(\text{ZnO})_x(\text{SnO}_2)_{1-x}$  with x being in the range between 0 and 1. ZTO, especially with x < 50 %, is also reported to be very stable against chemical etching [38]. The ZTO system is widely studied in the literature since it does not contain the not so abundant but widely used indium [12]. In 2010 Lee *et al.* showed that ZTO exhibits a band transport in the saturation regime [39]. This band transport is due to delocalized states which are more pronounced at higher values of the charge carrier concentration *n*. Temperature dependent mobility measurements reveal that the mobility decreased with increasing temperature in the saturation regime. This trend is typical for a band transport. Their result show a clear mobility edge with good agreement with the model of Mott [40].

Currently ZTO films are processed by sputtering [41, 42, 43, 16] or spin-coating techniques [44, 45, 46, 47] which are both associated with a large material consumption. In contrast, the ink-jet printing process is more favorable because the ink is mainly supplied to the area of interest. No additional post processing like patterning with masks or photolithography are necessary, thereby leading to a reduction in potential production costs by 64 % [15]. This implies that production waste can be reduced and the scale of production can be increased [48].

There are two ZTO phases reported in the literature. The first one is the trigonal, illmenite phase of ZnSnO<sub>3</sub> first processed via an ionic exchange reaction by Kovacheva and Petrov in 1998 [49] and the second one is the inverse cubic spinell phase of Zn<sub>2</sub>SnO<sub>4</sub> first reported by Barth and Posnjak in 1932 [50]. Kovacheva and Petrov reported that the ZnSnO<sub>3</sub> phase is not thermodynamically stable and decomposes into Zn<sub>2</sub>SnO<sub>4</sub> and SnO<sub>2</sub> [49]. The bandgap of ZnSnO<sub>3</sub> has been reported to be 3.5 eV and the work function to be 5.3 eV [51]. Zn<sub>2</sub>SnO<sub>4</sub> has a bandgap of 3.35 eV [41] and a work function of 5.02 eV [52]. The CBM is defined in both phases by unoccupied 4s and 5s orbitals of zinc (Zn) and tin (Sn), respectively [38].

The first transistors were processed by magnetron sputtering reported by Chiang *et al.* in 2004 [42]. Jeong *et al.* reported on thin film transistors composed of solution processed ZTO [53]. They employed  $Zn(CH_3COO)_2 \cdot 2H_2O$  and  $Sn(CH_3COO)_2$  in a solution of 2-methoxyethanol and ethanolamine as a stabilizer. Their thin films show an amorphous structure with embedded nanocrystals if processed at 500 °C. It was reported that if other elements like indium (In) or tin (Sn) are added to the crystalline ZnO the system transforms into an amorphous structure [54, 55]. Processed bottom-gate, top-contact transistors using  $SiO_2$  gate dielectrics exhibit a maximum mobility of  $1.1 \text{ cm}^2 \text{ V}^{-1} \text{ s}^{-1}$ . Ink-jet printed ZTO transistors were first reported by Kim *et al.* in 2009 [56]. They used a similar precursor route and transistor layout as reported by Jeong *et al.* [53], but this time the solution was applied via ink-jet

printing. Their maximum saturation mobility was reported to be  $0.6\,\mathrm{cm^2~V^{-1}s^{-1}}$ . Unfortunately, almost all groups use the widely applied but toxic 2-methoxyethanol as a solvent, which is not suitable for industrial production. In 2015 Branquinho *et al.* [57] showed that a precursor solution based on EtOH can result in high quality ZTO layers. They could create transistors with a saturation mobility of  $0.8\,\mathrm{cm^2~V^{-1}s^{-1}}$  using a thin  $\mathrm{AlO_x}$  dielectric layer.

22 Theory

## 3 Experiment

This chapter will introduce the ethanol (EtOH) based precursor route. The two solution processing methods, spin coating and ink-jet printing, are presented. In addition, the various thin film characterization techniques that give information about the morphology, structure, and electronic levels of ZTO are displayed. Then the different transistor layouts used throughout this thesis will briefly be presented. The chapter closes with a presentation of the electrical characterization of the transistors.

#### 3.1 Precursor route

In this section it will be presented how the ZTO precursor solution was processed. The precursor route is also based on EtOH as a solvent similar to the one described by Branquinho *et al.* [57]. But in contrast to their approach no urea  $(CO(NH_2)_2)$  as a fuel but HCl as a stabilizer and oxidation agent was added. First the hygroscopic salts zinc nitrate hydrate  $(Zn(NO_3)_2 \cdot xH_2O)$  99.999% and tin(II)-chloride  $(SnCl_2)$  99.99% both purchased from Sigma-Aldrich were weighted in a nitrogen  $(N_2)$  filled glove box (GB). This mixture of salts was then dissolved in 99.8% pure EtOH  $(H_5C_2-OH)$  ordered from Carl Roth GmbH in air. The obtained solution exhibits precipitation, since basic tinchlorid is not stable under hydrophilic conditions (**Equation 3.1**) [58].

$$SnCl_2 + H_2O_{(g)} \rightleftharpoons Sn(OH)Cl + HCl$$

Precipitation (3.1)

With addition of HCl 34 wt % (Merck) the balance of **Equation 3.1** can be shifted to the left. This avoids the formation of basic tin hydroxide chloride Sn(OH)Cl salt as a product of the presented hydrolysis reaction (**Equation 3.2**). The SnCl<sub>2</sub> is strongly reductive [59]. Oxygen from the air leads to a slow oxidation of SnCl<sub>2</sub> from Sn<sup>2+</sup> 2 Cl<sup>-</sup> to Sn<sup>4+</sup> 4 Cl<sup>-</sup> (**Equation 3.2**) [58]. The formation of Sn(OH)Cl and the resulting precipitation reaction are avoided.

$$\operatorname{SnCl}_2 + 2\operatorname{HCl} + \tfrac{1}{2}\operatorname{O}_2 \longrightarrow \operatorname{SnCl}_4 + \operatorname{H}_2\operatorname{O} \qquad \text{No precipitation} \tag{3.2}$$

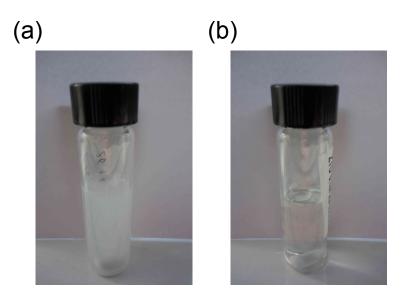

The difference between the two reactions can be seen in the pictures of precursor solutions in **Figure 3.1**. Picture (a) shows precipitation of Sn(OH)Cl if no HCl was added. A clear solution with no signs of precipitation can be seen in picture (b).

**Figure 3.1:** Pictures of the ZTO precursor solution without the addition of HCl showing precipitation (a) and with the addition of HCl resulting in a clear solution (b).

This precursor solution was then stirred for at least 14 hours at room temperature in air. Before usage it was filtered through a  $0.2\,\mu m$  polytetrafluoroethylen (PTFE)-filter in order to remove any residuals. The final precursor solution is stable for up to twelve month stored in ambient atmosphere.

#### 3.2 Processing methods

The above described precursor solution was either applied by spin coating or ink-jet printing. Both methods will now briefly be described. In addition, it will be explained how the processed films are transformed to the oxide state and which organic dielectrics were used for the top-gate transistors.

#### Spin coating and annealing condition

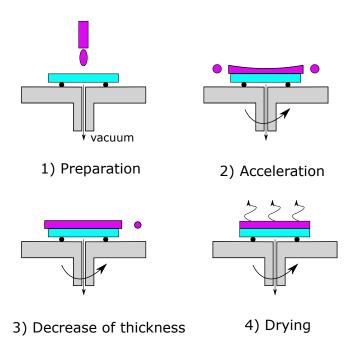

Spin coating or spin casting is a common method for the application of solutions or dispersions. After dispensation onto the substrate, thin films can be processed by rotating the substrate at high angular velocity between 1500 and 5000 revolutions per minute (rpm). As first reported by Lawrence in 1988 [60] the spin coating process can be separated into four steps: preparation, acceleration, decrease of thickness, and drying (**Figure 3.2**).

24 3 Experiment

**Figure 3.2:** Illustration of the four steps of a spin coating process: 1) preparation, 2) acceleration, 3) decrease of layer thickness, and 4) drying.

First, the substrate is fixed onto the spinning table by using a slight vacuum. Then the precursor solution is applied and the spin coater is turned 'on' simultaneously. At the beginning excess solvent is thrown off the substrate until the film is thin enough that it can withstand the rotating speed of the substrate. The acceleration of the substrate until the final spin casting speed was reported to have an influence on the uniformity of the layers. The higher the final spin coating speed the more uniform the layers will be [61]. Once the film can follow the speed of the substrate the viscous and adhesive forces match the centrifugal forces. The viscosity of the solution, determined mainly by its concentration, has the biggest impact on its flow. During the last step the layer thickness is decreased by the drying process, meaning the evaporation of solvent. The final film thickness depends on the concentration of the solvent at the beginning and the spinning speed.

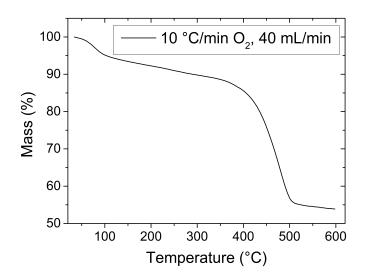

After the application of the precursor solution, either by spin coating or by ink-jet printing, it has to be transformed to its semiconducting oxide state. This process is normally performed by thermal decomposition of the precursor in an oven or on a hotplate. But other methods like UV ozone treatment in combination with thermal annealing [62], chemical decomposition [63, 64], and laser sintering [65] are possible too. However, in this thesis the processed precursor solution was annealed at 500 °C for 10 min on a hotplate in air after each layer deposition step if not stated otherwise.

#### Ink-jet printing

Apart from the above described spin coating process, ink-jet printing was also used throughout this thesis for the application of ZTO precursor solutions. The description of this technique will refer to

3.2 Processing methods 25

the review articles of Cummins [66], Derby [67], and Wijshoff [68]. First the different types of ink-jet printing systems will be presented. Second, the piezoelectrically driven system will be discussed in more detail. This subsection closes with an explanation of the possible interactions between the drops and the substrate including the coffee stain effect, and a presentation of the most important ink parameters.

Since its invention in the beginning of the early 19th century ink-jet printing was applied in the publishing and graphics industry. But the first commercial ink-jet printing systems were not produced before the 1950's. Ink-jet printing technology can be divided into two main branches: the continuous branch where drops are ejected continuously and the drop-on-demand (DOD) branch. The on demand drops are created by thermal, piezoelectric, electrostatic, or acoustic excitation. Since in this thesis the DOD technique based on piezoelectric excitation was used, it will now be discussed briefly.

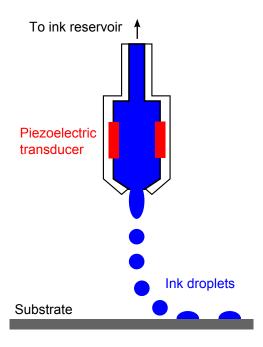

**Figure 3.3** shows an illustration of how a piezoelectric powered DOD ink-jet printer works. The ejection of the ink is managed by a piezoelectric transducer which is displayed in red. The necessary pressure to eject ink droplets is created by mechanical forces which are created by the inverse piezoelectric effect and the application of an electrical bias signal.

**Figure 3.3:** Sketch of a piezoelectric driven DOD ink-jet system containing a piezoelectric transducer displayed in red.

A satisfying printing result not only requires an advanced printing system but additionally certain properties of the ink. The main constants which characterize the quality of the ink are composed of these parameters: density  $\rho$ , dynamic viscosity  $\eta$ , and surface tension  $\kappa$ . They are used to define the Reynolds Re, Weber We, and Ohnesorge Oh numbers which are expressed in **Equations 3.3** to **3.5**.

26 3 Experiment

$$Re = \frac{\nu_{\rm F} \rho d_{\rm n}}{\eta} \tag{3.3}$$

$$We = \frac{v_{\rm F}^2 \rho d_{\rm n}}{\sigma} \tag{3.4}$$

$$Oh = \frac{\sqrt{We}}{Re} = \frac{\eta}{(\sigma \rho d_{\rm n})^{0.5}}$$

(3.5)

The other parameters are the fluid velocity  $v_{\rm F}$  and the diameter of the printing noozles  $d_{\rm n}$ . Fromm defined another constant Z as Z=1/Oh here labeled as Fromm number [69]. This number should range between one and 10 according to Reis and Derby in order to achieve a good drop formation [70, 67]. If Z is smaller than one the ink is too viscous to be ejected and if Z is larger than 10 its viscosity is too small leading to the creation of satellite drops and spilling. Another effect, which often appears in the printing process, is the coffee stain effect. It occurs when the contact line of the solvent is pinned which leads to a material transport from the center of the droplet to its edge, where a ring is created after the evaporation of the solvent [71]. Another explanation was given by Hu and Larson in 2006 [72]. They explained that it occurs if the Marangoni flow, which is created by the latent heat of evaporation, is suppressed.

For the application of the precursor ink a commercially available desktop DOD ink-jet printer Dimatix DMP2831 from the Fujifilm Holdings Corporation was used. The cartridges store up to 1.5 mL ink, which is ejected through 16 nozzles. Each printed drop contains 10 pL of ink. The spacing between the individual drops was set to 20 µm. Using the printer software it is possible to operate the printer with a predefined printing pattern. The printed films were thermally annealed in the same manner as the spin coated films.

#### 3.3 Transistor layouts

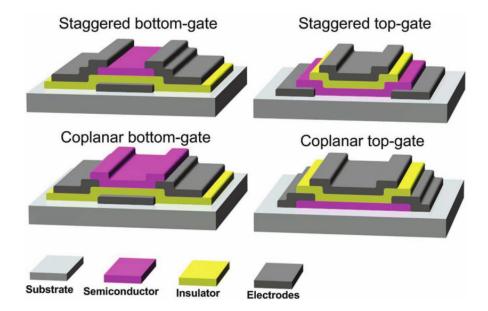

Displayed in **Figure 3.4** are four different layouts possible in a thin-film transistor [15].

FETs can be distinguished by the location of the gate electrode at either top or bottom and by the position of the source and drain electrodes relative to the semiconductor as either staggered or coplanar. Staggered is used if the source and drain electrodes are on opposite sides of the semiconductor/dielectric interface and coplanar if they are orientated on the same sides defined by Wallmark and Johnson [73]. The staggered bottom-gate layout is mainly used for the application of amorphous Si because it can easily be processed and shows the best electrical performance. This is the standard layout for display

3.3 Transistor layouts 27

**Figure 3.4:** Illustration of four main field-effect transistor layouts namely bottom-gate or top-gate orientation in staggered or coplanar positioning of the source and drain electrodes relative to the semiconductor. This illustration was taken from the publication of Fortunato *et al.* [15].

manufacturing because the gate electrode shields the semiconductor from the backlight. Polycrystalline Si is normally processed using a coplanar top-gate structure because its crystallization requires high temperature which could affect the lower layers. This layout also protects the semiconductor from contact with air.

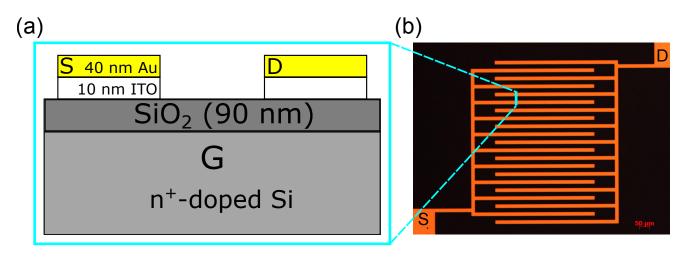

## Bottom-gate, bottom-contact layout

Now the layouts applied in this thesis will be presented and discussed. Prestructured and commercially available substrates from the Fraunhofer Institute for Photonic Microsystems IPMS (Dresden, Germany) were used as a standard. They exhibit a bottom-gate, coplanar bottom-contact layout, a size of 15x15 mm, and are labeled from here on as Fraunhofer (FH) substrates. The substrates consist of n-doped Si ( $n = 3x10^{17}$  cm<sup>-3</sup>) exhibiting a thickness of 675  $\mu$ m and act as the gate of the transistor. They were covered at the IPMS by a 90 nm thick thermally grown SiO<sub>2</sub> used as gate insulator, followed by interdigitated source/drain electrodes composed of 10 nm ITO as an anchor layer and 30 nm Au. From the 16 prestructured transistors only four with a channel length  $L = 20 \,\mu$ m and a width W of 10 mm (W/L = 500) were analyzed to avoid short channel effects. The main benefit of these substrates is that only the semiconductor has to be applied in order to build functional devices. **Figure 3.5** (a) shows a cross-sectional representation of a single source-drain structure and **Figure 3.5** (b) displays the top view image of the interdigitated source/drain structure of a 20  $\mu$ m channel length transistor. In the top right and bottom left of the latter image a part of the contact pads can be identified.

28 3 Experiment

**Figure 3.5:** Cross-sectional representation of a FH substrate exhibiting a bottom-gate, bottom-contact layout (a). Top view image of a FH substrate showing the interdigitated source/drain structures with a channel length of 20 μm and a channel width of 10 mm (b).

The FH substrates were first cleaned by ultrasonication in technical acetone for 10 minutes, followed by a purging step with de-ionized (DI)-H<sub>2</sub>O. These two steps were necessary in order to remove a protective polymer layer applied by the supplier. Then they were cleaned by ultrasonication in pure acetone and propanediol for 15 minutes. Subsequently they were treated in an air plasma (70 W) for 60 s in a home made vacuum chamber in combination with the RF-generator PFG 300 RF by Trumpf Hüttinger GmbH & Co KG if ZTO was applied by ink-jet printing. If ZTO was applied by spin coating the substrates were put for 15 min in an UV-ozone photoreactor PR-100. Both treatments were performed to increase the hydrophilicity of the substrates and to remove organic residuals.

## Top-gate layout

In addition staggered top-gate transistors were processed. Glasses with a thickness of 1.1 mm and covered with 100 nm ITO were purchased from VisionTek Systems Ltd. (Chester, UK). These substrates were patterned in order to define ITO contact pads using a photolithographic process which involved the application of the photoresist AZ 1518 via spin coating followed by a UV treatment for 1 min and sequential development and etching in MIF 726 and hydrobromic acid (HBr). Then they were cleaned by ultrasonication in N-methyl-2-pyrrolidone (NMP) and acetone for 60 min each. Each of the glass substrates were cut into four 25x17.5 mm pieces. Remaining glass splinters were sprayed off with DI-H<sub>2</sub>O. Then they were cleaned by ultrasonication in 5 vol % Deconex watery solution, followed by a DI-H<sub>2</sub>O spraying and N<sub>2</sub> drying step. They were put in acetone and propanediol and cleaned by ultrasonication for 15 minutes each.

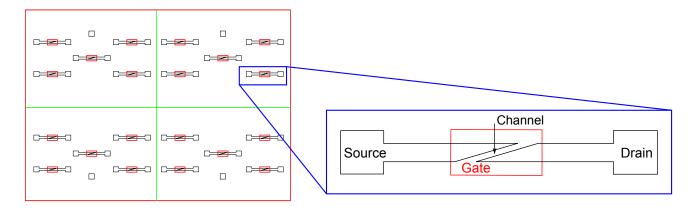

**Figure 3.6** displays the masks for the evaporation of the source-drain (black) and the gate structure (red). The substrate is cut along the green lines in order to obtain four samples. A single transistor with the

3.3 Transistor layouts

three electrodes and channel is shown as an enlargement of this figure. The glass substrates with the

**Figure 3.6:** Masks for the top-gate source-drain structure and the gate structure displayed in black and red, respectively. The substrate is cut along the green lines into four samples. It also shows an enlargement of the super-imposed masks of one top-gate transistor.

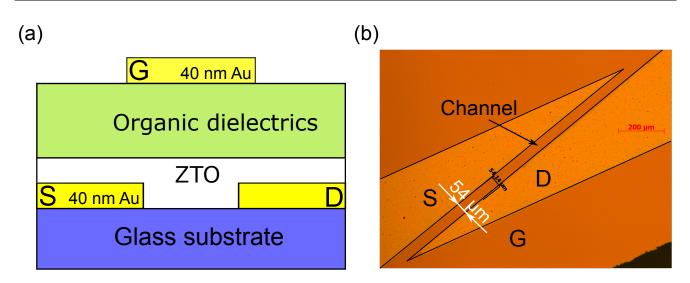

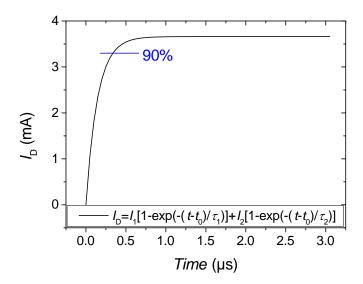

ITO contact pads were transferred to the evaporation chamber were 40 nm thick Au source and drain structures were applied. They define a channel with a length of 54 µm and a width of 1520 µm. Au was applied via a standard physical vapor deposition (PVD) process in an ultra high vacuum (UHV) chamber at a pressure of  $<10^{-6}$  mbar. The metal is heated via Joule heating until it starts to evaporate. The oscillating quartz crystal measures the rate of deposition in Å/s and the amount of deposited material in nm if the shutter above the evaporation boat is opened. When the deposition rate has reached the desired value, the shutter below the sample holder containing the sample can be opened and the deposition of the material onto the substrate starts. If the desired thickness is achieved the shutter is closed again. Typical metallic film thickness values are 40 nm and deposition rates are 2.0 Å/s. The noble metal Au was used because it does not oxidize and is stable against the acidic precursor solution. In addition, it sustains the annealing step at 500 °C. After the processing of ZTO either by spin coating or ink-jet printing the organic dielectrics are applied. They are applied by spin coating and drying as presented in the next subsection. The final device was obtained by thermal evaporation of 40 nm of Au top-gate electrode in the evaporation chamber. A representation of this staggered top-gate transistor is displayed as a crosssection representation in Figure 3.7 (a) and as a top view image of the channel region in Figure 3.7 (b).

## Organic dielectrics

In the top-gate configuration organic dielectrics were applied. Now these polymeric materials will be presented. PMMA was mainly used as the organic dielectric for top-gate transistors throughtout this thesis. PMMA shows good thermal and mechanical resistance and exhibits an electric resistivity ex-

30 Separation 3 Experiment

**Figure 3.7:** Cross-sectional illustration of the staggered top-gate layout used (a). Top view image of the channel region with labeling of the three electrodes (b).

ceeding  $2 \cdot 10^{15} \,\Omega$ cm [74]. The structural formula of PMMA also known under its industrial brand name PLEXIGLAS® can be seen in **Figure 3.8**. According to Kawamoto *et al*. [21] it exhibits the following values for the band gap, the work function, and the ionization energy:  $E_g = 4.8 \,\text{eV}$ ,  $\Phi = 5.0-5.2 \,\text{eV}$ , and  $E_{\text{ion}} = 8.1 \,\text{eV}$ .

$$CH_3$$

$O$

$O$

$H_3C$

$H_3C$

$n$

$CH_3$

Figure 3.8: Structural formula of poly(methyl methacrylate) (PMMA).

The utilized PMMA 7N granulates were purchased from Evonik Performance Materials GmbH and have a molar mass of 94.000 g/mole. PMMA solutions were produced by dissolving 6 or 10 wt % of PMMA in n-butyl acetate ( $H_3C-CO-O-C_4H_9$ ) purchased from Sigma-Aldrich, then stirring the mixture for at least 15 hours at 70 °C in a glove box. After filtering using a 0.2  $\mu$ m PTFE filter the final solution was obtained and left stirring on a stirring plate. Thin PMMA layers were obtained by spin coating the final solution at various spinning speeds and drying the films at 110 °C for 10 min on a hotplate. This temperature was selected because it is above the glass transition temperature  $T_G$  of PMMA of 105 °C and below its melting point of 160 °C.

Another polymeric dielectric used was PS with a  $T_G$  of 100 °C, purchased from BASF SE. Solutions in *n*-butyl acetate are prepared in the same manner as the PMMA solutions. The solution is applied

3.3 Transistor layouts 31

similarly to the PMMA solution by spin coating and drying at  $110\,^{\circ}$ C for  $10\,\text{min}$  on a hotplate. The structural formula of PS is displayed in **Figure 3.9**. The following electronic levels were reported for PS:  $E_g = 4.1\,\text{eV}$  [75],  $\Phi = 5.0\text{-}5.4\,\text{eV}$  and  $E_{\text{ion}} = 8.1\,\text{eV}$  [21].

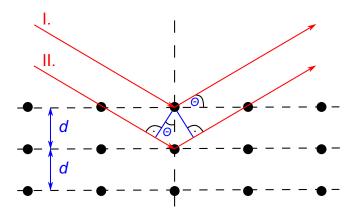

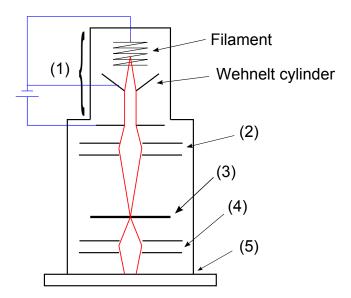

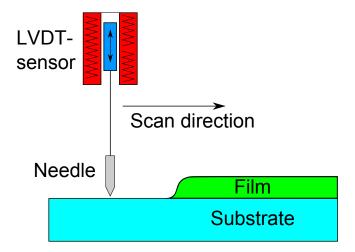

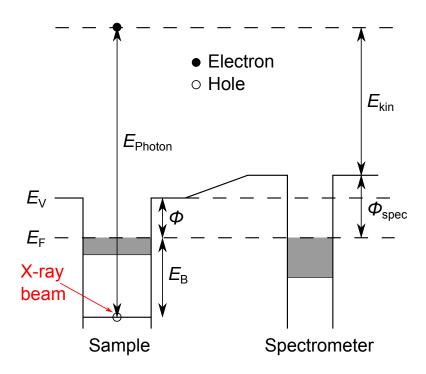

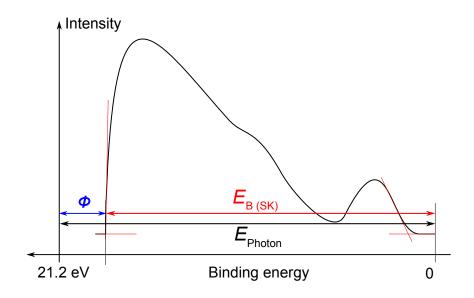

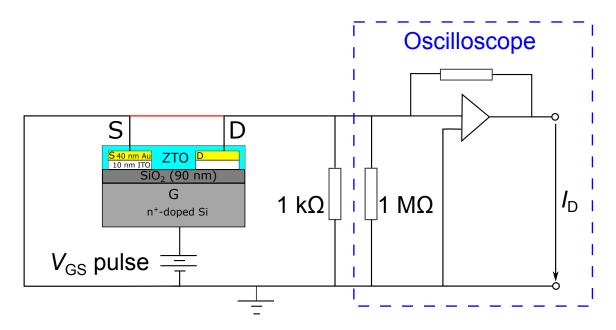

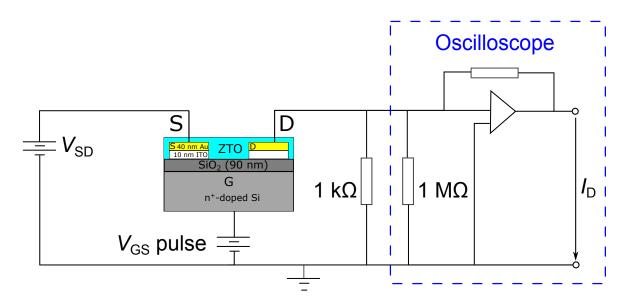

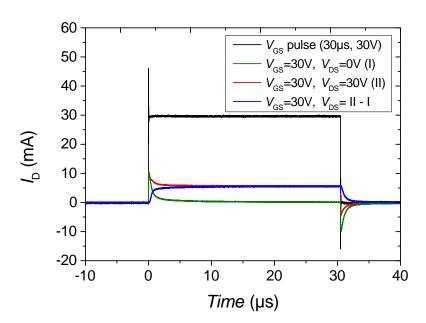

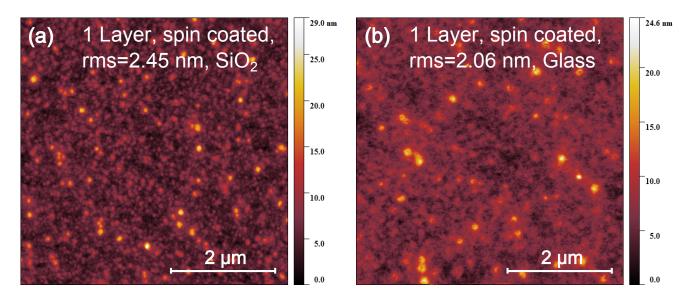

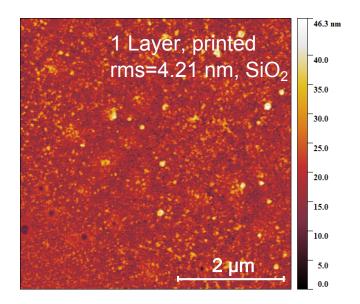

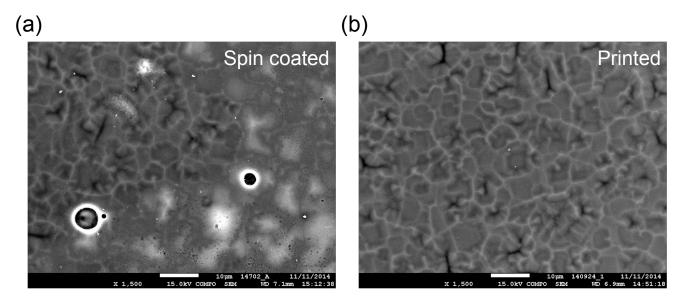

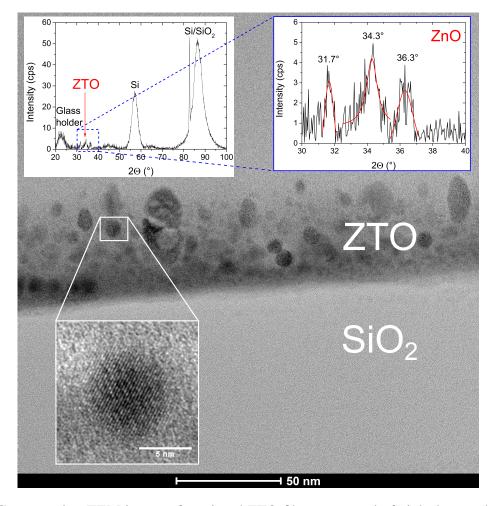

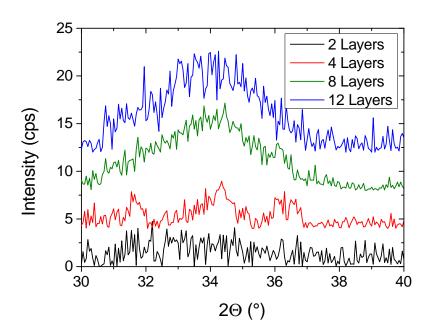

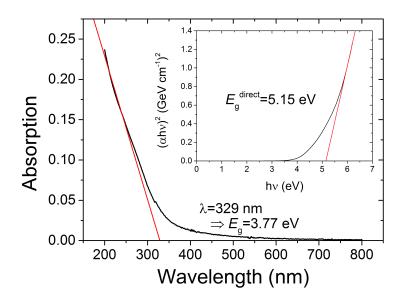

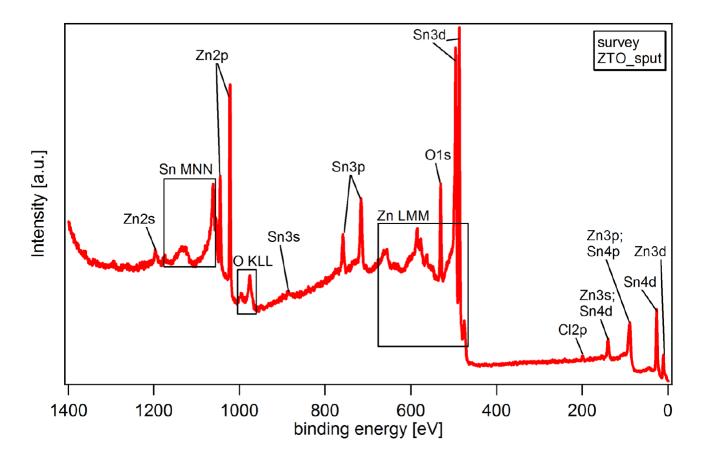

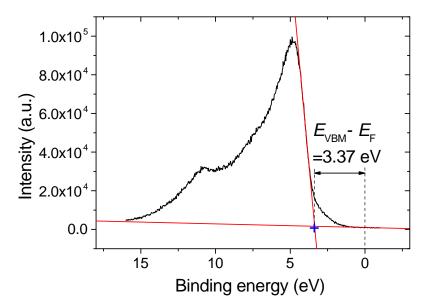

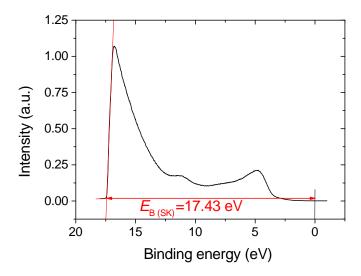

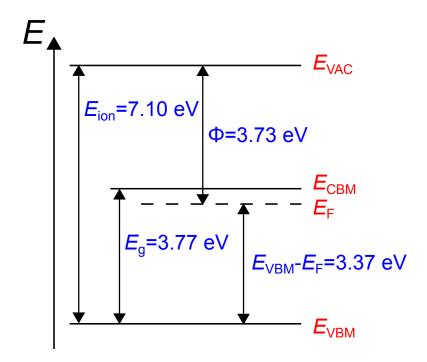

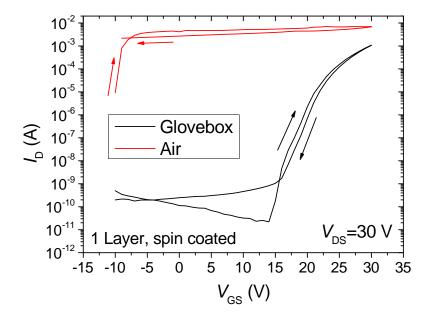

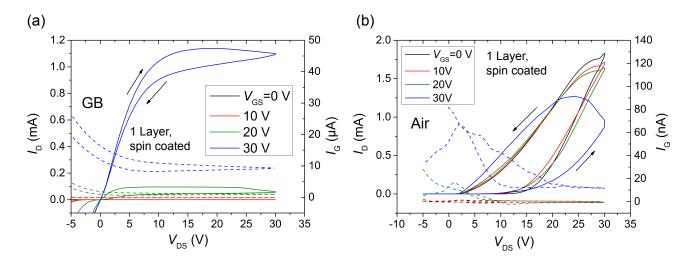

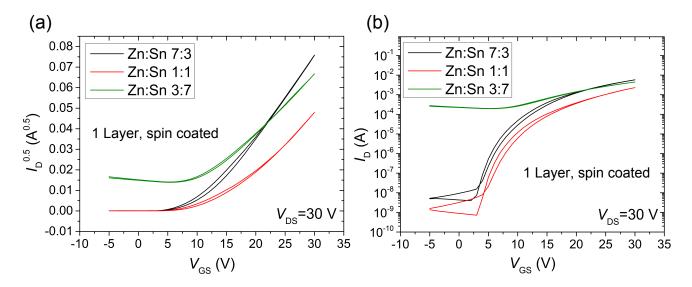

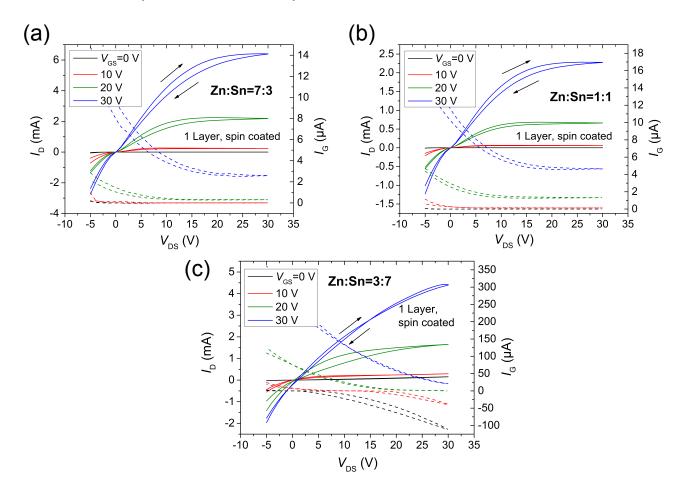

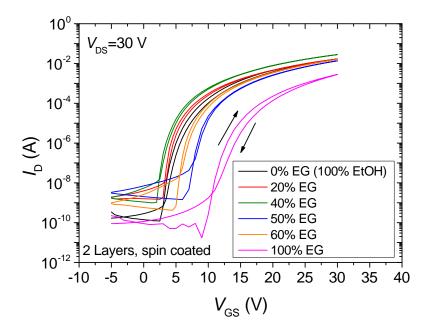

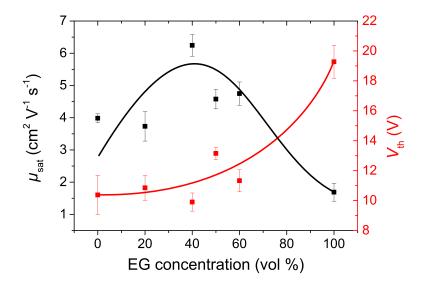

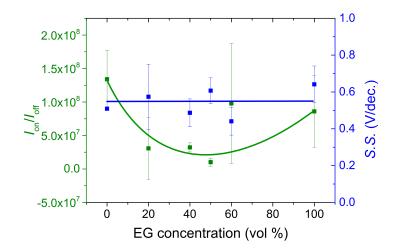

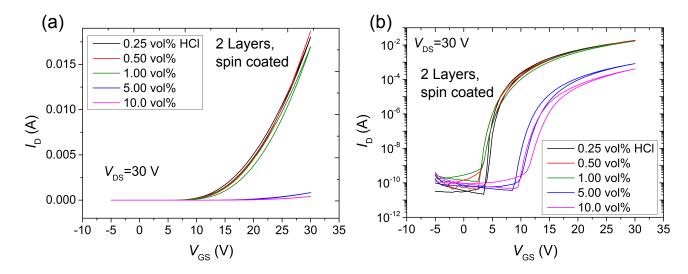

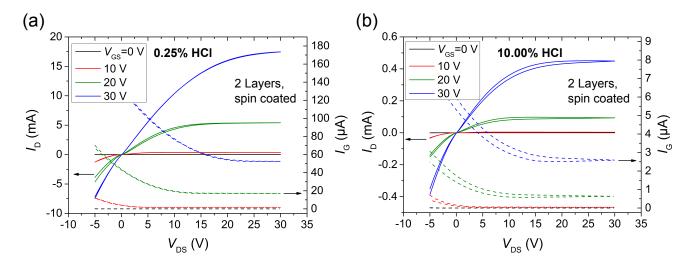

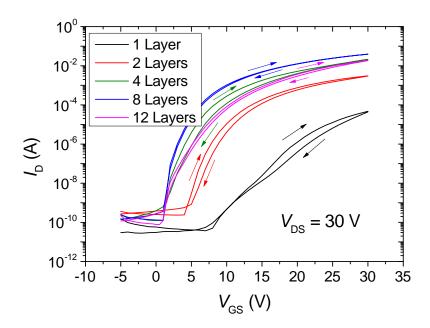

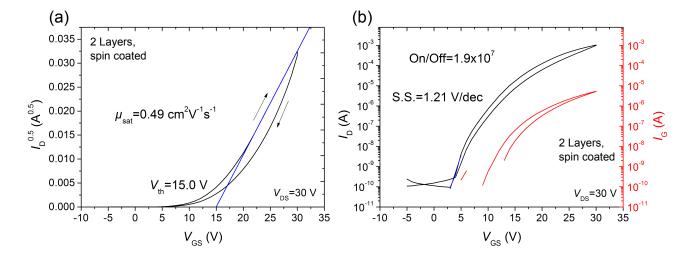

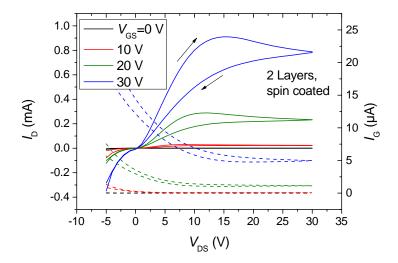

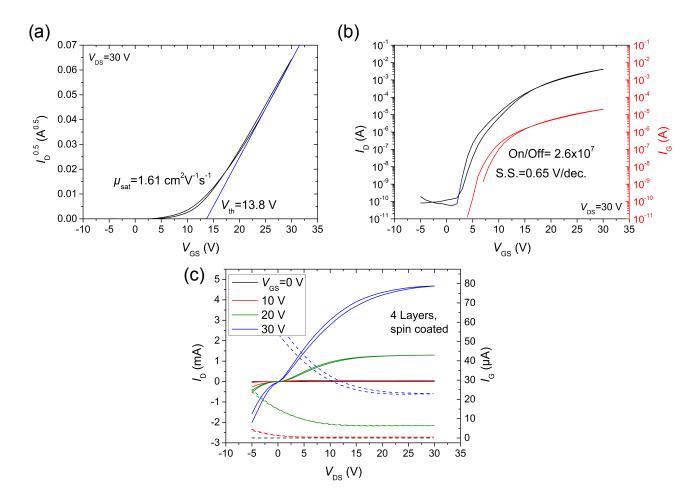

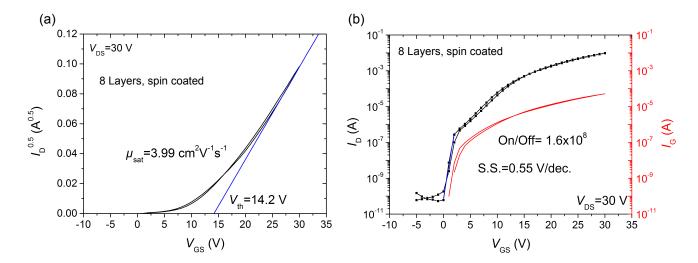

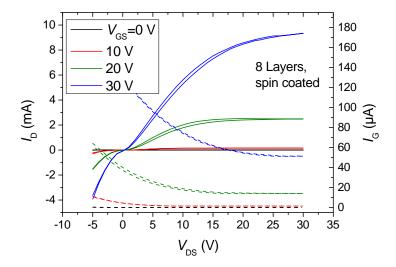

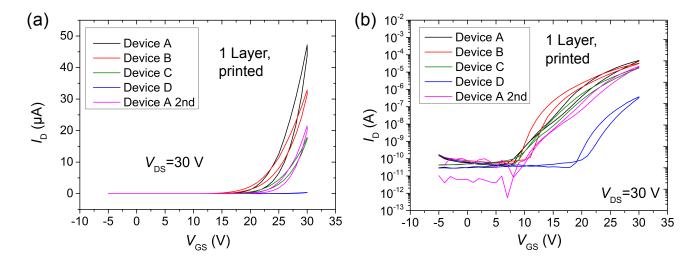

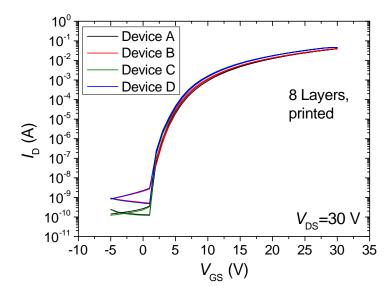

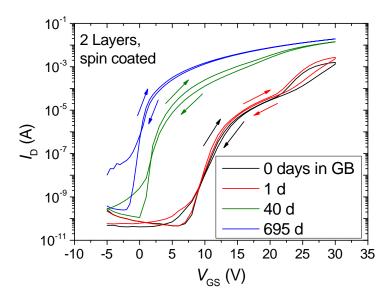

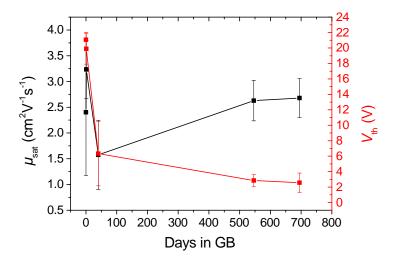

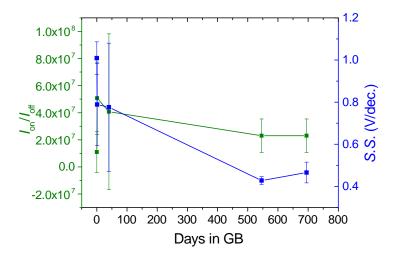

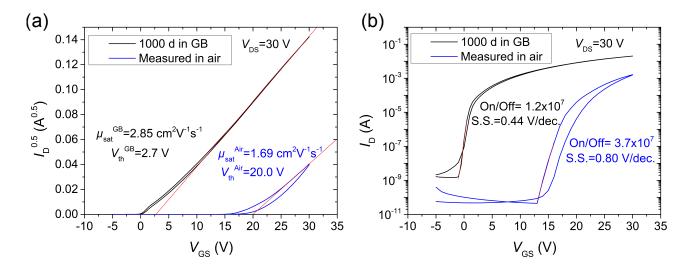

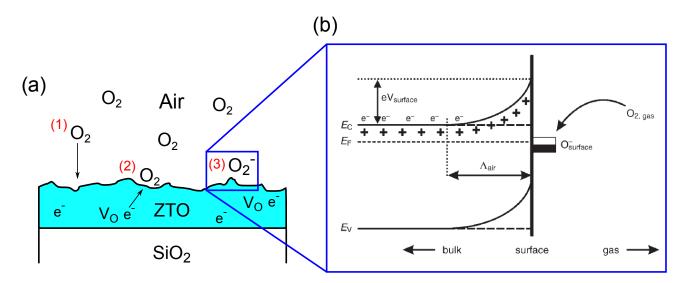

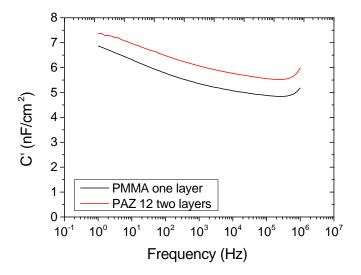

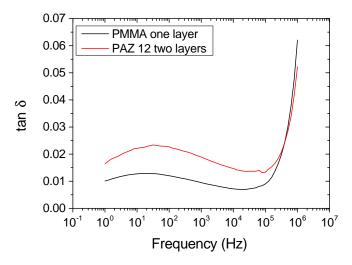

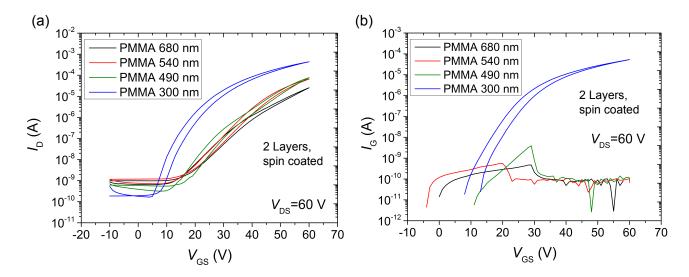

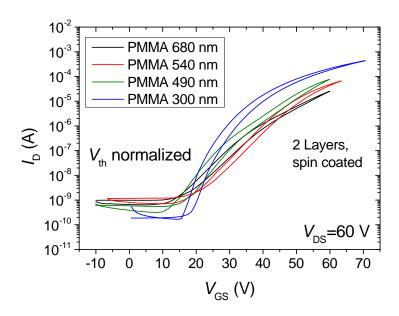

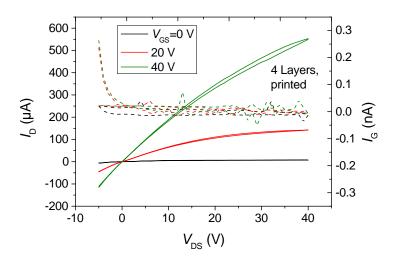

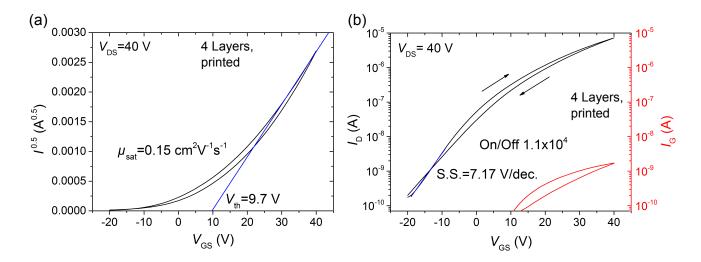

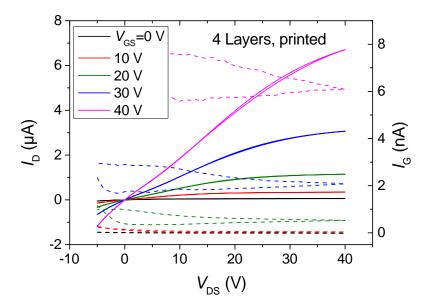

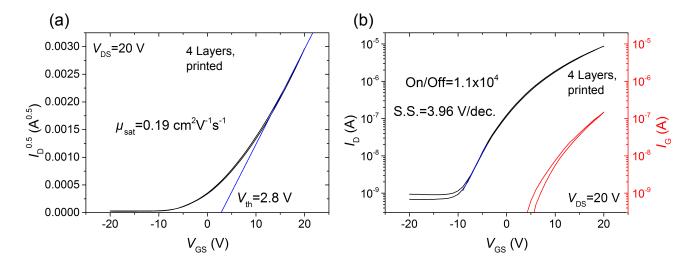

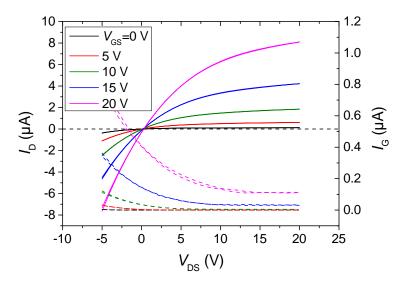

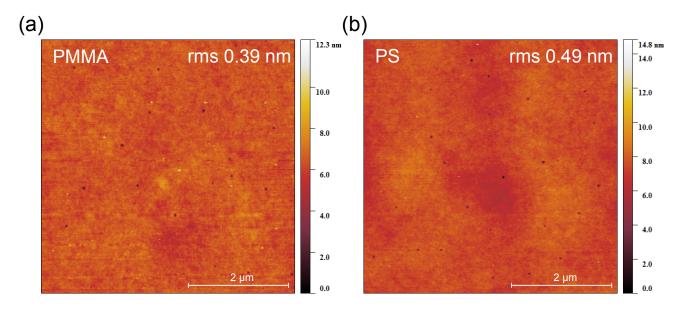

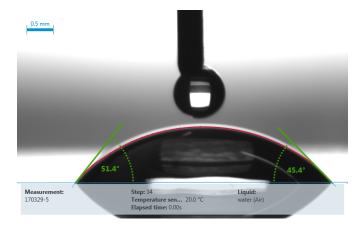

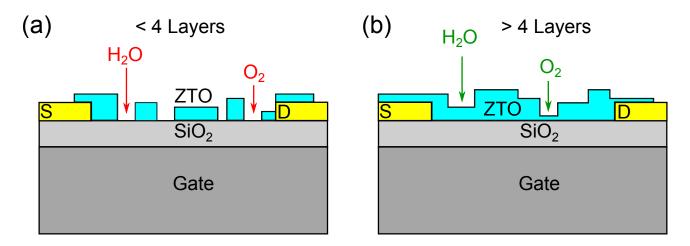

**Figure 3.9:** Structural formula of polystyrene (PS).